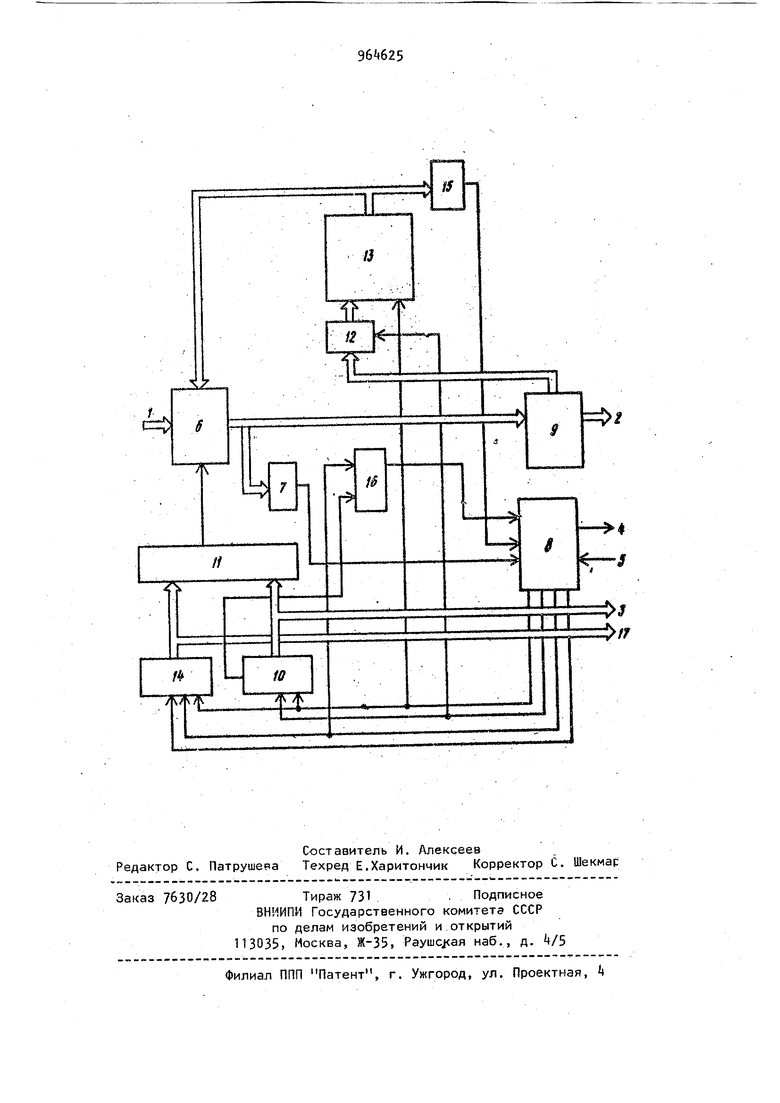

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах контроля и управления. Известны устройства для ввода информации, содержащие компараторы, чи по которых соответствует числу входных аналоговых сигналов, цифроаналоговый преобразователь, суммирующий счетчик и блок управления 1. Недостатком таких устройств является относительно невысокое быстроде ствие.. Наиболее близким по технической сущности к предлагаемому является густройство для ввода информации, со(держащее регистр, цифроаналоговый преобразователь, счетчик, формирователь сигналов приоритетного адреса, блок элементов И, элемент ИЛИ, блок микропрограммного управления и блок компараторов, первые, вторые, третий входы и выходы которого соединены соответственно с входными информационными шинами устройства, с выходами регистра, с выходом цифроаналогового преобразователя и с входами элемента ИЛИ, входы которого соединены с входами формирователя сигналов приоритетного адреса, первые выходы которого соединены с адресными выходами устройства, вторые выходы - с первыми входами блока элементов И, второй вход которого соединен с первым выходом блока микропрограммного управления и с первым входом счетчика, выход блока элементов И соединен с первыми входами регистра, второй вход которого соединен с вторым входом счетчика и с вторым выходом блока микропрограммного управления, первый вход которого подключен к выходу элемента ИЛИ, второй вход и выход - к управляющим входу и выходу устройства соответственно, а выходы счетчика соединены с первыми входами цифроаналогового преобразователя и с первыми 396 информационными выходами устройст,.ва 2 . Недостатком этого устройства явля ется ограниченное быстродействие в связи с тем, что в нем необходимо осуществлять полный перебор всех состояний цифроаналбгового преобразователя в каждом цикле преобразования. Цель изобретения - повышение быст родействия устройства. Указанная цель достигается тем, что в устройство для ввода информации, содержащее регистр, цифроаналоговый преобразователь, счетчик, формирователь сигналов приоритетного адреса, блок элементов И, элемент ИЛ блок мик|эопрограммного управления и блок компараторов, первый, второй и третий входы и выход которого соединены соответственно с входными инфор мационными шинами устройства, с выхо дом регистра, с выходом цифроаналогового преобразователя и с входом элемента ИЛИ, с входом формирователя сигналов приоритетного адреса, первый выход которого является адресным выходом устройства, второй выход соединен с первым входом блока элементов И, втброй вход которого соединен с первым выходом блока микропрограммного управления и с первым входом счетчика, выход блока элементов И со единен с первым входом регистра, вто рой вход которого соединен с вторым входом счетчика и с вторым выходом блока микропрограммного управления, первый вход которого подключен к выходу элемента ИЛИ, второй вход и выход которого являются управляющим входом и выходом устройства соответст венно, а выходы счетчика соединены с первым входом цифрраналогового преобразователя и является информационным выходом устройства, ввеДены элемент И, триггер и реверсивный счетчик, первый, второй и третий входы которого соединены соответствен но с вторым, третьим и четвертым выходами блока микропрограммного управления, а выход соединен с вторым входом цифроаналоговогр преобразователя и является вторым информационным выходом устройства, третий выход блока микропрограммного управления соединен с единичным входом триггера, нуле- , вой вход и выход которого соединены соответственно с вторым выходом счетчика и с вторым входом блока микропрограммного управления, третий вход соединен с выходом элемента И, входы которого подключены к выходам регистра. На чертеже изображена структурная схема устройства. Устройство содержит входные информационные шины 1, адресные, первые информационные, управляющие выходы и управляющий вход устройства 2-k и 5, блок компараторов 6, элемент ИЛИ 7, блок 8 микропрограммного управления, формирователь 9 сигналов приоритетного адреса, счетчик 10, цифроаналоговый преобразователь (ЦАП) 11, блок элементов И 12, регистр 13, реверсивный счетчик k, элемент И 15, триггер 1б, второй информационный выход 17 устройства. Устройство работает следующим образом. На суммирующий вход реверсивного счетчика lA, управляющего старшими разрядами ЦАП 11, блок 8 подает импульс. ЦАП 11 преобразует образовавшийся код в аналоговую величину, поступающую на вход компараторов 6, сравнивающих эту величину с аналоговыми величинами на входах 1. какая-либо и& входных .величин оканЛтся меньше, чем сигнал на выходе ЦАП 11, то соответствующий компаратор находится в единичном состоянии (исходное состояние компараторов нулевое, так как сигнал на выходе , ЦАП 11 равен нулю и оказывается меньше любого входного сигнала), а элемент ИЛИ выработает сигнал, поступающий в блок 8. В этом случае блок 8 формирует сигнал, поступающий на вычитающий вход реверсивного счетчика Ik и на единичный вход триггера 116. После этого блок 8 формирует последовательность импульсов, поступающих на суммирующий вход счетчика 10, управляющего младшими разрядами ЦАП 11. При появлении единичного сигнала на выходе элемента ИЛИ 7 блок 8 запрещает выдачу импульсов на вход счетчика 10 и формирует запрос на управляющем выходе k. Одновременно с этим формирователь 9 формирует на своих выходах позиционный и двоичный коды номера старшего по установленному приоритету компаратора из всех тех, которые находятся в данный момент в единичном состоянии. По сигналу на управляющем выходе k во внешнее устройство (на чертеже не показано) и по двоичному коду адреса на адресных выходах 2 осуществляется за пись кода результата преобразования, поступающего с выходов счетчиков 10 и 1 if на выходы 3, 17 устройства. По окончании этой операции блок 8 форми рует сигнал, который поступает на вх ды элементов И в блоке 12. Вторые входы элементов И соединены соответственно с выходами формирователя 9 на которых формируется позиционный код адреса входа аналоговых величин, для которого входная аналоговая величина равна аналоговой величине на выходе ЦАП 11. Поэтому при наличии сигнала на ка ком-либо из этих выходов блока формирования сигнала приоритетного адреса 9 происходит установка соответствующего триггера в регистре 13 в единичное состояние. В силу того, что сигнал с выходов триггеров регистра 13 поступает на запрещающий вход соответствующего компаратора в блоке 6, он принудительно устанавливается в нулевое состояние и удерживается в нем до окончания всего ци ла преобразования. , Если при этом единичный сигнал на выходе элемента ИЛИ 7 сохраняется .что указывает на наличие, единичного состояния еще одного или нескольких компараторов, то блок 8 вырабатывает очередной сигнал для выдачи информации во внешнее устройство. Такой процесс продолжается до тех пор, пока присутствует единичный сигнал на выходе элемента ИЛИ 7. Когда сигнал н выходе элемента ИЛИ 7 становится нулевым, то есть принудительно с помощью соответствующего триггера регистра 13 устанавливается в нулевое состояние после ний, из компараторов, сработавших в данном такте преобразования, блок 8 формирует дальнейшую последовательность импульсов, поступающих на суммирующий вход счетчика 10. После переполнения счетчика 10 на его выходе формируется сигнал, поступающий на нулевой вход триггера 1б и устанавливающий его соответственно в нулевое состояние. По сигналу триггера 16 блок 8 вновь формирует сигнал, поступающий . на суммирующий вход реверсивного счет чика 1. Если же после увеличения содержимого реверсивного счетчика сигнал на выходе элемента ИЛИ 7 оста95 6 нется в нулевом состоянии, блок В формирует еще один импульс, поступающий на суммирующий вход реверсивного счетчика 1. Так продолжается до тех пор, пока после очередного увеличения содержимого реверсивного счетчика 1 на выходе элементаИЛИ 7 появится единичный сигнал. При его появлении вновь выполняется последовательность описанных операций. Если учесть, что величины входных сигналов распределяются по диапазону изменения входных сигналов неравномерно, то отдельные участки диапазона, на которых не сработал ни один компаратор и соответственно сигнал на выходе элемента ИЛИ 7 имел нулевое - значение, можно проходить с дискретностью реверсивного счетчика i и тем самым существенно уменьшить среднее время цикла преобразования и повысить быстродействие устройства. Единичное состояние любого из триггеров.-регистра 13 сохраняется до конца цикла преобразования, что обет спечивает запоминание в конце каждого такта преобразования результатов преобразования только по тем входам 1, компараторы которых устанавливаются в единичное состояние в данном такте преобразования. Число триггеров в регистре 13 равно числу компараторов в блоке 6 и соответственно равно числу входных величин 1. При срабатывании соответствующего компаратора после окончания записи результата преобразования (кода, хранящегося в счетчиках Т и 10) по адресу, выработанному в блоке 9, каждый из триггеров в регистре П устанавливается в единичное состояние. Если все триггеры регистра 13 установлены в единичное состояние, о чем свидетельствует наличие единичного сигнала на выходе элемента И 15, то это говорит о том, что всевходные аналоговые сигналы уже преобт разованы в двоичный код и их двоичные эквиваленты хранятся в соответствующих ячейках.памяти во внешнем устройстве. В этом случае блок 8 заканчивает цикл преобразования и вырабатывает сигнал, устанавливающий счетчики 10 и 1,. а также регистр 13 в исходное состояние. Выработка этого сигнала может быть осуществлена и перед началом очередного цикла преобразования. В устройстве блок микропрограммно го управления 8 выполняет следующие функции: по сигналу на входе 5 формирует первый импульс, поступающий на суммирующий вход счетчика при наличии нулевых сигналов на выходе элемента ИЛИ 7 и на выходе триггера 16 формирует последующие импульсы, поступающие на суммирующий вход счетчика 14; при наличии единичного сигнала на выходе элемента ИЛИ 7 и нулевого сигнала на выходе триггера 16 формирует импульс, поступающий на вычитающий вход счетчика ТО, а также серию импульсов, поступающих на суммирующий вход счетчика 10 и на вход блока элементов И 12; при наличии единичного сигнала на выходе элемента И 15 формирует, импульс, сви детельствующий об окончании преобразования, который поступает одновременно на выход t и на входы установки в исходное состояние счетчиков 10 и 14, а также регистра 13. Блок 8 может быть реализован на основе микропроцессорного набора серии К5ВО по стандартным схемам управляющих вычислительных машин. Введение элемента И 15 также обе спечивает сокращение среднего времен цикла преобразования за счет более раннего окончания этого цикла при выполнении преобразования всех входных аТТалогоРых величин и соответственно повышает быстродействие устройства. Если обозначить разрядность кода результата преобразования (двоичного эквивалента входных аналоговых величин) fi, разрядность счетчика - т, разрядность реверсивного счетчика k, причем m+ k п, число квантов, образуемых реверсивным счетчиком, в котором должны считываться двоичные эквиваленты входных аналоговых величин d, число оставшихся квантов, образуемых реверсивным счетчиком пос ле того, как закончено преобразование всех входных аналоговых .величин (считаны все их двоичные эквиваленты) d, то выражение для кратности выигрыша во времени в предлагаемом преобразователе по сравнению с известным можно представить в виде F(t). d...d Выражение для получения выигрыша, представленного в единицах времени, приведено нише: T(. d. - 2 + 1 + di) dt где Т - время одного такта в преобразователе. Если принять, например, разряд|ность счетчика и реверсивного счетчи ка равной друг другу, то при входных аналоговых величинах, не превышающих значение, эквивалентное младшему разряду реверсивного счетчика (одному кванту) для 8-разрядного преобразователя, время одного цикла преобразования сокращается примерно в 14 раз л 8 -- 4-4 1-2 +1- - 1--14 Для 10-разрядного преобразователя время одного цикла в этом случае сокращается примерно в 30 раз W -7-V 1-1 -fi + r-i-so Если же, например, значения входных аналоговых величин располагаются таким образом, что их двоичные эквиваленты должны считываться в половине из всех квантов, образуемых реверсивным счетчиком, включая самый старший квант, то для 8-разрядного преобразователя время одного цикла преобразования сокращается примерно в 1,7 раза + B + fb-f Для 10-разрядного преобразователя время одного цикла в этом случае сокращается примерно в 1,8 раза :F(l)-- -fb- 32- /6 + 32- Таким образом, можно говорить об уменьшении среднего времени цикла преобразования-для системы, основаннр й на 8 (10)-разрядном преобразовав теле максимально в 14 (30) раз в заЬисимости от конкретности распределения уровней входных сигналов по диапазону, их изменения и внутри поддиапазонов, что подтверждает полезный эффект изобретения. Формула изобретения Устройство для ввода информации, содержащее регистр, цифроаналоговый 99б преобразователь, счетчик, формирователь сигналов приоритетного адреса, блок элементов И, элемент ИЛИ, блок микропрограммного управления и блок компараторов, первый, второй и третий входы и выход которого соединены соответственно с входными информацион ными шинами устройства, с выходом регистра, с выходом цифроаналогового преобразователя, с входом элемента ИЛИ, с входом формирователя сигналов приоритетного адреса, первый выход которого является адресным выходом устройства,, второй выход соединен с первым входом блока элементов И, вто рои вход которого соединен с первым выходом блока микропрограммного управления и с первым входом счетчика, выход блока элементов И соединен с первым входом регистра, второй вход которого соединен с вторым входом счетчика и вторым выходом блока микропрограммного управления, первый вход которого Подключен к выходу эле мента ИЛИ, второй вход и выход которого являются управляющим входом и выходом устройства соответственно, а выходы счетчика соединены с первым входом цифроаналогового преобразователя и является первым информацион5ным выходом устройства, отличающееся тем, что, с целью увеличения быстродействия устройства, в него введены элемент И, триггер и реверсивный счетчик, первый, второй и третий входы которого соединены соответственно с вторым, третьим и четвертым выходами блока микропрограм много управления, а выходы соединены с вторым входом цифроаналогового преобразователя и является вторым информационным выходом устройства, третий выход блока микропрограммного управления соединен с единичным входом триггера, нулевой вход и выход которого соединены соответственно с вторым выходом счетчика и с вторым входом блока микропрограммного управления, третий вход 1 оторого соединен с выходом элемента И, входы которого подключены к выходам регистра. Источники информации, принятые во внимание при экбпертмзе 1.Гитис Э. И. Преобразователи информации для электронных ц ифровых вы-, числительных устройств. 1975, с. /tZS. 2.Авторское свидетельство СССР №450157, кл. G Об F 3/05, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода аналоговой информации | 1985 |

|

SU1293734A1 |

| Устройство для ввода аналоговой информации | 1985 |

|

SU1260966A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Многоканальное устройство для ввода аналоговых данных | 1985 |

|

SU1273911A1 |

| Многоканальное устройство для ввода аналоговых данных | 1988 |

|

SU1501025A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2028730C1 |

| Способ измерения среднеквадратических значений переменных сигналов | 1990 |

|

SU1798705A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

Авторы

Даты

1982-10-07—Публикация

1981-03-09—Подача