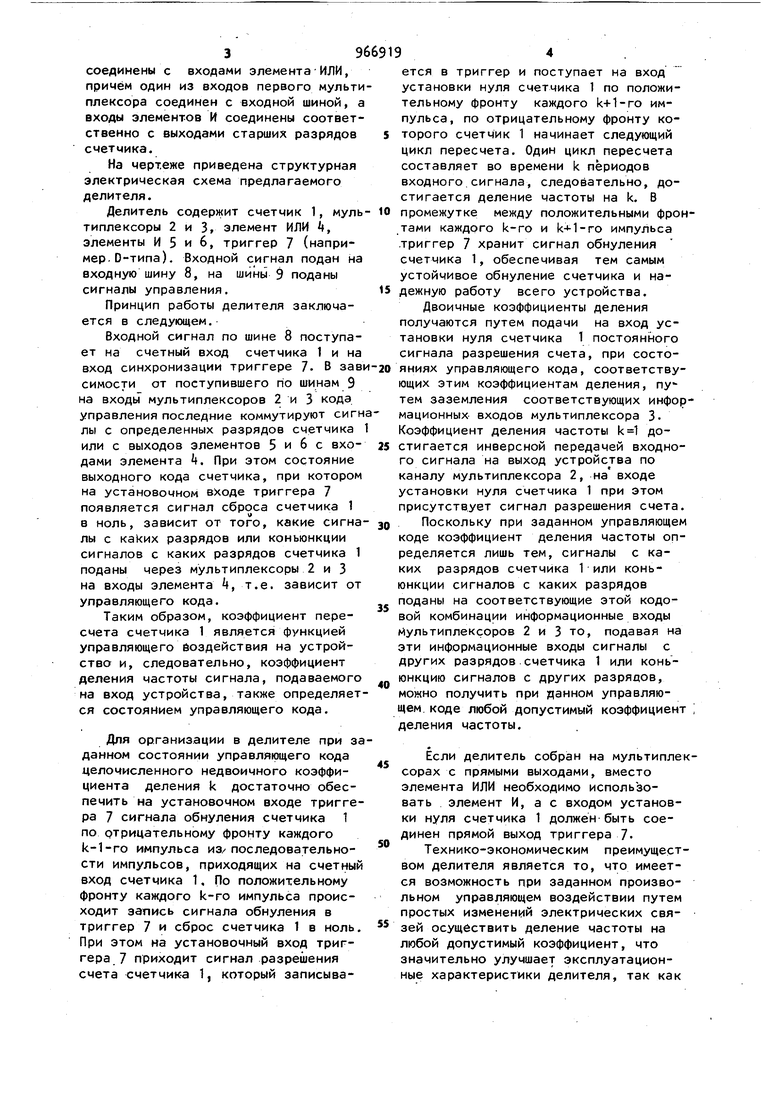

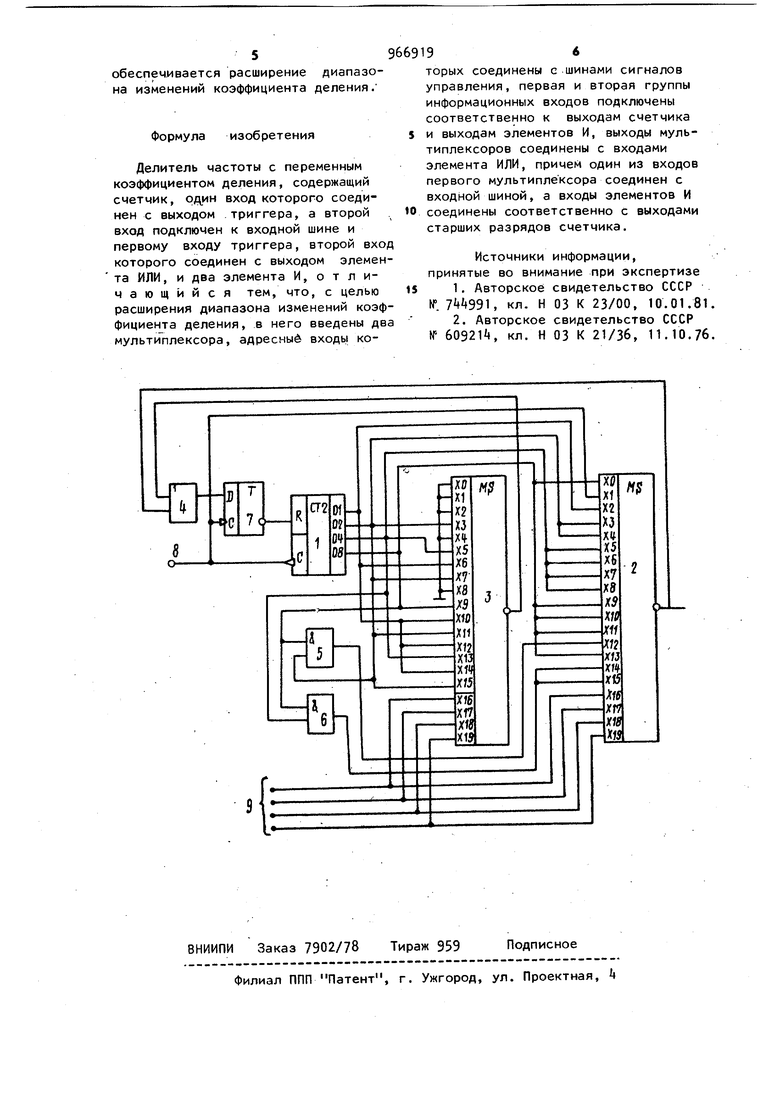

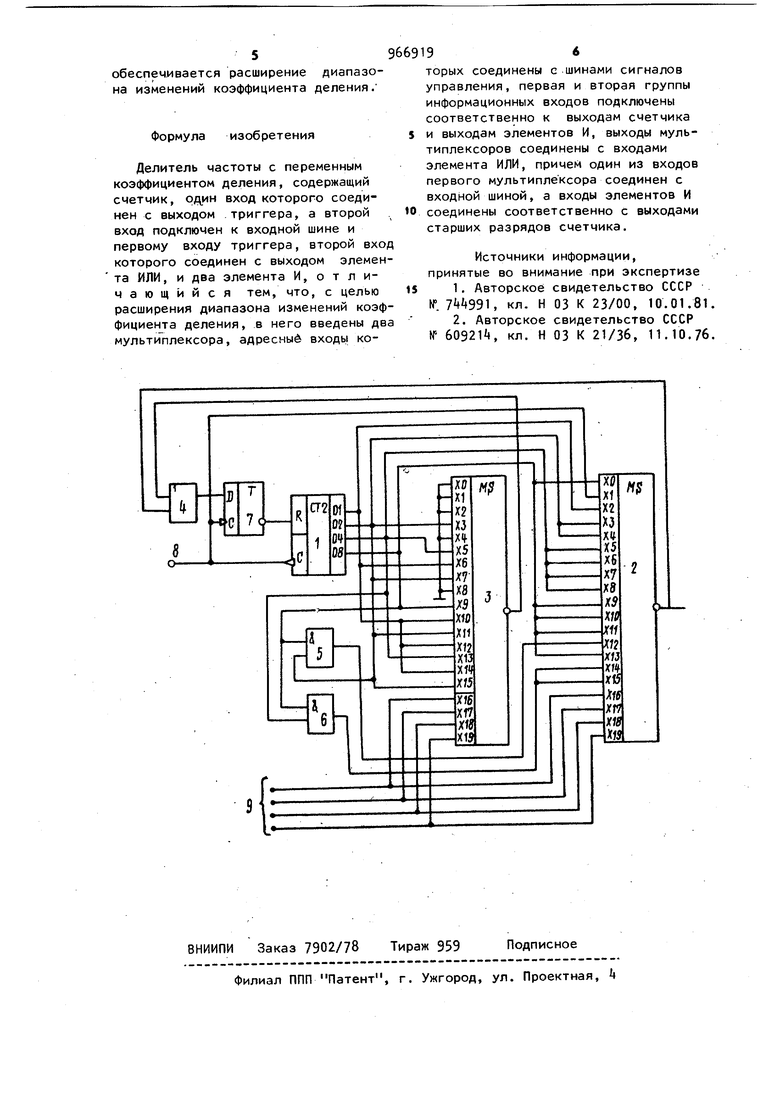

(5) ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ Изобретение относится к импульсной технике. Известен делитель частоты с переме ным коэффициентом деления, содержащий многоразрядное пересчетное устройство делитель, мультиплексор, регистр, информационный узел, содержащий регистр считывания, регистр коэффициента и формирователь Cl . Недостатком данного делителя являвтся его сложность. Наиболее близким по технической сущности к предлагаемому является делитель, содержащий двоичный счетчик на триггерах, выходы которых соединены с входами элементов И, другие входы которых подключены к шинам сигналов управления, а выходы соединены с элементом ИЛИ, выход которого через инвертор соединен с соответствующим входом счетчика, триггер, вход которого соединен с входом элемента ИЛИ, КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ а выход с одним из входов счетчи- : ка t2. Однако известный делитель не обладает достаточным диапазоном измене ния коэффициента деления. Целью изобретения является расширение диапазона изменений коэффициента деления. Поставленная цель достигается тем, что в делитель частоты с переменным коэффициентом деления, содержаший счетчик, один вход которого соединен с выходом триггера, а второй вход подключен к входной шине и первому входу триггера,второй вход которого соединен с выходом элемента ИЛИ, и два элемента И, введены два мультиплексора, адресные входы которых соединены с шинами сигналов управления , первая и вторая группы информационных входов подключены соответственно к выходам счетчика и выходам элементов И, выходы мультиплексоров 396 соединены с входами элемента ИЛИ, причём один из входов первого мультиплексора соединен с входной шиной, а входы элементов И соединены соответственно с выходами старших разрядов счетмика. На чертеже приведена структурная электрическая схема предлагаемого делителя. Делитель содержит счетчик 1, муль типлексоры 2 и 3, элемент ИЛИ Ц, элементы И 5 и 6, триггер 7 (например. D-типа). Входной сигнал подан на входную шину 8, на шйнь 9 поданы сигналы управления. Принцип работы делителя заключается в следующем. Входной сигнал по шине 8 поступает на счетный вход счетчика 1 и на вход синхронизации триггере 7. В зав симости от поступившего по шинам 9 на входьГ мультиплексоров 2 и 3 кода управления последние коммутируют сигн лы с определенных разрядов счетчика или с выходов элементов 5 и 6 с входами элемента . При этом состояние выходного кода счетчика, при котором на установочном входе триггера 7 появляется сигнал сброса счетчика 1 в ноль, зависит от того, какие сигна лы с каких разрядов или коньюнкции сигналов с каких разрядов счетчика 1 поданы через мультиплексоры 2 и 3 на входы элемента 4, т.е. зависит от управляющего кода. Таким образом, коэффициент пересчета счетчика 1 является функцией управляющего еоздействия на устройство и, следовательно, коэффициент деления частоты сигнала, подаваемого на вход устройства, также определяет ся состоянием управляющего кода. Для организации в делителе при за данном состоянии управляющего кода целочисленного недвоичного коэффициента деления k достаточно обеспечить на установочном входе триггера 7 сигнала обнуления счетчика 1 по отрицательному фронту каждого k-1-го импульса из/последовательности импульсов, приходящих на счетный вход счетчика 1. По положительному фронту каждого k-ro импульса происходит запись сигнала обнуления в триггер 7 и сброс счетчика 1 в ноль. При этом на установочный вход триггера 7 приходит сигнал разрешения счета счетчика 1, который записывается в триггер и поступает на вход установки нуля счетчика 1 по положительному фронту каждого k+1-го импульса, по отрицательному фронту которого счетчик 1 начинает следующий цикл пересчета. Один цикл пересчета составляет во времени k периодов входного,сигнала, следовательно, достигается деление частоты на k. В промежутке между положительными фронтеми каждого k-ro и k- -1-ro импульса триггер 7 хранит сигнал обнуления счетчика 1, обеспечивая тем самым устойчивое обнуление счетчика и надежную работу всего устройства. Двоичные коэффициенты деления получаются путем подачи на вход установки нуля счетчика 1 постоянного сигнала разрешения счета, при состояниях управляющего кода, соответствующих этим коэффициентам деления, путем заземления соответствующих информационных- входов мультиплексора 3. Коэффициент деления частоты достигается инверсной передачей входноГО сигнала на выход устройства по каналу мультиплексора 2, на входе установки нуля счетчика 1 при этом присутств,ует сигнал разрешения счета. Поскольку при заданном управляющем коде коэффициент деления частоты определяется лишь тем, сигналы с каких разрядов счетчика 1 или коньюнкции сигналов с каких разрядов поданы на соответствующие этой кодовой комбинации информационные входы Мультиплексоров 2 и 3 то, подавая на эти информационные входы сигналы с других разрядов счетчика 1 или коньюнкцию сигналов с других разрядов, можно получить при данном управляющем коде любой допустимый коэффициент , деления частоты. Если делитель собран на мультиплексорах с прямыми выходами, вместо элемента ИЛИ необходимо использовать элемент И, а с входом установки нуля счетчика 1 должен быть соединен прямой выход триггера 7. Технико-экономическим преимуществом делителя является то, что имеется возможность при заданном произвольном управляющем воздействии путем простых изменений электрических связей осуществить деление частоты на любой допустимый коэффициент, что значительно улучшает эксплуатационные характеристики делителя, так как обеспечивается расширение диапазона изменений коэффициента деления. Формула изобретения Делитель частоты с переменным коэффициентом деления, содержащий счетчик, один вход которого соединен с выходом триггера, а второй вход подключен к входной шине и первому входу триггера, второй вхо которого соединен с выходом элемен та ИЛИ, и два элемента И, отличающийся тем, что, с целью расширения диапазона изменений коэф фициен та деления, в него введены дв мультиплексора, адресные входц ко9торых соединены с шинами сигналов управления, первая и вторая группы информационных входов подключены соответственно к выходам счетчика и выходам элементов И, выходы мультиплексоров соединены с входами элемента ИЛИ, причем один из входов первого мультиплексора соединен с входной шиной, а входы элементов И соединены соответственно с выходами старших разрядов счетчика. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №. 7tt991, кл. Н 03 К 23/00, 10.01.81. 2. Авторское свидетельство СССР № 60921А, кл. Н 03 К 21/36, 11.10.76.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1986 |

|

SU1368993A1 |

| Многоканальное измерительное устройство | 1988 |

|

SU1617430A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2002 |

|

RU2218669C1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1661981A1 |

| Устройство для измерения отношения частот последовательностей импульсов | 1988 |

|

SU1599793A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1396277A1 |

| Управляемая линия задержки | 1990 |

|

SU1725370A2 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

Авторы

Даты

1982-10-15—Публикация

1981-03-05—Подача