ныи выход которого соединен с входом второго элемента И, выход третьего элемента И соединен с единичным входом второго триггера и входом первого элемента задержки, вторая группа информационных входов .устройства соединена с.входами соответствующих элементов ИЛИ второй груп пы и с соответствукйцими входами третьего элемента ИЛИ, выход которого соединен с вторым входом второго эл мента И, выход второго элемента И соединен с входом первого одновибратора и с входом синхронизации первого регистра, выход которого соединен с первым входоМ .блока сравнения, выход первого одновибратора соединен с управляющими входом блока сравнения и через второй элемент задержки с первыми входами третьего и четвертого элементов И, выход которого соединен с первым входом первого элемента ИЛИ и является первым управляющим выходом устройства, выход регистра адреса возврата соединен с . вторым входом блока сравнения, выход которого соединен с вторыми входами третьего и четвертого элементов И, выход регистра адреса соединен с информационным входом блока модификации адреса и первым информационным входом коммутатора, выход которого соединен с вторыми входами соответтвующих элементов И К групп, выходы регистра передачи управления соединены с соответствующими входами чеТ вертого элемента ИЛИ, выход которого соединен с вторым входом первого элемента ИЛИ, через второй одновибратор - с вервын управляющим входом коммутатора, через третий элементзадержки - с вторым управляющим и с инверсным входами коммутатора, и через четвертый элемент задержки - с нулевым входом регистра адреса передачи управления, третий информационный вход устройства соединен с входом первого шифратора и с третьим входом первого элемента ИЛИ, выход дешифратора соединен с входами второго Ш1 ратора, выходы которого соединены с вторым информационным входом коммутатора,

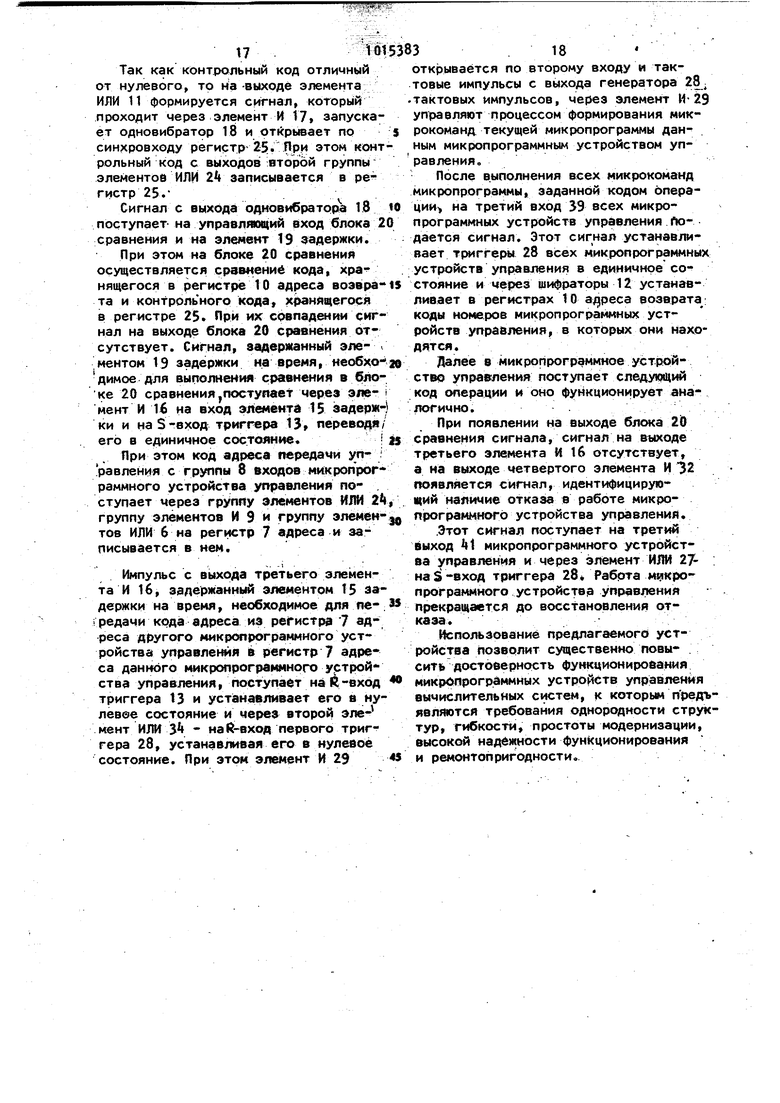

2. Устройство по п. 1, о т л и ч аю щ е е с я тем, что блок модифика- . ции адреса содержит группу элементов И, группу сумматоров по модулю два, причем, входы кода немодифицируёмой части, адреса первой группы входов блока соединены с соответствующими выходами группы выхрдов блока, входы кода модифицируемой части ад раса соединены с входами первой группь1 входов группы сумматоров по модуле два, выходы котррых соединены с выходами модифицируемой масти адреса группы выходов блока, входы .модифицируемой части адреса соединены с первыми входами элементов И группы, выходы которых соединены с вторыми входами сумматоров по модулю два группы, входы кодрё проверяемых условий соединены с В1ТОРЫМИ входами Элементов И группы.

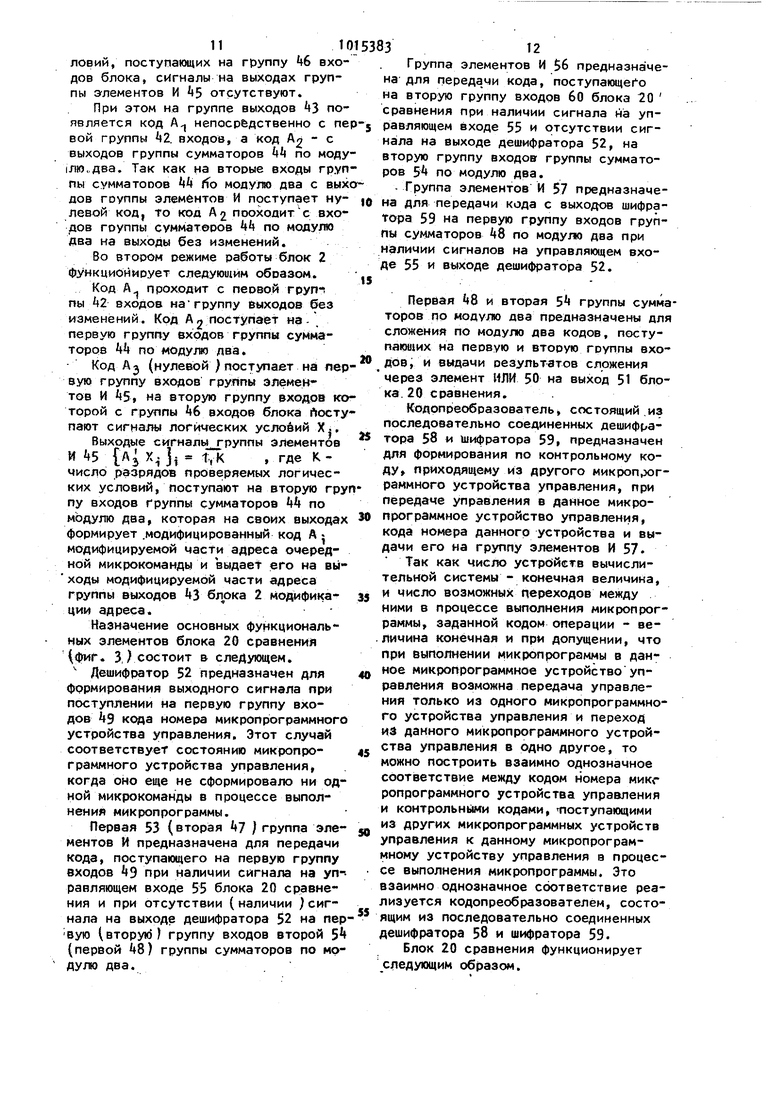

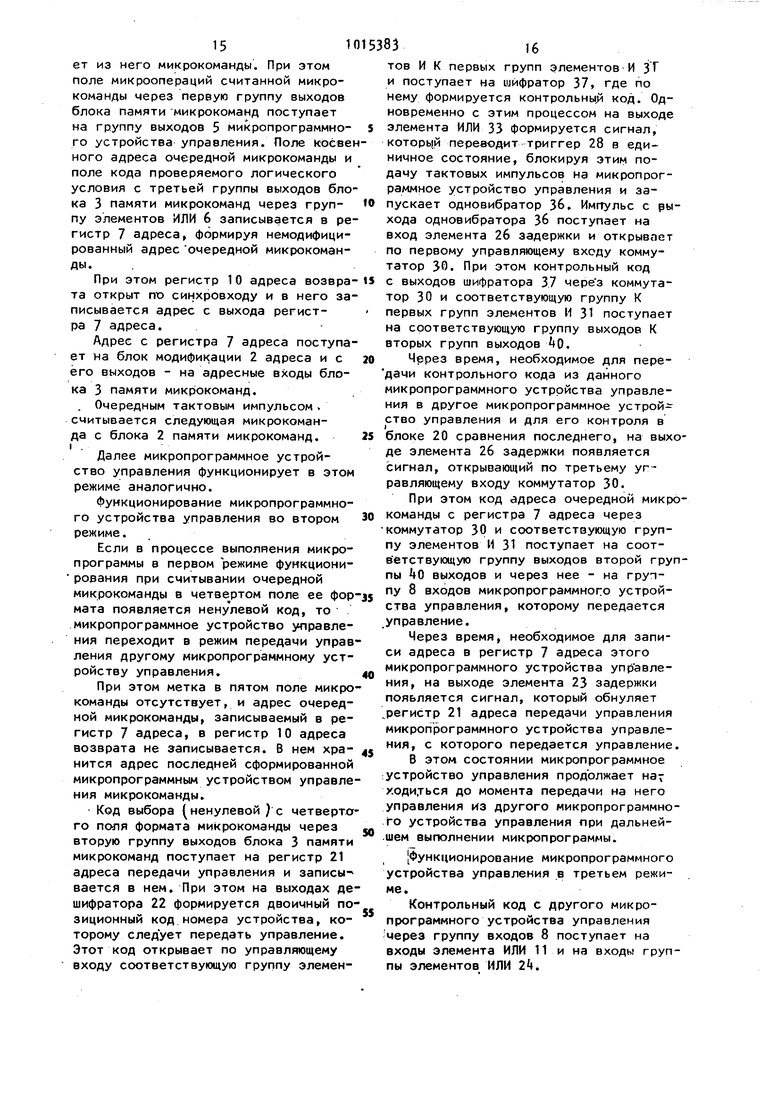

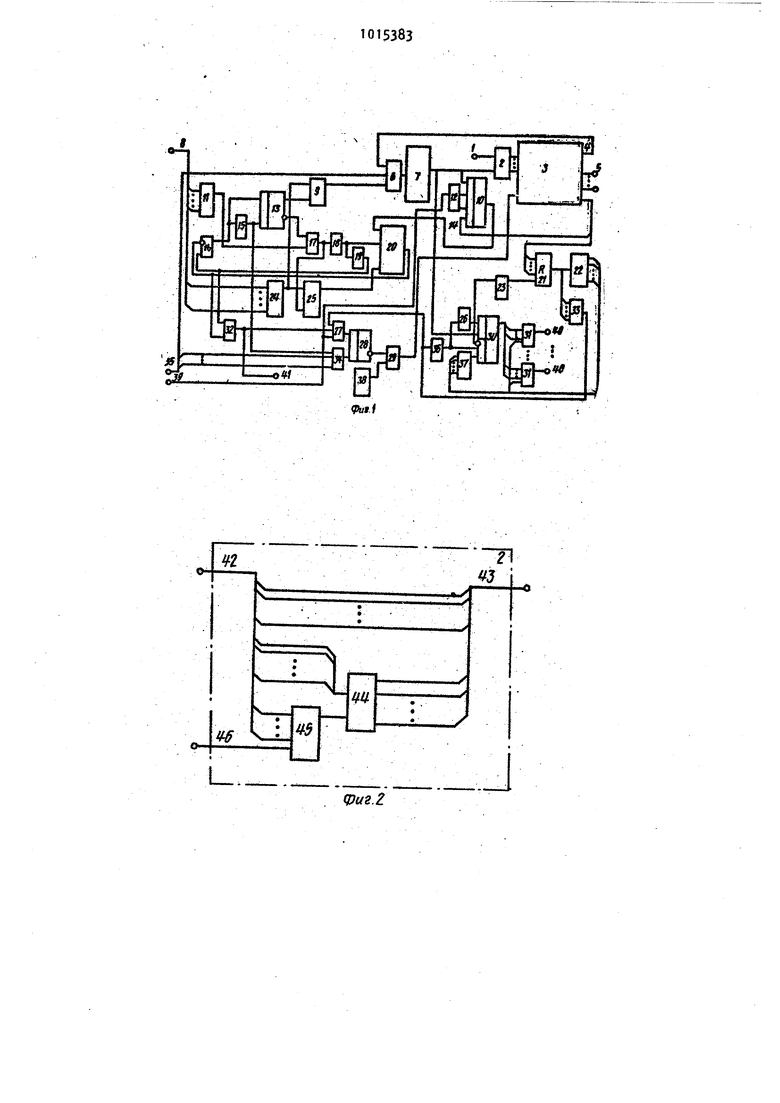

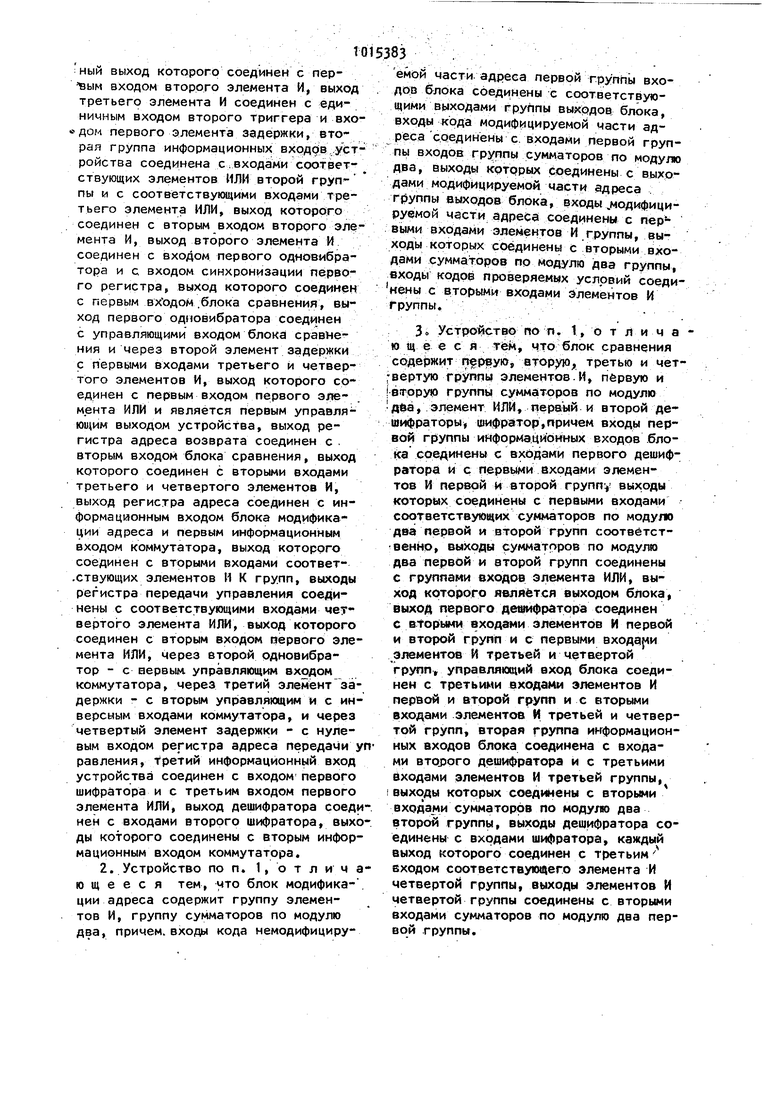

3 Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок сравнения соде|эжит , вторую третью и четвертую элементов.И, первую и вторую группы сумматоров по модулю , элемент ИЛИ, первой и второй дешифраторы, шифратор,примем входы первой группы ийформа.ционных входов .блока соединены с входами первого дешифратора и с первыми входами элементов И первой и второй группу выходы которых соединены с первыми входами соответствующих сумматоров по модулю два первой и второй групп соотвётст венно, выходы сумматоров по модулю два первой и второй групп соединены с группами входов элемента ИЛИ, выход которого является выходом блока, выход первого дешифратора соединен с BtopibiMM входами элементов И первой и второй групп и с первыми входами элементов И третьей и четвертой групп, управляющий вход блока соединен с третьи1 и входами элементов И первой и второй групп и с вторыми входами элементов И третьей и четвертой групп, вторая группа информационных входов блока соединена с входами BTOj3oro дешифратора и с третьими входами элементов И третьей группы, I выходы которых соединены с вторыми входами сумматоров по модулю два второй группы, выходы дешифратора соединены с входами шифратора, каждый выход которого соединен с третьим входом соответствую«вего элемента И четвертой группы, выходы элементов И четвертой группы соединены с вторыми входами сумматоров по модулю два первой группы. Изобретение относится к автоматике и вычислительнойтехнике и может быть использовано при проектировании цифровых вычислительных машин и систем с микропрограммным упрёвлением с высокой достоверностью функционирования. Известно устройство микропрограммного управления, содержащее арифметический блок, блоки памяти адресных микрокоманд и микроопераций, сче чик микрокоманд 11. Недостатками этого устройства являются отсутствие возможности переда чи управления, с одного микропрограммного устройства управления на другое и невозможность наращивания объема и количества микропрограмм. Наиболее близким к предлагаемому является микропрограммное устройство управления, содержащее регистр ад реса, регистр адреса возврата, регистр адреса передачи управления, К первых групп элементов И, блок памяти микрокоманд, первый элемент ИЛИ, генератор тактовых импульсов j дешифратор, первый и второй элементы И, причем группа выходов регистра адреса соединена с группой информационных входов регистра адреса возврата, первая группа выходов блока памяти микрокоманд - с первой группой выхо дов устройства, управляющий вход бло ка памяти микрокоманд подключен к вы ходу первого элемента И, первый вход которого соединен с выходом генератора тактовых импульсов, первый выход второй группы выходов блока памя ти микрокоманд соединен с входом син ронизации регистра адреса возврата,, а остальные выходы второй группы выходов - с информационными входами ре гистра адреса передачи управления, группа выходов которого соединена с входами дешифратора, каждый из.выходов которого подключен к управляющим входам. К первых групп элементов И .с ответственно, группы выходов кото-., рых соединены с вторыми(K+V) группами выходов устройства соответственно Структура вычислительной системы., в состав которой входит это микропро раммное устройство управления, состо ит из нескольких идентичных устройст В каждый отдельно взятый момент времени работает только одно устройство После выполнения всех микрокомандмикропрограммы этим устройством инициируется работа следующего устройства путем передачи его управления по фиксированному адресу 23. Существенным недостатком микропрограммных устройств управления этой вычислительной системы является низкая достоверность функционирования, обусловленная отсутствием контроля правильности передачи управления с одного устройства на другое. Этот недостаток сужает функциональные возможности микропрограммных устройств управления таких вычислительных систем, не позволяет обнаружить сбой в процессе выполнения микропрограммы, контролировать правильность перехода от одного стандартного устройства (БИС ) к другому, что . затрудняет поиск отказавшего элемента, снижает оперативность, обнаружения и устранения отказов, а следовательно, эффективность микропрограммного устройства управления и вычислительной системы в целом, нивелирует преимущества однородной вычислительной структуры. Цель изобретения - повышение достоверности функционирования микропрограммного устройства управления при выполнении микропрограмм большого объема. Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее регистр адреса, регистр адреса,передачи управления, К первых групп элементов И, блок памяти микрокоманд, первый элемент ИЛИ, дешифратор, первый и второй элементы И и генератор тактовых импульсов, причем группа выходов регистра адреса соединена с группой информационных входов регистра адреса возврата, управляющий вход блока памяти микрокоманд соединен с выходом первого элемента И, первый вход которого соединен с выходом генератора Тактовых импульсов, первый выход первой группы выходов блока памяти микрокоманд соединен с входом синхронизации регистра адресавозврата, а остальные выходы первой группы - с-информационными входами регистра адреса передачи управления, группа выходов которого соединена с входами дешифратора, каждый из К выходов которого соединен с управляющими входами соответствующих элементов И К первых групп, группы выходов которых образуют К групп выходов устройства, вторая группа выходов блока памяти микрокоманд является (К+1}-й группой выходов устройства, введены первый и второй триггеры, блок сравнения, первый регистр, третий и четвертый элемент И, второй, , третий и четвертый элементы ИЛИ, первая и вторая группы элементов ИЛИ первый, второй, третий и четвертый элементы задержки, вторая группа эле ментов И, первый и второй одновибраторы, коммутатор, первый и второй шифраторы, блок модификации адреса, причем выход первбго элемента ИЛИ соединен с единичным входом первого триггера, инверсный выход которого соединен с вторым входом первого эле мента И, выход первого элемента задержки соединен с нулевым входом/вто рого триггера и с первым входом -второго элемента ИШ, выход которого со единен с нулевым входом первого триг- гера, первая группа информационных входов устройства соединена с соот ветствующими входами второго элемента ИЛИ и,с первыми входами элемен тов ИЛИ первой группы, выходы которой соединены с информационными входами регистра адреса, третья группа выходов блока памяти микрокоманд и группа выходов элементов И второй группы соединены cooTBetcTBeHHo с вт рыми и третьими входами элементов ИЛ первой группы, выходы элементов ИЛИ второй группы соединены с информаци.онными входами элементов И второй группы и с группой информационных входов первого регистра, управляющие входы элементов И второй группы соединены с прямым выходом второго три гера , инверсный выход которого соеди нен с первым входом второго элемента И, выход третьего элемента И соединен с единичным входом второго триггера и входом первого элемента з держки, вторая группа .информационных Входов устройства соединена с входами соответствующих элементов ИЛИ вто рой группы и с соответствующими вход ми третьего элемента ИЛИ, выход которого соединен с вторым входом втррого элемента И, выход jToporo элеме та И соединен с вхо4о1 л первого одновибратора и с входом синхронизации первого регистра, выход которого соединен с первьм вяодом блока сравнения, выход первого одновибратора соединен с управляющим входом блока сравнения и. через второй элемент за|Дер хки с первыми входами третьего и четвертого элементов И, выход которого соединен с первым входом первого элемента ИЛИ и является первым управляющим выходом устройства, в.ыход регистра адреса возврата соединен с вторым входом блока сравнения, выход которого соединен с вторыми входами третьего и четвертого элементов И, выход регистра адреса соединен с информационным входом блока модификации адреса и первым информационным входом коммутатора, выход которого соединен с вторыми входами соответствукяцих элементов И К групп, выходы регистра передачи управления соединены с соответствующими входами .четвертого элемента ИЛИ, выход которого соединен с вторым входом первого элемента ИЛИ, через второй одновибратор - с первым управляющим входом Коммутатора, через третий элемент задержки - с вторым управля1ащим и с инверсным входами коммутатора, и через четвертый элемент задержки - с нулевым входом регистра адреса передачи управления , третий информационный вход устройства соединен с входом первого шифратора и с третьим входом первого элемента ИЛИ, выход дешифратора соединен с входами второго шифратора, выходы которого соединены с вторым информаццонным входом коммутатора. Блок модификации адреса содержит группу элементов И, Труппу сумматоров по модулю два, причем входы кода немодифицируемой части адреса первой группы входов блока соединены с соответствущими сгыхадами группы выходов блока, вкоды блока модифицируемой части адреса совдине м с входами первой группы входов группы сумматоров по модулю два, выходы которых соединены с выходами модифи14йруемой части Iадреса fpynnы выходов блока, входы модифицируемой части адреса соединены с первыми входами элементов И группы, выходы которых соединены с вторыми входами сумматоров по модулю два группы, входы кодов проверяемых ; условий сое инвйы с вторыми входами элементов И группы. Кроме того, блок сравнения содержит первую, вторую, третью и четвертую группы элементов И, первую и вторую группы суммато00в по модулю два, элемент ИЛИ, первый и второй дешифраторы, шифратор, причем входы первой группы информационных входов блока соединены с входами первого дериифратора и с первыми входами элементов И первой и второй групп, выходы которых соединены с первыми входами соответствующих сумматоров по модулю два первой и второй групп соответственно, выходы сумматоров по модулю два первой и второй групп соединены с группами входов элемента ИЛИ, выход которого является выходом блока, оыход первого дешифратора соединён с вторыми входами элементов И первой и второй групп и с первыми входами элементов И третьей четвертой групп, управляющий вход блока соединен с третьими входами элементов И первой и второй групп и с вторыми вхбдами элементов И третьей и четвертой групп, вторая группа информационных входов блока соединена с входами второго дешифратора и с третьими входами элементов И третьей группы, выходы которых соединены с вторыми входами сумматоров по модулю два второй групгты, выходы дешифратора соединены с входами шифратора, каждый выход которого соединен с третьим входон соответствующего элемента И четвертой группы, выходы элементов И четвертой группы со единены с вторыми входами сумматоров по модулю два первой группы. Сущность изобретения состоит в по вышении достоверности функционирования микропрограммного устройства управления путем организации контроля передачи управления по фиксированному адресу от одного микропрограммного устройства управлений к другому. На фиг. 1 приведена функциональная схема предлагаемого микропрограм много устройства управления; на фиг. функциональная схема блока модификации адреса; на фиг. 3 - функциональная схема блока :равнения. Устройство (фиг 1) содержит четвертую группу входов 1 устройства, , блок 2 модифика(ии адреса, блок 3 па мяти микрокоманд, третью группу выхо дов блока t, первую группу выходов. 5 устройства, первую группу элементов ИЛИ 6., регистр 7 адреса, вторую группу 8 входов устройства вторую группу элементов И 9f регистр 10 адреса возврата, третий элемент ИЛИ 11 второй шифратор 12, второй триггер 1 тактовый вход регистра 10, первый элемент 15 задержки, третийэлемент И 16, второй элемент И 17i первый одновибратор 18, четвертый элемент 1 задержки, блок 20 сравнения, регистр 21 адреса передачи управления, дешифратор 22, третий элемент 23 задержки, вторую группу элементов ИЛИ 2, перт вый регистр 25, второй элемент 26 задержки, первый элемент ИЛИ 27, первый триггер 28, первый элемент И 29, коммутатор 30, К первых групп элементов И 31 четвертый элемент И , четвертый элемент ИЛИ 33, второй элемент ИЛИ 3, первую группу входов 35 устройства, второй одновибратор Зб, первый шифратор 37 генератор 38 так- , товых импульсов, третий вход 39 устройства, К вторых групп kQ выходов , устройства,третий выход «I устройства. На фиг. 2 показаны первая группа 2 входов блока модификации адреса, группа выходов A3 блока модификации адреса, группа сумматоров 4 по моду/то два,, группа элементов И 45, вторая группа k6 входов блока модификации адреса. Устройство (фиг. 3 I содержит также .вторую группу элементов И f7, первую группу сумматоров 8 по модулю два, первую группу входов блока сравнения, элемент ИЛИ 50, выход 51 блока сравнения, первый .дешифратор 52, первую группу элементов И 53, вторую группу сумматоров 5 по модулю два, управляющий вход 55 блока сравнения, третью группу элементов И 56, четвертую группу элементов И 57, второй дешифратор 58| шифратор 59, вторую группу входов 60 блока сравнения. . Назначение основных функциональных элементов микропрограммноТо устройства управления (фиг. 1} состоит в следукяцем.. Блок 3 памяти.микрокоманд предназначен для хранения микрокоманд и их считывания по-адресу, поступающему с блока 2 модификации адреса. При наличии сигнала на .управляющем вхр- . де с выхода первого элемента И 29. микрокоманд состоит из пяти полей. Первое поле -. поле кода косвенного адреса очередной микрокоманды, второе - поле кода проверяемого логического условия; третье - поле микроопераций, четвертое - поле кода efai6opa микропрограммного устройства управления, которому необходимо передать управление; пятое поле - метка управления записью информации в регистр 10. Первое и второе поля,формата микрокоманды при ее считывании поступают через третью группу выходов блока 3 памяти микрокоманд .на. вторую группу первой группы элементов ИЛИ 6 третье поле через первую группу выходов поступает на группу выходов 5 устройства, четвертое и пятое поля через вторую группу выходов поступают на информационные входы регистра 21 адреса передачи управления и на синхровход регистра 1 О адреса возврата соответственно. Регистр 7 адреса предназначен для формирования адреса очередной микрокоманды,. Регистр 10 адреса возврата предназначен для хранения кода адреса по след(;1ей выполненной микропрограммным .устройством управления микрокоманды а в нерабочем положении устройства для хранения кода номера этого устройства и выдачи этих кодов на nep вую группу входов блока, 20 сравнения Регистр 21 адреса передачи уоравления предназначен для хранемия кода выбора, считываемого из четвертого поля микрокоманды ( кода номера того микропрограммного устройства управле ния, которому нужно передать управление )и вмдачи его на входы дешиф ратора 22. Дешифратор 22 предназначен для фо мированияПО коду с выхода регистра 21 адреса передачи управления дво . йчного позиционного кода номера микропрограммного устройства управления к которому следует передать управление, и открытия этим сигналом по управляющему входу одной из К первых групп элементов И 31. Шифратор 37 предназначен для формирования по двоичному позиционному коду с выхода дешифратора 22 контрольного кода и выдачи его на первую группу информационных входов коммута тора 30. Коммутатор 30 предназначен для ра дельной во времени передачи на L-ю вторую группу выходов kQ микропрогра 1МНОГО устройства управления сначала контрольного кода, а затем, с задерж кой на время проверки правильности п . редачи контрольного кода в блоке сра нения микропрограммного устройства у равления, которому передается управление, кода адреса очередной микрокома нды Элемент ИЛИ 33, одновибратор 36, элемент 26 задержки предназначены дл формирования управляющих сигналов об печения временного разделения передачи крнтрольнрго кода и адреса очередной микрокоманды через коммутатор 30. Элемент 23 задержки предназначен для формирования сигнала обнуления регистра 21 после окончания передачи адреса из данного микропрограммного устройства управления в регистр 7 адреса другого микропрограммного устройства управления. Блок 20 сравнения предназначен для сравнения при передаче управления данному микропрограммному устройству управления контрольного кода и кода адреса последней, выполненной данным микропрограммным устройством управления j микрокоманды (или кода номера устройства при первом его включении в процессе выполнения микропрограммы )и выдачи выходного сигнала (в случае их несравнёния /на элементы И 16 и 32. Группа элементов ИЛИ 6 предназначена для записи в регистр 7 адреса koдй микрокоманды или с третьей группы выходов блока 3 памяти микрокоманд, или с первой группы входов 35 микропрограммного устройства управления, или с выходов группы элементов И 9. Группа элементов ИЛИ 2 предназначена для приема передаваемых на данное микропрограммное устройство управления кодов из одного из других устройств и выдачи их на регистр 25 и на группу элементов И 9. Регистр 25 предназначен для приема и хранения контрольного кода и выдачи его на вторую группу входов блока 20 сравнения. Элемент ИЛИ 11 предназначен для формирования сигнала. Идентифицирующего начало передачи адресной информации в данное микропрограммное устройство управления из других микропрограммных устройств управления. Триггер 13 предназначен для формирования управляющих сигналов, norf действием которых сначала (состояние триггера 13 нулевое) поступающий на микропрограммное устройство управления контрольный код записывается в регистр 25 и сравнивается в блоке 20 сравнения с кодом, записанным в регистре 10 адреса возврата, а затем, в случае отсутствия сигнала на выходе блока сравнения, что соответствует правильному переходу к данному устройству, адрес очередной микрокоманды через -открытую по управляющему входу 9 , 16 группу элементов И у (состояние триг гера 13 единичное )-и группу элементов ИЛИ 6 записывается в регистр Т адреса. Элемент И 17 предназначен для формирования сигнала запуска одн вибратора 18 и сигнала управляющего записью контрольного кода в регистр 2 Одньвибратор 18 предназначен для формирования управляющего сигнала 26 на блок 20 сравнения И: через элемент задержки 19 на элементы И 16, 32. Элемент И 16 и элемент 15 задержки управляют установкой 13 сначала. в единичное, а затем в нулевое состояние. Элемент И 32 предназначен для фор мирования сигнала ошибки, соответствующе го неправильному переходу « дан ному модулю, и выдачи его на третий выход 1 микропрогра1«чного устройства управления и элемент ИЛИл 27 - на вход триггера 28. Триггер 28 предназначен для формирования сигнала, запрещающего гюда |Чу тактовых импульсов на микррпрог|раммное устройство,управления либо пои ошибочном переходе к нему, либо ПРИ передаче управления с него на . другое мйк:ропрограммное устройство управления и для разрешения выдачи тактовых импульсов в остальных слу чаях. Элементы ИЛИ 27 .и 3 предназначены для формирования управляющих сигналов на 5- и R-входы триггера 28 со ответственно. Блок 2 модификации адреса пред- назначен для иодификации адреса следующей микрокоманды при проверке логических условий, поступающих на чет вертую группу входов 1 мик ропрограммного устройстве управления, К вторых выходов ЛО микропрограммного устройства управдеНия Iпредназначены для передачи контрольjHoro кода и адреса перехода из данjHoro микропрограммного устройства.уп равления в одно из остальных микропрограммных устройств управления. - . Группа входов 35 предназначена для приема на микропрограммное уст ройство управления кода операции и выдачи его на регистр 7 адреса и на элемент ИЛИ З. Группа вхбдов 8 предназначена для приема контрольных кодов и адресу передачи управления в данное микро-программное устройство управления из 3 одного из других микропрограммных устройство управления. Группа выходов 5 предназначена для выдачи формируемых микропрограммным устройством управления микрокоманд на другие устройства вычислительной системы (АСУ, ОЗУ, периферийные устройства и т.д. К Р1ифратор 12 предназначен для установки в р егистре tO адреса возврата кода номера микропрограммного устрой-i ства управления при поступлении сиг- . на/1а на его вход. . Назначение основных функциональных элементов блока 2 модификаиии адреса (Фиг. 2 ) состоит в следующем. Группа элементовИ kS предназначена для формирования результатов поовеоки логического условия по значениям логических сигна/юв, поступающих на группу аходов блока Л6 и значениям разрядов второго поля считанной адресной мик|Х)команды, поступа1М1(ей на первую группу А2 входов блока модификации адреса. Группа сумматоров Цk по модулю два предназначена для формирования по сигналам с группы элементов И Л5 и по коду модифицируемой части адреса очередной микрокоманды, к которой передается управление после проверки логических условий в точке ветвления микропрограммы. Блок 2 модификации адреса функционирует следующим образом. , На первую группу входов поступает адрес-очередной микрокоманды (А А АЗ Ь где Aij - поле постоянной части адреса; . А У поле кода модифицкруемой части адреса; . поле кода проверяемого логического условия в точках ветвления. Блок функционирует в зависимости ;оде якимого поля двух режимах в поле АЗ отсутствует информация (заИисан нулевой код )- первый режим; в поле АЗ записана информация (записан код, отличный от нуля I - второй режим. Первый режим соответствует работе микрсэтрограммного устройства управлен| 1Я на Линейных участках микропрограммы, а второй режим - в точках ветвлениямикропрог оаммы, В первом режиме работы независимо tor значений,сигналов и логических ус10ловий, поступающих на группу k6 входов блока, сигналы на выходах группы элементов И S отсутствуют. При этом на группе выходов 3 появляется код А непосредственно с ne вой группы 2. входов, а код АО - с выходов группы сумматоров по моду 1лю„два. Так как на вторые входы груп пы суммаTODOB ( fro модулю два с вых дов гоуппы элементов И поступает нулевой код, то код А2 пооходитс вхо,дов группы cvMMiaTepoB по модулю два на выходы без изменений. Во ВТОРОМ оежиме работы блок 2 функционирует следующим обоазом. Код А проходит с первой труппы 2 входов нагруппу выходов без изменений. Код А« поступает на. первую группу входов группы сумматорой по модулю два. Код АЗ (нулевой ) поступает на пер вую группу входов группы элементов И its, на вторую группу входов ко торой с группы входов блока Лосту пают сигналы логических услоёий Х/, Выходые сигналы руппы элементов И kS {А Х JI 1,К , где Кчисло разрядов проверяемых логических условий, поступают на вторую гру пу входов группы сумматоров W по модулю два, которая на своих выходах формирует .модифицированный код А модифицируемой масти адреса очередной микрокоманды и выдает его на выходы модифицируемой части адреса группы выходов 3 2 модификации адреса. Назначение основных функциональных элементов блока 20 сравнения фиг. 3,) состоит в следующем. Дешифратор 52 предназначен для формирования выходного сигнала при поступлении на первую группу входов 9 кода номера микропрограммного устройства управления. Этот случай соответствует состоянию микропрограммного устройства управления, когда оно еще не сформировало ни одной микрокоманды в процессе выполнения микропрограммы. Лервая 53 (вторая 7 ) группа элементов И предназначена для передами кода, поступающего на первую группу входов Э при наличии сигнала на управляющем входе 55 блока 20 сравнения и при отсутствии (наличии ) сигнала на выходе дешифратора 52 на пер вую 1 вторую группу входов второй 5 (первой tS) группы сумматоров по мр дулю два. 312 Группа элементов И 56 предназначена для передачи кода, поступающего на вторую группу входов 60 блока 20 сравнения при наличии сигнала на управляющем входе 55 и отсутствии сигнала на выходе дешифратора 52, на вторую группу входов группы сумматоров 5А по модулю два. - Группа элементов И 57 предназначена для передачи кода с выходов шифратора 59 на первую группу входов групы сумматоров А8 по модулю два при наличии сигналов на управляющем вхое 55 и выходе дешифратора 52. Первая и вторая 5 группы сумматоров по МОДУЛЮ два предназначены для сложения по модулю два кодов, поступающих на первую и вторую гоуппы входов, и оезупьтатов сложения через элемент ИЛИ 50 на выход 51 блока. 20 сравнения. Кодопреобразовательj состоящий.из последовательно соединенных дешифратора 58 и uit«i)paTopa 59, предназначен для формирования по контрольному коду приходящему из другого микропрограммного устройства управления, при передаче управления в данное микропрограммное устройство управления, кода номера данного устройства и выдачи его на группу элементов И 57. Так как число устройств вычислительной системы - конечная величина, и число возможных переходов между ними в процессе выполнения микропрограммы, заданной кодом операции - величина конечная и при допущении, что при выполнении микропрограммы в данное микропрограммное устройство управления возможна передача управления только из одного микропрограммного устройства управления и переход ИЗ данного микропрограммного устройства управления в одно другое, то можно построить взаимно однозначное соответствие между кодом номера микг ропрограммного устройства управления и контрольными кодами, поступающими из других микропрограммных устройств управления к данному микропрограммному устройству управления в процессе выполнения микропрограммы. Это взаимно однозначное соответствие реализуется кодопреобразователем, состоящим из последовательно соединенных дешифратора 58 и шифратора 53. Блок 20 сравнения функционирует следующим образом. На первую группу входов kS из регистра 1 О адреса возврата поступает код номера устройства микро программное устройство управления еще не формировало,микрокоманд |, либо код адреса последней, выполненной микропрограммным устройством управления микрокоманды. При передаче управления в данное микропрограммное устройство управлеНИН из другого микропрограммного уст ройства управления на втравляющем вх де 55 появляется управляощий сигнал и на группе входов 60 - контрольный код. Если данное микропрограммное yc ройство упрабления включается в формирование микрокоманд первый раз е т чение выполнения микропрограммы (в регистре 10 адреса возврата записан код его номера), то на выходе дешифратора 52 формируется выходной сигнал. При этом по управляющим входам ; oтkp|Ывaютcя группы элементов И kj 57. При этой на первую группу входов группы сумматоров 8 по модулю два через группу элементов И 7 поступает код номера устройства, а на 1бтб рую Группу входов через группу элементов И 57 поступает код с выходов шифратора 9. Если эти коды равны (что соответствует правильной передаче управлени на данное микропрог{1 мМное устройство управления ), то сигнал на выходе группы сумматоров iS по модулю два,а следовательно, и на выхйда ; блока 2Q сравнения отсутствует , . В случае их нёсравнения (что соответствует неправильной передаче уп равления на выходах группы сумматороё Л8 по модулю Два ) появляется ненулевой код и э юменто« ЛШ 50 на выход 51 блока 20 сравнения Формируется сигнал ошибки. Если данное М1« |хэпрогра(«««ное устройство управления ак/ючается в формирование операционных микрокоманд второй t-и раз, то в регистре 10 адреса возврата хранится код адреса последней микроксзмёнды, сформирован ной. процессе выполнения микрог программы. При этом дешк ратор 52 не настроен на этот код и на его выходе сигнал отсутствует.При поступлении сигнала на управляющий вход 55 и контрольного кода на группу входов бб, вторая 7 и четвертая 57 группы элементов и закрыты, а первая 53.и третья 56 группы элементов И открыты по управляющим входём. При этом контрольный код через вторую группу входов 60, группу элементов И 56 поступает на вторые входы группы сумматоров 5 по модулю два, на первые входы которой с выходов группы элементов И 53 пает код адреса последней микрокоманды, исполненный устройством. Если эти коды равны, что соответствует правильной передаче управления, то на выходе группы сумматоров 5 пЬ . . модут два и на выходе 51 блока 20 сравнения сигнал отсутствует. В проивном выходе 51 блока 20 сравнения формируется сигнал, идентифицирующий неправильный переход к данному микропрограммному устройству управления. Предлагаемое микропрограммное устройство управления функционирует в ; трех режимах. Режим формирования . микрокоманд микпропрограммным устройством управления без передачи управления к другому мик ропрограммному устройству управления. Режим передами управления другоку микропрограммному устройству управления.. Режим приема управления из другого микропрограммного устройства управления. Функционирование в первом режиме. Сигналом начальной установки (не показан ) все элементы памяти Микропрограммного устройства управления устанавливаются в нулевое состояние. Сигналом с-входа 39 триггер 28 устанавливается в единичное состояние,, а в регистр. 10 через шифратор 12 записывается код номера данного микропрограммного уст136йства упг равления Код операции поступает через группу входов 35 микропрограммного устт ройства управления и группу Элементов ИЛИ 6 в регистр 7 адреса и запи- сывается в нем. Одновременно код адреса поступает через элемент ИЛИ 3 Haft-вход триггера 28 и устанавливает его а нулевое состояние. При этом, тактовый иш1ульс с выхода.генератора 38 через элементы И 29 поступает на управлякхций вход блока 3 памяти . микрокома и по адресу, поступающему на его адресные входы с выходов блока 2 модификации адреса, считыва-,. ет из него микрокоманды. При этом поле микроопераций считанной микрокоманды через первую группу выходов блока памяти микрокоманд поступает на группу выходов 5 микропрограммного устройства управления. Поле косвен ного адреса очередной микрокоманды и поле кода проверяемого логического условия с третьей группы выходов блока 3 памяти микрокоманд через группу элементов ИЛИ 6 записывается в регистр 7 адреса, формируя немодифицированный адрес очередной микрокоманды. При этом регистр 10 адреса возвра- ts с та открыт по синхровходу и в него записывается адрес с выхода регистра 7 адреса. Адрес с регистра 7 адреса поступает на блок модификации 2 адреса и с его выходов - на адресные входы блока 3 памяти микрокоманд. Очередным тактовым импульсом . считывается следующая микрокоманда с блока 2 памяти микрокоманд. Далее микропрограммное устройство управления функционирует в этом режиме аналогично. Функционирование микропрограммного устройства управления во втором режиме. Если в процессе выполнения микропрограммы в первом режиме функционирования при считывании очередной микрокоманды в четве ртом поле ее фор мата появляется ненулевой код, то микропрограммное устройство управления переходит в режим передачи управ ления другому микропрограммному устройству управления, При этом метка в пятом поле микро команды отсутствует, и адрес очередной микрокоманды, записываемый в регистр 7 адреса, в регистр 10 адреса возврата не записывается. В нем хранится адрес последней сформированной микропрограммным устройством управле ния микрокоманды. Код выбора ненулевой с четверто го поля формата микрокоманды через вторую группу выходов блока 3 памяти микрокоманд поступает на регистр 21 адреса передачи управления и записывается в нем. При этом на выходах де шифратора 22 формируется двоичный по зиционный код номера устройства, которому следует передать управление. Этот код открывает по управляющему входу соответствующую группу элемен10316 тов и К первых групп элементов И ЗТ и поступает на шифратор 37, где по нему формируется контрольны код. Одновременно с этим процессом на выходе элемента ИЛИ 33 формируется сигнал, которой переводит триггер 28 в единичное состояние, блокируя этим подачу тактовых импульсов на микропрограммное устройство управления и запускает одновибратор 36. Имггульс с рыхода одновибратора Зб поступает на вход элемента 26 задержки и открывает по первому управляющему входу коммутатор 30. При этом контрольный код выходов шифратора 37 через коммутатор 30 и соответствующую группу К первых групп элементов И 31 поступает на соответствующую группу выходов К вторых групп выходов tO. Через время, необходимое для передачи контрольного кода из данного микропрограммного устройства управления в другое микропрограммное устройство управления и для его контроля в блоке 20 сравнения последнего, на выходе элемента 26 задержки появляется сигнал, открывающий по третьему управляющему входу коммутатор 30. При этом код адреса очередной микрокоманды с регистра 7 адреса через коммутатор 30 и соответствующую группу элементов И 31 поступает на соответствующую группу выходов второй группы 0 выходов и через нее - на группу 8 входов микропрограммного устройства управления, которому передается управление. Через время, необходимое для записи адреса в регистр 7 адреса этого микропрограммного устройства управления, на выходе элемента 23 задержки появляется сигнал, который обнуляет ,регистр 21 адреса передачи управления микропрограммного устройства управления, с которого передается управление. В этом состоянии микропрограммное :устройство управления продолжает иаходи.ться до момента передачи на него управления из другого микропрограммного устройства управления при дальней.шем выполнении микропрограммы. Функционирование микропрограммного устройства управления в третьем режи- . Контрольный код с другого микропрограммного устройства управления через группу входов 8 поступает на входы элемента ИЛИ 11 и на входы группы элементов ИЛИ 2.

Так как контрольный код отличный от нулевого, то на -выходе элемента ИЛИ 11 формируется сигнал, который проходит через элемент И 17 запускает одновибратор 18 и открывает по 5 синхровходу регистр- 25. При этом контрольный код с выходов второй группы элементов или 24 записывается в регистр 25.

Сигнал с выхода одновибраторё 18 to поступает на управл яощий вход блока 20 сравнения и на элемент 19 задержки.

При этом на блоке 20 сравнения осуществляется срзанениё кода, хранящегося в регистре 10 адреса воэвра 1$ та и контрольного кода, хранящегос я в регистре 25. При их совпадении сWнал на выходе блока 20 сравнения отсутствует. Сигнал, задержанный элементом 13 задержки на время, необхо- О димое для выполнения сравнения в блоке 20 сравнения,поступает через эяг- i мент И 1 на вход эл ементд 15 задерж-) ки и на S-вход триггера 13, переводя/ его в единичное состояние. 25

При этом код адреса передачи уп- ; равления с группы 8 входов минропрограммного устройства управления по- . ступает через группу элементов ИЛИ 2, группу элементов И 9 и группу элемен-з тов ИЛИ б на регистр 7 адреса и записывается в нем.

Импульс с выхода третьего элемента И 16, задержанный элементом 15 задержки на время, необходимое для ое- 3 гредачи кода адреса из регистра 7 адреса другого микропрограммного устройства управления в регистр 7 адреса данного микропрограммного устройства управления, поступает на R-вход триггера 13 и уст;анавливает его в нулевее состояние и через второй эле- мент ИЛИ 3 - наК-вход первого триггера 28, устанавливая его в нулевое состояние. При этом элемент И 29

открывается по второму входу и тактовые импульсы с выхода генератора 28 .тактовых импульсов, через элемент И-2 управляют процессом формирования микрокоманд текущей микропрограммы данным микропрограммным устройством управления.

После выполнения всех микрокоманд микропрограммы, заданной кодом операции на третий вход 39 всех микропрограммных устройств управления fioдается сигнал. Этот сигнал устанавливает Т(1ггеры 28 всех микропрограммных устройств управления в единичное состояние и через шифраторы 12 устанавливает в регистрах 10 адреса возврата коды но14е.ров микропрограммных устройств управления, в которых они нахо дятся.

Далее в микропрограммное устройство управления поступает следлжнций код операции и оно функционирует анатгично.

При появлении на выходе блсжа 20 сравнения сигнала, сигнал на вшсоде третьего элемента И 16 отсутствует, а на выходе четвертого элемента И 32 появляется сигнал, идент1 ицирующий наличие отказа в работе микропрограммного устройства управления,

.Этот сигнал поступает на трет выход 41 микропрограммного устройства управления и через элемент ИЛИ 27на S-вход триггера 28 Работа MijiKpoпрограммного устройств)а управления прекращается до восстановления отказа.

Ifc:пользование предлагаемого устройства Позволит существенно повысить достоверность функционирования микропрограммных устройств управления вычислительных систем, к которьм предявл{М)Тся требования однородности , гибкости, простоты модернизации, высокой надежности функционирования и ремонтопригодности,.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1981 |

|

SU968813A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1015384A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1983 |

|

SU1108447A1 |

| Процессор с динамическим микро-пРОгРАММНыМ упРАВлЕНиЕМ | 1979 |

|

SU849223A1 |

(J}U2.Z

Г

49

53

W

«7

«tf

EH

57

59

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР If , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельства СССР If , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-30—Публикация

1981-12-05—Подача