со

00 О5

о 4

Изобретение относится к вычислительной технике и может быть использовано для выявления ненсправных микросхем постоянной памяти,

Цель изобретения - упрощение устройства.

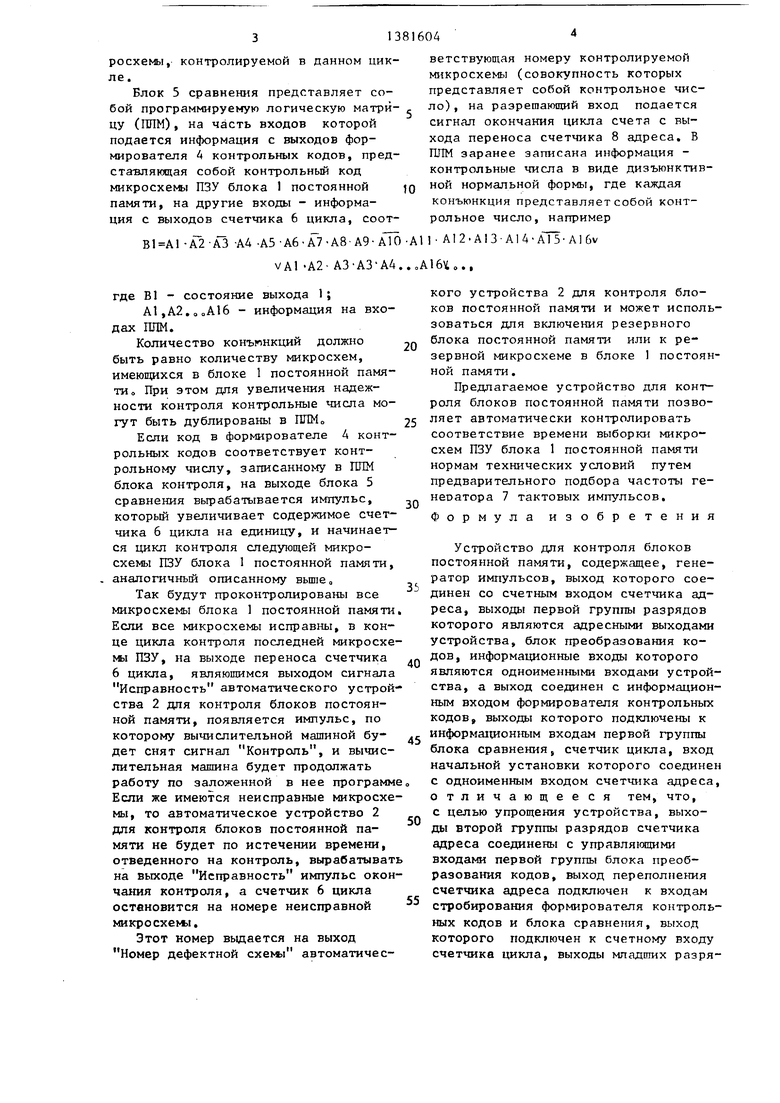

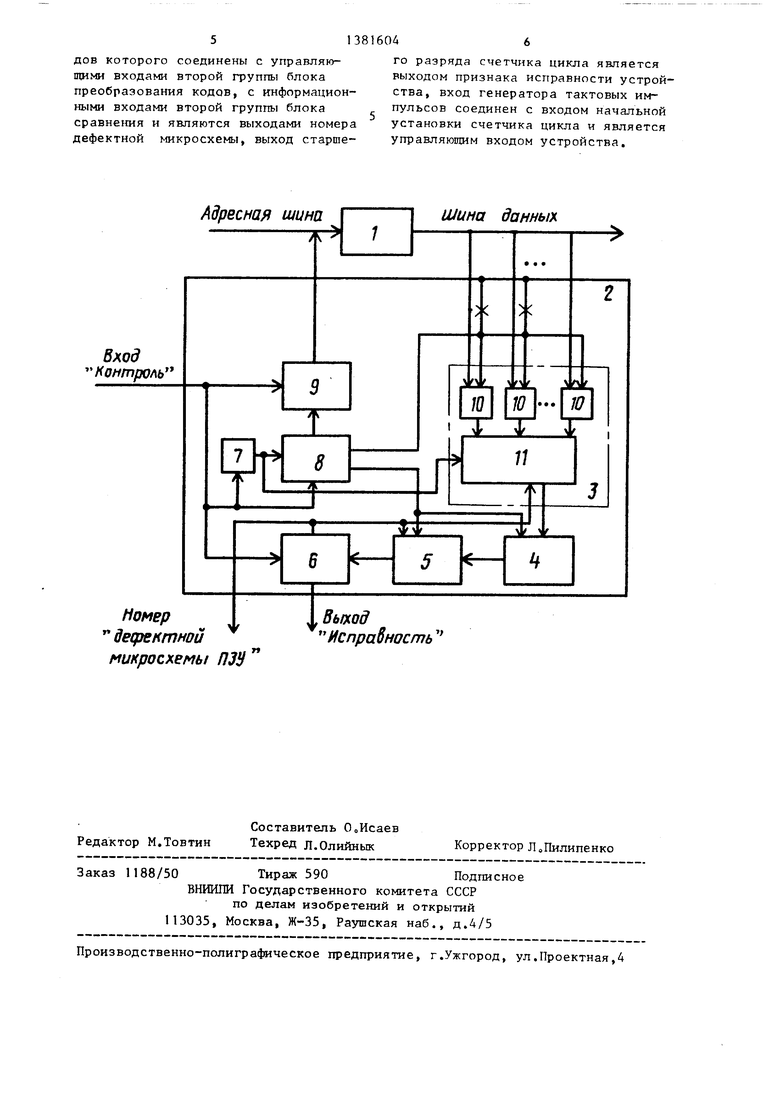

На чертеже показана схема устройства.

Устройство содержит контролиру- емый блок 1 постоянной памяти и устройство 2 для контроля блоков постоянной памяти, содержащее блок 3 преобразования кодов, формирователь 4 контрольных кодов, блок 5 сравне- ния, счетчик 6 цикла, генератор 7 тактовых импульсов, счетчик 8 адреса, буферный блок 9, первичный мультиплексор 10 данных, вторичный мультиплексор 11 данных

Устройство для контроля блоков постоянной памяти функционирует следующим образом.

На управляющий вход буферного блока 9, вход запуска генератора 7 тактовых импульсов, вход обнуления счетчика 8 адреса и вход установки нчального положения счетчика-6 цикла поступает сигнал Контроль, вырабатываемый вычислительной малшнор (не показана ) во время, отведенное программой для автоматического контроля (например, в начале работы при включении питания)„ При этом буферный блок 9 подключает группу стар- ших разрядов счетчика В адреса к адресной шине контролируемого блока 1 постоянной памяти, причем количество этих разрядов совпадает с разрядностью адресной шины; генера- тор 7 тактовых импульсов начинает вьфабатывать синхроимпульсы, которые поступают на счетный вход счетчика 8 адреса, установленный сигналом Контроль в начальное положение; уста- навливается в начальное положение счетчик 6 цикла. Группа младших разрядов счетчика 8 адреса поступает на управляющие входы первичных мультиплексоров 10 данных блока 3 преобразования кодов. На информационные входы этих мультиплексоров 10 поступает информация с шины данньпс контролируемого блока 1, считываемая по адресам, поступающим из автоматичес- кого устройства 2 контроля на адресную шину. Причем входы каждого первичного мультиплексора 10 данных подключены к шине данных блока 1

с

5 0

5 0с 0 5

0

постоянной памяти таким образом, чтобы все выходы каждой микросхемы ПЗУ из имеющихся в блоке 1 постоянной памяти были соединены с входами только одного из этих мультиппексо-. ров 10,

Далее устройство 3 преобразования кодов преобразует информацию, считываемую из контролируемого блока 1 постоянной памяти и представленную в виде параллельного кода - многоразрядного двоичного числа - в последовательный код, поочередно выдавая на свой выход все разряды этого числа.

Преобразование осуществляется следующим образом. В одном цикле происходит считывание информации по всем адресам со всех ячеек памяти микросхем блока 1 постоянной памяти, первичные мультиплексоры 10 данных представляют ее для каждой микросхемы в последовательном коде, а вторичный мультиплексор 1 1 данньтх про- пускает на выход блока 3 преобразования кодов в одном цикле информацию только из одной микросхемы блока 1 постоянной памяти, которая затем поступает в формирователь 4 контрольных кодов, где происходит обработка этой информации, заключающаяся, например, в подсчете битов, несущих информацию. В зависимости от типа микросхем, использованных в блоке 1 постоянной памяти, это могут быть О или Г о

Для исключения возможности потери таких битов вторичный мультиплексор 11 данных стробируется синхроимпульсом генератора 7 тактовых импульсов

С выходов формирователя 4 контрольных кодов двоичное число, полученное при подсчете битов последовательного кода, несущих информацию (контрольный код микросхемы), поступает на часть входов блока 5 сравнения, а формирователь 4 контроль ных кtoдoв обнуляется импульсом переноса с выхода переноса счетчика 8 адреса, который вырабатывается после перебора этим счет чиком 8 всех адресов. Этим же импульсом, поступающим на вход разрешения блока 5 сравнения разрешается работа этого блока. На другие входы блока 5 сравнения приходит сигнал с выхода счетчика 6 цикла, который определяет номер микросхемы, контролируемой в данном цикле.

Блок 5 сравнения представляет советствующая номеру контролируемой микросхемы (совокупность которых представляет собой контрольное чис

бой программируемую логическую матрй- , ло), на разрешающий вход подается

цу (ППМ), на часть входов которой подается информация с выходов формирователя 4 контрольных кодов, представляющая собой контрольный код микросхемы ПЗУ блока I постоянной памяти, на другие входы - информа10

сигнал окончания цикла счета с выхода переноса счетчика 8 адреса. В ПЛМ заранее записана информация - контрольные числа в виде дизъюнкти ной нормальной формы, где каждая конъюнкция представляет собой контрольное число, например

сигнал окончания цикла хода переноса счетчика ПЛМ заранее записана и контрольные числа в ви ной нормальной формы, конъюнкция представляе рольное число, наприме

ция с выходов счетчика 6 цикла, соотВ1 А1-А2-АЗ -АД .А5-А6 АГ7-А8-А9-АТЬ-А11- А1 2 А 3-А1 А 6v VAl А2- A3-A3 AA..oAl6lio.,

ветствующая номеру контролируемой микросхемы (совокупность которых представляет собой контрольное чис

сигнал окончания цикла счета с выхода переноса счетчика 8 адреса. В ПЛМ заранее записана информация - контрольные числа в виде дизъюнктивной нормальной формы, где каждая конъюнкция представляет собой контрольное число, например

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программирования микросхем памяти | 1986 |

|

SU1381592A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для обнаружения ошибок в блоке постоянной памяти | 1984 |

|

SU1246141A1 |

| Программатор | 1986 |

|

SU1439677A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

Изобретение относится к вычислительной технике и может быть использовано для выявления неисправных микросхем постоянной памяти. Целью изобретения является упрощение устройства. Устройство содержит блок преобразования кодов, формирователь контрольных кодов, блок сравнения, счетчик цикла, генератор тактовых импульсов, счетчик адреса, буферный блок. В устройстве последовательно для каждой микросхемы памяти подсчитывается контрольньй код в виде количества хранимых единиц или нулей, который затем сравнивается с эталоном, хранимым в блоке сравнения, выполненном в виде программируемой логической матрицы. В случае несравнения на выходе устройства появляется номер дефектной микросхемы памяти. I ил о с:

где Bl - состояние выхода 1;

А1,А2.ооА16 - информация на входах ПЛМ.

Количество конъюнкций должно

быть равно количеству микросхем, имеющихся в блоке 1 постоянной памяти При этом дпя увеличения надежности контроля контрольные числа могут быть дублированы в ПЛМ„

Если код в формирователе А контрольных кодов соответствует контрольному числу, записанному в ПЛМ блока контроля, на выходе блока 5 сравнения вьфабатывается импульс, который увеличивает содержимое счетчика б цикла на единицу, и начинается цикл контроля следующей микросхемы ПЗУ блока 1 постоянной памяти, аналогичный описанному вьшш „

Так будут проконтролированы все микросхемы блока 1 постоянной памяти Если все микросхемы исправны, в конце цикла контроля последней микросхемы ПЗУ, на выходе переноса счетчика 6 цикла, являющимся выходом сигнала Исправность автоматического устройства 2 для контроля блоков постоянной памяти, появляется импульс, по которому вычислительной машиной будет снят сигнал Контроль, и вычислительная машина будет продолжать работу по заложенной в нее программ Если же имеются неисправные микросхемы, то автоматическое устройство 2 для контроля блоков постоянной памяти не будет по истечении времени, отведенного на контроль, вырабатыват на выходе Исправность импульс окончания контроля, а счетчик 6 цикла остеновится на номере неисправной микросхем).

Этот номер выдается на выход Номер дефектной схеьы автоматичес

5

0

5

0

.Q

5

0

5

кого устройства 2 для контроля блоков постоянной памяти и может использоваться для включения резервного блока постоянной памяти или к резервной микросхеме в блоке 1 постоянной памяти.

Предлагаемое устройство для контроля блоков постоянной памяти позволяет автоматически контролировать соответствие времени выборки микросхем ПЗУ блока 1 постоянной памяти нормам технических условий путем предварительного подбора частоты ге- неоатора 7 тактовых импульсов.

Формула изобретения

Устройство для контроля блоков постоянной памяти, содержащее, генератор импульсов, выход которого соединен со счетным входом счетчика адреса, выходы первой группы разрядов которого являются адресными выходами устройства, блок преобразования кодов, информационные входы которого являются одноименными входами устройства, а выход соединен с информационным входом формирователя контрольных кодов, выходы которого подключены к информа1щонным входам первой группы блока сравнения, счетчик цикла, вход начальной установки которого соединен с одноименным входом счетчика адреса, отличающееся тем, что, с целью упрощения устройства, выходы второй группы разрядов счетчика адреса соединены с управлякмцими входами первой группы блока преобразования кодов, выход переполнения счетчика адреса подключен к входам стробирования формирователя контрольных кодов и блока сравнения, выход которого подключен к счетному входу счетчика цикла, выходы младших разрядов которого соединены с управляку- mjiNiH входами второй группы блока преобразования кодов, с информационными входами второй группы блока сравнения и являются выходами номера дефектной микросхемы, выход старшеАдресная шина

Вход Контроль

ПЗУ

t

Выход Испрабность

го разряда счетчика цикла является выходом признака исправности устройства, вход генератора тактовых импульсов соединен с входом начальной установки счетчика цикла и является управляюшлм входом устройства.

Шина данных

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1080218A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-03-15—Публикация

1985-12-27—Подача