13

Изобретение относится к вычислительной технике и может быть использовано в программаторах постоянных зйпоминающих устройств,

Цель изобретения - увеличение выхода годных микросхем постоянной ламяти при программировании,

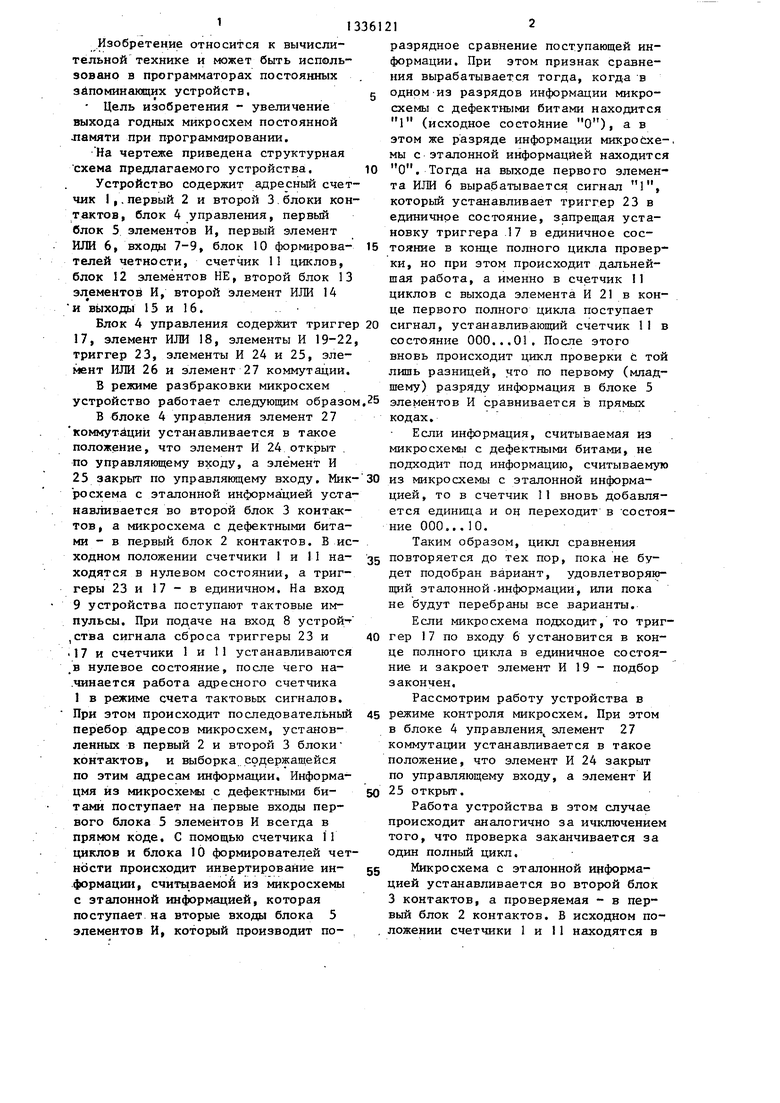

На чертеже приведена структурная схема предлагаемого устройства,

Устройство содержит адресный счетчик I,.первый 2 и второй 3.блоки контактов, блок 4 управления, первый блок 5 элементов И, первый элемент ИЛИ 6, входы 7-9, блок 10 формирова- телей четности, счетчик 11 циклов, блок 12 элементов НЕ, второй блок 13 эл ементов И, второй элемент ИЛИ 14 и выходы 15 и 16,

Блок 4 управления содержит триггер 17, элемент ИЛИ 18, элементы И 19-22 триггер 23, элементы И 24 и 25, элемент ИЛИ 26 и элемент 27 коммутации,

В режиме разбраковки микросхем устройство работает следуюпщм образом

В блоке 4 управления элемент 27 коммутации устанавливается в такое положение, что элемент И 24 открыт . по управляющему входу, а элемент И 25 закрыт по управляющему входу, Микросхема с эталонной информацией устанавливается во второй блок 3 контактов, а микросхема с дефектными битами - в первый блок 2 контактов, В исходном положении счетчики 1 и II на- ходятся в нулевом состоянии, а триггеры 23 и 17 - в единичном. На вход 9 устройства поступают тактовые импульсы. При подаче на вход 8 устроит ства сигнала сброса триггеры 23 и 17 и счетчики 1 и 11 устанавливаются в нулевое состояние, после чего на- .чинается работа адресного счетчика 1 в режиме счета тактовых сигналов, При этом происходит последовательный перебор адресов микросхем, установленных в первый 2 и второй 3 блоки контактов, и выборка.содержащейся по этим адресам информации, Информа- цмя из микросхемы с дефектными би- тами поступает на первые входы первого блока 5 элементов И всегда в прямом коде, С помощью счетчика П циклов и блока IО формирователей четности происходит инвертирование ин- .формации, считываемой из микросхемы с эталонной информацией, которая поступает на вторые входы блока 5 элементов И, который производит по212

разрядное сравнение поступающей информации. При этом признак сравнения вырабатывается тогда, когда в одном из разрядов информации микросхемы с дефектными битами находится 1 (исходное состойние О), а в этом же разряде информации микросхемы с эталонной информацией находится О, Тогда на выходе первого элемента ИЛИ 6 вырабатывается сигнал 1, который устанавливает триггер 23 в единичное состояние, запрещая установку триггера .17 в единичное состояние в конце полного цикла проверки, но при этом происходит дальней- щая работа, а именно в счетчик 11 циклов с выхода элемента И 21 в конце первого полного цикла поступает сигнал, устанавливающий счетчик 11 в состояние 000,,,01, После этого вновь происходит цикл проверки с той лишь разницей, что по первому (младшему) разряду информация в блоке 5 элементов И сравнивается в прямых кодах,

Если информация, считываемая из микросхемы с дефектными битами, не подходит под информацию, считываемую из микросхемы с эталонной информацией , то в счетчик 11 вновь добавляется единица и он переходит в состояние 000.,,10,

Таким образом, цикл сравнения повторяется до тех пор, пока не будет подобран вариант, удовлетворявз- щий эталонной -информации, или пока не будут перебраны все варианты.

Если микросхема подходит, то триггер 17 по входу 6 установится в конце полного цикла в единичное состояние и закроет элемент И 19 - подбор закончен.

Рассмотрим работу устройства в режиме контроля микросхем. При этом в блоке 4 управления элемент 27 коммутации устанавливается в такое положение, что элемент И 24 закрыт по управляющему входу, а элемент И 25 открыт.

Работа устройства в этом случае происходит аналогично за ичключением того, что проверка заканчивается за один полный цикл,

Микросхема с эталонной информацией устанавливается во второй блок 3 контактов, а проверяемая - в первый блок 2 контактов, В исходном положении счетчики 1 и 1I находятся в

313

нулевом состоянии, а триггеры 23 и 17 - в единичном. На третий вход устройства поступают тактовые импульсы. -При подаче на вход 8 устройства сигнала сброса триггеры 23 и 17 устанавливаются в нулевое состояние и начинается работа счетчика 1 в режиме счета тактовых сигналов. При этом происходит последовательный перебор адресов микросхем, устаиовленных в первый 2 и второй 3 блоки контактов и выборка содержащейся по этим адресам информации.

Информация из проверяемой микро- схемы в прямом коде поступает на первые входы блока 5 элементов И, а в обратном .коде - на пернле входы блока элементов И 13. Информация из эталонной микросхемы в прямом коде по- ступает на вторые входы блока 13 элементов И, а в обратном коде - на вторые входы блока 5 элементов И,

Блоки 5 и 13 элементов производят поразрядное сравнение поступающей информации. При этом при совпадении считываемой информации на выходах элементов ИЛИ 6 и 14 сигналы отсутствуют и сигналом по входу 7 триггер 17 в конце первого полного цикла устанавливается в единичное состояние, закрывая элемент И 19, что свидетельствует о том, что цикл проверки закончен и информация обеих микросхем соответствует одна другой.

В случае, когда из проверяемой микросхемы считывается 1, а из эталонной О, то на выходах элементов ИЛИ 6 и 1А появятся сигналы, которые постзшят на вход элемента И 25 блока 4, Снимаемый сигнал с выхода . элемента И 25 устанавливает триггер 17 в единичное состояние, не дожидаясь конца полного цикла проверки, и закрывает элемент И 19, При этом сигналы на вход адресного счетчика 1 не поступают, а снимае№1й сигнал с выхода элемента ИЛИ 14 свидетельствует 6 том, что информация в обеих микросхемах не совпадает, а сигнал с выхода элемента И 25 - о том, что проверяемая микросхема не может быть запрограммирована в соответствии с эталонной микросхемой.

В случае, когда из проверяемой микросхемы считывается О, а из эталонной - 1, то на выходе элемента ИЛИ 6 сигнал отсутствует, а на выходе элемента ИЛИ 14 сигнал появля

5 О

0 5 Q

g

5

ется, что свидетельствует о том, что информация в обеих микросхемах не совпадает. При этом сигнал на выходе элемента И 25 отсутствует и проверка «продолжается до конца полного цикла. В конце полного цикла сигналом по йходу 7 триггер 17 устанавливается в единичное состояние и закрывает элемент И 19. Отсутствие сигнала в течение полного цикла на выходе элемента И 25 свидетельствует о том, что проверяемая микросхема может быть запрограммирована в соответствии с эталонной микро схемой,

Формула изобретения

Устройство для разбраковки и контроля микросхем постоянной памяти, содержащее адресный счетчик, выходы которого подключены к адресным входам блока управления и являются ад- ресными выходами устройства, а вход сброса адресного счетчика является одноименным входом устройства и подключен к входам сброса блока управления и счетчика циклов, выходы которого соединены с входами второй группы блока формирователей четности, входы первой группы которого являются входами эталонных данных устройства, а выходы подключены к входам второй группы первого блока элементов И, входы первой группы которого являются входами контролируемых данных устройства, а выходы соединены с входами первого элемента ИЛИ, выход которого подключен к входу признака сравнения блока управления, входы тактовых импульсов и окончания контроля которого являются одноименными входами устройства, выхода синхронизации и окончания цикла блока управления соединены соответственно со счетными входами адресного счетчика и счетчика циклов, отличающеес-я тем, что, с Целью расширения функциональных возможностей устройства за счет дополнительной селекции микросхем памяти, в него введены блок эле ментов НЕ, второй блок элементов И и второй элемент ИЛИ, причем входы блока элементов НЕ подключены к входам контролируемых данных устройства, а выходы соединены с входами первой группы второго блока элементов И, входа второй группы которого под1у110- чены к входам эталонных данных уст51336121в

ройства, а выходы соединены с одними мации устройства и соединен с входом входами второго элемента ИЛИ, другие признака несовпадения блока управле- входа которого подключены к выходам ния, выход признака разбраковки кото- первого блока элементов И, а выход рого является одноименным выходом является выходом несовпадения инфор- .. устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разбраковки микросхем | 1981 |

|

SU968852A1 |

| Устройство для разбраковки микросхем | 1982 |

|

SU1103288A1 |

| Устройство для контроля оперативной памяти | 1983 |

|

SU1295455A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для контроля интегральных микросхем оперативной памяти | 1984 |

|

SU1249588A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля состояния информационно-измерительной системы | 1986 |

|

SU1314342A1 |

| Устройство для контроля КМОП-логических схем | 1987 |

|

SU1552137A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для контроля монтажа | 1990 |

|

SU1785001A1 |

Изобретение относится к вычислительной технике и может быть исполь% - зовано в программаторах постоянных Запоминающих устройств. Целью изобретения является расширение функциональных возможностей устройства за счет дополнительной селекции микросхем памяти. Устройство содержит адресный счетчик, счетяик циклов, блок формирователей неточности, первый и второй блоки элементов И, первый и второй элементы ИЛИ, блок элементов НЕ, блок управления. Увеличение выхода годных при программировании достигается за счет предварительной подборки дефектных микросхем в соответствии с эталонной информацией с последующей проверкой правильности программирования, 1 ил. i (Л С

№.

Авторы

Даты

1987-09-07—Публикация

1985-10-17—Подача