Изобретение .относится к запоминающим устройствам.

По основному авт.св. 744738 известно устройство, содержащее адресный блок памяти, соединенный с первым ассоциативным блоком памяти, второй ассоциативный блок памяти, одни из входов которого соединены с первым входом адресного блока памяти, блок управления, выходы которого подключены к управляющим входам ассоциативных блоков памяти, первый и второй коммутаторы и дешифратор, причем входы первого коммутатора подключены соответственно к первому выходу дешифратора и к выходу адресного блока памяти, а выходы - к другим входам второго ассоциативного блока памяти, выходы которого соединены со входом дешифратора и одним из входов второго кокмутатора, другой вход которого подключен ко второму выходу дешифратора, а выход - ко 2-ому вховходу адресного блока памяти 1.

В этом устройстве при обнаружении отказа в какой-либо ячейке блок управления определяет кратность ошибки и в зависимости от характера отказа адреса неработоспособной ячейки и номера отказавших разрядов фиксируются

во втором ассоциативном блоке памяти или адрес неработоспособной ячейки записывается в аргументной части перс вого ассоциативного блока памяти.

Недостатком этого устройства является его низкая надежность и невысокое быстродействие. При обращении ко второму ассоциативному блоку мяти в работе постоянно участвуют дешифратор и два коммутатора, что снижает надежность и &лстродействие запоминающего устройства.

Цель изобретения - повышение надежности и быстродействия устройства.

15

Поставленная цель достигается тем, что в оперативное запоминающее устройство с автономным контролем введена схема сравнения и элемент ИЛИ, причем входы схемы сравнения подклю20чены к выходам адресного блока памяти и второго кокмутатора, а выход соединен с маркерными входами ассоциативного блока памяти, маркерные выходы которого подключены к входам 25 элемента ИЛИ, выход которого соединен с входом адресного блока памяти.

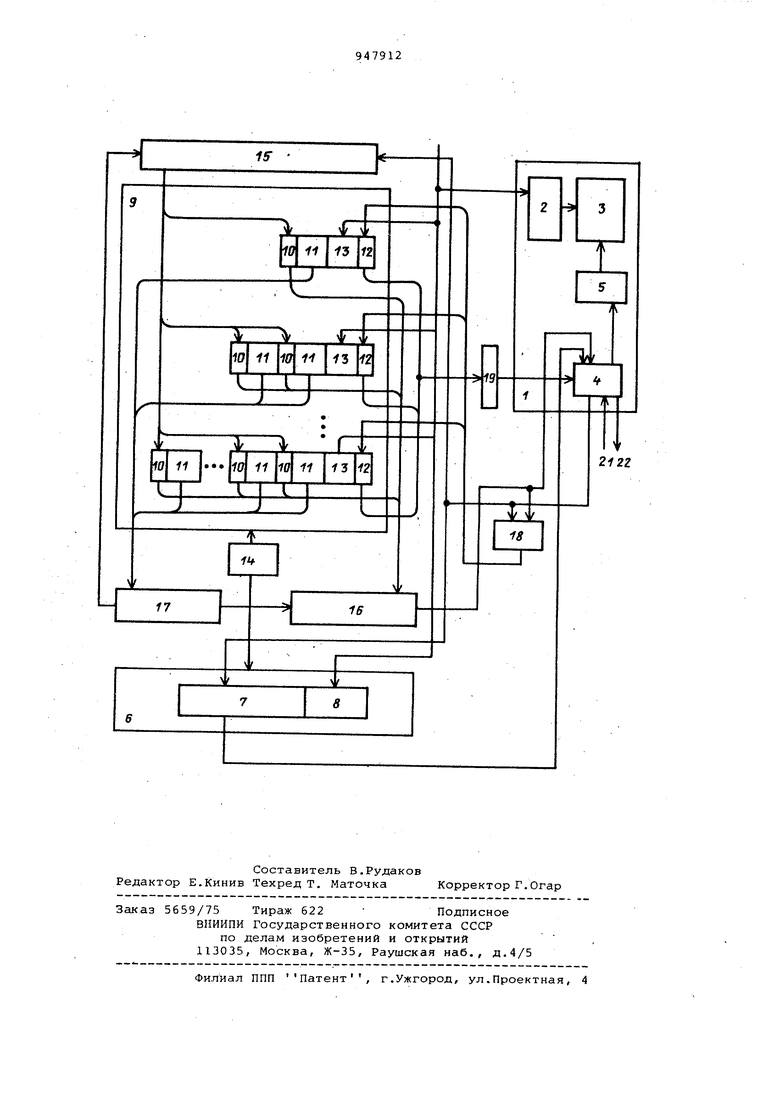

На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит адресный блок

30 1 памяти, состоящий из адресного вяока 2, блока 3 запоминающих матриц, регистра 4слова и усилителя 5 считывания-записи, причем адресный блок 1 памяти соединен с первым ассоциативным блоком 6 памяти, который имеет функциональную часть 7 для размещения полного слова отказавшей ячейки и аргументную часть 8 для -запоминания адреса отказавшей ячейки, и вторым ассоциативным блоком 9 памяти состоящим из функциональной части 10 .для размещения содержимого отказавших разрядов, признаковой части 11 для хранения номера отказавшего разряда, маркерной части 12 для хранения результатов сравнения и аргументной части 13 для запоминания отказавших ячеек адресного блока 1 памяти. Устройство содержит также блок 14 управления, выходы которого подключены к управляющим входам ассоциативных блоков 6 и 9 памяти, первый 15 и .второй 16 коммутаторы и дешифратор 17, причем входы первого коммутатора 15 подключены соответственно к первому выходу дешифратора 17 и к выхо ду адресного блока 1 памяти, а выход - к другому входу второго ассоциативного блока 9 памяти, выходы которого соединены с входом дешифратора 17 и одним из входов второго коммутатора 16, другой вход которого подключен ко второму выходу дешифратора 17, а выход - к второму входу адресного блока 1 памяти и к одному из входов схемы 18 сравнения, другой вход которой соединен с одним из выходов адресного блока 1, а выход с маркерными входами блока 9, маркерные выходал которого .через элемент ИЛИ 19 подключены к одному из входов блока 1. Адрес подается на вход 20 устройства, записываемое слово - на вход 21, .а считываемое - на выход 22, Устройство работает следующим образом. В паузах между внешними обращения ми .блок 14 управления .производит контроль исправности ячеек адресного блока 17 памяти. При обнаружении неисправности в какой-либо ячейке блок 14 управления определяет кратность ошибки. Если кратность ошибки меньше или равйа т, где m определяют из неравен ства + ) (п - количество раз слова, записываемого в адресный блок 1 памяти), то блок 14 управлени дополнительно определяет номера отка завших разрядов ячейки блока 1 и характер отказа (устойчивый устойчивая ). При этом адрес не работоспособной ячейки фиксируется в аргументной части 13, номера отказав ших разрядов в признаковой части 11, характер отказа разряда ячейки в фун кциональной части 10 второго ассоциативного блока 9 памяти. Если кратность ошибки больше т, то адрес неисправной ячейки записывают в аргументную часть 9 первого ассоциативного блока 6 памяти. При обращении к оперативному запоминающему устройству по адресу, установленному на входе 20, происходит одновременное обращение как к адресному блоку 1 памяти, так и к ассоцитивным блокам б и 9 памяти. . При выполнении операции записи данные со входа 21 заносят в регистр 4 слова и через усилители 5 считывания-записи записывают в блок 4 запоминающих матриц по адресу, зафиксированному в блоке 2. Если при ассоциативном поиске в блоке б обнаружен адрес обращения, то данные с регистра- 4 слова записывают в функциональную часть 7 блока б. Если зтот адрес обнаружен при ассоциативном поиске в блоке 9, то содержимое признаковой части 11 соответствующей ячейки блока 9 поступает на дешифратор 17, а содержимое функциональной части 10 поступает на второй коммутатор 16. Одновременно на другой вход первого коммутатора 15 и на один из входов узла 18 сравнения с регистра 4 слова поступает записываемое слово. При совпадении соответствующих разрядов записываемого слова с содержимым функциональной части 10 (т.е. значением состояния неработоспособных разрядов ячеек) схема 18 сравнения взводит маркерный разряд 12 соответствующей ячейки блока 9 в . Если содержимое функциональной части 10 не совпадает с значением соответствующего разряда регистра 4, то маркерный разряд остается в О состоянии, и разряды слова соответствующие отказавшим разрядам ячейки блока 1 записывают в функциональную часть 10 блока 9. При выполнении операции чтения из оперативного запоминающего устройства происходит выборка содержимого блока 3 на регистр 4, одновременно происходит ассоциативный поиск в блоках 6 и 9. Если в блоках 6 и 9 такого адреса нет, то значение слова на регистре 4 является истинным и выдается на выход 22. Если в блоке 6 есть такой адрес, то содержимое ячейки блока, связанной с этим адресом, выдается на регистр 4 и далее на выход 22. При обнаружении адреса обращения в блоке 9, опрашивается маркерный разряд 12 данной ячейки. Если он взведен в , то производится выдача слова с регистра 4 без изменения . Если значение маркерного разряда равно О, то содержимое признаковой части 11 данной ячейки блсжа 9 поступает на дешифратор 17, входные сигналы которого подаются на вход второго коммутатора 16. Разряды слов соответствующие отказавшим разрядам ячейки блока 1 через второй коммутатор 16 из функциональной части 10 блока 9 записывают в регистр слова 4 Правильное значение слова выдается на выход 22. При обращении для записи к ячейкам, вторым отказал один разряд, при несовпадении содержимого функциональ ной части 10 со значением соответствующего разряда регистра слова 4 инвертируется значение маркерной части 12. При обращении к ячейкам, в которых отказало два и более разрядов (но не больше т-разрядов) при первом несовпадении содержимого функциональ ной части 10 со значением соответствующего разряда регистра слова, маркерный разряд устанавливается в О до очередной паузы для проведения контроля исправности ячеек блока 1. Таким образец, предлагаемое устройство позволяет в режиме считывани при выборке слова из ячейки с отказавшими разрядами при взведенном в маркерном разряде исключить из работы дешифратор 17, второй коммутатор 16, признаковую 10 и функциоиальную 11 части блока 9, что повышает надежность и быстродействие устройства . Формула изобретения Оперативное запоминающее устройство с автономным контролем по авт.св. № 744738, о т л и ч аЪ щ е е с я тем, что, с целью повышения надежности и быстродействия устройства, оно содержит схему сравнения и злемент ИЛИ, причем входы сравнения подключены к выходам адресного блока памяти и второго коммутатора, а выход соединен с маркерными входами ассоциативного блока памяти, маркерные выходы которого подключены к входам элемента ИЛИ, выход которого соединен с входом адресного блока памяти. Источники информации, принятые во внимание при экспертизе 1, Авторское Свидетельство СССР -744738, кл. G 11 С 29/00, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с автономным контролем | 1978 |

|

SU744738A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU970479A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство | 1972 |

|

SU437127A1 |

| Оперативное запоминающее устройст-BO C САМОКОНТРОлЕМ | 1979 |

|

SU794671A1 |

Авторы

Даты

1982-07-30—Публикация

1979-04-05—Подача