(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1984 |

|

SU1249589A1 |

| Устройство для хранения информации с контролем | 1989 |

|

SU1691897A1 |

| Устройство для контроля цифровых данных | 1985 |

|

SU1381718A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Устройство для контроля и коррекции информации | 1980 |

|

SU940160A1 |

| Устройство для коррекции микрокоманд | 1984 |

|

SU1164709A1 |

| Устройство для обнаружения и ис-пРАВлЕНия ОшибОК B блОКАХ ВычиСли-ТЕльНОй МАшиНы | 1979 |

|

SU840912A1 |

| Процессор ввода-вывода с коррек-циЕй ОшибОК | 1979 |

|

SU849221A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Устройство для обнаружения и исправления ошибок | 1982 |

|

SU1149263A1 |

Изобретение относится к запоминающим устройствам.

Известно устройства для контроля блоков памяти, содержащее накопитель, адресный блок, блок управления, блок записи-считывания, основной регистр слова, элементы ИЛИ, основные сумматоры по модулю два и основную схему сравнения 1 .

Недостатками этого устройства являются малая обнаруживающая и корректирующая способность, так как оно позволяет исправлять ошибку только в пределах одного байта, и большие затраты оборудования.

Наиболее близким к изобретению техническим реи1ением является устройство для контроля блоков памяти, содержащее группу сумматоров по модулю два, первый элемент ИЛИ, элемент И и инвертор, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом первого Э1гемента ИЛИ 2.

Нещостатком этого устройства является отсутствие эффективной возможности ипращивания его разрядности путем прост, Го соединения нескольких устройсугв, этом суммарное число коитр-(1 разрядов возрастает пропорционально разрядности контролируемой памяти. Кроме того, необходимо разрабатывать различные схемл для блока, генерирующего разряды кода Хэмминга, и блока фор№1рующего корректирующие синдромы, которые служат для указания номера разряда памяти, в котором произошла ощибка. Это приводит к увеличению аппа10ратных затрат и снижению надежности устройства.

Цель изобретения - упрощение и повышение надежности устройства.

Поставленная цель достигается тем,

15 что в устройство для контроля блоков памяти, содержащее сумматоры по модулю два, первый элемент ИЛИ, элемент И и элемент НЕ, выход которого соединен с первым входом элемента И,

20 второй вход которого соединен с выходом первого элемента ИЛИ, входы которого соединены с выходами одних из сумматоров по модулю два и с одним из в-лходов устройства, другие

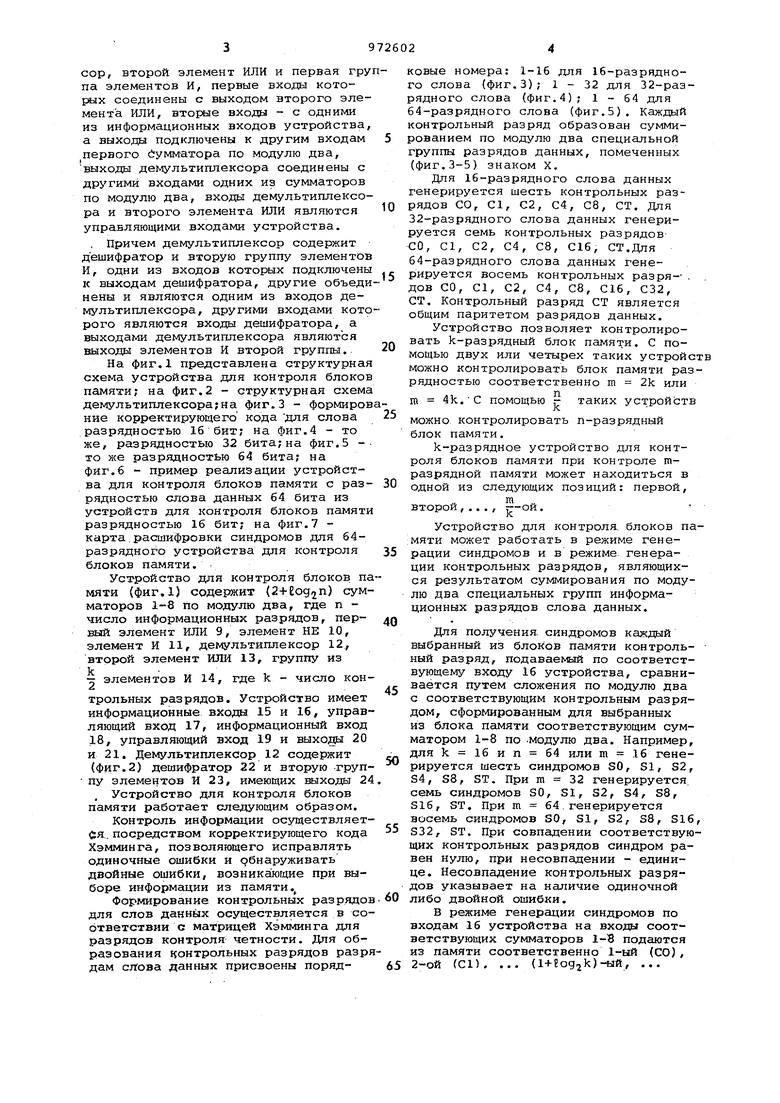

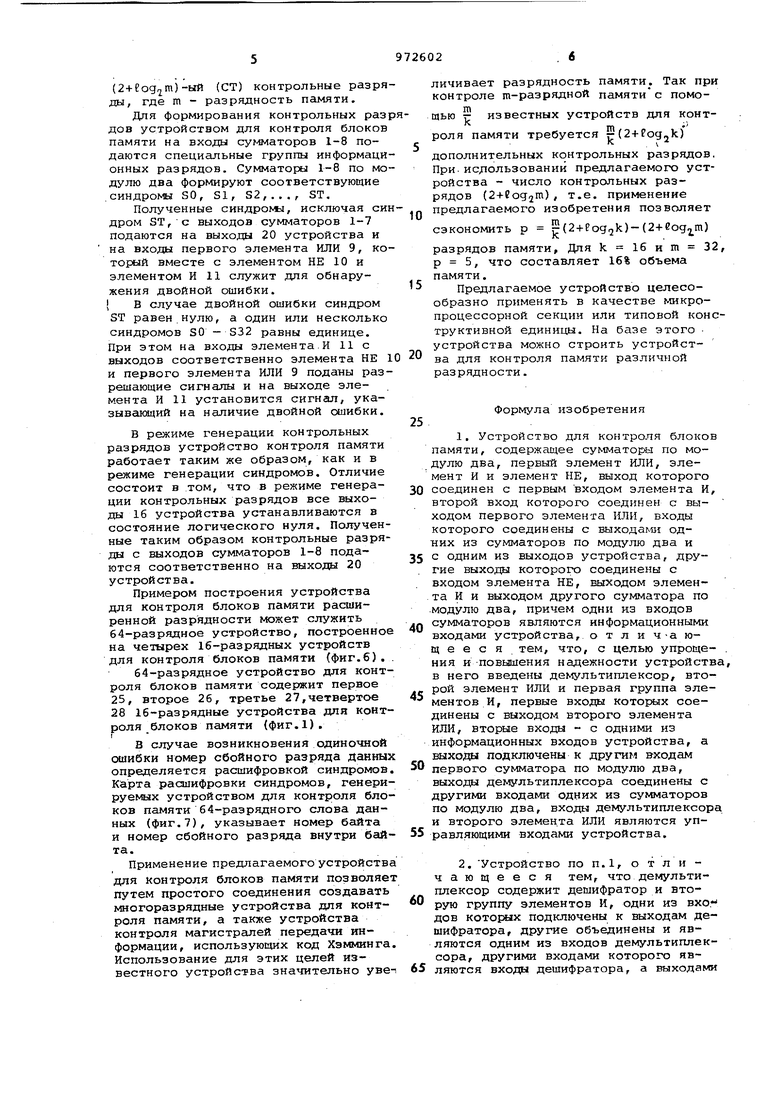

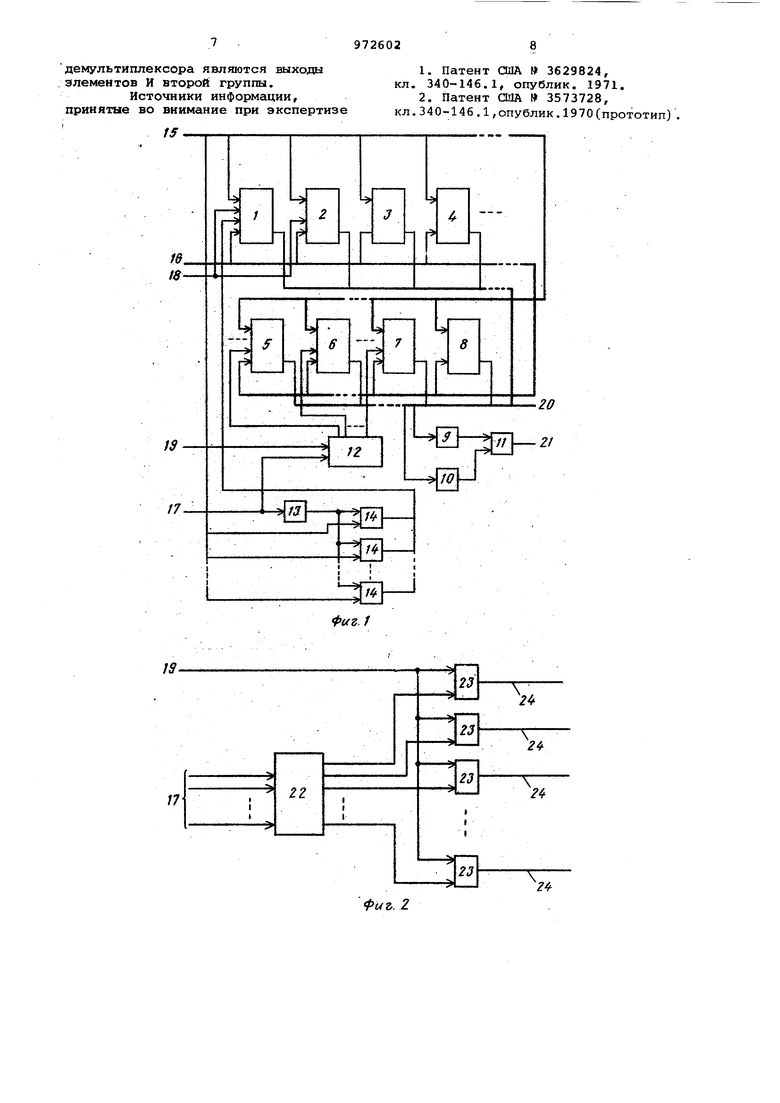

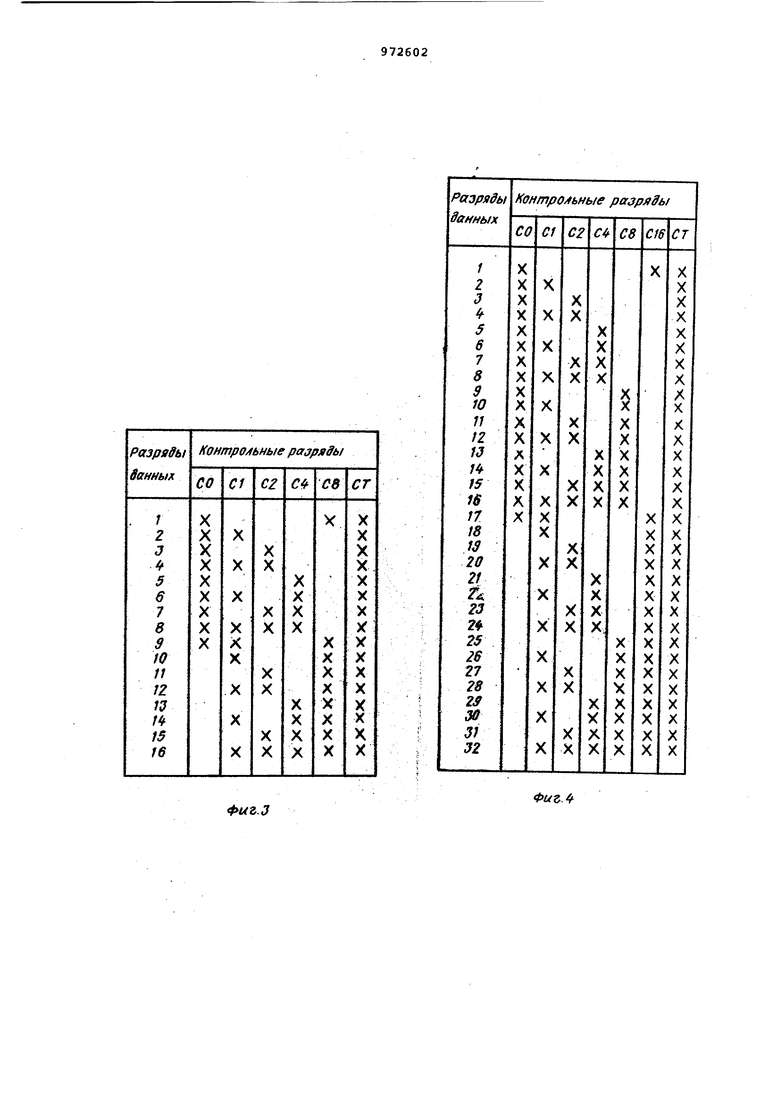

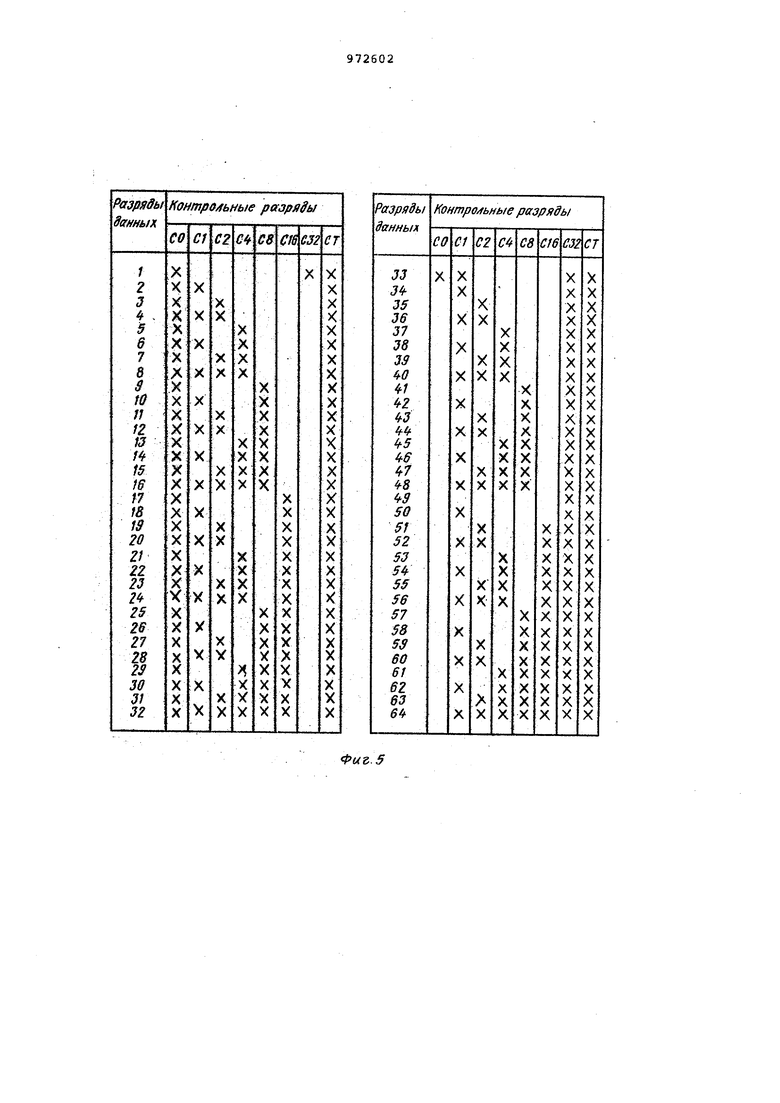

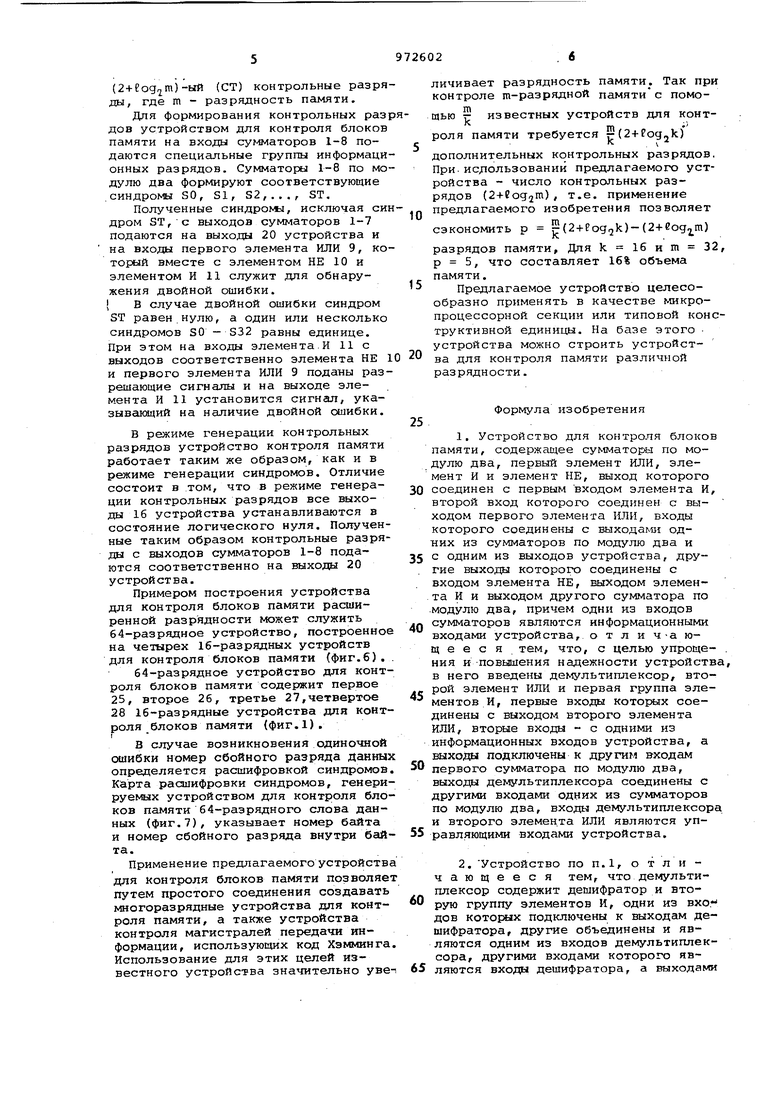

25 выходы которого соединены с входом элемента НЕ, выходом элемента И и выходом другого cyм.1aтopa по модулю два, причем одни из входов ON MBTOров являются информлиионкыми вхол.ми устройства, введены детльтипл ксор, второй элемент ИЛИ и первая тру па элементов И, первые входы которых соединены с выходом второго элемента ИЛИ, вторле входы - с одними из информационных входов устройства а выходы подключены к другим входам первого йумм атора по модулю два, выходы демультиплексора соединены с другими входами одних из сумматоров по модулю два, входы демультиплексора и второго элемента ИЛИ являются управляющими входами устройства. , Причем демультиплексор содержит дешифратор и вторую группу элементов И, одни из входов которых подключены к выходам дешифратора, другие объеди нены и являются одним из входов демультиплексора, другими входами кото рого являются входы дешифратора, а выходами демультиплексора являются выходы элементов И второй группы, На фиг.1 представлена структурная схема устройства для контроля блоков памяти; на фиг.2 - структурная схема демультиплексора;на фиг.З - формиров ние корректирующего кода для слова разрядностью 16 бит; на фиг.4 - то же, разрядностью 32 бита;на фиг.5 то же разрядностью 64 бита; на фиг.б - пример реализации устройства для контроля блоков памяти с разрядностью слова данных 64 бита из устройств для контроля блоков памяти разрядностью 16 бит; на фиг.7 карта расшифровки синдромов для 64разрядного устройства для контроля блоков памяти. Устройство для контроля блоков па мяти (фиг.1) содержит (S+Eogjn) сум маторов 1-8 по модулю два, где п число информационных разрядов, первый элемент ИЛИ 9, элемент НЕ 10, элемент И 11, демультиплексор 12, второй элемент ИЛИ 13, группу из - элементов И 14, где k - число кон трольных разрядов. Устройство имеет информационные входеа 15 и 16, управ ляющий вход 17, информационный вход 18, управляющий вход 19 и выхода 20 и 21. Демультиплексор 12 содержит (фиг.2) дешифратор 22 и вторую .груп - пу элементов И 23, имеющих выходы 2 Устройство для контроля блоков памяти работает следующим образом. Контроль информации осуществляет ся, посредством корректирующего кода Хэмминга, позволяющего исправлять одиночные ошибки и рбнаруживать двойные ошибки, возникающие при выборе информации из памяти. Формирование контрольных разрядо для слов данийх осуществляется в со ответствии с матрицей Хэмминга для разрядов контроля четности. Для образования контрольных разрядов разр дам сяова данных присвоены порядковые номера: 1-16 для 16-разрядного слова (фиг.З); 1-32 для 32-разрядного слова (фиг.4); 1 - 64 для 64-разрядного слова (фиг.5). Каждый контрольный разряд образован суммированием по модулю два специальной группы разрядов данных, помеченных (фиг.3-5) знаком X. Для 16-разрядного слова данных генерируется шесть контрольных разрядов СО, С1, С2, С4, С8, СТ. Для 32-разрядного слова данных генерируется семь контрольных разрядовСО, С1, С2, С4, С8, С16, СТ.Для 64-разрядного слова данных генерируется восемь контрольных разря-- . дов СО, С1, С2, С4, С8, С16, С32, СТ. Контрольный разряд СТ является общим паритетом разрядов данных. Устройство позволяет контролировать k-разрядный блок памяти. С помощью двух или четырех таких устройств можно контролировать блок памяти разрядностью соответственно m 2k или m 4k.С помощью ,- таких устройств можно контролировать п-разрядный блок памяти. k-разрядное устройство для контроля блоков памяти при контроле горазрядной памяти может находиться в одной из следующих позиций: первой, второй,..., . Устройство для контроля, блоков памяти может работать в режиме генерации синдромов и в режиме генерации контрольных разрядов, являющихся результатом суммирования по модулю два специальных групп информационных разрядов слова данных. Для получения, синдромов каждый выбранный из блоков памяти контрольный разряд, подаваемый по соответствующему входу 16 устройства, сравнивается путем сложения по модулю два с соответствующим контрольным разрядом, сформированным для выбранных из блока памяти соответствующим сумматором 1-8 по .модулю два. Например, для k 16 и п 64 или m 16 генерируется шесть синдромов SO, SI, S2, S4, S8, ST. При га 32 генерируется, семь синдромов SO, SI, S2, S4, SB, S16, ST. При m 64.генерируется восемь синдромов SO, SI, S2, 38, SI6, S32, ST. При совпадении соответствующих контрольных разрядов синдром равен нулю, при несовпадении - единице. Несовпадение контрольных разрядов указывает на наличие одиночной либо двойной ошибки. В режиме генерации синдромов по входам 16 устройства на входа соответствующих сумматоров 1-В подаются из памяти соответственно 1-ый (СО), 2-ой (С1). ... (l+togгk), ... (2+Zog m)tiPi (СТ) контрольные разря ды, где m - разрядность памяти. Для формирования контрольных раз дов устройством для контроля блоков памяти на входы сумматоров 1-8 подаются специальные группы информаци онных разрядов. Сумматоры 1-8 по мо дулю два формируют соответствующие .синдромы SO, SI, S2,..., ST. Полученные синдромы, исключая си дром ST, с выходов сумматоров 1-7 подаются на выходы 20 устройства и на входы первого элемента ИЛИ 9, ко торый вместе с элементом НЕ 10 и элементом И 11 служит для обнаружения ДВОЙНОЙ ошибки, j В случае двойной ошибки синдром ST равен.нулю, а один или несколько синдромов SO - 832 равны единице. При этом на входы элемента.И 11 с выходов соответственно элемента НЕ и первого элемента ИЛИ 9 поданы раз решающие сигналы и на выходе элемента И 11 установится сигнал, указывакйций на наличие двойной ошибки. В режиме генерации контрольных разрядов устройство контроля памяти работает таким же образом, как и в режиме генерации синдромов. Отличие состоит в том, что в режиме генерации контрольных разрядов все выходы 16 устройства устанавливаются в состояние логического нуля. Полученные таким образом контрольные разряды с выходов сумматоров 1-8 подаются соответственно на выходаг 20 устройства. Примером построения устройства для контроля блоков памяти расширенной разрядности может служить 64-разрядное устройство, построенное на четырех 16-разрядных устройств для контроля блоков памяти (фиг.б). 64-разрядное устройство для контроля блоков памяти содержит первое 25, второе 26, третье 27,четвертое 28 16-разрядные устройства для контроля блоков памяти (фиг.1), В случае возникновения одиночной ошибки номер сбойного разряда данных определяется расшифровкой синдромов карта расшифровки синдромов, генерируемых устройством для контроля блоков памяти 64-разрядного слова данных (фиг.7), указывает номер байта и номер сбойного разряда внутри байта. Применение предлагаемого устройств для контроля блоков памяти позволяе путем простого соединения создавать многоразрядные устройства для контроля памяти, а также устройства контроля магистралей передачи информации, использующих код Хэмминга Использование для этих целей известного устройства значительно уве личивает разрядность памяти. Так при контроле т-разрядной памятис помощью известных устройств для контроля памяти требуется (2+Pog-k) . дополнительных контрольных разрядов. При.использовании предлагаемого устройства - число контрольных разрядов (2+Уод ш), т.е. применение предлагаемого изобретения позволяет сэкономить р (2+PogQk)-(2+Cog m) разрядов памяти. Для k 16 и m 32, р 5, что составляет 16% объема памяти. Предлагаемое устройство целесообразно применять в качестве микропроцессорной секции или типовой конструктивной единицы. На базе этого . устройства можно строить устройства для контроля памяти различной разрядности. Формула изобретения 1.Устройство для контроля блоков памяти, содержащее сумматоры по модулю два, первый элемент ИЛИ, элемент И и элемент НЕ, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, входы которого соединены с выходами одних из сумматоров по модулю два и с одним из выходов устройства, другие выходы которого соединены с входом элемента НЕ, выходом элемента И и выходом другого сумматора по .модулю два, причем одни из входов сумматоров являются информационными входами устройства, о т л и ч-а ющ е е с я тем, что, с целью упроце- . НИН и повышения надежности устройства, в него введены демультиплексор, второй элемент ИЛИ и первая группа элементов И, первые входы которых соединены с выходом второго элемента ИЛИ, вторые входы - с одними из информационных входов устройства, а выходы подключены к другим входам первого сумматора по модулю два, выходы демультиплексора соединены с другими входами одних из сумматоров по модулю два, входы демультиплексора и второго элемента ИЛИ являются управляющими входами устройства. 2.Устройство по П.1, о т ли чающееся тем, что демультиплексор содержит дешифратор и вторую группу элементов И, одни из вхо. дов которых подключены к выходам дешифратора, другие объединены и являются одним из входов демультиплексора, другими входами которого являются входы дешифратора, а выходами

демультиплексора являются выходы элементов И второй группы.

Источники информации, принятые во внимание при экспертизе

кл.340-146.1,опублик.1970(прототип)

р1АЪ.2

Фиг.З

Фие.

Фиг. 5

фи. 6

фи-&. 7

Авторы

Даты

1982-11-07—Публикация

1981-05-06—Подача