ней с вторым коллектором первого п-р-п-транзистора первого разряда, базой трехколлекторного транзистора второго ключевого элемента и выходом первого согласующего элемента, первый и второй коллекторы второго п-р- п-транзистора триггера последнего разряда подключены соответственно к выходу и входу третьего и четвертого согласующих элементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Управляющий регистр для буферного запоминающего устройства | 1987 |

|

SU1499405A1 |

| Регистр для буферного запоминающего устройства | 1984 |

|

SU1170511A1 |

| Управляющий регистр для буферного запоминающего устройства | 1984 |

|

SU1231536A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1973 |

|

SU389548A1 |

| Распределитель импульсов для многотактового запоминающего устройства на регистрах сдвига | 1978 |

|

SU752488A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Цифровые электронные часы | 1978 |

|

SU779967A1 |

| Элемент памяти для регистра сдвига | 1979 |

|

SU847373A1 |

1

Изобретение откосится к вычисли - тельной технике, в частности к запоминающим устройствам (3y)j и может быть составной частью БИС буферного .ЗУ регистрового типа на совмещенных П р-п-р-транзисторных структурах (на инжекционных схемах).

Цель изобретения - упрощение регистра сдвига.

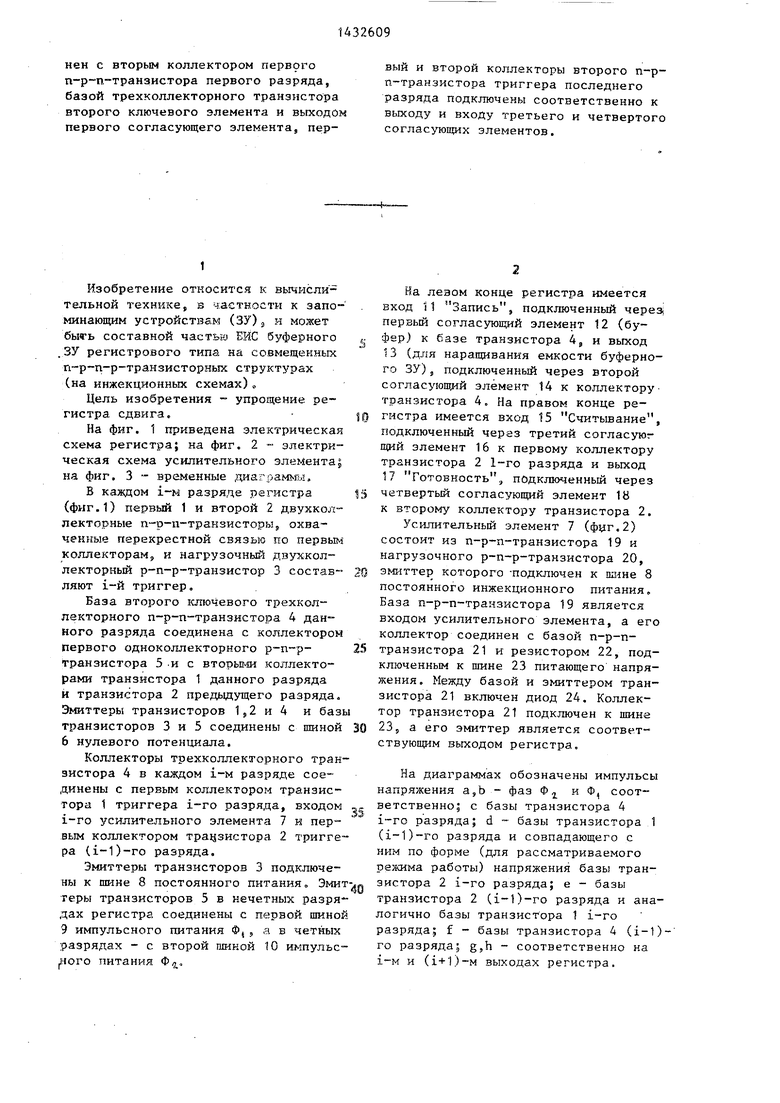

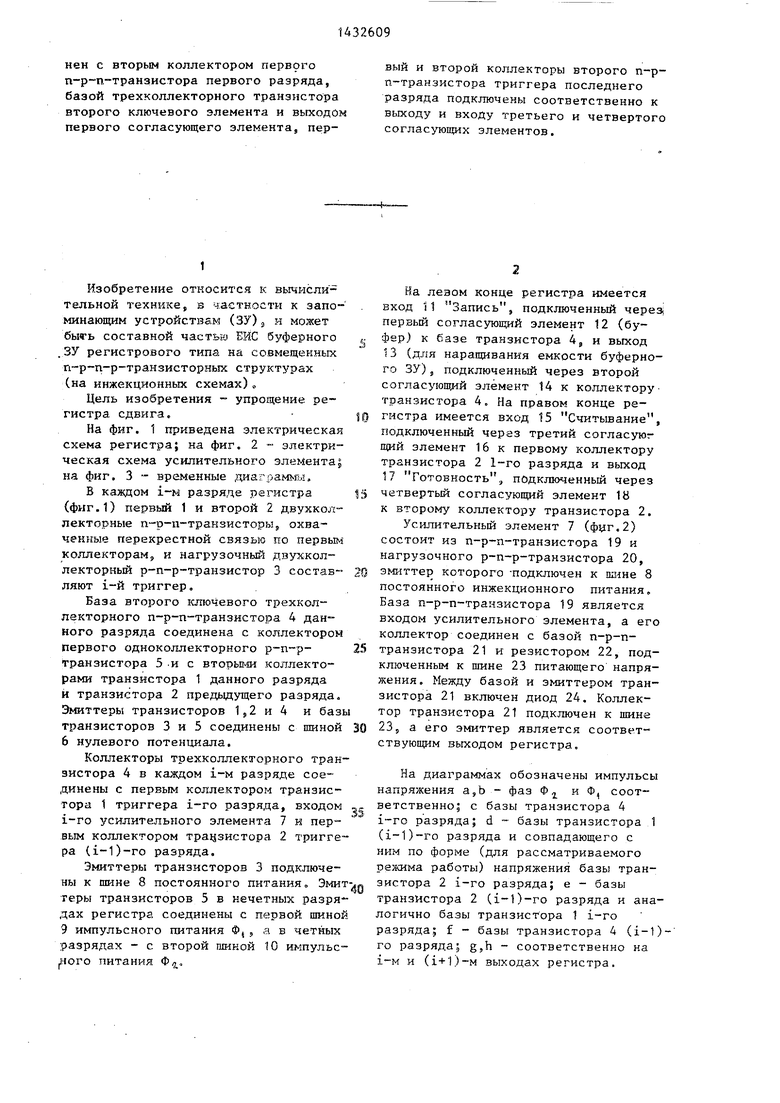

На фиг, 1 приведена электрическая схема регистра; на фиг. 2 - электрическая схема усилительного элемента; на фиг. 3 - временные диагоаммъь

В каяадом i-м разряде регистра (фиг.1) первый 1 и второй 2 двухкол- лекторные п-р-п-тракзисторы охваченные перекрестной связью по первым коллекторам, и нагрузочный двухкол- лекторный р-п-р-транзистор 3 составляют i-й триггер,

База второго ключевого трехкол лакторного п-р-п-транзистора 4 данного разряда соединена с коллектором первого одноколлекторного транзистора 5 -и с вторьп и коллекторами транзистора 1 данного разряда и транзистора 2 предьщущего разряда. Эмиттеры транзисторов и 4 и баз транзисторов 3 и 5 соединены с шиной 6 нулевого потенциала.

Коллекторы трехколлекторного транзистора 4 в каждом i-M разряде соединены с первым коллектором транзистора 1 триггера i-ro разряда, входом i-ro усилительного элемента 7 и первым коллектором транзистора 2 триггера (i-l)-ro разряда.

Эмиттеры транзисторов 3 подключены к шине 8 постоянного питания. Эмитеры транзисторов 5 в нечетных разря дах регистра соединены с первой шино 9 импульсного питания Ф, а в четных разрядах - с второй ямной 10 импульс jHoro питания Ф,,

На левом конце регистра имеется вход 11 Запись, подключенный через первый согласую1ций элемент 12 (бу- . фер) к базе транзистора 4, и выход 13 (для наращивания емкости буферного ЗУ), подключенный через второй согласующий элемент 14 к коллектору- транзистора 4. На правом конце ре0 гистра имеется вход 15 Считьшание, подключенный чераз третий согласуюг щий элемент 16 к первому коллектору транзистора 2 1-го разряда и выход 17 Готовность,, подключенный через

f} четвертый согласующий элемент 18 к второму коллектору транзистора 2.

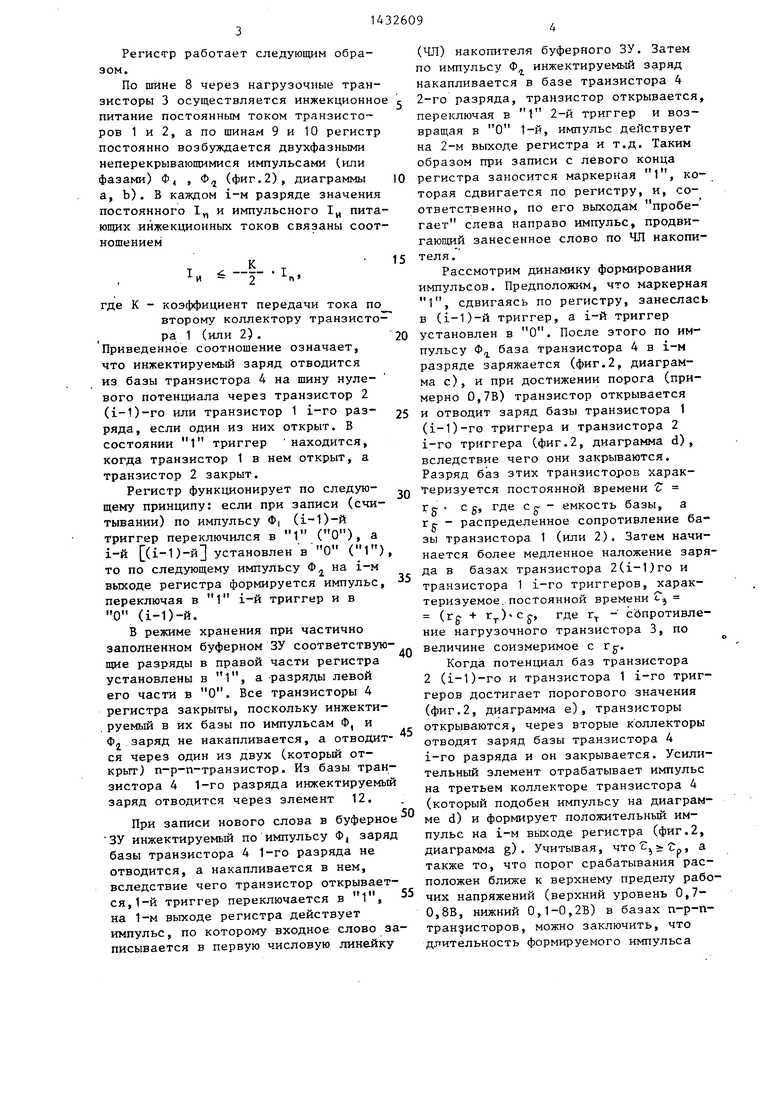

Усилительный элемент 7 (фуг.2) состоит из п-р-п-транзистора 19 и нагрузочного р-п-р-транзистора 20,

0 эмиттер которого -подключен к шлне 8 постоянного инжекционного питания. База п-р-п-транзистора 19 является входом усилительного элемента, а его коллектор соединен с базой п-р-п5 транзистора 21 к резистором 22, подключенным к шине 23 питающего напряжения. Между базой и эмиттером транзистора 21 включен диод 24. Коллектор транзистора 21 подключен к шине

0 23, а его эмиттер является соответствующим выходом регистра.

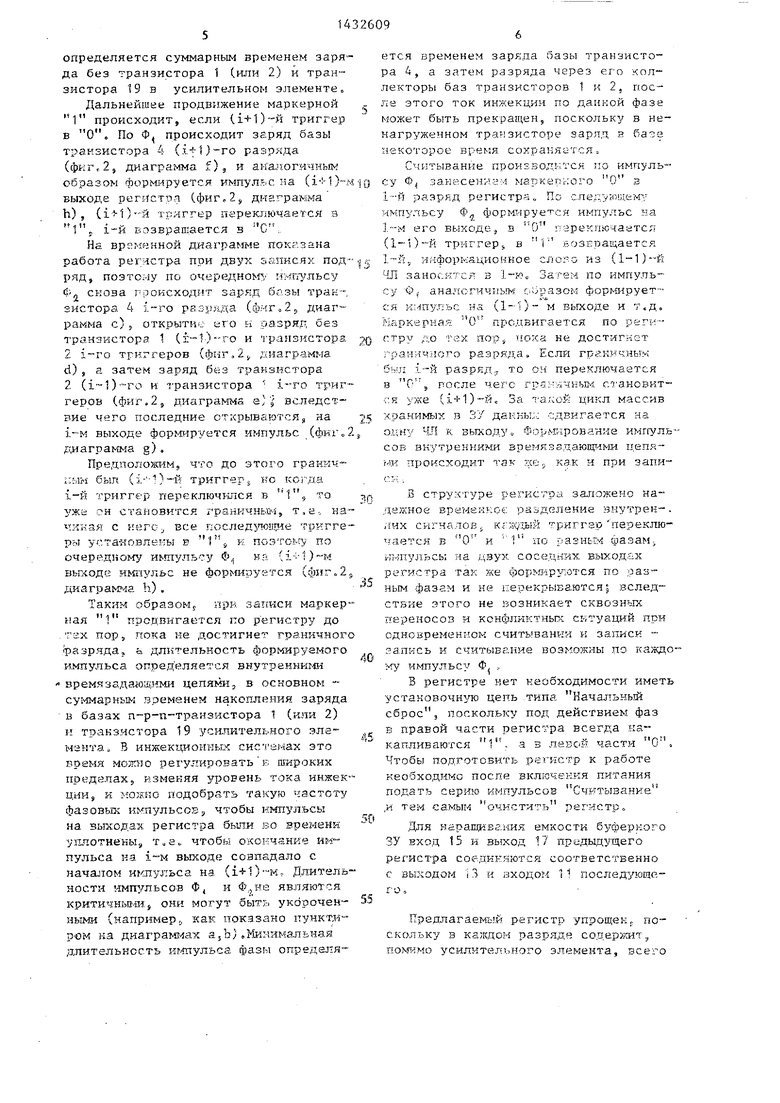

На диаграммах обозначены импульсы напряжения а,Ь - фаз Ф и Ф, соот- , ветственно; с базы транзистора 4

разряда; d - базы транзистора 1 (i-1)-ro разряда и совпадающего с ним по форме (для рассматриваемого режима работы) напряжения базы транзистора 2 1-го разряда; е - базы транзистора 2 (i-l)-ro разряда и аналогично базы транзистора 1 i-ro разряда; f - базы транзистора 4 (i-1)- го разряда; g.h - соответственно на i-M и (i+1)-M выходах регистра.

Регистр работает следующим образом.

По пгане 8 через нагрузочные транзисторы 3 осуществляется инжекционно питание постоянным током транзисторов 1 и 2, а по шинам 9 и 10 регистр постоянно возбуждается двухфазными неперекрывающимися импульсами (.или фазами) Ф, , Ф (фиг.2), диаграммы а, Ь). В каждом i-м разряде значения постоянного 1„ и импульсного 1„ питающих инжекционных токов связаны соотношением

К , IH 6 -- -I-,.

где К - коэффициент передачи тока по второму коллектору транзистора 1 (или 2). Приведенное соотношение означает, что инжектируемый заряд отводится из базы транзистора 4 на шину нулевого потенциала через транзистор 2 (i-1)-ro или транзистор 1 i-ro разряда, если один из них открыт. В состоянии 1 триггер находится, когда транзистор 1 в нем открыт, а транзистор 2 закрыт.

Регистр функционирует по следующему принципу: если при записи (считывании) по импульсу Ф| (1-1)-й триггер переключился в 1 (О), а i-й (1-1)-й установлен в О (1) то по следующему импульсу Ф. на i-м выходе регистра формируется импульс, переключая в 1 i-й триггер и в О (i-1)-й.

В режиме хранения при частично заполненном буферном ЗУ соответствующие разряды в правой части регистра установлены в 1, а разряды левой его части в О. Все транзисторы 4 регистра закрыты, поскольку инжектируемый в их базы по импульсам Ф, и

Ф заряд не накапливается, а отводит ся через один из двух (который открыт) п-р-п-транзистор. Из базы транзистора 4 1-го разряда инжектируемый заряд отводится через элемент 12.

При записи нового слова в буферное ЗУ инжектируемый по импульсу Ф, заряд базы транзистора 4 1-го разряда не отводится, а накапливается в нем, вследствие чего транзистор открывается, 1-й триггер переключается в 1 ,

.

на 1-м выходе регистра действует импульс, по которому входное слово записывается в первую числовую линейку

с 10 15

20

30

35

40

45

50

(ЧЛ) накопителя буферного ЗУ. Затем по импульсу Ф инжектируемый заряд накапливается в базе транзистора 4 2-го разряда, транзистор открывается, переключая в 1 2-й триггер и возвращая в О 1-й, импульс действует на 2-м выходе регистра и т.д. Таким

н 1

кообразом при записи с левого конца регистра заносится маркерная торая сдвигается по регистру, и, соответственно, по его выходам пробегает слева направо импульс, продвигающий занесенное слово по ЧЛ накопителя.

Рассмотрим динамику формирования импульсов. Предположим, что маркерная 1, сдвигаясь по регистру, занеслась в (i-1)-й триггер, а i-й триггер

О. После этого по имустановлен в а

пульсу Ф„ база транзистора 4 в i-м

разряде заряжается (фиг.2, диаграмма с), и при достижении порога (примерно 0,7В) транзистор открывается

25 и отводит заряд базы транзистора 1 (i-l)-ro триггера и транзистора 2 i-ro триггера (фиг.2, диаграмма d), вследствие чего они закрываются. Разряд баз этих транзисторов харак- геризуется постоянной времени € Ге с g, где с с- емкость базы, а Гг- - распределенное сопротивление базы транзистора 1 (или 2). Затем начинается более медленное наложение заряда в базах транзистора 2(i-1)ro и транзистора 1 i-ro триггеров, характеризуемое, постоянной времени (rg- + r)«Cj, где г - сйпротивле- ние нагрузочного транзистора 3, по величине соизмеримое с rg-.

Когда потенциал баз транзистора 2 (i-1)-ro и транзистора 1 i-ro триггеров достигает порогового значения (фиг.2, диаграмма е), транзисторы открываются, через вторые коллекторы отводят заряд базы транзистора 4 i-ro разряда и он закрывается. Усилительный элемент отрабатывает импульс на третьем коллекторе транзистора 4 (который подобен импульсу на диаграмме d) и формирует положительный импульс на i-M выходе регистра (фиг.2, диаграмма g). Учитывая, чтосГ ь ср, а также то, что порог срабатывания расположен ближе к верхнему пределу рабо чих напряжений (верхний уровень 0,7- 0,8В, нижний О,1-0,2В) в базах п-р-п- трандисторов, можно заключить, что длительность формируемого импульса

определяется суммарным временем заря да без транзистора 1 (или 2) и транзистора 19 в усилительном элементе. Дальнейшее продвижение маркерной М происходит, если (1+1)й триггер в О. По Ф, происходит заряд базы транзистора 4 (if1)-го разряда (фкг,25 диаграмма f),, и аналогичньск образом формируется импул..с на (i-i-1

выходе регистра (.фиг „2, диаграмма h) 5 ()й триггер переключается в 1 % i-й возврашается s C V

На временной диаграмме показана работа регистра при двух записях под-.| ij ряд, поэтому по очередному ммп-ульеу Ф, скова происходит заркд базы трак-, эистора 4 i-ro разряда (фяг,2,, диаг--- рамма с)5 открытие его и разряд без транзистора 1 ()--ro и траизисторз. 0 2. i-ro триггеров (фнг,2;, диаграмма d)J а затем заряд без транзистора 2 ()-го и 1 ранзистора i-ro триггеров (фиг.25 диаграмма вследст- зие чего последние открываются на 75 i-M выходе формируется импульс (фкг„25 диаграмма g),

Предположим что до этого граничным был (з.- -1)-й триггеру ко ког да i-й триггер ггереключ5-шся в 1, то -.п ужа он становится граничным, т.е., на- чикзя с неге J все послед тоище триггеры установлены в ;, к позтол-гу по очередному иьгаульсу Ф,, ва (iv1)M импульс не фop шpyйтcя (фпг 25 диагра№4а Ь) ,

Таким образом при записи маркерная I продвигается по регистру до .тех пор, ГЕОка не. достигнет граничного (разряда, а. длительность формируемого импульса определяется внутренниг-ш времязада ощ,нми цепями в осковном - суг марнмм временем накопления заряда в базах п р-п-транзистора 1 (или 2) и транзистора 19 уси.пительного зле- , мента. В инжекционных системах это время можно регулировать Б широких пределах, изменяя уровень тока инжек- ции, и можно подобрать такую частоту фазовык импульсов,, чтобы инпупъсы на вь ходах регистра были во времени узьяотнекы, т„е. чтобы окончание пульса ка выходе совпадало с началом импульса на ()-м, Длительности -ш1гшьсов Ф( и Ф,,не являются крктичньвШ} они могут быть укорочен- 55 ными (например 5 как покд.зано пункти™ ром на диаграмГ ах ajb) Минимальная длительность иг-шульса фазы определяется временем заряда базы транзистора 4, а затем разряда через его коллекторы баз транзисторов I и 2. после этого ток инжекции по данной фазе может быть прекращен, поскольку в ненагруженном тра нзисторе заряд в базе. пекоторое время сохраняется

С - -изтывание произзод.ктсн по импуль- )М о с у Ф 3 а н е с е ни г м ма р к е р к о го О з i-й разряд регистра По следующему

40

импульсу Ф формирует ся импульс на J.-M его вьлходе, в О парекпючаатся (1- |) й триггер,; в Г БОЗЕратцается 1--й„ ияфоркационкое слово из (1-1 )й ЗД заносятся в , Затем по импульсу Ф( аналогичным rjOpasoM форг-дарует- ся импульс на (1-1)- м выходе и т.д. Маркерная О продвигается по регистру до тех nopj пока не достигнет г раничгюго разряда. Если гргк - чны м бьш i-й разряд у то он переключается в О 5, после чего граничным с гановит- ся уже (1-|-1)-й За та.;сок цикл массив хранимых в ЗУ даккы,;-: сдвигается на одну ЧЛ R выходу Фор№фование имггуль С-ОБ внутрекни и времязздаювщми депя- г-5к происходит так r-ice,; как н при запи

с

3 структуре регистра заложено на ,цежное вре меккоб: разделение зкутрек-. лих сигналов,; кгяудай триггер переключается в О и Г по разным фазам И1.шульсь: на двух соседних выходах регистра так же фор шру;отся по разным фазам и не перекрываются; вследствие этого не вознир;ает сквозных переносов и конфликтньк ситуаций при одновременном считывании к записи - яа.пнсь и считывание возможны по каждо- угу импульсу Ф, ,

Б регистре кет необходимости иметь устаковочн по цепь типа Начальный сброс, поскольку под действием фаз в правой части регистра всегда накапливаются 1, аз левс1Й части О „ Чтобы подготовить регистр к г аботе необходимо после включения питания по,дать серии импульсов Считывание ,и тем самым очистить регистр.

Дд7я нараЕЩвгния емкости буферного ЗУ вход 15 и выход 17 предыдзлдего регистра соединяготся соответственно с выходом i 3 и входом 11 последующего

Предлагаегсый регистр упрощен,, поскольку в ка;1сдом разряде содерйшт, усилителханого элемента, всего

ij 0 5

п

5

0

импульсу Ф формирует ся импульс на J.-M его вьлходе, в О парекпючаатся (1- |) й триггер,; в Г БОЗЕратцается 1--й„ ияфоркационкое слово из (1-1 )й ЗД заносятся в , Затем по импульсу Ф( аналогичным rjOpasoM форг-дарует- ся импульс на (1-1)- м выходе и т.д. Маркерная О продвигается по регистру до тех nopj пока не достигнет г раничгюго разряда. Если гргк - чны м бьш i-й разряд у то он переключается в О 5, после чего граничным с гановит- ся уже (1-|-1)-й За та.;сок цикл массив хранимых в ЗУ даккы,;-: сдвигается на одну ЧЛ R выходу Фор№фование имггуль С-ОБ внутрекни и времязздаювщми депя- г-5к происходит так r-ice,; как н при запи

с

3 структуре регистра заложено на ,цежное вре меккоб: разделение зкутрек-. лих сигналов,; кгяудай триггер переключается в О и Г по разным фазам И1.шульсь: на двух соседних выходах регистра так же фор шру;отся по разным фазам и не перекрываются; вследствие этого не вознир;ает сквозных переносов и конфликтньк ситуаций при одновременном считывании к записи - яа.пнсь и считывание возможны по каждо- угу импульсу Ф, ,

Б регистре кет необходимости иметь устаковочн по цепь типа Начальный сброс, поскольку под действием фаз в правой части регистра всегда накапливаются 1, аз левс1Й части О „ Чтобы подготовить регистр к г аботе необходимо после включения питания по,дать серии импульсов Считывание ,и тем самым очистить регистр.

Дд7я нараЕЩвгния емкости буферного ЗУ вход 15 и выход 17 предыдзлдего регистра соединяготся соответственно с выходом i 3 и входом 11 последующего

Предлагаегсый регистр упрощен,, поскольку в ка;1сдом разряде содерйшт, усилителханого элемента, всего

три п-р-п-траьзистора и совмещенные с ними нагрузочные р-п-р-транзисторы. Упрощение, достигнутое за счет совмещения функциональных узлов регистра, обеспечивается благодаря использованию особых свойств инжекционных п-р-п-р-транзисторных структур; возможности регулирования в широких пределах задержки срабатывания п-р-п- транзисторов (и,в частности, триггер- ных структур, не нарушая при этом их устойчивости) и удобства составления ло1 ического элемента простым

объединением двух выходов на один вход - базу п-р-п-транзистора.

Упрощение регистра позволяет значительно увеличить емкость буферного ЗУ. Расчетный вариант буферного ЗУ (по стандартной технологии Изо- планар с 4-мкм-транзисторами), содержащего предлагаемый регистр и регистровый накопитель: емкость 4 кбит (организация 512 х 8 разрядов), максимальная частота фаз (записи- с читывания) 8 МГц, длительность импульсов Ф , Ф. 50-60 НС.

W

f/T

иг.1

Фиг. 2

IB

Г0,

rO-JTl

Редактор В.Петраш

Составитель Л.Амусьева

Техред Л.Сердюкова Корректор В.Романенко

Заказ 5450/46

Тираж 590

ВПИИПИ Государственного комитета СССР

по делам изобретений и открытии 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Буферное запоминающее устройство | 1980 |

|

SU974411A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Микроэлектроника, 1982, т.11, вып.5, с.434, рис.3. | |||

Авторы

Даты

1988-10-23—Публикация

1985-04-15—Подача