(5) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО КОДИРОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| Аналого-цифровой преобразователь биполярных сигналов | 1981 |

|

SU1018231A1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU750727A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1078608A1 |

| Устройство для контроля аналоговых объектов | 1986 |

|

SU1397941A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Преобразователь напряжение-код | 1977 |

|

SU661784A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU938396A1 |

| Аналого-цифровой преобразователь поразрядного кодирования | 1980 |

|

SU936418A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

Изобретение относится к устройствам аналого-цифрового преобразования и может быть использовано в вычислительной и измерительной технике.

Известен аналого-цифровой преобразователь поразрядного кодирования, содержащий сумматор, блок сравнения и ключ в каждом разряде(1.

Однако устройство имеет недостаточное быстродействие.

Известен аналого-цифровой преобразователь поразрядного кодирования, содержащий первый, второй, третий и п-ный сумматоры, первый, второй, третий и п-ный блоки сравнения, а также первый, второй и третий ключи, причем первые входы ;всех блоков сравнения подключены к шине опорного напряжения Uon-, а вторые входы - к выходам одноименных сумматоров, входы которых подключены к шине кодируемого напряжения U, первые входы второго, третьего и п-ного сумматоров через первый ключ подключены к первому входу первого сумматора и к шине первого эталонного напряжения Ugr-i вторые входы третьего и п-го сумматоров через второй ключ подключены ко второму входу второго сумматора и к шине второго эталонного напряженйй третий вход П-DO сумматора через третий ключ подключен к третьему входу третьего сумматора и к шине третьего эталонного напряжения U а п-ый вход п-го сумматора подключен к шине одноименного эталонного напряжения кроме того, управляющие входы первого, второго и третьего ключей соединены с выходами

10 соответственно первого, второго и третьего блоков сравнения .2

Недостатком устройства является невысокое быстродействие, обусловленное переходными процессами в це15пи последовательно соединенных: первых - сумматора, блока сравнения и ключа, вторых - сумматора, блока сравнения и ключа, третьих - сумматора, блока сравнения и ключа и п-х сум20матора и схемы сравнения. Лишь после завершения переходных процессов в « этой цепи на выходах блоков сравнения получают код N, являющийся цифровым эквивалентом величины кодируемого

25 напряжения 0.

Цель изобретения - повышение быстродействия преобразования.

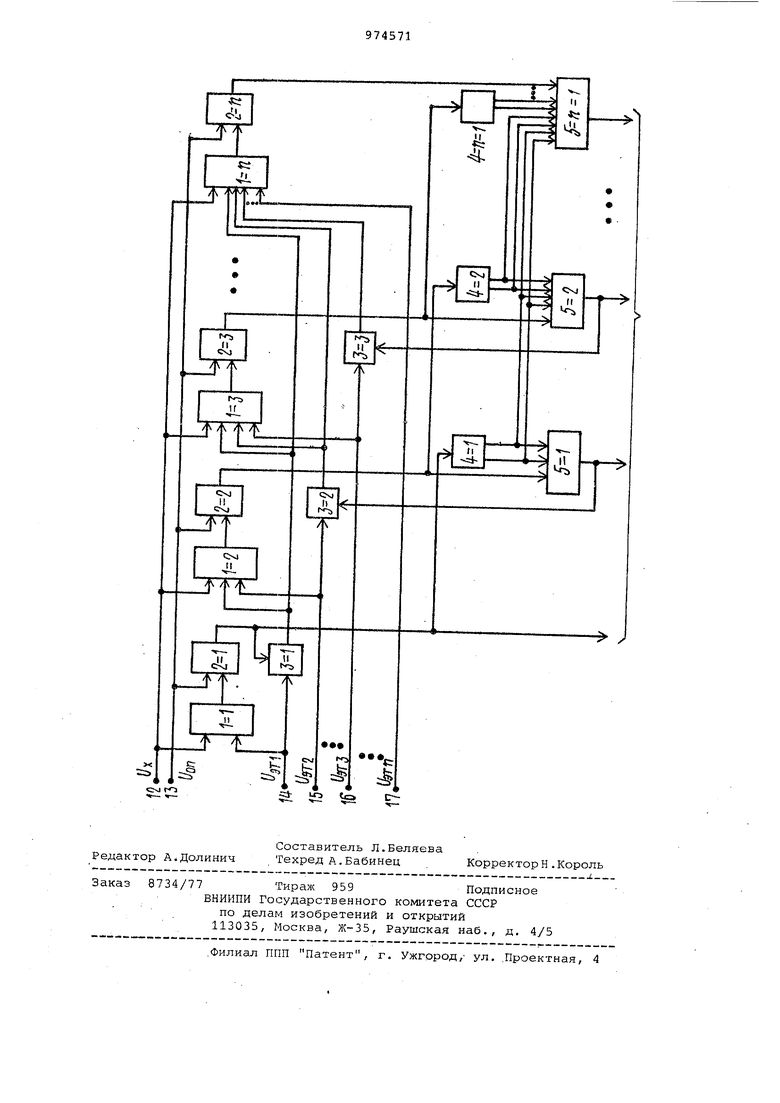

Поставленная цель достигается тем, что в аналого-цифровой преобра30зователь поразрядного кодирования. содержащий n-сумматоров, первьле вхо ды которых подключены к шине входно сигнала, шина первого эталонного на пряжения подключена ко второму вход первого сумматора и через первый ключ - к вторым входам СО второго по п-ый сумматоры, шина второго эта лонного напряжения подключена к тре тьему входу второго сумматора и через второй ключ - к третьим входам с третьего по п-ый сумматор, аналогичным образом подключены с третьей по (п-1)-ю шины эталонных напряжений, а шина п-го эталонного на пряжения подключена к n+1-y входу п-го сумматора, выходы п сумматоров соответственно подключены к первым входам п компараторов, вторые входы которых подключены к шине опорного напряжения, выход первого компарато ра подключен к управляющему входу первого ключа, введены п--1 логических блоков и п-1 цифровых блоков сравнения, входы которых соединены соответственно с выходами с первого по n-1-й компаратор, а выходы со второго по,п-й компаратор сое динены соответственно с первыми входами с первого по (п-1)-и логических блоков, вторые и третьи входы которых соединены с соответствующими выходами первого цифрового блока сравнения, четвертый и пятый входы с второго по ()-й логических блоков соединены соответственно с первым и вторым выходами второго цифрового блока сравнения, аналогично подключены входы с третьего по И -2 логических блоков с выходами с третьего по(и-2 п,ифровых блоков сравнения, при этом(2ц-2)-ой и(2ивходы Си-17-го логического блока под ключены соответственно к первому и второму выходам (и -1 Ьго цифрового блока сравнения, а выходы с первого по СИ-2)-й логических блоков, подсое цинены соответственно к упра вляющим входам со второго по (и-1)-и ключ. На чертеже представлена функциональная схема аналого-цифрового преобразователя поразрядного кодирования. Преобразователь содержит п сумматоров 1-1, 1-2, 1-3,.1-п, п компараторов 2-1, 2-2, 2-3, 2-п, (п-1) ключей 3-1, 3-2, 3-3, (n-i) цифровых блоков 4-1, 4-2, 4-П-1, сравнения (п-1) логических блоков 5-1, 5-2 5-п-1 . Аналого-цифровой преобразователь работает следующим образом. Кахсдый п -1 компаратор 1 осущест ляет операцию сравнения опорного напряжения 0 с выходным напряжением соответствующего сумматора Uji. При этом на его выходе формируется сигнал S логической 1, если Uj- г UQP , и сигнал логического О, если Uj.. . Каждый -1 цифровой блок сравнения выполняют операцию сравнения предыдущего состояния сигнала S. , t-1, на выходе -i -го компаратора с настоящим , и формируют на своих выходах сигналы логических 1 и О в соответствии с выражениями 1 S,-tH, 2,,а Ч Ч-tH, где Zy 2. сигналы соответственно на первом ивтором выходах )-ого цифрового блока сравнения. Выходные сигналы о(.2.г ъ соответственно первого, второго и П-1-ГО логических блоков 5 определяются следующими выражениями o6,--(Sa,,3), } ,. 2.. VZ,VZ2.a.i(2; cin4Svi,-t 2.3.. гг Предположим, что величина кодируемого напряжения Uy такова, что ей соответствует цифровой эквивалент N Ы(, 2,,,.. о/и 010, ...0. Предполохсим также, что величина и у уменьшается и становится такой, что этому значению U у должен соответствовать цифровой эквивалент (код)М 001, . , .,1. При этом на выходе второго компаратора 2-2 сигнал Зд изменяется с логической 1 на логический О, что приведет к формированию сигнала логической 1 на втором выходе второго цифрового блока сравнения 4--2, т.е. Т, а это в свою очередь, приводит к изменению сигналов otj. , 0(9,, и в соответствии с вырахчениями CU U), (3) о , oti 1,о(у, 1, Сигнал d остается неизменным. Таким образом, на выходе аналого-цифрового преобразователя получаем код , ...,1. В соответствии с изменением 0(2 и of-j, одновременно происходят переходные процессы в цепи-второй ключ 3-2, третий сумматор 1-3 и в цепи третий ключ 3-3, п-й сумматор 1-п. После этого любое новое изменение величины кодируемого напряжения U передается на выход аналого-цифрового преобразователя по истечении переходных Процессов в какой-либо из компараторов. Таким образом, на получение очередного кода напряжения Uy затрачивается время, равное Т. Предположим теперь, что величина кодируемого напряжения Uyначинает увеличиваться и становится такой, что ей должен соответствовать код N 010,,..О, При этом, на выходе второго компаратора 2-2 сигнал S, изменяется с логического () на лог ческую 1, что приводит к появлени сигнала логической 1 на первом вы де второго цифрового блока сравнения 4-2, т.е. 2, что, в сво очередь, приводит к изменению . I ci и в соответствии с выра жениями (1), (2;,(3);ot.j;rl, , Сигнал of. остается неизменным. Таким образом, на выходе аналого-цифрового преобразователя получают код , В соответствии с изменением oL и в(.-,- в схеме преобразователя происхо дят переходные процессы и аналогично предыдущему через отрезок времени равный Т на выходе аналого-цифровог преобразователя может быть получен очередной код. Таким образом, быстродействие пре лагаемого аналого-цифрового преобразователя по сравнению с прототипом больше в п раз, при условии, что кодируемое напряжение Uy за отрезок времени, равный Т, изменяется не более чем на один квант. Формула изобретения Аналого-цифровой преобразователь поразрядного кодирования, содержащий h сумматоров, первые входы которых подключены к шине входного сигнала, шина первого эталонного напряжения подключена ко второму входу первого сумматора и через первый ключ к вторым входам со второго по п-ый сумматоры, шина второго эталонного напряжения подключена к третьему входу второго сумматора и через второй ключ - к третьим входам с третьего по п-ый сумматор, аналогич ным образом подключены с третьей по (п-1)-ю шины эталонных напряжений, а шина п-ного эталонного напряжения .подключена к п + 1-у входу i-io сумматора, выходы п-сумматоров соответственно подключены к первым входам п компараторов, вторые входы которых подключены к шине опорного напряжения, выход первого компаратора подключен к управляющему входу первого ключа, отличающийс я тем, что, с целью повышения быстродействия, введены п-1 логических блоков и п-1 цифровых блоков сравнения, входы которых соединены соответственно с выходами с первого по (п-1)-и компаратор, а выходы со второго по п-й компаратор соединены соответственно с первыми аходами с первого по (п-1)-и логических блоков, вторые и третьи входы которых соединены с соответствующими выходами первого цифрового блокасравнения, четвертый и пятый входы со второго по (п-1)-и логических блоков соеди ены соответственно с первым и вторым выходами второго цифрового блока сравнения, аналогично подключены входы с третьего по п-2 логических блоков с выходами с третьего по (п-2) цифровых блоков сравнения, при этом (2п-2) -ой(2п-1)-й входы (п-1)-го логического блока подключены соответственно к первому и второму выходам (п-1)-го цифрового блока сравнения, а выходы с первого по (п-2)-и логических блоков подсоединены соответственно к управляющим входам со второго по (п-1)-и ключ. Источники информации, принятые во внимание при экспертизе 1.Смолов В.Б. и др. Полупроводниковые кодирующие и декодирующие преобразователи напряжений. Л., Энергия, 1967, с.139. рис. 2-7. 2. Электроника, 1976, № 3, с.53-55.

Авторы

Даты

1982-11-15—Публикация

1981-01-16—Подача