(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1981 |

|

SU985788A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1008742A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1007106A1 |

| Устройство микропрограммного управления | 1981 |

|

SU1007107A1 |

| Микропрограммное устройство управления /его варианты/ | 1984 |

|

SU1242943A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Микропрограммное устройство управления | 1981 |

|

SU964639A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1536380A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при проектировании устройств управления микропрограммных ЭВМ .

Известно микропрограммное устройство, содержащее счетчик, дешифратор, блок памяти, регистр, генератор, элементы И, ИЛИ Г 1 .

Недостатком указанного устройства является низкая экономичность блока памяти, обусловленная тем,, что если в формат линейки не помещается целое число микрокоманд, то часть блока памяти остается не заполненной инфор- ,5 мацией. В результате этого блок памяти.используетсп не эффективно.

Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому изоб- 20 ретению является устройство 2.

Недостатком этого устройства является низкая экономичность блока памяти, обусловленная невозможностью

использования всек ячеек памяти, если при записи целого числа микрокоманд в линейку блока памяти остается ячеек больше, чем половина длины микрокоманды.

Целью изобретения является повышение экономичности.

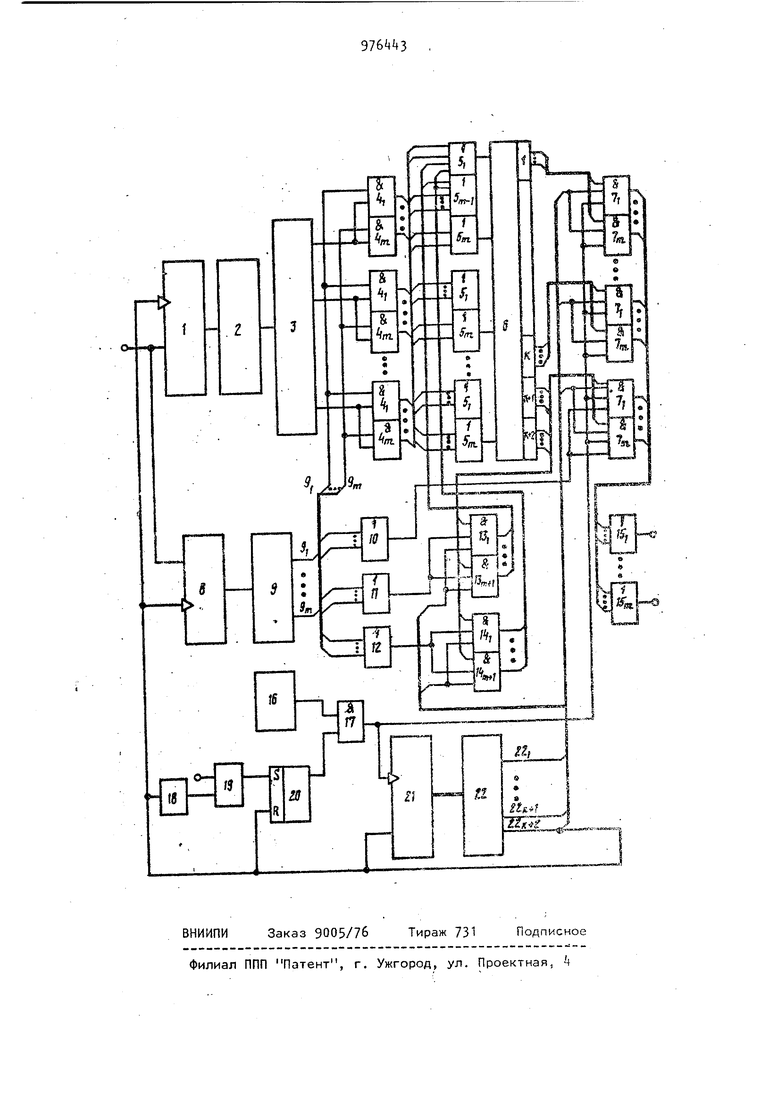

Поставленная цель достигается тем, что устройство, содержащее первый счетчик, информационный вход которого подключен к входу начального адреса устройства, а выход соединен с входом первого дешифратора, выход которого соединен с адресным входом блока памяти микрокоманд, каждый нз М (М-формат линейки блока памяти микрокоманд) выходов которого соединен с первыми входами m (гп-формат микрокоманды) элементов И группы из соответствующих М групп, а вторые входы элементов И т-ой группы соединен с выходами второго дешифратора соответственно, вход которого соединен с выходом второго счетчика, выходы элементов ИМ группсоединены с соответствующими входами элементов ИЛИ СК+2) групп (К-копичество микрокрманд в одной линейке), выходы которых соединены с информационными входами регистра, m выходов первой группы которого подключены к первым входам m элементов И.группы из .(+0 групп соответственно, выходы которых соединены с входами m элементов ИЛИ (К+З) группы, выходы которых ПОДКЛК5чены к выходу микрокоманд устройства вторые входы каждого элемента И (К+1) групп подключены к выходу элемента И, а третьи входы - к (К+1) выходам третьего дешифратора соответственно, вход которого соединен с выходом тре тьего сметчика, счетный вход которо г,о соединен с выходом элемента И, первый вход которого соединен с генератором тактовых импульсов, а втоорой - с единичным выходом триггера, едичный вход которого подключен к выходу первого элемента ИЛИ, первый вход которого подключен к управляющему входу устройства, а второй вход к выходу элемента задержки, дополнительно содержит первую И втрру.ю группы (т-1) элементов И, второй, третий и .четвертый элементы ИЛИ, гфичем первые входы (т-1) элементов И первой группы подключены к выходу второго элемента ИЛИ, вторые входы к выходам второй гпуппы регистра со 9тветственно, третои входы (л1-1) элементов И первой группы соединены с (К+2)-ым выходом третьего дешифратора, а выходы - с третьими входами (т-1) элементов ИЛИ первой групгш из (К+2) групп, четвертые входы которых подключены к выходам (т-1) элементов И второй группы, первые входы которых соединены с выходом третьего элемента ИЛИ, входы которого подключены к выходам второго дешифратора второй группы, вторые входы (т-1) элементов И второй группы подключены к (К+2)-му выходу третьего дешифратора и к входам сброса триггера и третьего счетчика, входу элемента задержки, счеткым входам первого и второго счетчиков, третьи входы (т-1) элементов И второй группы соединены с информаЦИП1-1ЯЫМИ выходами второй группы регистра, информационный вход второго с-етчика соединен с входом начально-0 адреса регистра, выходы третьей . , уппь, эгорого дешифратора подключены -. входам четвертого элемента ИЛИ, 97 34 выход которого соединен с четвертыми входами элементов И (К+1)-ой группы. На чертеже изображена функциональная схема микропрограммного устройСтва управления. Предлагаемое устройство содержит счетчик 1, дешифратор 2, блок 3 памяти микрокоманд, М групп элементов И , (К+2) группы элементов ИЛИ 5, реТ-истр 6, (К+1) группы элементов И 7, счетчик 8, дешифратор 9, элемент ИЛИ 10, элементы ИЛИ 11, 12, (К+2) группу Элементов И 13, (К+З) группу элементов И И, (К+З) группу элементбв ИЛИ 15, генератор 16 тактовых импульсов, элемент И 17, элемент 18 задержки, элемент ИЛИ 19, триггер 20, счетчик 21, дешифратор 22. Устройство работает следующим образом. Начальный адрес поступает на первый вход счетчика 1 и второй вход счетчика 8. По информации на выходе счетчика 1 дешифратор 2 выбирает нужную линейку микрокоманд в блоке памйти. По информации на выходе счетчика 8 дешифратор 9 открывает один из элементов И в аждой из групп k. Линейка микрокомандчерез выбранные элементы И i и элементы ИЛИ 5 записывается в регистр. МикрокоманДЫ из регистра 6 считываются поочередно через группы элементов 7 и элементов ИЛИ 15 на выход устройства при наличии сигнала с дешифратора 22 и генератора 16, причем с (К+1)-ой группы выходов регистра 6 микрокоманда считывается также при наличии сигнала с выхода элемента ИЛИ 10. С (К+1)-ой группы выходов регистра 6 через (К+2) группу элементов И 13 и с (К+2)-ой группы выходов через (К+З) группу элементов И часть микрокоманды переписывается в первые разряды при сигнале с . (К+2)-го выхода дешифратора 22 и при наличии сигналов на выходе элемента ИЛИ 11 и элемента ИЛИ 12 соответственно. По сигналу с второго входа устройства, поступающему на первый.вход элемента ИЛИ 19, триггер 20 устанавливается в 1. Сигнал с прямого выхода триггера разрешает прохождение тактовых импульсов с генератора 16 через элемент И 17 на счетный вход счетчика 21 и вторые входы элементов И 7. По соетоянию счетчика 21 дешифратор 22 считывает микрокоманды. После считывания целых микрокоманд, по сигналу с (К+2)-го выхода дешифратора 22 часть микрокоманды переписывается в первые разряды регистра 6, устанав ливаются в О триггер 20 и счетчик 21, увеличивается содержимое счётчиков 1 и 8 на единицу. Сигналом с выхода элемента 18 задержки триггер 20 устанавливается в 1 и начинается процесс считывания следующей линейки микрокоманд. На первый вход устройства, которым являются первый вход счетчика 1 и второй вход счетчика 8, поступает начальный адрес. По начальному адре су, записанному в счетчике 1, дешифратор 2 выбирает в блоке 3 памяти линейку микрокоманд. По начальному адресу, записанному в счетчике S, дешифратор 9 выбирает один элемент из каждой группы , и микрокоманды с блока 3 памяти считываются через элементы И М групп и элементы ИЛИ (К+2) групп 5 и записывается в регистр 6. По сигналу, поступающему на второ вход устройства, который проходит че рез элемент ИЛИ 1Э, триггер 20 устанавливается в единичное состояние, с прямого выхода триггера 20 разрешается прохождение тактовых импульсов с генератора 16 через элемент И 17. Тактовые импульсы поступают на счетный вход счетчика 21. По состоянию- счетчика 21 де1иифратор 22 выбирает по очереди одну из групп элементов И 7. При наличии сигнала с де шифратора 22 и тактового импульса с генератора 16 микрокоманда считывает ся с регистра 6 и через группу элементов И 7 и группу элементов ИЛИ 15 поступает на выходы устройства. Информация и микрокомандах в (К+1)-ой и (К+2)-ой частях регистра 6 соответствует позиционному коду на выходе дешифратора 9. Если в (К+1)-ой ячейке записана целая микро команда, то при наличии сигналов на выходе элемента ИЛИ 10, на (К+1)-ом. выходе дешифратора 22 и тактового импульса с генератора микрокоманда считывается с (К+1)-ой ячейки регист ра через (К+1) группу элементов И 7 и группу элементов ИЛИ 15. Если в (К+2)-ой ячейке нет информации, то по сигналу на (К+2)-ом выходе дешифратора 22 счетчик 21 и триггер 20 устанавливаются в О, содержимое счетчиков 1 и 8 увеличивается на единицу. По новому адресу дешифратор 2 выбирает.в блоке 3 памяти очерёдную линейку микрокоманд. Дешифратор 9 выбирает соответствующие элементы И t. Считанные с блока 3 памяти микрокоманды через элементы И и элементы ИЛИ 5 записываются в регистр 6, начиная с первого разряда. Сигнал с (К+2)-го выхода дешифратора 22, пройдя через элемент 18, элемент ИЛИ 19, вновь устанавливает триггер 20 в единичное состояние. Начинается считывание микрокоманд с регистра, 6. Если после считывания целых микрокоманд в (К+1)-ой ячейке нахо с;ится часть микрокоманды, то устройство работает-следующим образом. При появлении сигнала на (К+1)-ом выходе дешифратора 22 и при наличии сигнала на выходе элемента ИЛИ 11 часть микрокоманды с (К+1)-ой ячейки через (К+2) группу элементов И 13 и первую группу элементов ИЛИ 5 переписывается в первые разряды регистра 6. По сигналу с (К+2)-го выхода дешифратора 22 устанавливается в О триггер 20 и счетчик 21, а также увеличивается на единицу содержимое счетчиков 1 и 8. После этого начинается считыван1/ ё очередной линейки микрокоманд. Однако в регистр в микрокоманды записываются и оставшиеся незаполненными разряды. Если в (К+1)-ой ячейке записана целая микрокоманда, а в (К+2)-ой часть другой микрокоманды, (К+1)-ом такте считывается целая микрокоманда, как было описано выше. По сигналу с (К+2)-го выхода дешифратора 22 и сигналу на выходе элемента ИЛИ 12 часть микрокоманды и;. (К+2)-ой ячейки через (К+3) группу элементов И Tt и первую группу элементов ИЛИ 5 записывается в первые разряды регистра 6. Далее работа устройства аналогична случаю,когда часть микрокоманды записана в (К+1)-ой ячейке регистра 6. Выигрыш в экономичности сохраняется за счет исключения из схемы счетчика и. дешифратора. Предлагаемое микропрограммное устройство полностью использует весь объем блока памяти. Благодаря этому повышается экономичность всего устройства, -достигается более высокая производительность и надежность. . Формула изобретения Микропрограммное устройство управления, содержащее первый счетчик, информационный вход которого подключен к входу начального адреса устройства, а выход соединен с входом первого дешифратора, выход которого соединен с адресным входом блока памяти микрокоманд, каждый из М (М-формат линейки блока памяти микрокоманд) выходов которого соединен с первыми входами m (m-формат микрокоманды) элементов И группы из соответствующих И групп. а вторые входы элементов И т-ой группы соединены с выходами второго дешифратора соответственно, вход которого соединен с выходом второго счётчика, выходы элементов И М групп соединены с соответствующими входами элементов ИЛИ (К+2) групп (К-количество микрокоманд в одной линейке), выходы которых соединены с информационными входами регистра, m выходов первой группы которого подключены к первым входам m элементов И группы из (К+1) групп соответственно, выходы которых соединены с входами m :элементов ИЛИ (К+3) группы, выходы , которых подключены к выходу микрокоманд устройства, вторые входы каждого элемента И (К+1) групп подключены к выходу элемента И, а третьи входы к (К+1) выходам .третьего дешифратора соответственно, вход которого соединен с выходом третьего счетчика, счетный вход которого соединен с выходом элемента И, первый вход которого соединен с генератором тактовых импульсов, а второй - с единичным выходом триггера, единичный вход которого подключен к выходу первого элемента ИЛИ, первый вход которого подключен к управляющему входу устройства, а второй вход - к выходу элемен- j та задержки, отличающееся 37

кл. G 06 F 9/22, 1981 (прототип). 38 тем, что, с целью повышения экономичности устройства, оно дополнительно содержит первую и вторую группы (т-1) элементов И, второй, третий и четвертый элементы ИЛИ, причем первые входы (ш-1) элементов И первой группы подключены к выходу второго элемента ИЛИ, вторые входы - к выходам второй группы регистра соответственно, третьи входы (т-1) элементов И первой группы соединены с (К+2)-ым выходом третьего дешифратора, а выходы - с третьими входами (т-1) элементов ИЛИ первой группы из (К+2) групп, четвертые входы которых подключены к выходам (т-1) элементов И второй группы, первые входы которых соединены с выходом третьего элемента ИЛИ, входы которого подключены к выходам второго дешифратора второй группы, вторые входы (т-1) элементов И второй группы подключены к (К+2)-му выходу третьего дешифратора и к входам сброса триггера и третьего счет.чика, входу элемента задержки, счетным входам первого и второго счетчиков, третьи входы (т-1) элементов И второй группы соединены с информационными выходами второй группы регистра, информационный вход второго счетчика соединен с входом начального is/i ре са регистра, выходы третьей группы второго дешифратора подключены к входам четвертого элемента ИЛИ, выход которого соединен с четвертыми входами элементов И (К+1)-ой группы. Источники информации, ринятые во внимание при экспертизе

Авторы

Даты

1982-11-23—Публикация

1981-05-04—Подача