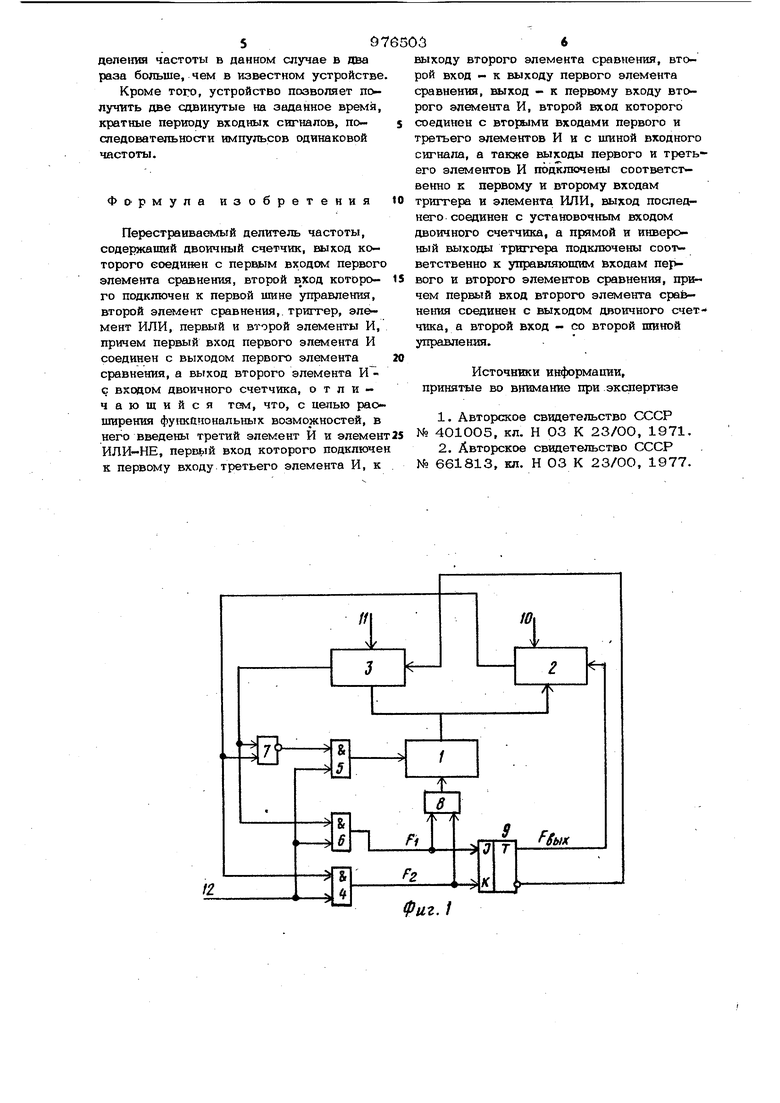

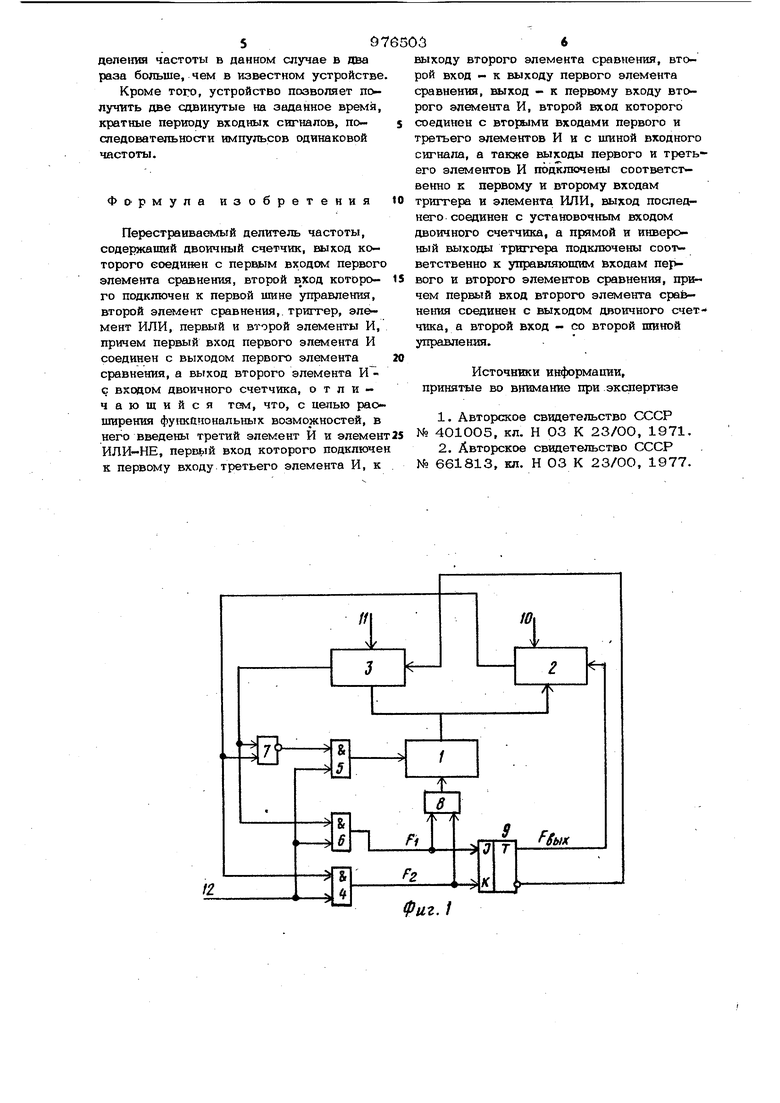

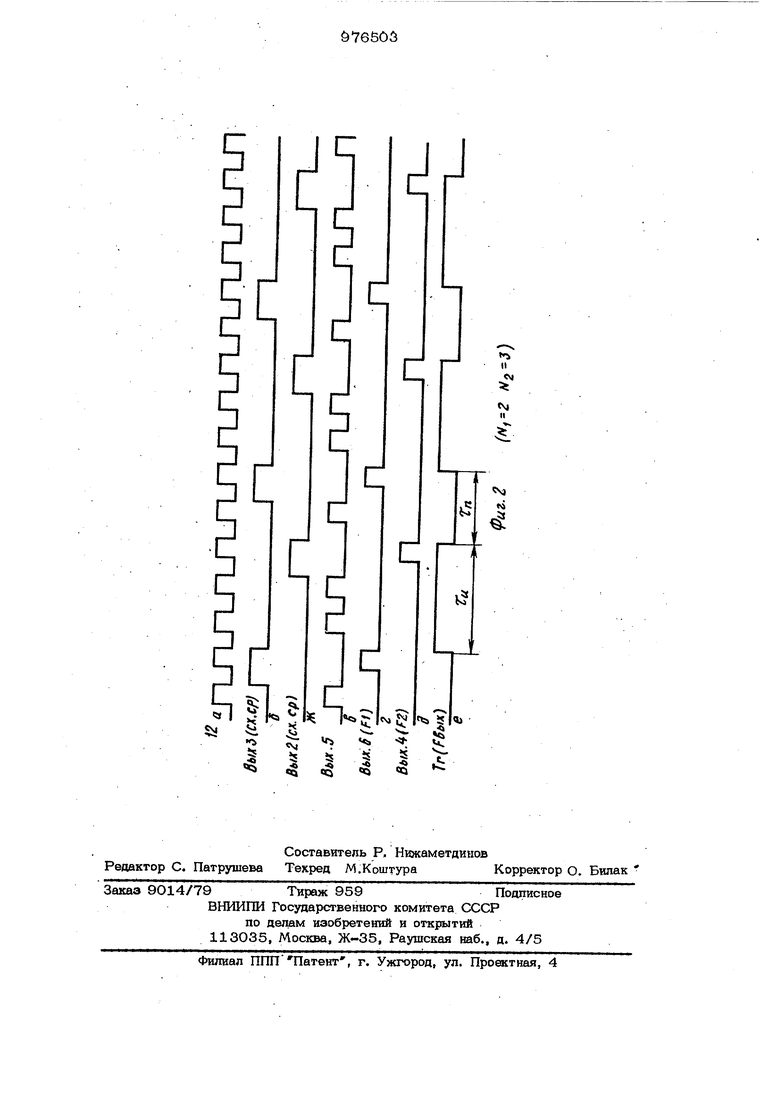

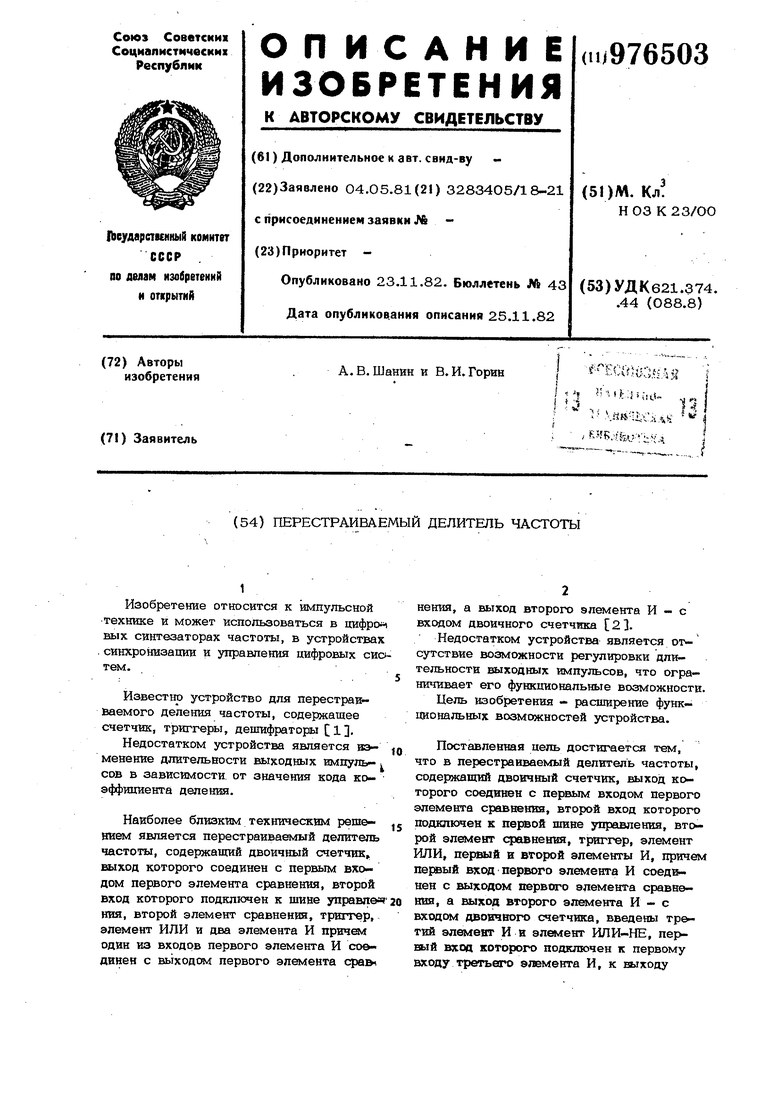

Изобретение относится к импульсной технике и может использоваться в цифро вых синтезаторах частоты, в устройствах . синхронизапии и управления цифровых сио тем. Известно устройство для перестраиваемого деления частоты, содержащее счетчик, триггеры, дешифраторы 1, Недостатком устройства является изменение длительности выходных импулЕ сов в зависимости от значения кода коэффициента делешш. Наиболее близким техническим решением является перестраиваемый делитель частоты, содержаишй двоичный счетчик выход которого соединен с первым входом первого элемента сравнения, второй вход которого подключен к шине управпеа ния, второй элемент сравнения, триггер, элемент ИЛИ и два элемента И причем один из входов первого элемента И соединен с вь1ходом первого элемента сра&ч нения, а выход второго элемента И - с входом двоичного счетчика 2. Недостатком устройства является отсутствие возможности регулировки длительности выходных импульсов, что ограничивает его функциональные возможности. Цель изобретения - расширение функциональных возможностей устройства. Поставленная цель достигается тем, что в перестраиваемый делитель частоты, содержащий двоичный счетчик, выход которого соединен с первым входом первого элемента сравнения, второй вход которого подключен к первой шине управления, второй элемент сравнения, триггер, элемент ИЛИ, первый н второй элементы И, причем первый вход первого элемента И соединен с выходом первого элемента сравнения, а выход второго элемента И - с входом двоичного счетчика, введены третий элемент И н элемент ИЛИ-НЕ, вход которого подключен к первому входу третьего элемента И, к выходу второго эпемента сравнения, второй вход к выходу первого элемента сравнения, выход - к первому входу второго элемента И, второй вход которого соединен с вторыми входами первого и третьего элементов И и с шиной входного сигнала, а также выходы первого и третьего элементов И подключены соответственно к первому и второму входам триггера и элемента ИЛИ, выход последнего соединен с установочным входом двоичного счетч№ка, а прямой и инверсный выходы триггера подключены соответственно к управляющим входам первого и второго элемен тов сравнетш, причем первый вход второ го элемента сравнения соединен с выходом двоичного счетчика, а второй вход со второй шиной управления. На фиг. 1 представлена структурная схема перестраиваемого делителя частоты; на фиг. 2 - временные диаграммы, объясняющие работу устройства. Устройство содержит двоичный счетчик 1, первый и второй элементы 2 и 3 сравнения, первый, второй, третий элементы 4-6 И, элемент 7 ИЛИ-НЕ, элемент 8 ИЛИ, триггер 9, первую и вторую шины 10 и 11 управления, шину 12 входного сигнала, причем выход двоичного счетчика подключен к первым входам первого -и второго элементов 2-3 сравнения, первые входы которых cooi ветственно соединены с шинами 10-11 управления. Первый вход счетчика 1 соединен с выходом второго элемента 5 И, второй вход - с выходом элемента 8 ИЛИ первый и второй входы которого соответственно подключены к выходам третьего и первого элементов 6,4 И и к первому и второму входам триггера 9, прямым и инверсным выходами соединенным соответственно с BtopbiM входом первого и второго элемента 2 и 3 сравнения. Выход первого элемента 2 сравнения подключен к второму входу элемента 7 ИЛИ НЕ и к первому входу элемента 4 И, второй вход которого соединен с вторыми входами второго и третьего элементов 5 и 6 И и с шиной 12 входного сигнала. Выход второго элемента 3 сравнения сое динен с первыми входами элементов 7, 6 ИЛИ-НЕ и И. Устройство работает следующим образом. Пусть содержимое счетчика 1, изменяемое синхронно с заданным фронтом очередного импульса шины 12 (фиг. 2а), поступившего на его вход с выхода элемента 5 И, оказалось значению кода элемента 3 сравнения. Тогда на ыходе элемента 3 сравнения сформируется единичный поте1шиал (фиг. 26), который через элемент 7 ИЛИ-НЕ запретит прохождение импульсов шины 12 через элемент 5 И (фиг. 2в) на счетный вход счетчика 1, поступая на вход элемента 6 И (фиг. 2г), откроет его для прохождения импульсов шины 12. Задним фронтом следующего импульса с выхода эл&мента 6 И через элемент 8 ИЛИ в счетчик 1 запишется 1 в первый разряд и О в остальные разряды. Добавление единицы к начальному состоянию счетчика 1 связано с тем, что импульс начальной установки выделяется из последовательности счетных импульсов, уменьшая их количество на единицу. В тот же момент времени триггер С) переключается в состояние 1 (фиг. 2е), при этом на управляющий вход элемента 3 сравненгш поступит нулевой потенциал, запрещаюишй сигнал равенства, а на управлйющий вход элемента 2 сравнения единичный потенциал разрешения. При достижении счетчиком 1 состояния, равного значению кода элемента 2 сравнения, элемент 2 сравнения сформирует единичный сигнал равенства (фиг.2ж) и шпш работы устройства повторится, причем в данном случае импульс начальной установки счетчика 1 появится на выходе элемента 4 (фиг. 2д), а триггер переключается его задним фронтом в состояние ноль. Период следования выходных импульсов, снимаемых с единичного плеча триггера 9, определяется произведением периода входных импульсов шины ±2 на сумму значения кодов элементов сравнения, где обратное значение суммы кодов составляет коэффициент деления. Длительность выходных импульсов равна произведению значения кодов первого элемента сравнения на период входных импуль сов шины 12, а продолжительность паузыпроизведению значения кодов второго элемента сравнения на период входных импульсов шины 12. Таким образом, предлагаемый перестраиваемый делитель частоты обладает широкими функционалыа 1ми возможностями, заключающимися в том, что в нем реализовано как произвольные изменения частоты, так и длительности выход1а1х иМиульсов и паузы между ними, причем диапазон изменения коэффициента деле1пга частоты в данном случае в два раза больше, чем в известном устройстве Кроме того, устройство позволяет получить две сдвинутые на заданное BpeMia, кратные периоду входных сигналов, поспедоватепьности импульсов одинаковой частоты. Формула изобретения Перестраиваемый делитель частоты, содержащий двоичный счетчик, выход которого соединен с первым входом первого элемента сравнения, второй которого подключен к первой шине управления, второй элемент сравнения, триггер, элемент ИЛИ, первый и второй элементы И, причем первый вход первого элемента И соединен с выходом первого элемента сравнения, а выход второго элемента входом двоичного счетчика, отличающийся тем, что, с цепью расширения функциональных возможностей, в него введены третий элемент И и элемент ИЛИ-НЕ, первь1й вход которого подключе к первому входу третьего элемента И, к выходу второго элемента сравнения, второй вход - к выходу первого элемента сравнения, выход - к первому входу второго элемента И, второй вход которого соединен с вторыми входами первого и третьего элементов И и с шиной входного сигнала, а также выходы первого и третьего элементов И подключены соответственно к первому и второму входам триггера и элемента ИЛИ, выход последнего соединен с установочным входом двоичного счетчика, а прямой и инвероный выходы триггера подключены сооьветственно к управляющим Входам первого и второго элементов сравнения, причем первый вход второго элемента сравнения соединен с выходом двоичного счетчика, а второй вход - со второй пшной управления. Источники информации, принятые во внимание при эксяпертизе 1.Авторское свидетельство СССР № 401005, кл. Н 03 К 23/ОО, 1971. 2.Авторское свидетельство СССР № 661813, кл. Н 03 К 23/00, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный компаратор | 1983 |

|

SU1167719A2 |

| Перестраиваемый делитель частоты следования импульсов | 1981 |

|

SU995334A1 |

| Частотный компаратор | 1981 |

|

SU1023630A1 |

| Перестраивающий делитель частоты | 1977 |

|

SU661813A1 |

| Перестраиваемый делитель частоты | 1977 |

|

SU678672A1 |

| Устройство автоматической подстройки частоты | 1987 |

|

SU1539999A2 |

| Делитель частоты с переменным коэффициентом деления | 1976 |

|

SU657619A1 |

| Перестраиваемый делитель частоты | 1982 |

|

SU1023662A1 |

| Устройство автоматической подстройки частоты | 1985 |

|

SU1298915A1 |

| Устройство для сглаживания периодических случайных сигналов | 1981 |

|

SU982012A1 |

Фиг. I

Авторы

Даты

1982-11-23—Публикация

1981-05-04—Подача