(54) УСРЕДНЯЮЩЕЕ УСТРОЙСТВО С БЛОКИРОВКОЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU970717A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

| Устройство для синхронизации приемника телеграфных сигналов | 1980 |

|

SU970715A1 |

| Фазовый дискриминатор | 1982 |

|

SU1027799A1 |

| Устройство синхронизации | 1981 |

|

SU1003376A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU965005A2 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

1

Изобретение относится к радиотех- v нике.

Известно усредняющее устройство с блокировкой, содержащее фазовый дискриминатор, первый выход которогчэ подключен к первому входу первого реверсивного счетчика и к первому входу первого элемента И, второй вход которого соединен с выходом первого триггера, к входам которого подюиочены первые выходы первого коммутатора и первого реверсивного счетчика, второй выход которого соединен с первым входом второго ; триггера, выход которого подключен к первому входу второго элемента И, второй вход которого соединен с вторым выходом фазового дискриминатора и с вторым входом первого реверсивного счетчика, соответствующие выходы которого подключены к одним входам первого коммутатора, а также второй коммутатор, первый счетчик и последовательно соединенные первый элемент задержки в второй счетчик С11

Однако в известном устройстве точ ность недостаточна,.

Цель изобретения - повышение точноо. ти при воздействии помех..

Для достижения поставленной цели : в усредняюшее устройство с блокировкой, содержащее фазовый дискриминатор, первый выход шэторого подключен к первому

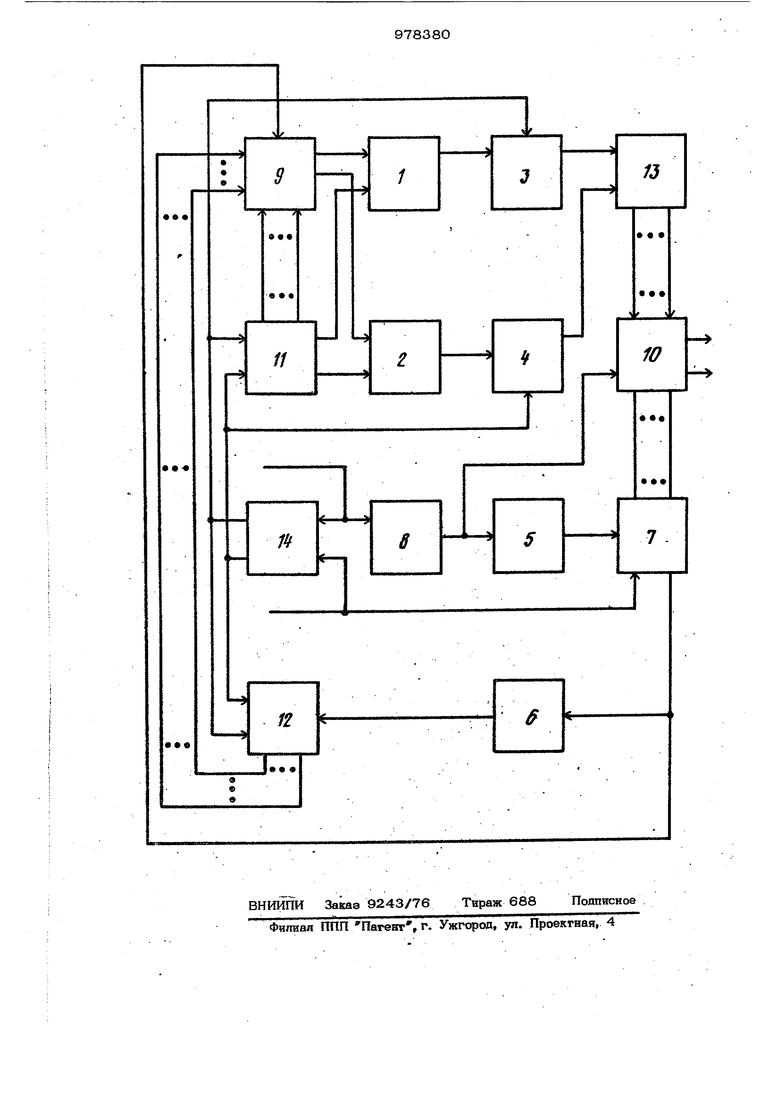

10 входу первого реверсивного счетчика в к первому входу первого элемента И, второй вход которого соеяинен с выходом первого трвггера, к вход(м которого подключены первые выходы первого мутатора, и первого реверсивного счег- чика, второй выход которого соединен с nepBbifM входом второго триггера, выход которого подключен к первому входу . ; второго элемента И, второй вход: кото20рого соединен с вторым выходом фазовое го дискриминатора и с вторым входом Iпервого реверсивного счетчика, соотват .ствующие выходы которого подключены к одним входам первого коммутатора, а также второй коммутатор,первый счетчик и последовательно соединенные первый элемент задерл{ки и второй счетчик, введены второй реверсивный .счетчик, и последовательно соединенные второй элемент задержки и третий реверсивный счетчик, выходы которого подклю чен%з к другим входам первого коммутато ра, соответствующий вход которого соединен с входом второго элемента задерж ки и с выходом второго счетчика, второй вход которого с оединен с первым входом фазового дискриминатора, второй вход ко торого соединен с входом первого счетчика. Выход которого подключен к входам первого элемента задержки и второго коммутатора, одни входы которого соединены с jвыxoдaми второго реверсивного счетчика, к входам которого подютючены выходы первого и второго элемента И, при этом второй выход первого коммутатора соединен с вторым входом второго триггера, первый и второй выходы фазов го дискриминатора подключены к соответствуюшЕМ входам третьего реверсивного счетчика, а соответствующие выход второго счетчика соединены с другими входами второго коммутатора. На чертеже изображена структурная электрическая схема предлагаемого устройства, Усредн5пощее устройство с блокиров. кой содержит триггеры 1 и 2, элементы ИЗ и 4, элементны 5 и 6 задержки, счетчики 7 и 8, коммутаторы 9 и 10, раверсивные счетчики 11-13, фазовый дискриминатор 14. Устройство работает следующим обраНа вход устройства поступает последовательность формируемых тактовых импульсов, следующих с частотой, близкой к скорости телеграфирования приним емых элементов сообщения, а на другой вход - фронты принимаемых элементов сообщения. Выходные сигналы предлагаемого устройства предназначены для коррекции частоты и фазы формируемых устройством тактовой синхронизации тактовых импульсов. Фазовый дискриминатор 14 анализирует взаимное месторасположение тактовых импульсов и фронтов принимаемых элементов сообщения и формирует коррек ирующие импульсы Добавления (форми руются по одному на кагкдый фронт элемента сообщения на первом выходе фазового дискриминатора, если фаза тактовых импульсов отстает от фазы принимаемых элементов сообщения) или вычитания (формируются по одному на каждый фронт принимаемых элементов сообщения на втором выходе -фазового дискриминатора, если фаза тактовых импульсов опережает фазу принимаемых элементов сообщения). Вследствие того, что элементы принимаемь:х сообщений подвергаются искажениям в канале связи, на выходах фазового дискриминатора 14 формируются как истинные, так и ложные корректирующие импульсы (как добавления, так и вычитания). Реверсивный счетчик 11, емкость которого,исходя из требований быстродействия, выбирается весьма малой, осуществляет первую ступень усреднения входных корректирующих сигналов. Если число импульсов добавления (вычитания), поступивщих на его первый (второй) вход, превысит на величину С (где - коэффициент пересчета реверсивного счетчика 11) число импульсов вычитания (добавления), поступивших на его второй (первый) вход, то на первом (втором) выходе реверсивного счетчика 11, который является выходом последнего разряда добавления (вычитания), т.е. после максимального усреднения, формируется импульс, устанавливающий триггер 1(2) в единичное состояние, вследствие чего последующие импульсы добавления (вычитания) проходят на выход элемента И 3 (4) без усреднения. Этим обеспечивается высокое быстродействие усреднения корректирующих импульсов. Сброс триггера 1 (2) в нулевое состо5шие осуществляется через коммутатор 9 сигналов с одного из промежуточных разрядов вычитания (добавления) реверсивного счетчика 11 сигналом с одного из его третьих выходов, т.е. частично усредненным сигналом противоположного корректирующего воздействия. Для обе печения точности и быстродействия усреднения выходных корректирующих импульсов устройства коэффициент частичного усреднения импульсов сброса блокировочных триггеров выбран изменяющимся автоматически в зависимости от режима работы устройства (режим устойчивой тактовой синхронизации, режим вхождения в синхронизм, режим устойчивости рассогласования частот передатчика и приемника, режим полного совпадения этих частот н т.д.), который характеризуется в первом приближении соотнощением числа корректирующих импульсов добавления и вычитания, сформи рованных на выхоаах фазового дискримргна ра 14 за определенный промежуток времен Этот промежуток времени должен быть достаточно велик (для суждения в уело ВИЯХ помех о режиме работы устройства анализу следует подвергнуть как миним в нескопъко раз большее число корректирующих импульсов, чем это позволяет емкость реверсивного счетчика 11. Анализ режима работы устройства осуществляется в реверсивном счетчике 12 за промежуток времени, определяемый периодом следования сигналов на втором выходе счетчика 7. При этом каждый импульс, формируемый на втором выходе счетчика 7, осуществляет перезапись показаний ( кода числа, имеющег ся в данный момент времени) реверсивного счетчика 12 в коммутатор 9, а спустя время задержки в элементе задержки 6 переводит реверсивный счетчик 12 ъ нулевое состо1шие, т.е. подготавливает его к новому процессу анализа режима работы устройства. Чем ближе показания реверсивного счетчика 12 к нулю, тем более вербятно, что фор мируемые на выходах фазового дискриминатора 14 корректирующие импульсы обусловлены помехами в канале связи. Поэтому коммутатор 9 в этом случае устанавливает малый коэффициент усреднения импульсов сброса блокировочных триггеров, т.е. коммутирует вторые входы триггеров 1 н 2 с выходами одних из пер- вых разрядов добавления и вычитания (или даже входов первых разрядов) реверсивного счетчика 11. Чем: больще от личаются показания реверсивного счетчи ка 12 от нуля, тем вероятнее, что корректирующие импульсы преобладающего знака (например, добавления) являются истинными и тем выше устанавливаемый коммутатором 9 коэффициент частичного усреднения корректирующих импульсов противоположного знака, т.е. импульсов сброса блокировочных триггеров (в данном случае импульсов вычита ния). Для повышения динамической точное,ти измерения реверсивным счетчиком 12 соотнощения корректирующих импуль JCOB разных знаков во времени, вследствие чего возрастает точность и помехоустойчивость усреднения выходны ; импульсов устройства, промежутки време ни, в течение которых распределяются режимы работы устройства, сделаны зависимыми от частоты воздействия фронтов принимаемых элементов сообщения на фазовый Дискриминатор 14 (опедует иметь в виду, что на каждый фронт принимаемого элемента сообщения фазовым дискриминатором 14 можёт быть сформировано не более одного корректирующего ил-шульса). Эта зависимость частоты воздействия на время анализа режима работы устройства реализуется посредством счетчика 7, на тактовый вход которого поступают фронты принимаемых элементов сообщения, вследствие чего c eтчик 7 заряжается, а на его втором выходе (выходе промежуточного разряда) периодически формируются импульсы, управляющие сбросом реверсивного счетчика 12 и вводом его показаний в коммутатор 9. Частота следования этих импульсов определяется частотой следования фронтов принимаемых элементов сообщения. Реверсивный счетчик 13 обеспечивает вторую ступень усреднения корректирующих импульсов, при этом частота .следования выходных корректирующих импульсов оказьгоается независимой от структуры принимаемых элементов сообщения, что повыщает точность и помехоустойчивость усреднения, а также создает более благоприятные условия для высокоточной коррекции частоты и фазы i формируемых устройством тактовой синхронизации (в состав которого входит предлагаемое устройство) тактовых импульсов. Это достигается следующим образом. Частота следования тактовых импульсов -на входе счетчика 8 и его емкость определяют период. времени, в течение которого производится анализ структуры принимаемых, элементов сообщения. Известно, что подстройка частоты и фазы тактовых импульсов производи-гся только по моментам перехода принимаемых элементов сообщения из одного состояния в другое (из единичного в левое и обратно). Кроме тогоjизвестно, что разные типы сообщений имеют различную структуру, т.е. характеризуются разной средней частотой чередования в сообщении единичных и нулевых элементов и их групп. При этом средняя статистическая структура сообщения сохраняется в течение достаточно больших промелсутков времени (от долей кодограммы до сотен и тысяч кодограмм). Учет этого. влияния осуществляется посредством коммутатора 1О и счетчика 7. Показания счетчика 7 в момент формироания импульса на выходе- счетчика 8,

характеризующие статическук- структуру принимаемых элементов сообщения, переписываются в коммутатор 10, вследствие чего первый и второй выходы коммутатора 1О подключены соответственно к выходам определенных разрядов добавления и вычитания реверсивного счетчика 13, т.е. устанавливается вполне определенный коэффициент усреднения корректирующих импульсов, сформированных на выходах элементов И 3 и 4. Чем вьпиё показания счетчика 7, тем больший коэффициент усреД1:ания выходных корректирующих импульсов устанавливается коммутатором 1О, вследствие чего обеспечивается практически полная независимость частоты следования выходных им-пульсов устройства от структуры принимаемых сообщений. Сброс счетчика 7 в нулевое состояние производится сигналом с выхода элемента 5 задержки, т.е. вслед за вводом показаний счетчика 7 в коммутатор 10.

Предлагаемое устройств о обеспечивает в сравнении с прототипом повышение точности и помехоустойчивости ус репнения.

Формула изобретения Усредн1пощее устройство с блотаровкой, содержащее фазовый дискриминатор, первый которого подключен к первому входу первого реверсивного счетчина и к первому входу первого элемента И, второй вход которого соединен с выходом первого триггера, к входам которого подключены первые выходы первого коммутатора и первого реверсивного счетчика,- второй выход которого соединен с первым входом второго триггера, выход которого подключен к первому

входу второго элемента И, второй вход которого соединен с вторым выходом фазового дискриминатора и с вторым входом первого реверсивного счетчика, соответствующие вылэды которого подключены к одним входам первого комму- татора, а также второй коммутатор, первый счетчик и последовательно соединенные первый элемент задержки и второй счетчик, отличающееся тем, что, с целью повышения точности при воздействии помех, введены второй реверсивный счетчик и последовательно соединенные второй элемент задержки и третий реверсивный счетчик, выходы которого подключены к другим входам первого коммутатора, соответствующий вход которого соединен с входом второго элемента задержки и с выходом второго счетчика, второй вход которого соединен с первым входом фазового дисKpHNtHHaTopa, второй вход которого соединен с входом, первого счетчика, выход которого подключен к входам первого элемента задержки и второго ком мутато.ра, одни входы которого соединены с выходами второго реверсивного счетчика к входам которого подключены выходы первого и второго элементов И, при этом второй выход первого коммутатора соединен с вторым вход омвторого триггера, первый и второй выходы фазового дискриминатора подключены к соответствующим входам третьего реверсивного счетчика, а соответствующие выходы второго счетчика соединены с другими входами второго коммутатора.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-11-30—Публикация

1981-05-08—Подача