Изобретение относится к запоминаюи-.им устройствам.

Известен дешифратор, содержащий четыре транзистора и конденсатор, причем источники первого и второго транзисторов соединены со стоком третьего транзистора, сток первого и затвор второго транзисторов подключены к шине питания, затвор первого транзистора соединен с управляющей шиной, а .затвор и исток третьего транзистора - с адресной шиной и шиной земли соответственно, сток второго транзистора подключен к затвору четвертого транзистора и к одной обкладке конденсатрра, другая обкладка которого объединена с источником четвертого транзистора и с выходной шиной, сток четвертого транзистора соединен с входной шиной 1 .

Недостатком этого устройства йвляется низкая надежность.

Наиболее близким по технической сущности к предлагаемому является дешифратор для запоминающего устройства, содержащий девять транзисторов и два конденсатора, причем истоки первого, второго и третьего транзисторов соединены со стоком четвертого

транзистора и с одной из обкладок первого и второго конденсатора, другие обкладки которых подключены к затворам второго и третьего транзисторов и к источнику пятого транзистора, затвор и сток которого соединены со стоком первого; транзистора и с шиной питания, затворы первого, шестого и седьмого TpkH3HCTOpoB

10 подключены к управляющей шине, а затвор четвертого транзистора - к адресной шине, сток второго транзистора соединен с затвором восьмого транзистора, а сток третьего транзис15тора - с затвором девятого, стоки восьмого и девятого транзисторов подключены к первой и второй входным шинам соответственно, исток восьмого и сток шестого транзисторов со20единены с первой выходной шиной, а исток девятого и сток седьмого транзисторов - с второй выходной шиной 2 .

Недостатком этого устройства явля25ется низкая надежность, обусловленная тем, что при бросках величины напряжения питания, обусловленных помехами от внешних устройств, на затворах второго и третьего транзис30торов к моменту появления положитель

ного потенциала на входных шинах может возникнуть потенциал, превышающий величину разности напряжения питания и порогового напряжения Транзисторов ,что приведет к повышению токов утечки через второй и третий транзисторы, снижению потенциала на затворах восьмого и девятого транзисторов ухудшению фронтов сигналов и уровней логической единицы на выходных шинах.

Цель изобретения - повышение надежности дешифратора для запоминающего устройства.

Поставленная цель достигается тем, что в дешифратор для запоминающего устройства, содержащий МДПтранзисторы, причем истоки первого и второго транзисторов соединены со стоком третьего транзистора, сток второго транзистора соединен с затвором четвертого транзистора, затвор второго и исток пятого транзисторов объединены, сток первого транзистора соединен с затвором и стоком пятого транзистора и шиной питания, затвор первого транзистора является управляющим входом дешифратора, исток третьего транзистора соединен с шиной нулевого потенциала, а затвор является адресным входом дешифратора, исток и сток четвертого транзистора являются соответственно выходом и информационным входом дешифратора введен шестой МДП-транзистор, исток которого соединен с затвором второго транзистора, затвор подключен к шине питания, а сток является управляющим входом дешифратора.

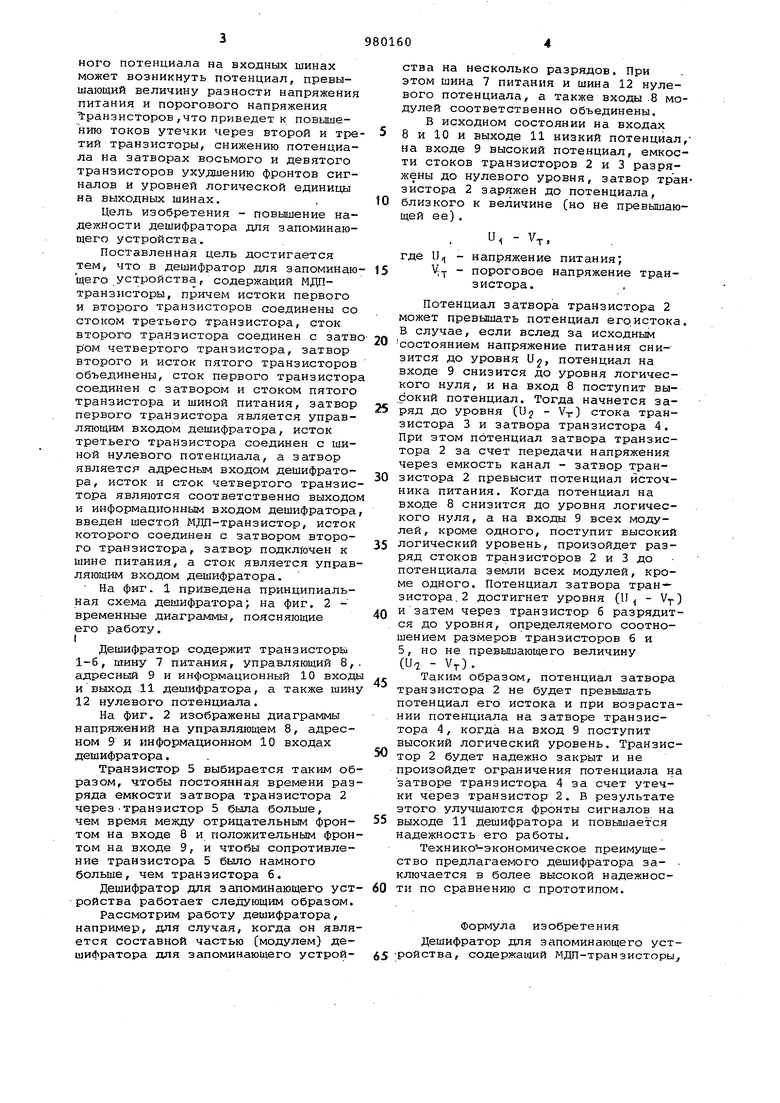

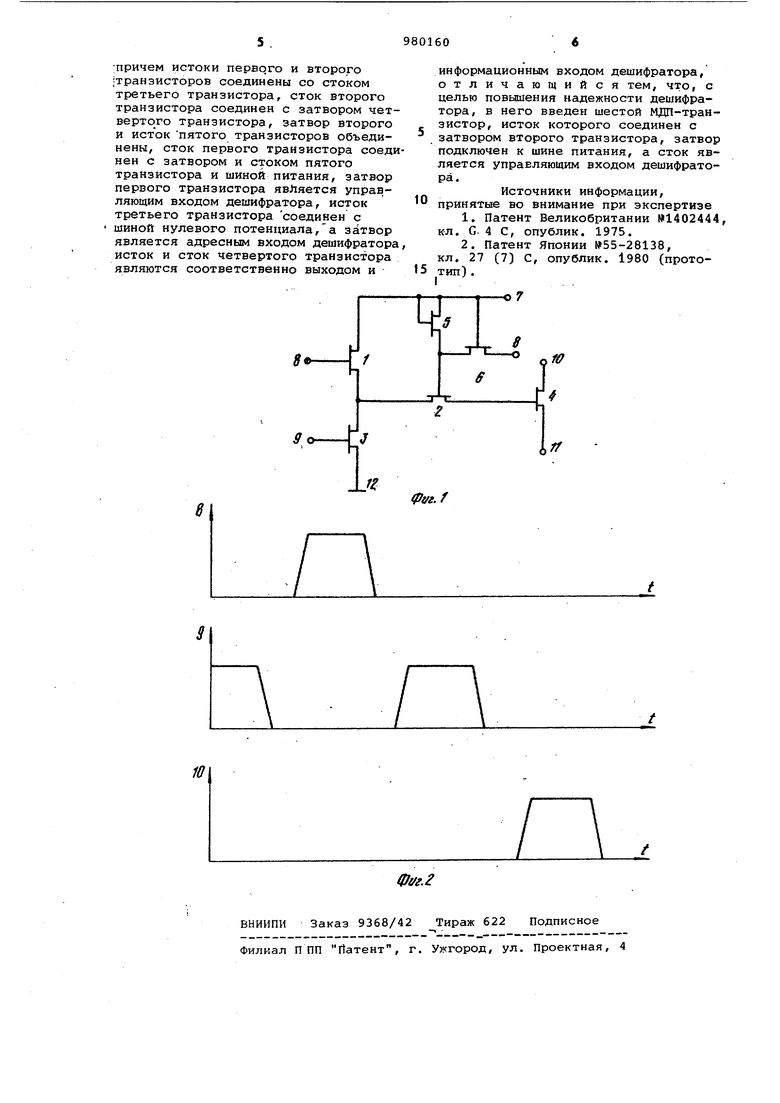

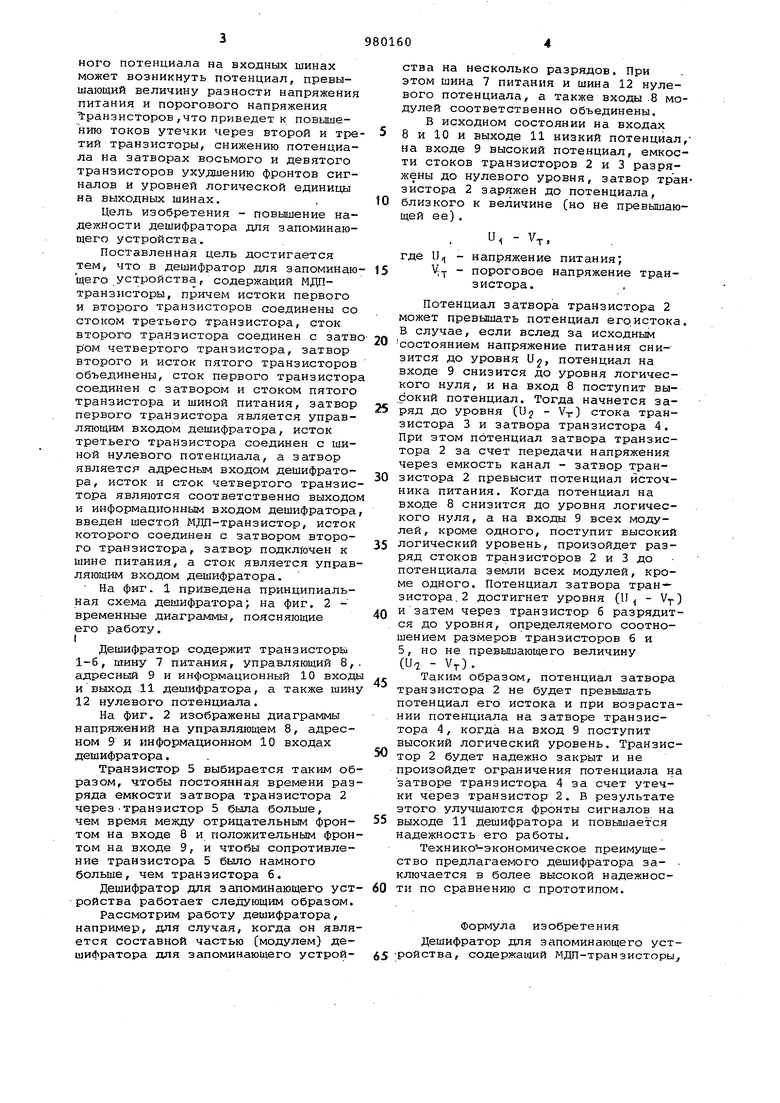

На фиг. 1 приведена принципиальная схема дешифратора на фиг. 2 временные диаграммы, поясняющие его работу. I

Дешифратор содержит транзисторы

1-6, шину 7 питания, управляющий 8,адресный 9 и информационный 10 входы и выход 11 дешифратора, а также шину 12 нулевого потенциала.

На фиг. 2 изображены диаграммы напряжений на управляющем 8, адресном 9 и информационном 10 входах дешифратора.

Транзистор 5 выбирается таким образом, чтобы постоянная времени разряда емкости затвора транзистора 2 черезтранзистор 5 была больше, чем время между отрицательным фронтом на входе 8 и положительным фронтом на входе 9, и чтобы сопротивление транзистора 5 было намного больше, чем транзистора 6.

Дешифратор для запоминающего устройства работает следующим образом.

Рассмотрим работу дешифратора, например, для случая, когда он является составной частью (модулем) дешифратора апя запоминающего устройства на несколько разрядов. При этом шина 7 питания и шина 12 нулевого потенциала, а также входы .8 модулей соответственно объединены. В исходном состоянии на входах

8 и 10 и выходе 11 низкий потенциал,на входе 9 высокий потенциал, емкости стоков транзисторов 2 и 3 разряжены до нулевого уровня, затвор транзистора 2 заряжен до потенциала,

близкого к величине (но не превышающей ее) .

и - VT,

где U,j - напряжение питания; XT пороговое напряжение транзистора.

Потенциал затвора транзистора 2 может превышать потенциал его.истока. В случае, если вслед за исходным

состоянием напряжение питания снизится до уровня Uj, потенциал на входе 9 снизится до уровня логического нуля, и на вход 8 поступит высокий потенциал. Тогда начнется заряд до уровня (и 2 - V-,.) стока транзистора 3 и затвора транзистора 4. При этом потенциал затвора транзистора 2 за счет передачи напряжения через емкость канал - затвор т ранзистора 2 превысит потенциал источника питания. Когда потенциал на входе 8 снизится до уровня логического нуля, а на входы 9 всех модулей, кроме одного, поступит высокий

логический уровень, произойдет разряд стоков транзисторов 2 и 3 до потенциала земли всех модулей, кроме одного. Потенциал затвора транзистора. 2 достигнет уровня (11 - V-p)

изатем через транзистор 6 разрядится до уровня, определяемого соотношением размеров транзисторов б и 5, но не превышающего величину (U7 - VT).

Таким образом, потенциал затвора транзистора 2 не будет превышать потенциал его истока и при возрастании потенциала на затворе транзистора 4, когда на вход 9 поступит высокий логический уровень. Транзистор 2 будет надежно закрыт и не

произойдет ограничения потенциала на затворе транзистора 4 за счет утечки через транзистору 2. В результате этого улучшаются фронты сигналов на

выходе 11 дешифратора и повышается надежность его работы.

Технико-экономическое преимущество предлагаемого дешифратора за- ключается в более высокой надежности по сравнению с прототипом.

Формула изобретения

Дешифратор для запоминающего уст65 Ройства, содержащий МДП-транзисторы

;причем истоки первого и второго ;транэисторов соединены со стоком третьего транзистора, сток второго транзистора соединен с затвором четверто го транзистора, затвор второго и исток пятого транзисторов объединены, сток первого транзистора соединен с затвором и стоком пятого транзистора и шиной питания, затвор первого транзистора является управляющим входом дешифратора, исток третьего транзистора соединен с шиной нулевого потенциала,а затвор является адресным входом дешифратора исток и сток четвертого транзистора являются соответственно выходом и

информационным входом дешифратора, отличающийся тем, что, с целью повышения надежности дешифратора, в него введен шестой МДП-транзистор, исток которого соединен с затвором второго транзистора, затвор подключен к шине питания, а сток является управляющим входом дешифратора.

Источники информации, принятые во внимание при экспертизе

1.Патент Великобритании N11402444, кл. G 4 С, опублик. 1975.

2.Патент Японии №55-28138,

кл. 27 (7) С, опублик. 1980 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресный формирователь | 1981 |

|

SU1007133A1 |

| Формирователь адресных сигналов | 1982 |

|

SU1049967A1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

| Дешифратор адреса | 1981 |

|

SU966905A1 |

| Формирователь импульсов | 1981 |

|

SU991507A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ НА МДП-ТРАНЗИСТОРАХ | 1991 |

|

RU2088979C1 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

| Адресный формирователь | 1988 |

|

SU1624521A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

8

,/87

.ff

fpai.f

Авторы

Даты

1982-12-07—Публикация

1981-06-22—Подача