10

Изобретение относится к цифровой вычислительной технике и может быть использовано либо в виде самостоятельного устройства, либо в составе запоминающего устройства на МДП-тран- эисторах в интегральном исполнении для дешифраций входных сигналов.

Целью изобретения является уменьшение потребляемой мощности.

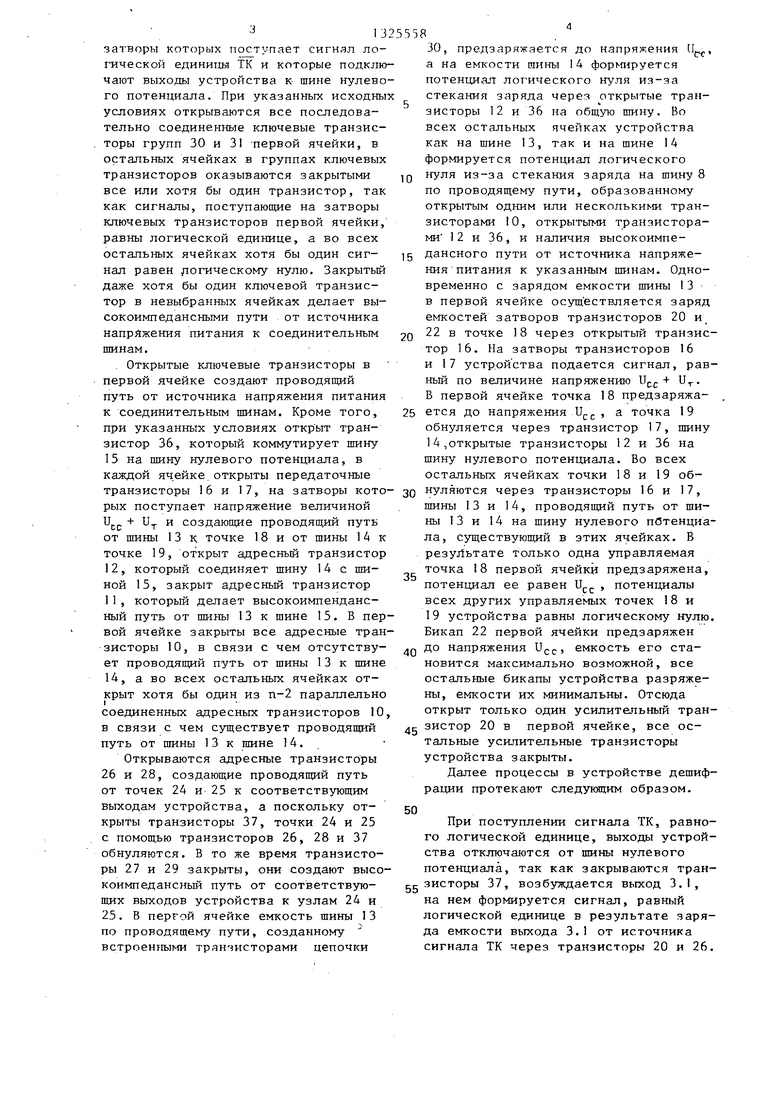

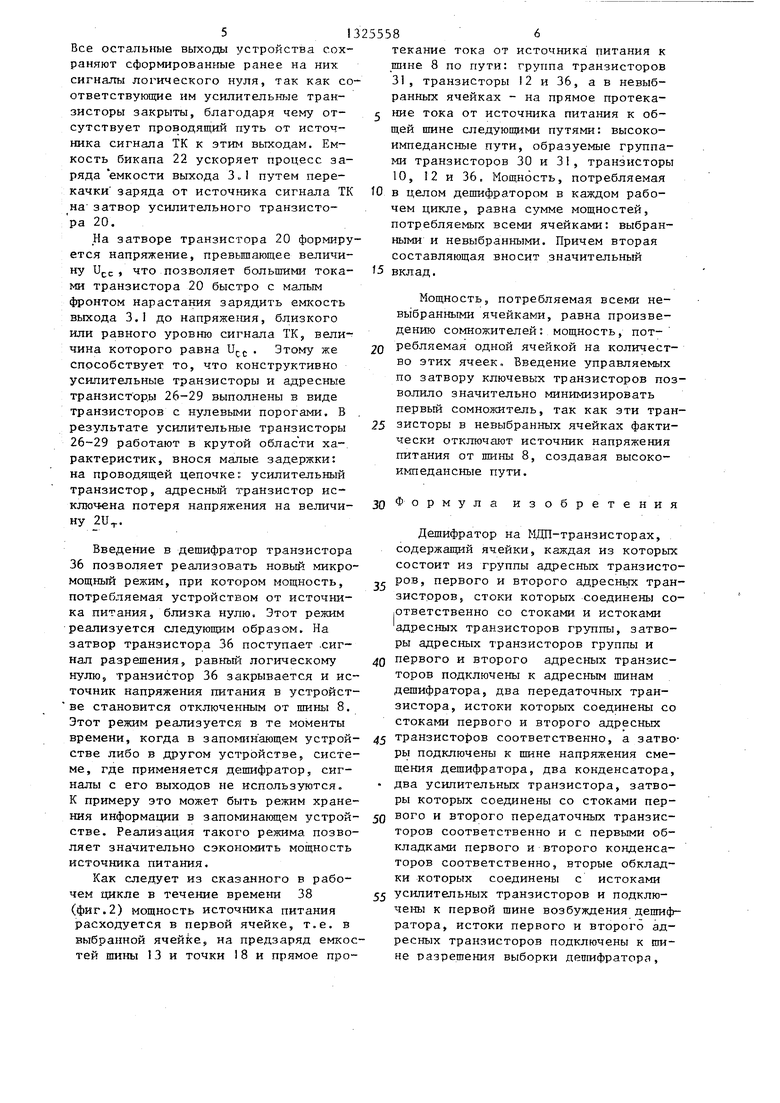

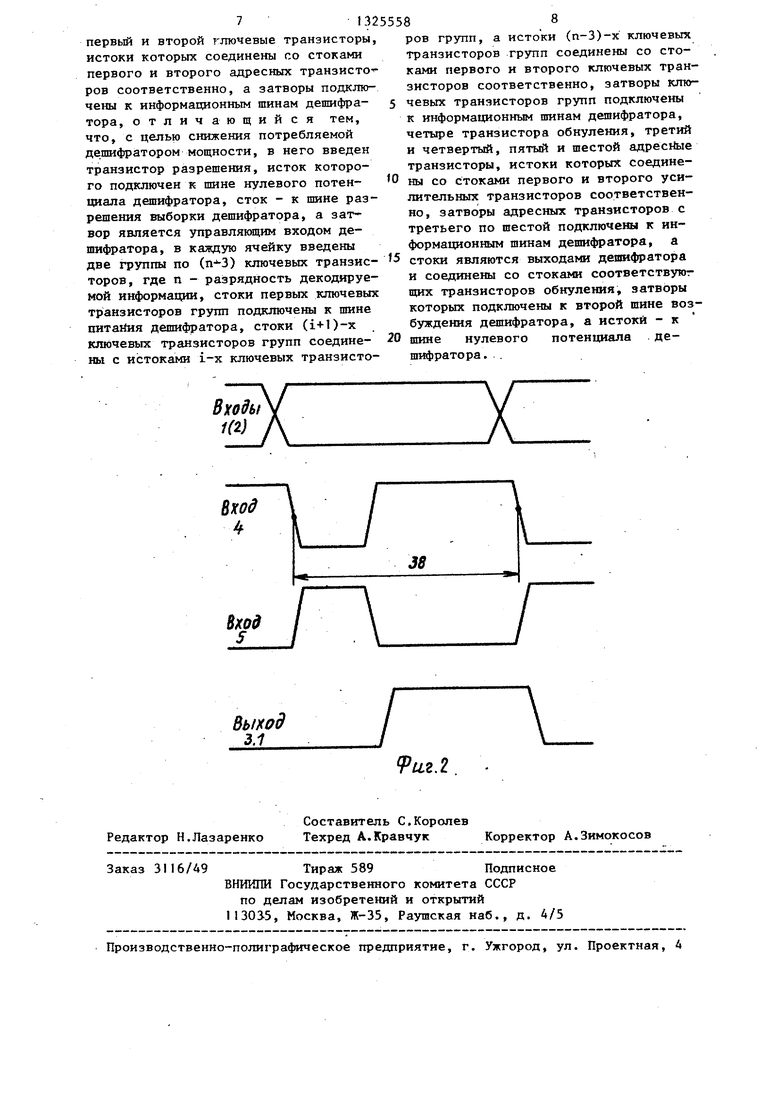

На фиг.1 представлена электрическая принципиальная схема дешифратора на МДП-транзисторах; на фиг.2 - временная диаграмма его работы.

Дешифратор осуществляет дешифрацию п-разрядного входного двоичного слова, имеет п информационных шин 1.,...,1.(п-1), I. п И п инверсных информационных сиг- налов, п информационных шин .1,.,.,2.(п-1), 2.п и п прямых информационных сигналов по количеству выходов относятся к типу устройств дешифрации с полным, т.е. равным 2 ,

количеством выходов. Ввходрл устройст- 25 ство входят транзистор

п

15

20

ва- 3.1, 3.2,... ,3.2. Дешифратор также содержит первую шину 4 возбуждения, вторую шину 5 возбуждения, на .которую подается противофазный сигнал по отношению к шине 4, шину 6 напряжения смещения, управляющий вход 7 разрешения, шину 8 нулевого

потенциала, шину 9 питания.

В состав каждой ячейки устройства входят группа адресных транзисторов 10, первый 11, второй 12 адресные транзисторы. Стоки транзисторов 10 Объединены и подключены к первой соединительной шине 13, истоки также Объединены и подключены к второй- соединительной шине 14. Истоки транзисторов 1I и 12 объединены и подключены к шине 15 разрешения. В состав Каждой ячейки входят первый 16 и второй 17 передаточные транзисторы, причем сток транзистора 16 соединен с первой управляемой точкой 18, а сток транзистора I7 - с второй управляемой точкой 19, затворы всех передаточных транзисторов объединены и подключены к шине 6, т.е. к выходу источника сигнала смещения, равного (Ugp+ и) в, где Ugj - напряжение источника питания, U,. - пороговое напряжение ЦЦП-транзистора. Каждая ячейка содержит первый 20 и второй

21усилительные транзисторы, первый

22и второй 23 конденсаторы обратной связи. Истоки усилительных транзисторов всех ячеек объедине ны к шине 4. Затвор уси транзистора 20 подключ равляемой точке 18, ст управляемой точке 24. тельного транзистора 2 второй управляемой точ к четвертой управляемой состав каждой ячейки вх 26, четвертый 27, пятый 29 адресные транзисторы и вторая 31 группы ключ торов. Ключевые транзи соединены последователь стоки первых транзистор пы 30 и 33 из группы 3 объединены и подключены т.е. и источнику питани дой ячейке исток перво транзистора 34 подключе соеданительной шине 13 го ключевого транзистор рой соединительной шине

- и

и

35

2 транзисторов 37 о

Конструктивно устрой ции выполнено на МДП-тр трех типов. Транзисторы

30 17, 22 и 23 - индуциро 20, 21, 26-29, 36 - тр левыми порогами, а тран 30 и 31 - встроенного т

Конденсаторы 22 и 2 но выполнены в виде бик зисторов индуцированно и истоки которых соедин с подзатворным инверсны зуют первую обкладку ко

40 вторую образует затвор Емкость такого конденса ется напряжением на зат больше напряжение, тем кость .

45 Дешифратор работает бочего цикла, т.е. в те 38 (фиг.2). В начальный ни, когда сигнал возбут вен логическому нулю, с

50 логической единице, сиг ния - логической единиц 1 и 2 устройства дешифр ет такая комбинация адр лов, в которой прямые а

55 лы равны логическому ну ственно все инверсные единице.

Выходы устройства 3 3.2 обнуляются транзис

5 ство входят транзистор

5

0

ров всех ячеек объединены .и подключены к шине 4. Затвор усилительного транзистора 20 подключен к первой управляемой точке 18, сток - к третьей управляемой точке 24. Затвор усилн- тельного транзистора 21 подключен к второй управляемой точке 19, сток - к четвертой управляемой точке 25. В состав каждой ячейки входят третий 26, четвертый 27, пятый 28, шестой 29 адресные транзисторы, первая 30 и вторая 31 группы ключевых транзисторов. Ключевые транзисторы в группе соединены последовательно. Причем стоки первых транзисторов 32 из группы 30 и 33 из группы 31 всех ячеек объединены и подключены к шине 9, т.е. и источнику питания Ucc « В каждой ячейке исток первого ключевого транзистора 34 подключен к первой соеданительной шине 13, исток второго ключевого транзистора 35 - к второй соединительной шине 14. В устрой36 разрешения

- и

и

5

2 транзисторов 37 обнуления.

Конструктивно устройство дешифрации выполнено на МДП-транзисторах трех типов. Транзисторы 10-12, 16,

0 17, 22 и 23 - индуцированного типа, 20, 21, 26-29, 36 - транзисторы с нулевыми порогами, а транзисторы г-рупп 30 и 31 - встроенного типа.

Конденсаторы 22 и 23 конструктивно выполнены в виде бикапов - транзисторов индуцированного типа,- стоки и истоки которых соединены и вместе с подзатворным инверсным слоем образуют первую обкладку конденсатора, а

0 вторую образует затвор транзистора. Емкость такого конденсатора управляется напряжением на затворе, чем больше напряжение, тем больше емкость .

5 Дешифратор работает в течеш е рабочего цикла, т.е. в течение времени 38 (фиг.2). В начальный момент времени, когда сигнал возбуткдения ТК равен логическому нулю, сигнал ТК 0 логической единице, сигнал разрешения - логической единице, на входы 1 и 2 устройства дешифрации поступает такая комбинация адресных сигналов, в которой прямые адресные сигна5 лы равны логическому нулю, соответ- . ственно все инверсные логической единице.

Выходы устройства 3.1, 3.2,..., 3.2 обнуляются транзисторами 37, на

затворы которых поступает сигнял логической единицы ТК и которые подключают выходы устройства к шине нулевого потенциала. При указанных исходны условиях открываются все последовательно соединенные ключевые транзисторы групп 30 и 31 -первой ячейки, в остальных ячейках в группах ключевых транзисторов оказываются закрытыми все или хотя бы один транзистор, так как сигналы, поступающие на затворы ключевых транзисторов первой ячейки, равны логической единице, а во всех осталънь1х ячейках хотя бы один сигнал равен логическому нулю. Закрытый даже хотя бы один ключевой транзистор в невыбранных ячейках делает высок оимпедан с ными пути от источника напряжения питания к соединительным шинам.

. Открытые ключевые транзисторы в первой ячейке создают проводящий путь от источника напряжения питания к соединительным шинам. Кроме того, при указанных условиях открыт транзистор 36, который коммутирует шину 15 на шину нулевого потенциала, в каждой ячейке открыты передаточные транзисторы 16 и 17, на затворы которых поступает напряжение величиной Uj. + и и создающие проводящий путь от шины 13 к; точке 18 и от шины 1А к точке 19, открыт адресный транзистор 12, который соединяет шину 14 с шиной 15, закрыт адресный транзистор 1, который делает высокоимпенданс- ный путь от шины I3 к шине 15. В первой ячейке закрыты все адресные транзисторы 10, в связи с чем отсутствует проводящий путь от шины 13 к шине 14, а во всех остальных ячейках открыт хотя бы один из п-2 параллельно соединенных адресных транзисторов 10 в связи с чем существует проводящий путь от шины 13 к шине 14..

Открываются адресные транзисторы 26 и 28, создающие проводящий путь от точек 24 и 25 к соответствующим выходам устройства, а поскольку открыты транзисторы 37, точки 24 и 25 с помощью транзисторов 26, 28 и 37 обнуляются. В то же время транзисторы 27 и 29 закрыты, они создают высо- коимпедансный путь от соответствующих выходов устройства к узлам 24 и 25. В пергой ячейке емкость шины 13 по проводящему пути, созданному встроенпыьш транзисторами цепочки

5

0

30, предзаряжается до напряжения (1; а на емкости шины 14 форьшруется потенциал логического нуля из-за стекания заряда через открытые транзисторы 12 и 36 на общую шину. Во всех остальных ячейках устройства как на шине 13, так и на шине I4 формируется потенциал логического нуля из-за стекания заряда на ши,ну 8 по проводящему пути, образованному открытым одним или несколькими транзисторами 10, открытыми транзисторами 12 и 36, и наличия высокоимпе- дансного пути от источника напряжения питания к указанным шинам. Одновременно с зарядом емкости шины 13 в первой ячейке осуществляется заряд емкостей затворов транзисторов 20 и 22 в точке 18 через открытый транзистор 16, На затворы транзисторов 16 и 17 устройства подается сигнал, равный по величине напряжению U(. + В первой ячейке точка 18 предзаряжа5 ется до напряжения U

ее

а точка 19

0

5

обнуляется через транзистор 17, шину 14,открытые транзисторы 12 и 36 на шину нулевого потенциала. Во всех остальных ячейках точки 18 и 19 обнуляются через транзисторы 16 и 17, шины 13 и 14, проводяш 1й путь от шины 13 и 14 на шину нулевого пбтенциа ла, существуюш 1й в зтих ячейках, В результате только одна зшравляемая точка 18 первой ячейки предзаряжена, потенциал ее равен U

.(-J, , потенциалы всех других управляемых точек 18 и 19 устройства равны логическому нулю, Бикап 22 первой ячейки предзаряжен

Q до напряжения ,, емкость его становится максимально возможной, все остальные бикапы устройства разряжены, емкости их минимальны. Отсюда открыт только один усилительный транg зистор 20 в первой ячейке, все остальные усилительные транзисторы устройства закрыты.

Далее процессы в устройстве дешифрации протекают следукяцим образом,

0

При поступлении сигнала ТК, равного логической единице, выходы устройства отключаются от шины нулевого потенциала, так как закрываются тране зисторы 37, возбуждается выход 3,1, на нем формируется сигнал, равный логической едигшце в результате заряда емкости выхода 3.1 от источника сигнала ТК через транзисторы 20 и 26,

Все остапьные выходы устройства сохраняют сформированные ранее на них. сигналы логического нуля, так как соответствующие им усилительные транзисторы закрыты, благодаря чему отсутствует проводящий путь от источника сигнала ТК к выходам. Емкость бикапа 22 ускоряет процесс заряда емкости выхода 3„ путем перекачки заряда от источника сигнала ТК на затвор усилительного транзисто- ра 20.

На затворе транзистора 20 формируется напряжение, превышающее величину Uj-c , что позволяет большими токами транзистора 20 быстро с малым фронтом нарастания зарядить емкость выхода 3.1 до напряжения, близкого или равного уровню сигнала ТК, вели- чина которого равна и.. . Этому же способствует то, что конструктивно усилительные транзисторы и адресные транзисторы 26-29 выполнены в виде транзисторов с нулевыми порогами. В результате усилительные транзисторы 26-29 работают в крутой области характеристик, внося малые задержки: на проводящей цепочке: усилительный транзистор, адресньм транзистор исключена потеря напряжения на величи- ну 2V.

Введение в дешифратор транзистора 36 позволяет реализовать новый микромощный режим, при котором мощность, потребляемая устройством от источника питания, близка нухш. Этот режим реализуется следующим образом. На затвор транзистора 36 поступает .сигнал разрешения, равный логическому нулю, транзистор 36 закрывается и источник напряжения питания в устройст- ве становится отключенным от щины 8. Этот режим реализуется в те моменты времени, когда в запомин ающем устройстве либо в другом устройстве, системе, где применяется дешифратор, сигналы с его выходов не используются. К примеру это может быть режим хранения информации в запоминающем устройстве. Реализация такого режима позволяет значительно сэкономить мощность источника питания.

Как следует из сказанного в рабочем цикле в течение времени 38 (фиг.2) мощность источника питания расходуется в первой ячейке, т.е. в выбранной ячейке, на предзаряд емкостей шины 13 и точки 18 и прямое протекание тока от источника питания к шине 8 по пути: группа транзисторов 31, транзисторы 12 и 36, а в невыб- ранньгх ячейках - на прямое протекание тока от источника питания к общей шине следующими путями: высоко- импедансные пути, образуемые группами транзисторов 30 и 31, транзисторы 10, 12 и 36, Мощность, потребляемая

в целом дешифратором в каждом рабочем цикле, равна сумме мощностей, потребляемых всеми ячейками: выбранными и невыбранными. Причем вторая составляющая вносит значительный

вклад.

Мощность, потребляемая всеми невыбранными ячейками, равна произведению сомножителей: мощность, потребляемая одной ячейкой на количество этих ячеек. Введение управляемых по затвору ключевых транзисторов позволило значительно минимизировать первый сомножитель, так как эти транзисторы в неЕ1ыбранных ячейках фактически отключают источник напряжения питания от щрио. 8, создавая высоко- импедансные пути.

Формул а изобретения

Дешифратор на МДП-транзисторах, содержащий ячейки, каждая из которых состоит из группы адресных транзисторов, первого и второго адресных транзисторов, стоки которых соединены соответственно со стоками и истоками адресных транзисторов группы, затворы адресных транзисторов группы и первого и второго адресных транзисторов подключены к адресным шинам дешифратора, два передаточных транзистора, истоки которых соединены со стоками первого и второго адресных транзисторов соответственно, а затворы подключены к шине напряжения смещения дешифратора, два конденсатора, два усилительных транзистора, затворы которых соединены со стоками первого и второго передаточных транзисторов соответственно и с первыми обкладками первого и второго конденсаторов соответственно, вторые обкладки которых соединены с истоками усилительных транзисторов и подклю- к первой шине возбуждения дешифратора, истоки первого и второго адресных транзисторов подключены к тине разрешения выборки депшфратора,

первый и второй т-лючевые транзисторы истоки которых соединены со стоками первого и второго адресных транзисто ров соответственно, а затворы подключены к информационным шинам дешифратора, отличающийся тем, что, с целью снижения потребляемой дешифратором мощности, в него введен транзистор разрещения, исток которого подключен к шине нулевого потенциала дешифратора, сток - к шине разрешения выборки дешифратора, а затвор является управляющим входом дешифратора, в каждую ячейку введены две группы по () ключевых транзисторов, где п - разрядность декодируемой информации, стоки первых ключевых транзисторов групп подключены к шине питайия дешифратора, стоки (1+1)-х ключевых транзисторов групп соединены с истоками i-x ключевых транзистоO

5

0

ров групп, а истоки (п-З)-х ключевых транзисторов групп соединены со стоками первого и второго ключевых транзисторов соответственно, затворы ключевых транзисторов групп подключены к информационным шинам дешифратора, четыре транзистора обнуления, третий и четвертый, пятый и шестой адресные транзисторы, истоки которых соединены со стоками первого и второго усилительных транзисторов соответственно, затворы адресных транзисторов с третьего по шестой подключены к информационным шинам дешифратора, а стоки являются выходами дешифратора и соединены со стоками соответствуют щих транзисторов обнуления, затворы которых подключены к второй шине возбуждения дешифратора, а истоки - к шине нулевого потенциала дешифратора . ..

Входь

1(2)

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор на МДП-транзисторах | 1983 |

|

SU1455362A1 |

| Ячейка фоточувствительного матричного запоминающего устройства | 1989 |

|

SU1709392A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1070604A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Дешифратор адреса | 1982 |

|

SU1068999A1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Динамическая ячейка памяти | 1974 |

|

SU523454A1 |

Изобретение относится к вычис- лител 1ной технике и может быть исnj « 2J пользовано в составе запоминающего устройства. Цель изобретения - снижение потребляемой мощности. Поставленная цель достигается тем, что в дешифратор дополнительно введены группы ключевых транзисторов 30, 31, адресные транзисторы 26-29, разрешающий транзистор 36, транзисторы обнуления 37 с соответствующими связями. При этом в два раза уменьшается количество ячеек дешифратора. Кроме того, транзистор 36 обеспечивает работу дешифратора в микрорежиме. В результате достигается снижение потребляемой мощности. 2 ил. а ЗГ (Л . t 2( со ю СП ел ел 00 иг-z) 3( )t4n}ln гл Фиг.} гпв

Вход 4

Г Гл

Вы)(од

3,1

Редактор Н.Лазаренко

Составитель С.Королев

Техред А.Кравчук Корректор А.Зимокосов

Заказ 3116/49Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 11303.5, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

иг.г

| Патент США № 3778782, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Патент США № 4099162, кл..С 11 С 5/02, опублик | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1987-07-23—Публикация

1986-03-18—Подача