Изобретение относится к импульсной технике и может быть использовано в системах синхронизации цифровых устройств в качестве делителя частоты с переменным коэффициентом деления.

Известен делитель частоты следования импульсов, содержащий счетчик, дешифратор, триггер и элементы И 1.

Наиболее близким по технической сущности к изобретению является управляемый делитель частоты следования импульсов, содержащий счетчик импульсов, выход которого соединен с выходной шиной делителя частоты, триггер, выход которого соединен с первым входом элемента И, блок форми4х)вания кода поправки, вход котоpojro. соединен с шинами кода деления, а выход - с информационными входами счетчика импульсов, линию задержки, вход которой подключен к выходной шине делителя частоты, а выход соединен с вторым входом элемента И и .с. одним входом триггера, второй вход которого через инвертор соединен с выходной шиной делителя частоты 2,

Недостатком данного делителя састоты является ограниченное быс-тродействие тиз-за наличия в схеме линии задержки.

Цель изобретения - повышение быстродействия .

Указанная цель достигается тем, что в управляемый делитель частоты Следования импульсов, содержащий триггер, прямой выход которого сое- . цинен с первым входом первого элемент

10 та И, блок формирования кода прправ ки, группа входов которого соединена с шинами кода деления, а выходы - с информационными входами счетчика импульсов, введен второй

15 элемент И, первый вход которого соединен с инверсным выходом триггера, второй вход - с вторым входом первого элемента И и входной шиной, а выход - с синхровходом счетчика импуль20сов и первым входом триггера, второй вход которого соединен с выходом счетчика импульсов, тактовый вход которого подключен к выходу первого элемента И.

25

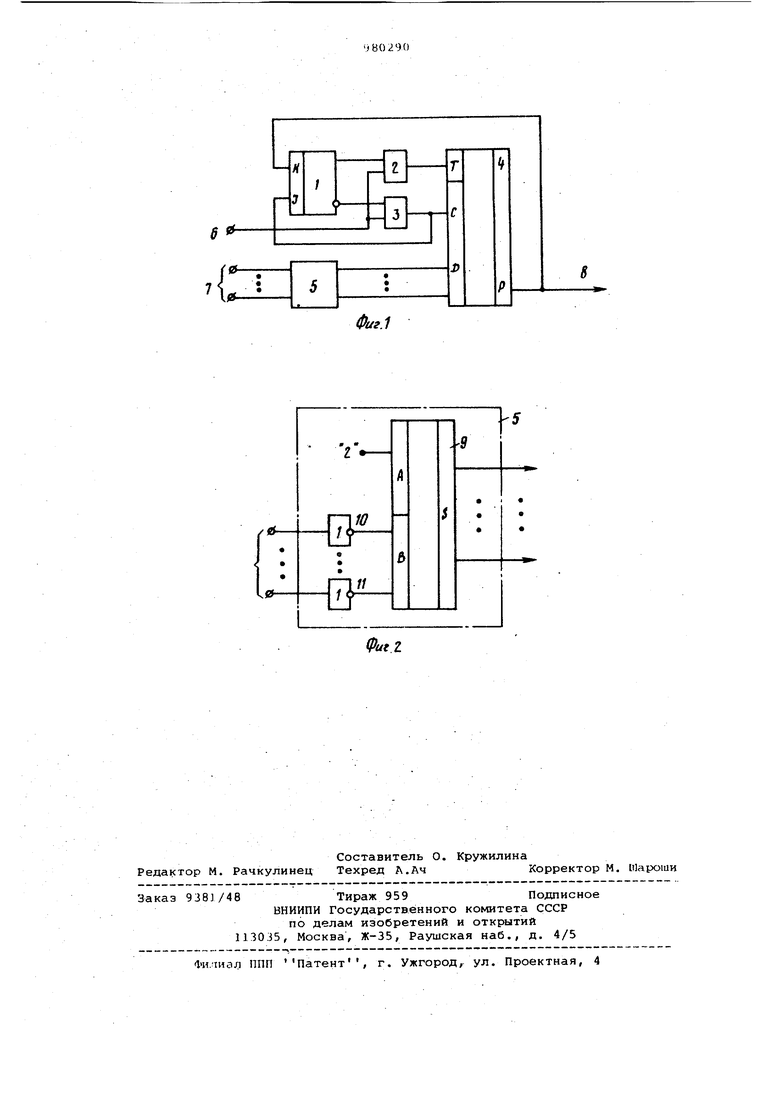

При этом блок формирования кода поправки выполнен в виде сумматора, первая группа входов которого соединена с выходами соответствующих инверторов, входы которых являются

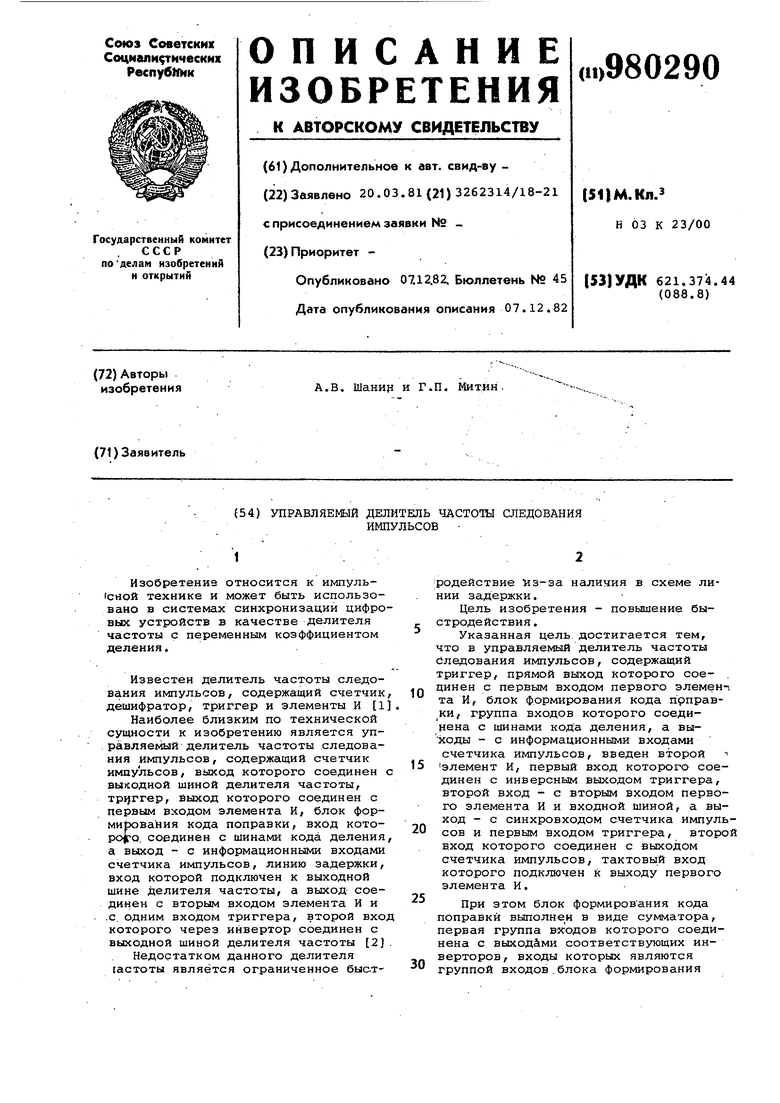

30 группой входов.блока формирования кода, ..;я группа входов - с шинами кода константы, а выходы являются выходами блока формирования ко да поправки. На фиг, 1 представлена структурная схема предлагаемого делителя частоты; на фиг. 2 - блок формирования кода поправки. Управляемый делитель частоты содержит триггер 1, элементы И 2 и 3, счетчик 4 импульсов, блок 5 формирования кода поправки, входную шину 6 шины 7 кода деления и выходную шину 8. Блок формирования кода поправки содержит двоичный сумматор 9, инверторы 10 и 11. Делитель работает следующим образом. Предположим, триггер 1 находится в нулевом состоянии, импульсы счета поступают по шине 6. Первый посту пающий импульс проходит через открытый элемент 3 на синхровход счетчика 4. Своим передним фронтом этот им пульс записывает в счетчик 4 код поправки, сформированный блоком 5, а задним фронтом переключает триггер в единичное состояние, так что входные импульсы, начиная со второго, поступают через элемент 2 на тактовы вход счетчика 4. Импульс переполнения с выхода сче чика поступает на шину 8 и своим зад ним фронтом переключает триггер 1 в нулевое положение.-Далее работа схемы происходит аналогично. Схема формирования кода поправки преобразует код деления, поступающий по шинам 7, в код поправки, равный где К. - код коэффициента деления; п - разрядность счетчика. Предлагаемый управляемый делитель частоты отличается повьшенным быстродействием и может применяться в системах автоматики и импульсной техники для получения любого целочисленного коэффициента деления частоты следования импульсов. Формула изобретения 1.Управляемый делитель частоты следования импульсов, содержащий триггер, прямой выход которого соединен с первым входом первого элемента И, блок формирования кода поправки, группа входов которого соединена с шинами кода деления, а выходы - с информационными входами счетчика импульсов, отличающийся тем, что, с целью повышения быстродействия, в него введен второй элемент И, первый вход которого соединен с инверсным выходом триггера, второй вход - с вторым входом первого элемента И и входной шиной, а выход - с синхровходом счетчика импульсов и первым входом триггера, второй вход которого соединен свыходом счетчика импульсов, тактовый вход которого подключен к выходу первого элемента И. 2.Делитель частоты по п. 1, о тличающийс я тем, что блок формирования кода поправки выполнен в виде сумматора, первая группа входов которого соединена с выходами соответствующих инверторов, входы которых являются группой входов блока формирования кода, вторая группа входовк шинам кода константы, а выходы являются выходами блока формирования кода поправки. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 513507, кл. Н 03 К 23/00, 1974. 2,Авторское свидетельство СССР 524320, кл. Н 03 К 23/00, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Перестраиваемый делитель частоты | 1982 |

|

SU1023662A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1661981A1 |

| Блок управления для запоминающего устройства | 1977 |

|

SU723679A1 |

| Перестраиваемый делитель частоты следования импульсов | 1981 |

|

SU995334A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Устройство формирования серий импульсов | 1981 |

|

SU962890A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1267601A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

Авторы

Даты

1982-12-07—Публикация

1981-03-20—Подача