(54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Вычислительное устройство | 1983 |

|

SU1080135A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ M-МЕРНОГО ВЕКТОРА | 1995 |

|

RU2080650C1 |

| Арифметическое устройство с фиксированной точкой | 1984 |

|

SU1241230A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

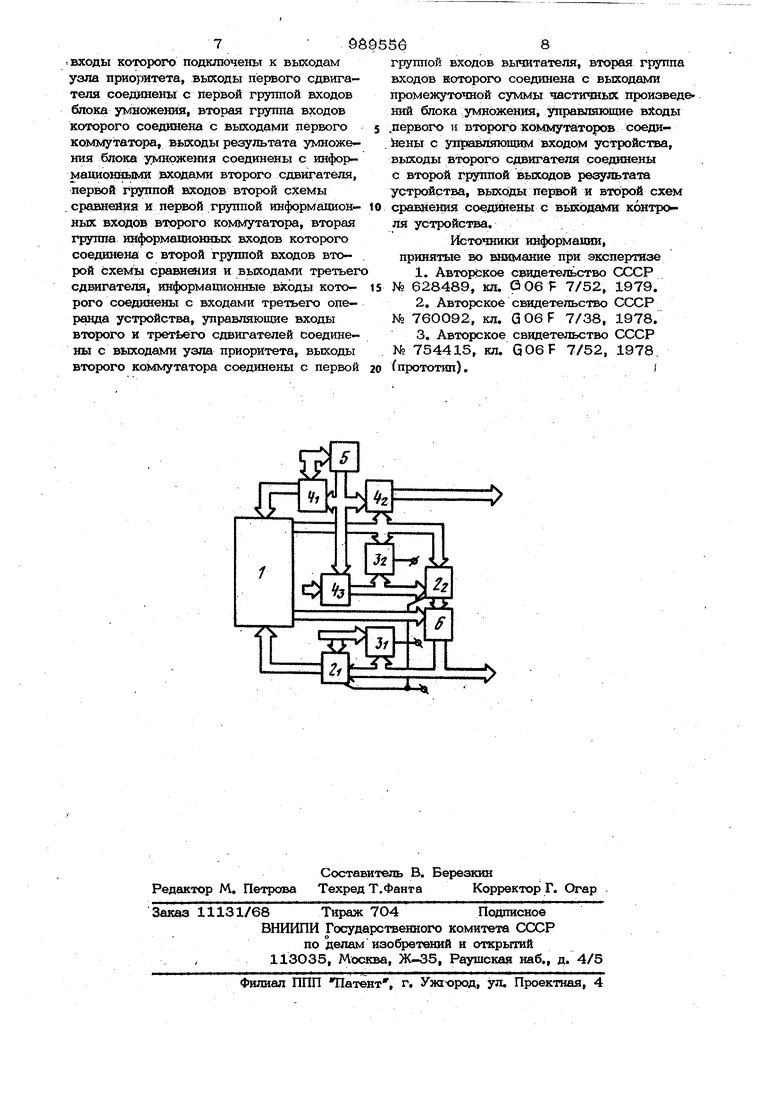

Изобретение относится к хшфровой вычислительной технике и может быть п мененъ в составе унив хзальнызс или специализированных вычислительных машин для оператиюяого вычисления арифметических операций умножения и деления. Известны устройства для выполнения арнфлетических олерашй умножения и деления, включающие матрицу H-w одноразрядных сумматоров, m цифровых функоиональных преобразователе, И разрядный регистр 1 и 2 . Однако в этих устройствах не выполняется одновременно операшся умножения и деления и, соответственно, не осущест ляется контроль вычислительного процес са-умножения делением и наоборот, в связи с чем в устройст вах ограничены функциональные возможности и вычислений. Наиболее близким к предлагаемому является вьямслительное устройство, содержащее блок умножения, вынитатель. узел определения знака частного, входные шины и выходную ипшу, причем группа выходов вычитателя, соответствующие входы которого соединены с выходами блока умножения, подключена к вьосодной ищне устройства 13 . Недостатками известного устройства являются ограниченные функциональные возможности и невысокая точность из-за того, что в нем не организован контроль вычислительного процесса. Цель изобретения - расширение функ& циональных возможностей за счет выполнения как операшп{ деления, так и операции умножения и повышение точности за счет осуществления параллельного контроля вычисления. Указанная цель достигается тем, что в вычислительное устройство, содержащее блок уыножшшя н вычитатель, выходы которого соединены с первой группой выходов результата устройства, дополнительно введено два коммутатора, две схемы сравнения, первьтй, втооой и.тоет. тий сдвигатели и узел приоритета, причем входы первого операнда устройства соединены с первой группой входов лервой схемы сравнения и первой группой информационных входов первого коммутатора, вторая rjjynna информационных входов которого соединена с второй грудаюй входов первой скеалы сравнения ,и выходами вычитателя, входы второго операнда устройства соединены с входами узла приоритета и информационными входами первого сдвигателя, управляющие входы которого подключены к выходам y3Jria приоритета, выходы первого сдвигателя соединены с первой группой входов блока умножения, вторая группа входов которого соединена с выходами первого коммутатора, выходы результата умножения блока умножения соединены с информационными входами второго сдвигателя, первой группой входов второй схемы срав нения и первой группой информационных входов второго коммутатора, вторая груп па информационных входов которого соеди нена с второй группой входов второй схемы сравнения и выходами третьего сдвигателя, информационные входы которого соединены с входами третьего операнда устройства, управляющие входы второго и третьего сдвигателей соединен с выходами узла приоритета, выходы вто рого коммутатора соединены с первой группой входов вычитателя, вторая грзуппа входов которого соединена с выходами промежуточной суммы частичных произведений блока у 4ноження, управляющие входы первого и второго коммутаторов соединены с управляющим входся г уст1рой ства, выходы второго сдвигателя соединены со второй группой выходов результата устройства, выходы первой и второй схем срав|:|ения соединены с выходами контроля устройства. На чертежепредставлена схема предлагаемого устройства. Устройство содержит блок умножения 1, два коммутатора 2. и 2, дае схемы сравнения 3,, и 32, первый, второй и третий сдвигатели 4, 42 и 4, узел приоритета 5 и вычитатель 6. Входы первого операнда устройства соедишены с первой группой входов первой схемы сравнения 3 и первой группой информационных входов nejpBoro коммутатора 2, вторая группа информационных входов которого соединена со второй группой входов первой схемы сравнения 3. и вь ходами вычитатедя 6. Входы второго операнда устройства соединены со входами узла приоритета 5 и информационными входами первого сдвигателя 4, управляющие входы которого подключены к выходам узла приоритета 5, Выходы пер. вого сдвигателя 4 соединены с первой группой входов блока умножения 1, вторая группа входов которого соединена с выходами первого коммутатора 2i. Вььходь результата умножения блока умножения 1 соединены с я рмааяокаьшк входами второго сдвигателя 4, первой группой входов второй схемы сраоления 3 и первой группой информационных входов второго коммутатора 2, вторая iwima информационных входов которого соединена со второй группой входов второй схемы сравнения 3. и вьвсодами третьего сдвигателя 4, информахшонные {ВХОДЫ которого соединены со входами третьего операнда устройства. Управляющие входы второго и третьего сдвигателей 4 и 4 3 соединены с выходами узла приоритета 5, выходы второго коммутатора 2 соединены с первой группой входов вычитателя 6, вторая группа входов которого соединена с выходами прсялежуточной суммы частичных произведений блока умножения 1. Управляющие входы первого и второго коммутаторов 2 и 2л сое/ошены с управляющщу входом устройства. Выходы второго сдвигателя 4. соединены со второй группой выходов результата устройст ва. Вьссоды первой и второй схем сравнения 3 и 3 соединены с выходами KOHI роля устройства, а выходы вычитателя 6 подключены к первой группе выходов результата устройства. , V Операция умножения а X 1э для сдучая, когда младший разр5ш И вектора и 1, может бы1пь записана И V,.j ..ИЛИ соответственно и-i grM-i-аи-е- дв. Ъ-I e-i : .- e-1 где-I O,(j..., м--.. Операция деления в соответствии с (З) V.r . W Для случая, когда один или vi младашх разрядов вектора а равны нулю, тогда вьфажения (2)-(4) могут быть записаны V- : (5) ,:4%rr.|; d x --U,

и операция деления соответственно Vl -iH-i-w n-t- и-i-f

х ъ -z a x - (T;

о - Работа устре с-гаа ирсзясходит следу б здим обрааовм.

Операция умяаж&вяя На управляющий вход устройства прядется значение О, при вход первого операнда подклкхчается к BTOpcrfi группе входов бяока

умвожеяхш X и эаярещается подключение третьего операнда усоройства к выходу коммутатора. При подаче на входы первого и второго сшерандов эяачедей с ни соответственно в узле приррнтета определяется колнчестЕю ненулевык младших разрядов д , чему в первом с двигателе 4 реализуется CfSfsstr вектора о на число нулевых, мпадщих разрадов вектора ё. во втором сдвигателе реализуется сдвиг в сторону старшие, а в третьем - в сторону младших разрядов на число 141. После окончания niepe ходного процесса в устройстве на выходе резут тата умножения блока, умножения 1 по вьфаж шю (5) и (6) офазуется вектор 2 IQ , а на выходе промежуточиьсс сумм частичных птэризведений - соот

ветственно значение Га х .которое йоступ&ет на вторую группу входов йдаитателя 6. Вектор 2 (m - чисто . вектора , равных ц) 1эез второй коммутатор 2 посчуще |К1 первую группу входов вычитателя в, на выходе которого по выражению (7) образуется вектсф х , посчупаюший на вторую группу вхсщсв первой схемы сра&нения 3. ,, ва первую гртшу входов которой поступает вектор X со входа первого сшерадда. Если умноже}ше выпопнево правильно, на выходе первой схс сравнения 3 появляется сигнал, xapai&теризующий конец переходного процесса и правильность вычисления лектора значение которого образуется на выходе второго сдвигателя ( в сто.poi старших разрядов на число И1 )

Операция деления. На управляюший вход устройства подается значение 1. Деление возможно для класжа чисел Ъ и С11 делящихся нацело. При r iynna входов третьего операнда подключается через второй коммутатор к первой группе входов вычитателя 6. Выход вычитателя 6 через первый коммутатор 2 подклао чается к второй группе входов бпсиса У1«шожеш1я 1.V V

После подачи значений и Q cooTiael ственно на входы третьего, второго one рандов на выходе первого сдвигателя образуется вектор С1 , сдвинутый в сторону младших разрядов на число И1, равное количеству нулей в младших разрядах вектора. На выходе третьсЛ й сдвигатеяя 4 3 образуется вектор .) сдвицучгУй также на число W. После окончания переходного процесса в устройстве на выходе вычитателя 6 по вьфаженшо (7) , образуется значение искомого вектора X а на выходе peзyльta ra умножения блока умножения 1 - соответственно вектор 2 Ь поступающий на первую группу входов второй схемы ср авнения 2, на вторую группу входов которой поступает значение вектора 2Г со входа третьего (Х1еранда, Если операшя деления выпо нева правильно, то на выходе второй схемы сравнения появляется сигнал, характеризующий правильность ее вьшолнения и конец переходного процесса в устройстве, Такта офазом, в устройстве реалиа1уерся параллельный контроле вычислительного процесса и фиксация момента окончания переходного процесса при умножении всевозможных чисел и делении для класса чисел, делящихся без остатм ка, при тсфровой точности подучаемого результата, что в совокупности расширяет функциональные возсможности устройства и- повьшюет его точность.

Формула изобретения

Вычислительное устройство, содержащее блок умножения и вычитатель, вьь ходы которого соединены с первой группо выходов результата устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет выполнения как «терапии деления, так и onepEUom умножения и повь шения точности за счет осуществления параллельного контроля вычисления, уст ройство содеркит два коммутатора, две схемы сравнения, первый, второй и третий сдвигатели и узел приоритета, причем входы первого операдда устройства соединены с первой группой входов первой схемы сравнения и первой группой информациошшх входов первого коммутатора, вторая группа информационных входов которого соединена с второй группой, входов первой схемы сравнения и вь ходами вычитателя, входы второго операнда устройства соединены с входами ,узла приоритета и информационными входами первогчэ сдвигателя, управляющие

1 входы которого подкгаоченьт к выходам уэла приоритета, выходы первого сдвигателя соединены с первой группой входов блока умножения, вторая группа входов которого соединена с выходами первого коммутатора, выходы рес льтата умножения блока умножения соединены с информационнь ми входами второго сдвигателя, первой Груцпой входов второй схемы сравнения и первой группой информашон- ных входов второго коммутатора, вторая группа информационных входов которого соединена с второй группой входов второй схемы сравнения и выходами третьег сдвигателя, информахщонньте входы кото- рого соединены с входами третьего операнда устройства, управляющие входы второго и третьего сдвигателей соединены с выходами узла приоритета, выходы второго коммутатора соединены с первой

группой входов вычитателя, вторая группа входов которого соединена с выходами промежуточной суммы частичных произведНИИ блока умножения, управляющие .первого и второго коммутаторов соёди ны с угщавляющим входом устройства, выходы второго сдвигателя соединены с второй Группой выходов результата устройства, вьхходы первой и второй схем сравнения соедйяены с вькодами контроля устройства.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1983-01-15—Публикация

1980-09-04—Подача