Изобретение относится к вычислительной технике и может быть использовано для работы в составе мультипроцессора быстродействующих ЭВМ,

Цель изобретения - повышение скорости выполнения операций преобразования из двоичной системы счисления в десятичную и наоборот.

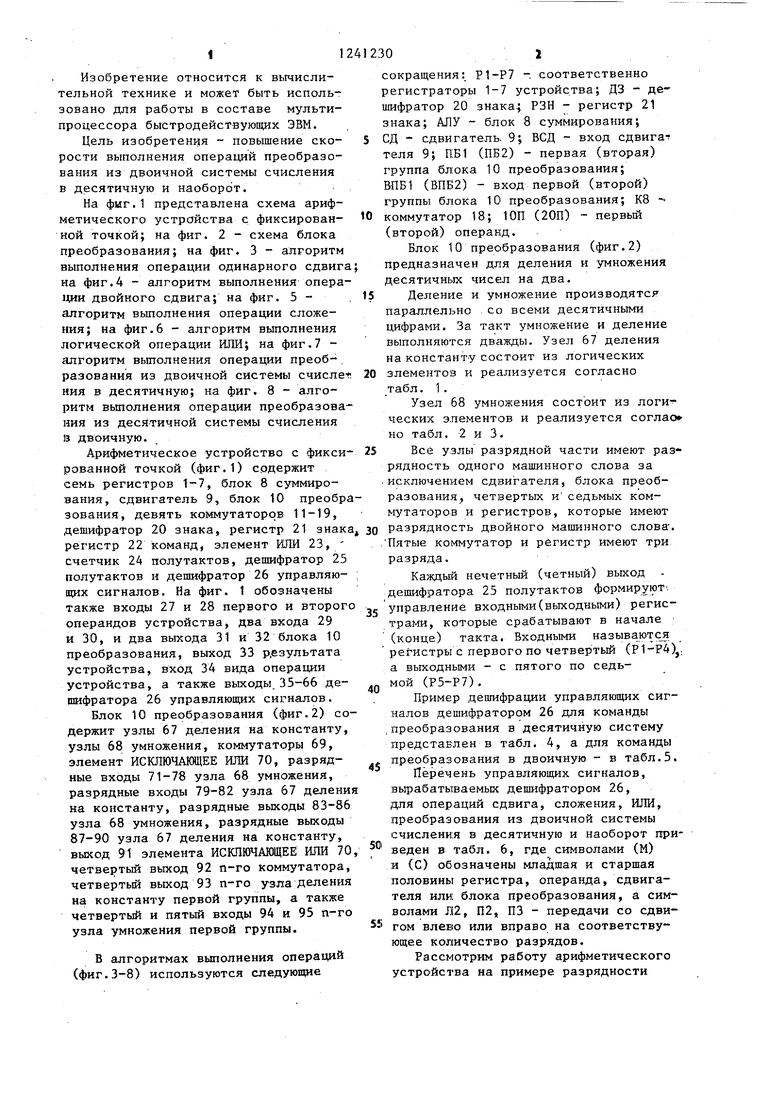

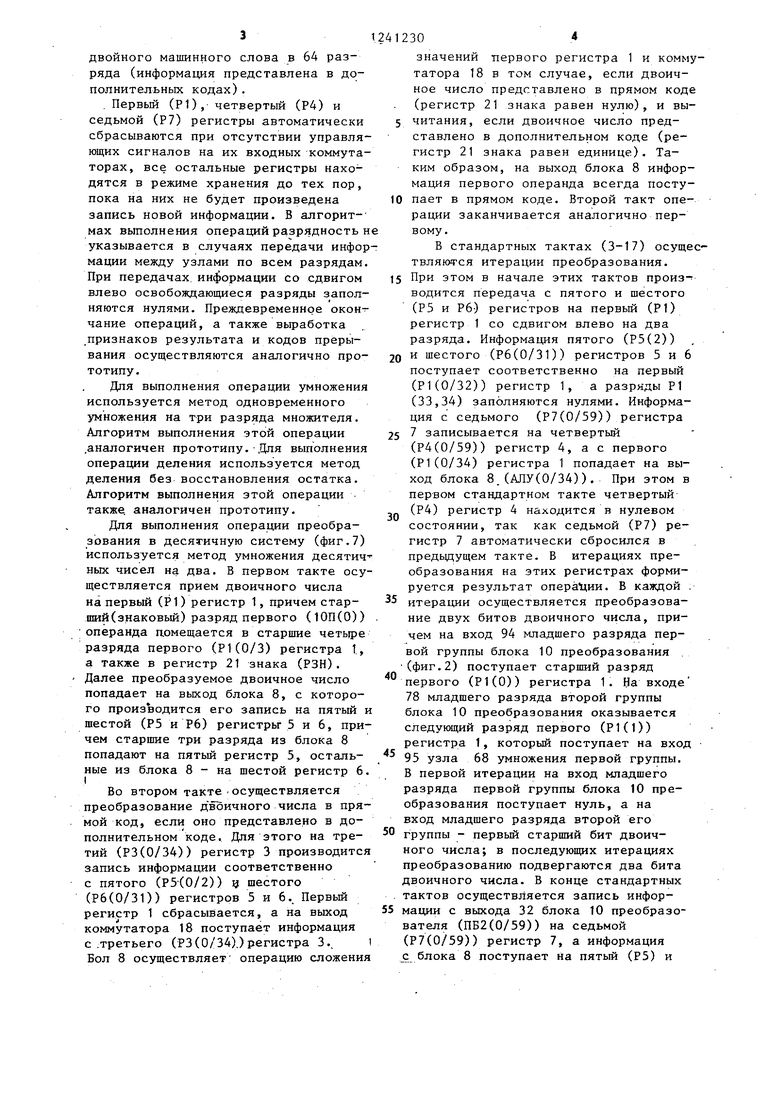

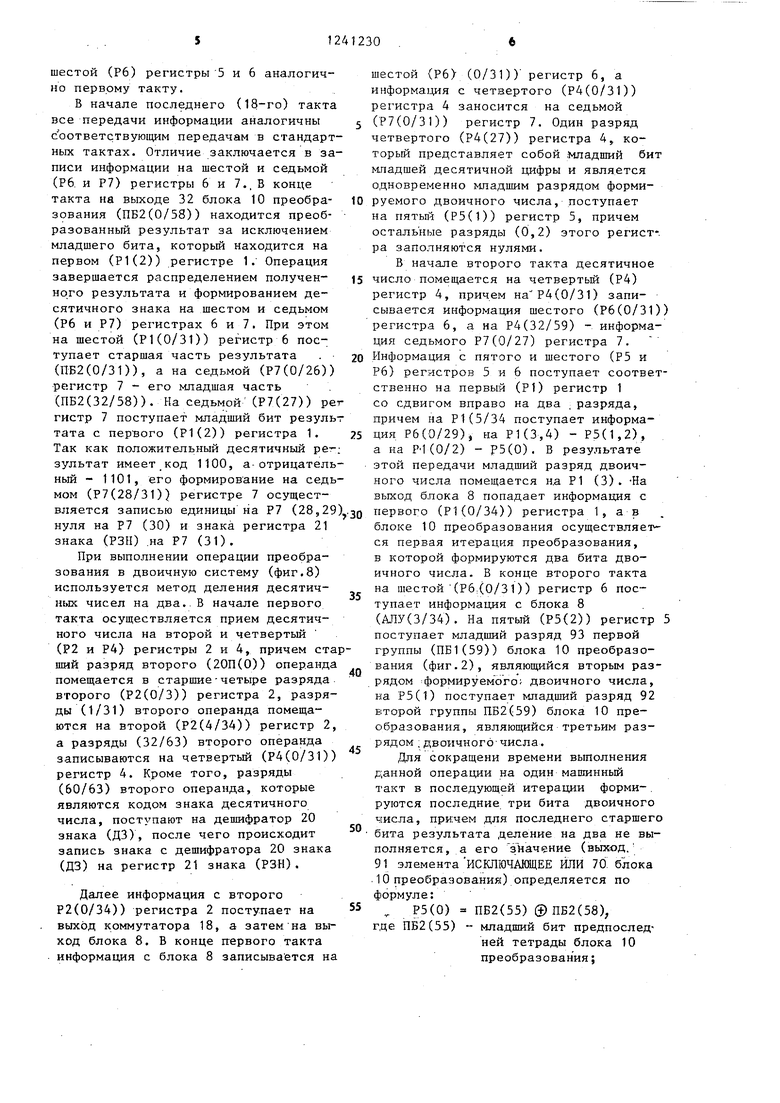

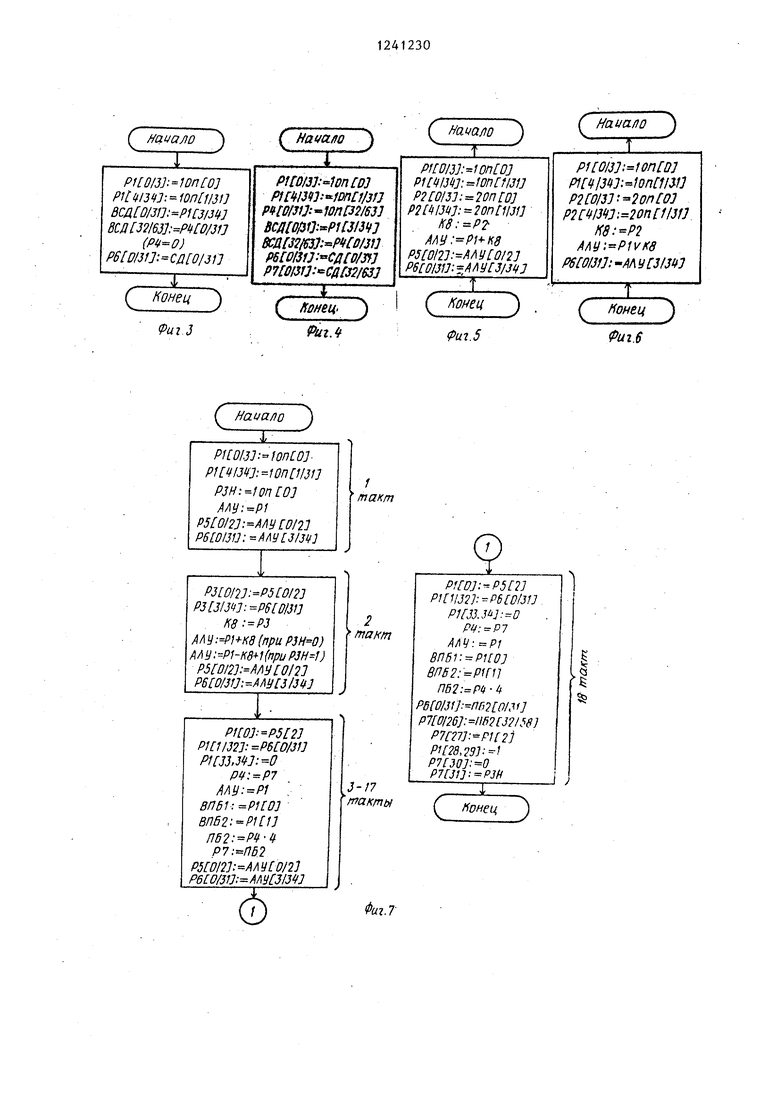

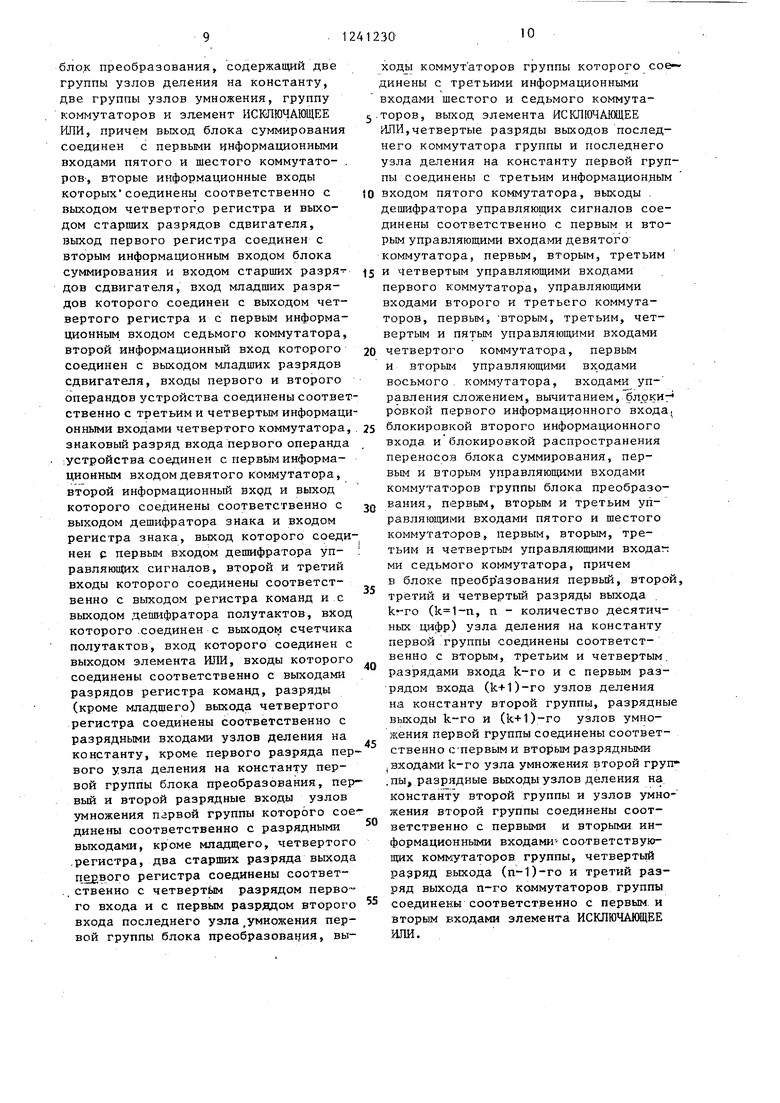

На фиг.1 представлена схема арифметического устройства с фиксированной точкой; на фиг. 2 - схема блока преобразования; на фиг. 3 - алгоритм выполнения операции одинарного сдвига на фиг.4 - алгоритм выполнения операции двойного сдвига; на фиг. 5 - алгоритм вьшолнения операции сложения; на фиг.6 - алгоритм выполнения логической операции ИЛИ; на фиг.7 - алгоритм вьтолнения операции преоб-. разования из двоичной системы счисле ния в десятичную; на фиг. 8 - алгоритм выполнения операции преобразова иия из десятичной системы счисления S двоичную.

Арифметическое устройство с фиксированной точкой (фиг.1) срдержит семь регистров 1-7, блок 8 суммирования, сдвигатель 9, блок 10 преобразования, девять коммутаторов 11-19, дешифратор 20 знака, регистр 21 sHaKE регистр 22 команд, элемент ИЛИ 23, счетчик 24 полутактов, дешифратор 25 полутактов и дешифратор 26 управляю- щих сигналов. На фиг. 1 обозначены также входы 27 и 28 первого и второго операндов устройства, два входа 29 и 30, и два выхода 31 и 32 блока 10 преобразования, выход 33 р.езультата устройства, вход 34 вида операции устройства, а также выходы.35-66 дешифратора 26 управляющих сигналов.

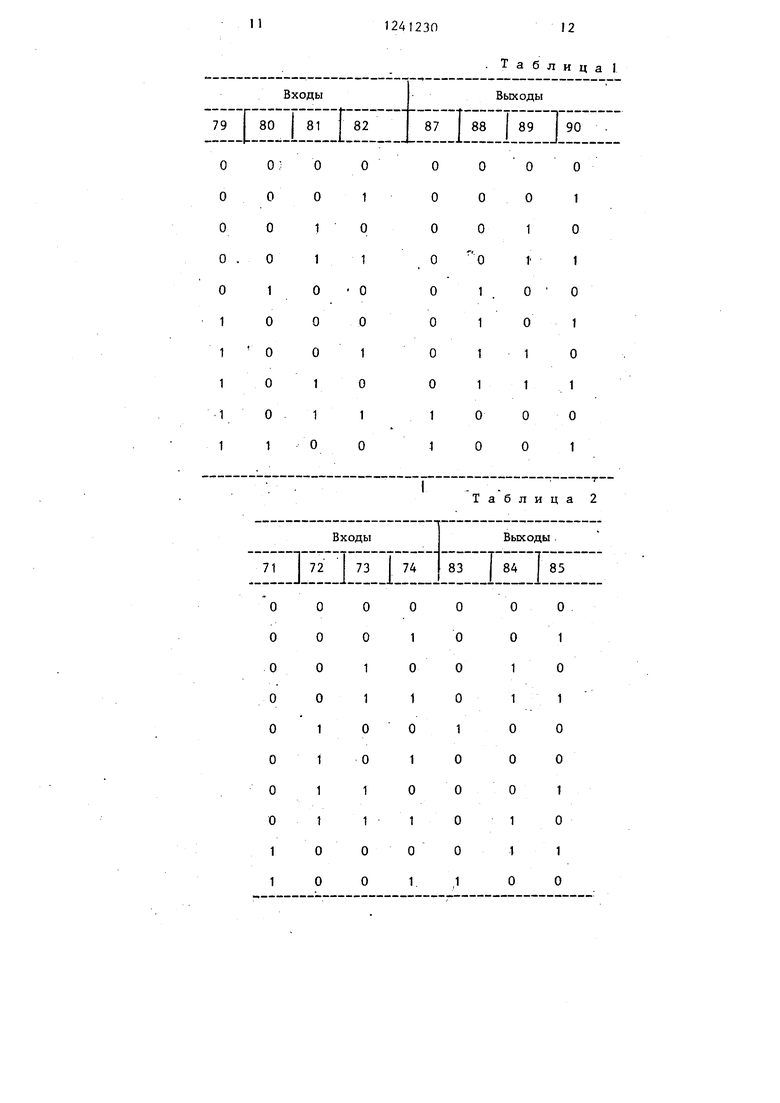

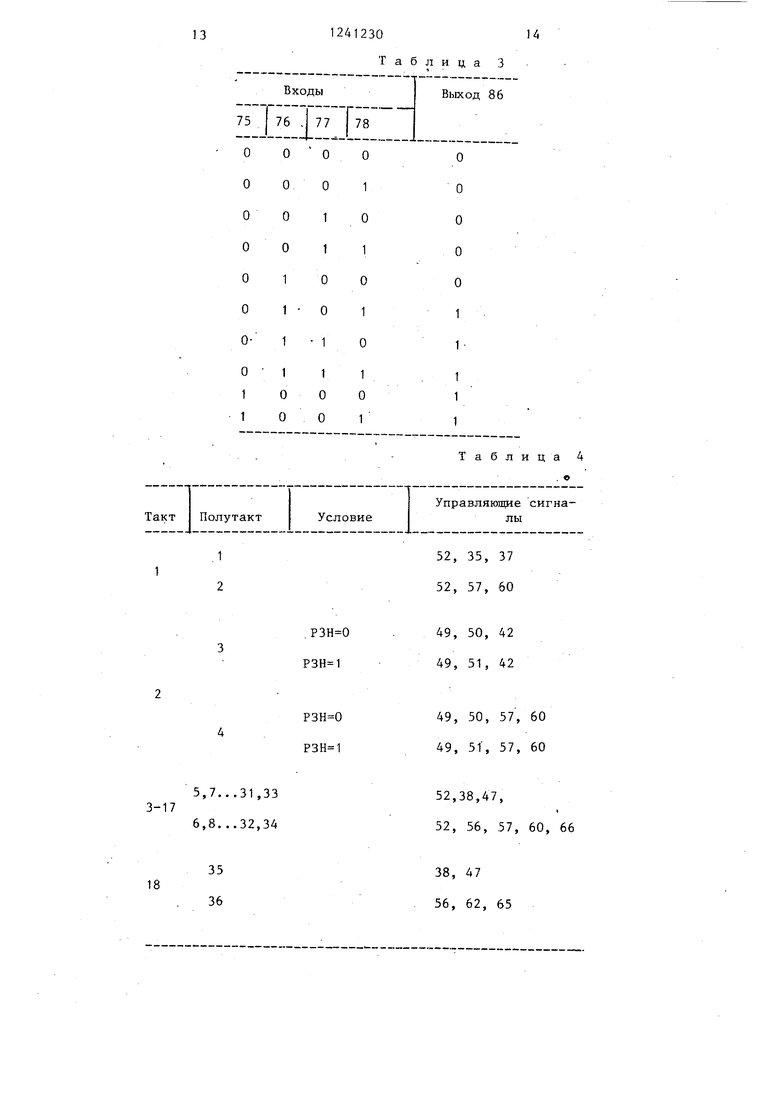

Блок 10 преобразования (фиг.2) содержит узлы 67 деления на константу, узлы 68 умножения, коммутаторы 69, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 70, разрядные входы 71-78 узла 68 умножения, разрядные входы 79-82 узла 67 делени на константу, разрядные выходы 83-86 узла 68 умножения, разрядные выходы 87-90 узла 67 деления на константу, выход 91 элемента ИСКПЮЧАЩЕЁ ИЛИ 70 четвертый выход 92 п-го коммутатора, четвертый выход 93 п-го узла деления на константу первой группы, а также четвертый и пятый входы 94 и 95 п-го узла умножения первой группы.

В алгоритмах выполнения операций (фиг.3-8) используются следующие

сокращения: Р1-Р7 -. соответственно регистраторы 1-7 устройства; ДЗ - де- шифратор 20 знака-; РЗН - регистр 21 знака; АЛУ - блок 8 суммирования;

СД - сдвигатель. 9; ВСД - вход сдвига-т теля 9; ПБ1 (ПБ2) - первая (вторая) группа блока 10 преобразования; ВПБ1 (ВПБ2) - вход первой (второй) группьз блока 10 преобразования; К8 -

коммутатор 18; 10П (20П) - первый (второй) операнд.

Блок 10 преобразования (фиг.2) предназначен для деления и умножения десятичных чисеип на два.

Деление и умножение производятся параллельно , со всеми десятичными цифрами. За такт умножение и деление выполняются дважды. Узел 67 деления на константу состоит из логических

элементов и реализуется согласно табл. 1.

Узел 68 умножения состоит из логи- ческих элементов и реализуется соглао но табл. 2 и 3.

Все узлы разрядной части имеют разрядность одного машинного слова за исключением сдвигателя, блока преобразования четвертых и седьмых ком- г-гутаторов и регистров, которые имеют

разрядность двойного машинного слова-. Пятые коммутатор и регистр имеют три разряда.

Каждый нечетный (четный) выход - дешифратора 25 полутактов формируют.

управление входными(выходными) регистрами, которые срабатывают в начале ; (конце) такта. Входными называются регистры с первого по четвертый (P1-P4)j: а выходными - с пятого по седьмой (Р5-Р7).

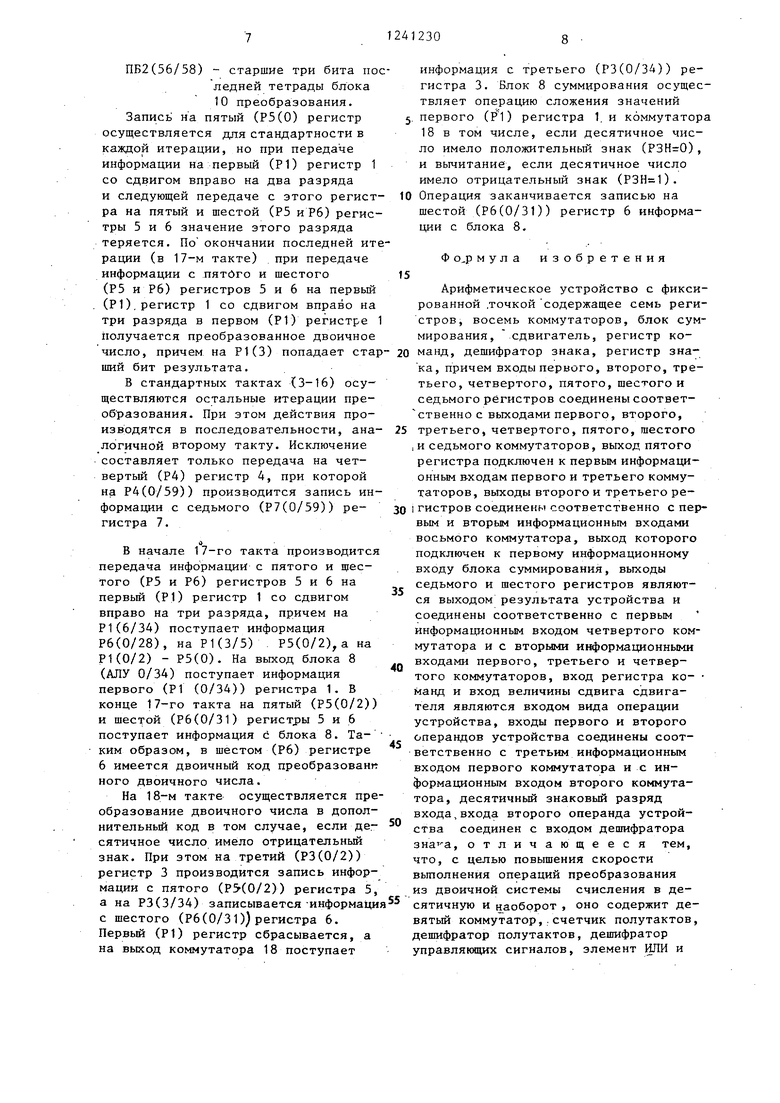

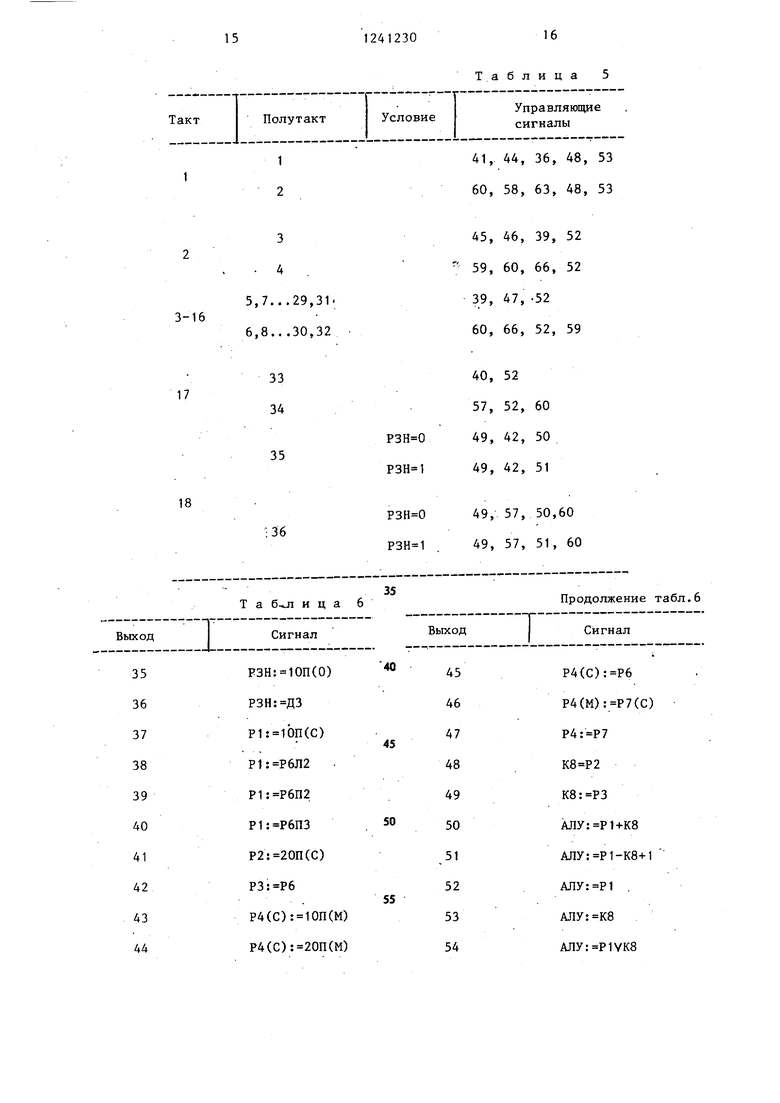

Пример дешифрации управляющих сигналов дешифратором 26 для команды преобразования в десятичную систему представлен в табл. 4, а для команды преобразования в двоичную - в табл.5.

Перечень управляюш;их сигналов, вьфабатываемых дешифратором 26, для операций сдвига, сложения, ИЛИ, преобразования из двоичной системы счисления в десятичную и наоборот приведен в табл. 6, где символами (М) и (С) обозначены младшая и старшая половины регистра, операнда, сдвигателя или блока преобразования, а сим- Л2, П2, ПЗ - передачи со сдвигом влево или вправо на соответствующее количество разрядов.

Рассмотрим работу арифметического устройства на примере разрядности

двойного машинного слова в 64 разряда (информация представлена в до;- полнительных кодах).

.Первый (Р1), четвертый (Р4) и седьмой (Р7) регистры автоматически сбрасываются при отсутствии управляющих сигналов на их входных коммутаторах, все остальные регистры находятся в режиме хранения до тех пор, пока на них не будет произведена запись новой информации. В алгоритмах вьтолнения операций разрядность не указывается в случаях передачи информации между узлами по всем разрядам. При передачах, информации со сдвигом влево освобождающиеся разряды заполняются нулями. Преждевременное окончание операций, а также вьфаботка признаков результата и кодов прерывания осуществляются аналогично прототипу.

Для выполнения операции умножения используется метод одновременного умножения на три разряда множитедя. Алгоритм выполнения этой операции .аналогичен прототипу. ,Для выполнения операции деления используется метод деления без восстановления остатка. Алгоритм выполнения этой операции также, аналогичен прототипу.

Для выполнения операции преобразования в десятичную систему (фиг.7) используется метод умножения десятич- ных чисел на два. В первом такте осуществляется прием двоичного числа на первьй (Р1) регистр 1, причем стар- пшйСз.наковый) разряд первого (10П(0)) . ;операнда помещается в старшие четьфе разряда первого (Р 1(0/3) регистра 1., а также в регистр 21 знака (РЗН). Далее преобразуемое двоичное число попадает на выход блока 8, с которого производится его запись на пятый и шестой (Р5 и Р6) регистры 5 и 6, причем старшие три разряда из блока 8 попадают на пятый регистр 5, остальные из блока 8 - на шестой регистр 6.

Во втором тактеосуществляется преобразование д воичного числа в пря- мой код, если оно представле.но в дополнительном коде. Для этого на третий (Р3(0/34)) регистр 3 производится запись информации соответственно с пятого (Р5-(0/2)) g шестого

(Рб(0/31)) регистров 5 и 6.. Первый регистр 1 сбрасывается, а на выход коммутатора 18 поступает информация с .третьего (РЗ(0/34).) регистра 3.. i

Бол 8 осуществляет операцию сложения

.

241230

значений

to

15

25

первого регистра 1 и коммутатора 18 в том случае, если двоичное число представлено в прямом коде (регистр 21 знака равен нулю), и вычитания, если двоичное число представлено в дополнительном коде (регистр 21 знака равен единице). Таким образом, на выход блока 8 информация первого операнда всегда поступает в прямом коде. Второй такт операции заканчивается аналогично первому.

В стандартных тактах (3-17) осуществляются итерации преобразования. При этом в начале этих тактов произ- водится передача с пятого и шестого (Р5 и Р6) регистров на первый (Р1) регистр 1 со сдвигом влево на два разряда. Информация пятого (Р5(2)) 20 и шестого (Р6(0/31)) регистров 5 и 6 поступает соответственно на первый (Р1(0/32)) регистр 1, а разряды Р1 (33,34) заполняются нулями. Информация с седьмого (Р7(0/59)) регистра 7 записывается на четвертый (Р4(0/59)) регистр 4, а с первого (Р1(0/34) регистра 1 попадает на выход блока 8,(АЛУ(0/34)). При этом в первом стандартном такте четвертый (Р4) регистр 4 находится в нулевом состоянии, так как седьмой (Р7) регистр 7 автоматически сбросился в предыдущем такте. В итерациях преобразования на этих регистрах формируется результат опера ции. В каждой . итерации осуществляется преобразование двух битов двоичного числа, причем на вход 94 младшего разряда первой группы блока 10 преобразования (фиг.2) поступает старший разряд первого (Р1(0)) регистра 1. На входе 78 младшего разряда второй группы блока 10 преобразования оказывается следующий разряд первого (Р1(1)) регистра 1, который поступает на вход 95 узла 68 умножения первой группы. В первой итерации на вход младшего разряда первой группы блока 10 преобразования поступает нуль, а на вход младшего разряда второй его группы - первый старший бит двоичного числа; в последующих итерациях преобразованию подвергаются два бита двоичного числа. В конце стандартных . тактов осуществляется запись инфор- 55 мации с выхода 32 блока 10 преобразователя (ПБ2(0/59)) на седьмой (Р7(0/59)) регистр 7, а информация с блока 8 поступает На пятый (Р5) и

30

35

40

50

шестой (Р6) регистры 5 и 6 аналогично первому такту.

В начале последнего (18-го) такта все передачи информации аналогичны сЪответствующим передачам в стандартных тактах. Отличие заключается в записи информации на шестой и седьмой (Р6. и Р7) регистры 6 и 7., В конце такта на выходе 32 блока 10 преобра- зования (ПБ2(0/58)) находится преобразованный результат за исключением младшего бита, который находится на первом (Р1(2)) регистре 1. Операция завершается распределением получен- ного результата и формированием десятичного знака на шестом и седьмом (Р6 и Р7) регистрах 6 и 7. При этом на шестой (Р1(0/31)) регистр 6 поступает старшая часть результата . (ПБ2(0/31)), а на седьмой (Р7(0/26)) регистр 7 - его младшая часть (ПБ2(32/58)). На седьмой (Р7(27)) per гистр 7 поступает младший бит резульг тата с первого (Р1(2)) регистра 1. Так как положительный десятичный результат имеет,код 1100, а-отрицательный - 1101, его формирование на седьмом (Р7(28/31)} регистре 7 осущест- впяется записью единицы на Р7 (28,29 нуля на Р7 (30) и знака регистра 21 знака (РЗН) .на Р7 (31).

При выполнении операции преобразования в двоичную систему (фиг.8) используется метод деления десятичных чисел на два.. В начале первого такта осуществляется прием десятичного числа на второй и четвертый (Р2 и Р4) регистры 2 и 4, причем сташий разряд второго (20П(0)) операнда

помещается в старшие-четыре разряда

второго (Р2(0/3)) регистра 2, разряды (1/31) второго операнда помещаются на второй (Р2(4/34)) регистр 2, а разряды (32/63) второго операнда записываются на четвертый (Р4(0/31)) регистр 4. Кроме того, разряды (60/63) второго операнда, которые являются кодом знака десятичного числа, поступают на дешифратор 20 знака (ДЗ), после чего происходит запись знака с дешифратора 20 знака (ДЗ) на регистр 21 знака (РЗН).

Далее информация с второго Р2(0/34)) регистра 2 поступает на выход коммутатора 18, а затем на выход блока 8. В конце п ервого такта информация с блока 8 записывается на

5 5 0 5 Q

0

5

0

шестой (Р6 (0/31)) регистр 6, а информа1дия с четвертого (Р4(0/31)) регистра 4 заносится на седьмой (Р7(0/31)) регистр 7. Один разряд четвертого (Р4(27)) регистра 4, ко- торьй представляет собой .младший бит м-падшей десятичной цифры и является одновременно младшим разрядом формируемого двоичного числа, поступает на пятьп (Р5(1)) регистр 5, причем остальные разряды (0,2) этого регист-. ра заполняются нулями.

В начале второго такта десятичное число помещается на четвертый (Р4) регистр 4, причем на Р4(0/31) записывается информа:ция шестого (Р6(0/31)) регистра 6, а на Р4(32/59) - информация седьмого Р7(0/27) регистра 7. Информация с пятого и шестого (Р5 и Р6) регистров 5 и 6 поступает соответственно на первый (Р1) регистр 1 со сдвигом вправо на два . разряда, причем на Р1(5/34 поступает информация Р6(0/29), на Р1(3,4) - Р5(1,2), а на Р 1 (0/2) - Р5(0). В результате этой передачи младший разряд двоичного числа помещается н.а Р1 (3). -На выход блока 8 попадает информация с первого (Р1(0/34)) регистра 1, а в блоке 10 преобразования осуществляется первая итерация преобразования, в которой формируются два бита двоичного числа. В конце второго такта на шестой (Рб;(0/31)) регистр 6 поступает информация с блока 8 (АЛУ(3/34). На пятый (Р5(2)) регистр 5 поступает младший разряд 93 первой группы (ПБ1(59)) блока 10 преобразования (фиг.2), являющийся вторым разрядом -формируемого; двоичного числа, на Р5(1) поступает мпадший разряд 92 второй группы ПБ2(59) блока 10 преобразования, являющийся третьим разрядом :ДВОИЧНОГО числа.

Для сокращени времени выполнения данной операции на один машинный такт в последующей итерации форми-. руются последние три бита двоичного чис.па, причем для последнего старшего бита результата деление на два не выполняется, а его зГнач ние (выход. 91 элемента ИСКЛЮЧАЩЕЕ ИЛИ 70 блока 10 преобразования) определяется по формуле:

Р5(0) ПБ2(55) ®ПБ2(58), где ПБ2(55) младший бит предпоследней тетрады блока 10 преобразования;

ПБ2(56/58) - старшие три бита по ледней тетрады блока 10 преобразования.

Запись на пятый (Р5(0) регистр осуществляется для стандартности в каждой итерации, но при передаче информации на первый (Р1) регистр 1 со сдвигом вправо на два разряда и следующей передаче с этого регистра на пятый и шестой (Р5 и Р6) регистры 5 и 6 значение этого разряда теряется. По окончании последней итрации (в 17-м такте) при передаче информации с пятого и шестого (Р5 и Р6) регистров 5 и 6 на первый . (Р1). регистр 1 со сдвигом вправо на три разряда в первом (Р1) регистре получается преобразованное двоичное число, причем на Р1(3) попадает стар ший бит результата.

В стандартных тактах (3-16) осуществляются остальные итерации преобразования. При этом действия производятся в последовательности, аналогичной второму такту. Исключение составляет только передача на четвертый (Р4) регистр 4, при которой на Р4(0/59)) производится запись информации с седьмого (Р7(0/59)) регистра 7.

о

в начале 17-го такта цроизводится передача информации с пятого и шестого (Р5 и Р6) регистров 5 и 6 на первый (Р1) регистр 1 со сдвигом вправо на три разряда, причем на Р1(6/34) поступает информация Рб(0/28), на Р1(3/5) Р5(0/2), а на Р1(0/2) - Р5(0). На выход блока 8 (АЛУ 0/34) поступает информация первого (Р1 (0/34)) регистра 1. В конце 17-го такта на пятый (Р5(0/2)) и шестой (Р6(0/31) регистры 5 и 6 поступает информация ci блока 8. Та- КИМ образом, в шестом (Р6) регистре 6 имеется двоичный код преобразована ного двоичного числа.

На 18-м такте осуществляется преобразование двоичного числа в дополнительный код в том случае, если десятичное число имело отрицательный знак. При этом на третий (РЗ(0/2)) регистр 3 производится запись информации с пятого (Р5 (0/2)) регистра 5, а на Р3(3/34) записывается информаци с шестого (Р6(0/31)) регистра 6. Первый (Р1) регистр сбрасывается, а на выход коммутатора 18 поступает

информация с третьего (Р3(0/34)) регистра 3. Блок 8 суммирования осуществляет операцию сложения значений 5. первого () регистра 1. и коммутатора 18 в том числе, если десятичное число имело положительньш знак (), и вычитание, если десятичное число имело отрицательный знак (). 10 Операция заканчивается записью на шестой (Р6(0/31)) регистр 6 информации с блока 8.

15

20

25

30

35

40

5

0

5

Ф о,р мула изобретения

Арифметическое устройство с фиксированной .точкой содержащее семь регистров, восемь коммутаторов, блок суммирования, сдвигатель, регистр команд, дешифратор знака, регистр зна- ка, причем входы первого, второго, третьего, четвертого, пятого, шестого и седьмого регистров соединены соответ- ственно с выходами первого, второго, третьего, четвертого, пятого, шестого , и седьмого коммутаторов, выход пятого регистра подключен к первым информационным в-ходам первого и третьего коммутаторов, выходы второго и третьего ре- I гистров соединены соответственно с первым и вторым информационным входами восьмого коммутатора, выход которого подключен к первому информационному входу блока суммирования, выходы седьмого и шестого регистров являются выходом результата устройства и соединены соответственно с первым информационным входом четвертого коммутатора и с вторыми )ормационными входами первого, третьего и четвертого коммутаторов, вход регистра ко- манд и вход величины сдвига сдвига- теля являются входом вида операции устройства, входы первого и второго операндов устройства соединены соответственно с третьим информационным входом первого коммутатора и с информационным входом второго коммутатора, десятичный знаковый разряд входа,входа второго операнда устройства соединен с входом дешифратора знат а, отличающееся тем, что, с целью повышения скорости вьтолнения операций преобразования из двоичной системы счисления в десятичную и наоборот , оно содержит девятый коммутатор,.счетчик полутактов, дешифратор полутактов, дешифратор управляющих сигналов, элемент ИЛИ и

блок преобразования, содержащий две группы узлов деления на константу, две группы узлов умножения, группу коммутаторов и эл.емент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выход блока суммирования соединен с первыми информационными входами пятого и шестого коммутато- . ров, вторые информационные входы которых соединены соответственно с выходом четвертого регистра и выходом старших разрядов сдвигателя, выход первого регистра соединен с вторым информационным входом блока суммирования и входом старших разрядов сдвигателя, вход младших разрядов которого соединен с выходом четвертого регистра и с первым информационным входом седьмого коммутатора, второй информационный вход которого соединен с выходом младших разрядов сдвигателя, входы первого и второго операндов устройства соединены соответственно с третьим и четвертым информационными входами четвертого коммутатора, знаковый разряд входа первого операнда ;устройства соединен с первым информационным входом девятого коммутатора, второй информационный вхрд и выход которого соединены соответственно с выходом дешифратора знака и входом регистра знака, вь&сод которого соединен р первым входом дешифратора уп- равляю1Цих сигналов, второй и третий входы которого соединены соответственно с выходом регистра команд и с выходом дешифратора полутактов, вход которого .соединен с выходом счетчика полутактов, вход которого соединен с выходом элемента ИЛИ, входы которого соединены соответственно с выходами разрядов регистра команд, разряды (кроме младщего) выхода четвертого регистра соединены соответственно с разрядными входами узлов деления на константу, кроме первого разряда первого узла деления на константу первой группы блока преобразования, первый и второй разрядные входы узлов умножения парвой группы которого соединены соответственно с разрядными выходами, кроме младщего, четвертого -регистра, два старших разряда выхода первого регистра соединены соответ- .,ственно с четвертым разрядом перво™ го входа и с первым разрддом второго входа последнего узла умножения первой группы блока преобразова1 ия, вы0

5

0

5

0

5

0

5

0

5

ходы коммутаторов группы которого сое динены с третьш 1и информационными входами шестого и седьмого коммута- ,торов, выход элемента ИСКЛЮЧАЩЕЕ дай,четвертые разряды выходов последнего коммутатора группы и последнего узла деления на константу первой группы соединены с третьим информационным входом пятого коммутатора, выходы . де1яифратора управляющих сигналов соединены соответственно с первым и вторым управляющими входами девятого коммутатора, первым, вторым, третьим и четвертым управляющими входами первого коммутатора, управляющими входами второго и третьего коммутаторов, первым, -вторым, третьим, четвертым и пятым управляющими входами четвертого коммутатора, первым и вторым управляющими входами восьмого . коммутатора, входами уп- равления сложением, вьиитанием,блоки- ровкой первого информационного входа блокировкой второго информационного входа и блокировкой распространения переносов блока суммирования, первым и вторым управляющими входами коммутаторов группы блока преобразования,, первым, вторым и третьим управляющими входами пятого и шестого коммутаторов, первым, вторым, третьим и четвертым управляюш|1ми входап ми седьмого ко.1мутатора, причем в блоке преобр азования первый, второй, третий и четвертый разряды выхода krro (, n - количество десятич- ньк цифр) узла деления на константу первой группы соединены соответственно с вторым, третьим и четвертым, разрядами входд k-ro и с первым раз- рядом входа (k+1)-ro узлов деления на константу второй группы, разрядные выходы k-ro и (k+1)-ro узлов умножения первой группы соединены соответственно с первым и вторым разрядными входами k-ro узла умножения второй груп .пы, разрядные выходы узлов деления на константу второй группы и узлов умножения второй группы соединены соответственно с первыми и вторыми информационными входами соответствующих коммутаторов группы, четвертый разряд выхода (п-1)-го и третий разряд выхода п-го коммутаторов группы соединены соответственно с первым, и Вторым входами элемента ИСКЛЮЧАЩЕЕ ШШ.

.

0.о

о

о

1

о

о

о

о

1

о о 1 1

о о о 1 1 о

Входы

llLllLl

о

О

о о 1 1 1 t о о

о о 1 1 о о 1 1 о о

Таблица

о

о

о

о

о

о

о

о

1

1

о о о о 1 1 1 1 о о

о

о

1

1

о

о

1

1

о

о

о

1

о

1

о

1

о

1

о

1

Таблица 2

74

О 1

О 1 О 1 О

1 о 1

83

О О О

о 1 о о о о 1

Выходы

85

и:

О О 1 1 О

о о 1 1 о

о 1

о 1 о о 1 о 1 о

13

1241230

Таблица 3

5,7...31,33 6,8...32,34

35 36

К

Таблица 4

52,38,47,

52, 56, 57,

38, 47 56, 62, 65

1

2

3

А

5,7...29,31. 6,8...30,32

33 34

35 : 36

Выход

I

Т а б-м и ц а 6 Сигнал

(0)

(C)

(С)

Р4(С)(М)

Р4(С)(М)

Таблица

41,. 44, 36, 48, 53 60, 58, 63, 48, 53

45, 46, 39, 52

59,60, 66, 52

39,47, -52

60,66, 52, 59

40,52

57, 52, 60 49, 42, 50 49, 42, 51

49, 57, 50,60 49, 57, 51, 60

Выход

Т

Продолжение табл.6 Сигнал

45

46

47

48

49

50

51

52

53

54

Р4(С)

Р4(М)(С)

АЛУ: Р1+К8

АЛУ: Р1-К8+1

АЛУ: Р1УК8

171241230

Продолжение табл.6

Продолжение табл.6

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство к однопериодному перфоратору для запоминания набираемых чисел | 1958 |

|

SU119733A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для преобразования чисел из кода системы остаточных классов в позиционный код с контролем ошибок | 1991 |

|

SU1797119A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для выдачи сообщений | 1989 |

|

SU1709367A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1987 |

|

SU1425708A1 |

| РАДИОМОДЕМ | 2010 |

|

RU2439820C1 |

Изобретение относится к вычислительной технике и может быть использовано дли работы в составе мультипроцессора, быстродействующих ЭВМ. Цель изобретения - повышение скорости выполнения операций преобразования из двоичной системы счисления в десяг тичную и наоборот. В устройство, содержащее семь регистров, восемь коммутаторов, блок суммирования, сдвига- тель и регистр команд, введены блок преобразования, , девятый коммутатор, регистр знака, злемент ИЛИ, счетчик полутактов, дешифратор полутактов, и дешифратор управляюпщх сигналов, а также оригинальная организация связей между блоками. 8 ил, 6 табл. (Л с N3 со

Фи1.1

л (&(ii.i

Мачало

Havaffo j -

Риг 5

AfZ.«

С НачалоJ

фиг.5

Фиг.6

Фиг. Т

Снацшю J

Р2Ш31 : P2CO/3J:-P i:u/31 :

РЗН:

КбAM

Р7 0тР6 0131 :

P5L11 :

Р5СОт:

2onL1l313

2оп 32/63

-D3

Р2

К8

.

PH27J

0

P 0 31 : P6i:o/31 P 32I53J: P7 OI27 ,2 .P5L01 П62-

PS 0/JO; Myi:3l3 J P5C2 : nSH59 P5 Dr---n52(L55 @L581

(раг.8

Редактор А.Огар

Составитель А.Клюев

Техред Н.Бонкаг О- Корректор М.ДемчикЗаказ 3489/43Тираж 671 . Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений И открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Pit-i Pl

P1 5lЗ J P6l:D/26 P1 D/2 1-P5 D

A/iy-P

)

P1C3/5 : P5 0/2 - PH6l3ii- : P6 D/28J

. P5LDI2 i AAy D/2 P6 0/31J: AM 3/3i

P3LD19J-5LOI21

. l dinpu ) A A У {n.pu P3H 1)

P5 DI2 : AAHOI23

Нонец j

| Патент США № 3462744, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Приспособление к индикатору для определения момента вспышки в двигателях | 1925 |

|

SU1969A1 |

| Регулятор для вертикальных ветряных двигателей | 1925 |

|

SU2060A1 |

Авторы

Даты

1986-06-30—Публикация

1984-12-26—Подача