Изобретение относится к цифровой вычислительной технике и может найтиv применение для аппаратной реализации вычисления функций.

По основному эвт. св. № 744590 известен цифровой функционашьный преобразователь, содержащий четыре сумматора-вычитателя, два регистра, блок анализа и блок управления, причем выходы блока анализа соединены с первыми управляющими входами первого - четвертого сумматоров-вычитателей и с входом блока управления, первый выход которого соединен с управляющими .входами регистров, а второй выход - с вторыми управляющими входами сумматоров-вычитателей, выход первого регистра соединен с первыми входами первого и второго сумматоров-вычитателей, вторые входы которых соединены с входом первого регистра и первым входом цифрового функционального преобразователя, выход второго регистра соединен с первыми входами третьего и четвертого сумматоров-вычитаталей, вторые входы которых соединены с входом второго регистра и вторым входом цифрового функционального преобразователя, выходы первого и третьего сумматороввычитателей соединены соответственно с первым и вторым входами блока анализа.

с Этот цифровой функциональный преобразователь предназначен для вычисления трех функций 2ху/(х+у), 2х /(х+у) и 2yV(x+y) .2.

Недостатком известного преобразо 0 вателя являются ограниченные функциональные возможности.

Цель изобретения - расширение Класса решаемых задач за счет дополнительного вычисления Функций)х-уЯ /СХ+У). (Зху-х)/(х+у) и (Зху-у }7 /ТХ-ЬУ).

Поставленная цель достигается тем, что в цифровой функциональный преобразователь введены три сумматоравычитателя ,, первые управляющие вхо20ды которых соединены с первым выходом блока анализа, вторые управляющие входы сумматоров-вычитателей соединены со вторымвыходом блока управления первые информационные входы пятого

25 и седьмого сумматоров-вычитателей

соединены.с выходом второго регибтра, первый и второй информационные входы шестого сумматора-вычитателя и вторац информационные входы пятого и седьмо-

30 го сумматоров-вычитателей соединены

с выходом первого регистра, третий информационный вход пятого сумматоравычитателя соединен с входом пуска преобразователя, третьи информационные входы шестого и седьмого сумматоров-вычитателей соединены.с первым входом преобразователя.

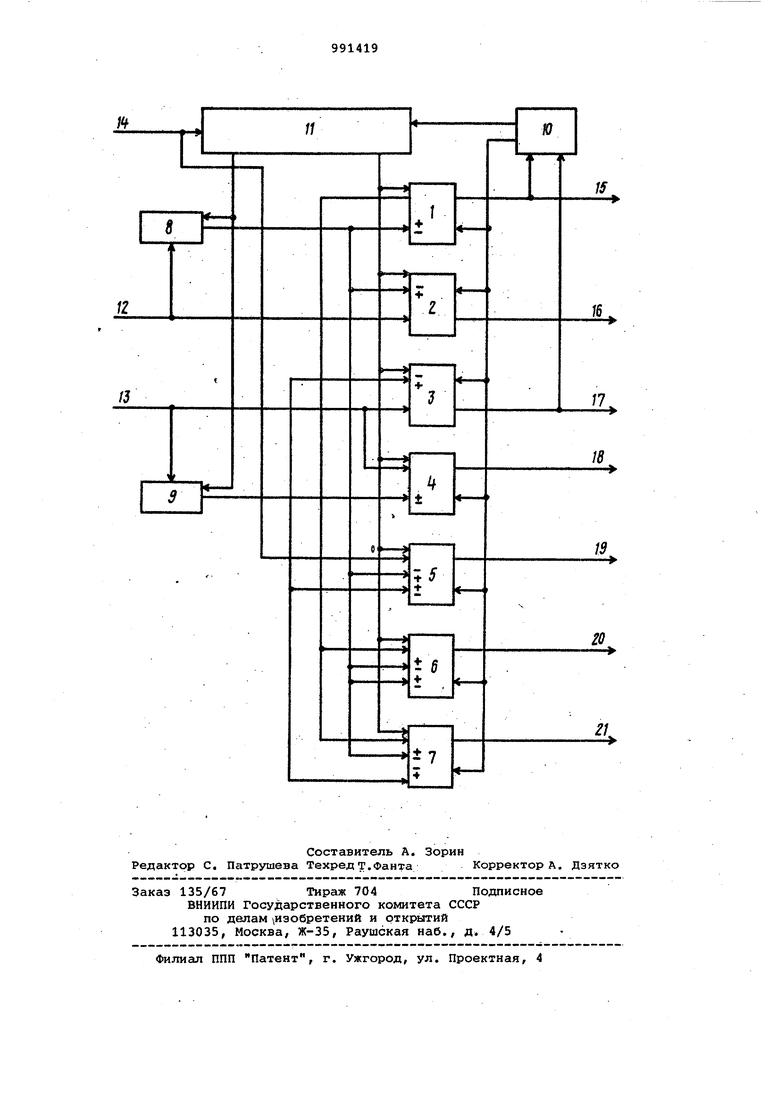

На чертеже приведена блок-схема преобразователя.

Преобразователь содержит сумматоры- вычи тат ели 1-7, регистры 8 и 9, блок 10 анализа, блок 11 управления, входы 12-14 преобразователя и выходы 15-21 преобразователя.

Сумматоры-вычитатели 5-7 могут быть выполнены либо в виде многоразрядной параллельной комбинационной логической схемы (матрицы) сложениявычитания, либо в виде последовательной схемы, содержащей одноразрядные сумматоры-вычитатели и регистр. Управляющий вход одноразрядного сумматор а- вычитател я является первым управляющим входом сумматора. Вход сдвига регистра является BIорым управляющим входом. Вход1Л первого одноразрядного сумматора-вычитателя явля ются первым и вторым информационными входами. Информационный вход регистра является третьим входом, а выход регистра является выходом сумматор-вычитателя.

Блок 11 управления содержит генератор импульсов, два триггера, счетчик, дешифратор, пять элементов И, три элемента ИЛИ и два элемента задержки, причем первый вход блока управления соединен.с первым входом первого элемента ИЛИ, входом первого элемента задержки и первым входом второго элемента ИЛИ, выход которого соединен с первым входом первого триггера, прямой и инверсный выходы которого соединены с первыми входами первого и второго элементов И, вторые входы которых соединены с выходом генератора импульсов, входы пуска и останова которого соединены с выходом первого элемента задержки и вторым входом блока управления соответственно, второй вход первого триггера соединен с выходом дешифратора, третьим выходом блока управления и первыми входами третьего и четвертоjго элементов И, вторые входы которых соединены с третьим входом блока управления, первый выход которого является выходом третьего элемента ИЛИ, первый вход которого соединен с выходом пятого элемента И, первый вход которого соедийен с прямым выходом .второго триггера, входы которого соединены с выходами четвертого элемента И и первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, выход первого элемента И соединен со вторым входом

третьего элемента ИЛИ, вторым входом блока управления и входом счетчика, выход которого соединен со входом дешифратора, выход второго элемента И соединен со вторым входом пятого элемента И через второй элемент задержки со вторым входом второго элемента ИЛИ, выход первого триггера является четвертым выходом блока управления.

Вычисления функций в данном преобразователе основано на одновременном решении системы разностных рекуррентных соотношений в итерационном процессе, ..

ло VN

х.,Х.с.хг Х v Уj -- j-cyj a- %-.

ах

--)

-JM-Zj- .- 2„

Io--X

0

о- . U,Vo-0 Nj4r- r4j 2:V v,-- :

л (

%Х N(/j.,,.jX2:

; Xil-V

о Qj,,,

где 3 О, п - номер итерации,

i О, п - вес или показатель

итерации /

п - число разрядов операнда (одного из аргумпнтов).

Рекуррентные соотношения алгоритма обладают рекуррентными свойствами и вычисляются одновременно в одном итерационном процессе. Каждое соотношение может вычисляться либо параллельно за один такт, либо последовательно за n+m тактов, где m Hlog rfчисло дополнительных заиштных разрядов регистров и сумматоров-цычитателей для компенсации погрешности усечения чисел при их сдвиге. Соотношение х- реализуется в сумматоре-вычитателв 1, соотношение у. реализуется в сумматоре-вычитателе 3, соотношение ZJ реализуется в сумматоревычитателе 2, соотношение Uj реализуется в сумматоре-вычитателе 4, соотношение V; реализуется в сумматоре-вычитателе 5, соотношение W: реализуется в сумматоре-вычитателе б, соотношение Q.I реализуется в. сумматоревычитателе V. Значения у2г получаются соответственно в регистрах 8 и 9. Логическое уравнение у- -х. решается в блоке 10 анализа. .Вычисления в преобразователе осуществляются следующим образом.

Первоначальное значение кода х устанавливается в регистр вив еумматоры-вычитатели 1-2 и 6-7, а значение кода у устанавливается в регистр 9 и в сумматоры-вычитателн 3-4 По стартовому импульсу с входа 14 устанавливается нулевое значение в сумматоре-вычитаТеле 5.

В момент,- появления в блоке управления импульса конца итерации в блоке 10 анализа вырабатывается значение цифры q- для следукяцей итерации. При значений а. --«-1 в сумматорах- . вычитателях 1,4, б, по первому и второму входам сумматоров-вычитателей 5 и 7 выполняется сложение, а в сумматорах-вычитателях 2-3, по второму входу сумматора-вычитателя 5 и по первому входу сумматора-вычитателя 7 выполняется вычитание. При q; / -1 режим их работы меняется на обратный.

При равенстве содержаний х и у: в сумматорах-вычитателях 1 и 3, J в блоке 10 анализа формируется сигнал на втором выходе, по которому в блоке 11 управления выключается генератор тактовых импульсов х и процесс вычисления закончен. При это в сумматорах-вычитателях 1 и 3 (выходы 15 и 17) содержится значение функции 2ху/(х+у), в сумматоре-вычитателе 2 (выход 16) содержится значение фукнции 2xV(x+y), в сумматоревычитателе 4 (выход 18) содержится значение функции (х-«-у), в сумматоре-вычитателе 5 (выход 19)содержится значение функции (х-у) /(х+у), в сумматоре-вычйтателе б (выход 20)5. содержится значение функции (Зху-х) /(х-«-у), в сумматоре-вычитателе 7 (выход 21) содержится значение функции (Зху-у)/(х-|-у) .

Максимальное время вычисления одновременно шести указанных функций в данном преобразователе для параллельного принципа работы в тактах равно , а для последовательного принципа работы в тактах равно

Тк,(п+т+1). .

Однако благодаря асинхронному режиму работы (прерывание процесса вычисления при х yi) для большинства значений арп ментов время вычисления значительно меньше максимального значения, так как процесс оканчивается на итерации, номер которой меньше значения п.

В обгцем случае погрешность вычис-. ления указанных функций определяется

0 длиной разрядной сетки регистров и сумматоров и при использовании дополнительных разрядов m всегда меньше единицы последнего младшего разряда п.

5

Формула изобретения

Цифровой функциональный преобраQ эователь по авт. св. 744590, о тличающийся тем, что, с целью расширения класса решаемых задач за счет дополнительного вычисления функций (х-у)/(х-у), (Зху-х / 5 /(х+у) и (Зху-у)/(), в него введены три сумматора-вычитателя, первые управляющие входы которых соединены с первым выходом блока анализа, вторые управляющие входы сумматоров-вычитателей соединены со вторьм выхо0дом блока управления, первые информационные входы пятого и седьмого сумматоров-вычитателей соединены с выходом второго регистра, первый и второй информационные входы шестого

5 сумматора-вычитателя и вторью информационные входы пятогр и седьмого сумматоров-вычитателей соединены с выходом первого регистра, третий информационный вход пятого сумматора0вычитателя соединен с входом пуска преобразователя, третьи информационные входы шестого и седьмого сумматоров-вычитателей соединены с первым входом преобразователя.

5

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР 744590, кл, G Об F 7/38, 1978 (прототип) ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1977 |

|

SU693379A2 |

| Цифровой функциональный преобразователь | 1980 |

|

SU926666A2 |

| Арифметическое устройство | 1980 |

|

SU960802A2 |

| Конвейерное устройство для вычисления гиперболических функций | 1981 |

|

SU1026141A1 |

| Цифровой функциональный преобразователь | 1976 |

|

SU748434A1 |

| Цифровой функциональный преобразователь | 1976 |

|

SU744590A1 |

| Устройство для преобразования систем координат | 1976 |

|

SU656069A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Вычислительное устройство | 1981 |

|

SU959071A1 |

Авторы

Даты

1983-01-23—Публикация

1980-05-20—Подача