Изобретеиие относится к цифровой вычислительной технике и может быть использовано при построении специализированных ЦВМ

Известно вычислительное устройство, предназначенное для решения задач поворота вектора на плоскости с использованием алгоритмов .Вопдера 1.

Недостатком такого устройства являются ограниченные функциональные возможности.

Наиболее близким к изобретению является вычислительное устройство 2, осуществляющее опергщию вращения вектора в плоскости вокруг оси. В таком устройстве операция вргицения вектора в плоскости xov вокруг оси 2.

cose -sineg О SineQ-cosQp О

выполняется по алгоритму .

V,x,-x,.-(,.,:r-

.,v -- VV- -.

.2 -2+Z.

в|м1вг,-. (

5 где Х ,V.,2f,e,- - значение координат

и угла на i-й ите.. ,. рации ;сА 1 arete--1 угловая постоянная

10 ,3,--,п.

. Недостатком устройства является то, что для последующих вращений вокруг оси Ч,

(5)

20

25

(4)

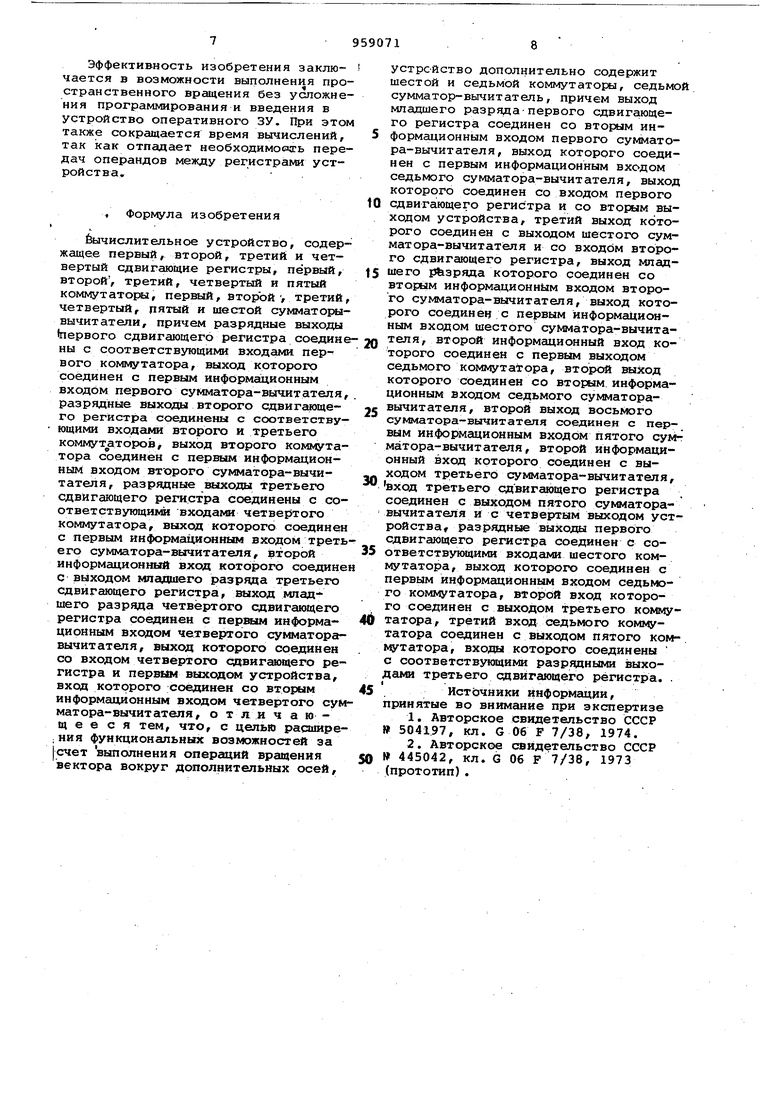

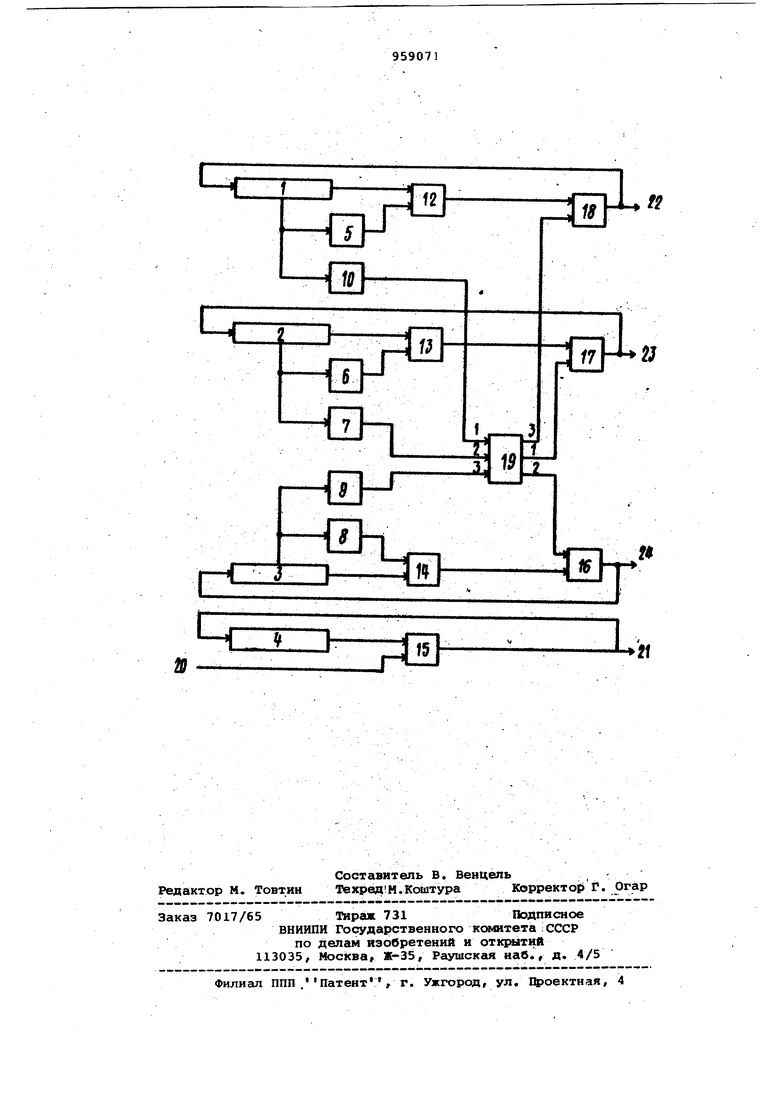

необходимо Выполнить пересылки данных между регистргми, что Приводит к ус ложнению программирования и потребует У введения в устройство оперативного ЗУ. Целью изобретения является расши рение функциональных возможностей за счет выполнения операций вращени вектора вокруг дополнительных осей. Поставленная цель достигается тем, что в вычислительное устройств содержащее первый, второй, третий и четвертый сдвигающие регистры, первый, второй, третий, четвертый и пятый коммутаторы, первый, второй, третий, четвертый пятый и шестой су маторы-вычитатели, причем разрядные . выходы первого сдвигающего регистра соединены с соответствующими входами первого коммутатора, выход которого соединен с первым информационным входом первого сумматоравычитателя, разрядные выходы второго сдвигающего регистра соединены с соответствующими входами второго и третьего коммутаторов, выход второго коммутатора соединен с первым информационным входом второго сумма тора- вычитател я, разрядные выходы третьего сдвигающего регистра соединены с соответствующими входами четвертого коммутатора, 1зыход которого соединен с первым информационным входом третьего сумматора-вычитателя, второй информационный вход которого соединен с выходом мпадшег.о разряда третьего сдвигающего регистра, выход младшего разряда четвертого сдвигающего регистра соединен с первым информационным входом четвертого сумматора-вычитателя,выход которого соединен со входом четвертого сдвигающего регистра и первым выходом устройства, вход которого соединен со вторым информационным-входом четвертого сумматора вычитателя, дополнительно введены шестой и седьмой коммутаторы, седьмой сумматор вычитатель, причем выход младшего разряда первого сдвигающего регистра соединен со вторым информационным входом первого сумматора-вычитателя, выход которог соединен с первым информационным входом седьмого сумматора вычитатеп выход которого соединен со входом первбго сдвигающего регистра и со вторым выходом устройства, третий выход которого соединен с выходом шестого сумматора-вычитателя и со вхсйом второго сдвигающего регистра BHjjpjt младшего разряда которого сое динен со вторым информационным эходом второго сумматора-вычитателя, выход которого соединен с первым ин формационным входом шестого суммато ра-вычиТателя, второй информационны вход которого соединен с первым выходом седьмого коммутатора , второй выход которого соединен со вторым информационным входом седьмого сумNfaTopa-вычитатепя, второй выход восьмого сумматора-вычитателя соеди нен с первым информационным входом пятого сумматора-вычитателя, второй информационный вход которого соединен с выходом третьего сумматора-вычитателя, вход.третьего сдвигающего регистра соединен с выходом пятого сумматора-вычитателя и с четвертым выходом устройства, разрядные выходы первого сдвигающего регистра соединены с соответствующими входами шестого коммутатора, выход которого соединен с первым информационным входом седьмого коммутатора, второй вход которого соединен с выходом третьего коммутатора, третий вход седьмого коммутатора соединен с выходом пятого коммутатора, входы которого соединены с соответствующими разрядными выходами третьего сдвигающего регистра. На чертеже представлена структурная схема устройства. Устройство содержит первый, второй, третий и четвертый сдвигающие регистры 1-4, первый, второй, третий, четвертый, пятый, шестой и седьмой коммутатора 5-10 и 19, первый, второй, третий, четвертый, пятый, шестой и седьмой сумматоры-вычитатели 12-18,ВХОД устройства 20 и первый, второй, третий и четвертый выходы устройства 21-24. Устройство работает след5 щим образом. Для пространственного поворота вектора XQ , У , г последовательно выполняются преобразования.(1), (3) и (4). Координаты ZQ, Хд и У предварительно заносятся в регистры , соответственно. Преобразование (1) выполняется по алгоритму (2). Координата во2 заносится в регистр 4. По команде из устройства управления коммутатор 10 закрывается, а в коммутаторе 19 вход 2 коммутируется на выход 2, вход 3 - на выход 1, а выход 3 закрыт. Вычисления в i+1-й итерации выполняются следующим образом. На сумматоре- вычитателе 12 производится сложение координаты 2ц с величиной , получаемой на коммутаторе 5. CyMMaZ rZ.+Z. через сумматор-вычйтатель 18 перезаписывается в регистр I. На сумматоревычитателе 13 производится вычитание их координаты Х величины , получаемой на коммутаторе б. Разность Xi-X складывается с учетом знак1 на сумматоре-вычитател 15 с величиной получаемой на коммутаторе 9. Очередное прибли,-2(м; -(-3 женйе X. ,Х,-Х.-1 1+1 1 1 записывается в регистр 2. На сумматоре вычитателе 14 производится вычита)ние из. координаты У) величины У ч 2-1(i-1) получаемой на коммутаторе 8. Разность y,v-y,- складывается с учетом знака .+ f на суммат.ор вычитателе 16 с величиной Х получаемой на коммутаторе 7. Очеред ное приближение У,, У.( +У - + записывается в регист 3, На -сумматоре-вычитателе 15 производится- вычитание с учетом знака из координаты 0, хранимой в регист ре 4, величины ct, поступающей со входа угловой константы. Очередное приближение - dL- , записывает в регистр 4. Аналогично описанному выполняетс п итераций (п-разрядность операндов и далее выполняется поворот на угол SOY вокруг оси 4(3). Преобразовани выполняется по алгоритму. . ,,VV - 4rV 9i4r r,. Координаты Z, X,У находятся в ре гистрах 1-3 соответсГвенно. Координата QOY заносится в регистр 4. По команде из устройства управления коммутатор 9 закрывается, а в коммутаторе 11 вход 2 коммутируется на выход 1, вход 1 коммутируется на вы ход 2, а выход 3 3 акрыт. Вычисления в i+1-й итерации выполняются следующим образом, В сумматоре-вычитателе 14 производится сложение координаты У с величной У - 2( , получаемой на коммутаторе 8. Сумма + через сумматор-вычитатепь 16 записы вается в регистр 3. На сумматоревычитателе 12 производится вычитани из координаты Z величины , Z получаемой на коммутаторе 5. Разность на сумматоревычитателе 18 суммируется с учетом знака -fi с величиной (3i, JJQ лучаемой на коммутаторе 7. Очередное Z --7-7 . Y .-1-{ приближение „ .i.j ij t-; L X 2. - , ITTТ1 записывается в регистр 1. На сумматоре-вычитателе 13 производится вычитание из координаты Х величины . , получаемой на коммутаторе 6. Разность X,-X:;-1 суммируется с учетом знака 4 на cyNMaторе-вычитателе 17 с величиной 2 . , получаемой на коммутаторе 10. Очередное приближение .-х.к x21( х, записывается в регистр 2. Координата i вычисляется (сводится к нулю) так же, как и при повороте вокруг оси. Аналогично описанному выполняётс я п итераций и далее выполняется поворот на угол .бох вокруг оси Х{4). Преобразование (4) выполняется по алгоритму X. X.fX.-2 1+1 1 1 4,r -J- -.f,v.. ,-- i°i(Ь) Координаты 2,У/Х находятся в ре истрах 1-3 соответственно. Координата QOX заносится в регистр 4. По команде из устройства управления коммутатор 7 закрывается, а в коммутаторе 19 вход 1 коммутируется на выход 2, вход 3 - на выход 3, а выход 1 3 акрыт. Вычисления i+1-й итерации выполняются следующим образом. На сумматоре-вычитателе -13 производится сложение координаты X,,- с величиной Х x2-( f получаемой на коммутаторе 6. Сумма Xi,.X, + X4 - 2( через ре 6. Сумма - : - - ч.сус сумматор-вычитатель 17 записывается в регистр 2. На сумматоре-вычитателе 12 производится вычитание из коорди наты Zv величины ;-2 , получаемой на. коммутаторе 5. Разность 2 2.. 2-2. на сумматоре-вычитателе 18 с учетом знака +fi суммируется с величиной 4i-2-fi-3) , получаемой на коммутаторе 9. Очередное приближе,HHez..Z.-Z.,-V,-r записывается в регистр 1. На сумматоре-вычитателе 14 производится вычитание из координаты У величины У:; 2 , получаемой на коммутаторе 8. Разность суммируется с учетом знака -f на сумма- торе вычитателе 16 с величиной , олучаемой на ко)умутаторе 10. Очерёдное приближение Уi 4i Уп .-(1-э; -,-zr2 записывается в регистр 3.. Координата 9,-+v, вычисляется (сводится к нулю) таким же образом, как;и при поворотах вокруг осей X и Y. Аналогичным образом выполняется п итераций. На этом вычисления заканчиваются. Координаты X, У, Z вектора, повернутого в пространстве вокруг осей Z, У, X, могут выдаваться из устройства при выполнении последней итераии последовательным кодом по первоу, второмуИ четвертому выходам устойства или после окончания вычислеий параллельным кодом из регистров 1-3, С третьего выхода устройства процессе вычислений выдается знаение ,- , Порядок поворота вектора Г(5, iiQ вокруг реей Z, У, X может j ии« ыть произвольным. Эффективность изобретения заключается в возможности выполнения пространственного вращения без усложнения программирования и введения в устройство оперативного ЗУ. При этом также сокращается время вычислений, так как отпадает необходимость передач операндов между регистрами устройства. Формула изобретения бычислительное устройство, содержащее первый, второй, третий и четвертый сдвигающие регистры, первый, второй , третий, четвертый и пятый коммутаторы, первый, второй третий четвертый, пятый и шестой сумматорывычитатепи, причем разрядные выходы (первого сдвигающего регистра соедине вы с соответствующию входами первого KOMNjyTaTopa, выход которого соединен с первым информационным входом первого сумматора-вычитателя разрядные выходам второго сдвигающего регистра соединены с соответствующими входами второго и третьего коммут аторов, выход второго KOMNVXaтора соединен с первым информационным входом второго сумматора-вычитателя, разрядные выходы третьего сдвигающего регистра соединены с соответствующими входами четвертого коммутатора, выход которого соединен с первым информацисжным входом треть его сумма тора-вычитателя, второй информационньШ вход которого соедине С выходом младшего разряда третьего сдвигающего регистра, выход младшего разряда четвёртого сдвигающего регистра соединен с пераим ннформационным входом четвертого сумматоравычитателя, выход которого соединен со входом четвертого сдвигающего регистра и первым выходом устройства, вход которого соединен со вторым информационным входом четвертого сум матора- вычитателя, о тли чающееся тем, что, с целью расшире ;ния функциональных возможностей за |счет выполнения операций вращения вектора вокруг дополнительных осей. устройство дополнительно содержит шестой и седьмой ксммутато1хл, седьмой, сумматор-вычитатель, причем выход младшего разряда-первого сдвигающего регистра соединен со вторым информационным входом первого сумматора-вычитателя, выход которого соединен с первым информационным входом седьмого сумматора-вычитателя, выход которого соединен со входом первого сдвигающего регистра и со вторым выходом устройства, третий выход которого соединен с выходом шестого сумматора-вычитат1еля и со входом второго сдвигающего регистра, выход младшего рёзряда которого соединён со вторым информационным входом второго сумматора-вычитателя, выход которого соединен с первым информадионным входом шестого сумматора-вычитателя, второй информационный вход которого соединен с первым выходом седьмого коммутатора, второй выход которого соединен со вторым информационным входом седьмого сумматоравычитателя, второй выход восьмого сумматора-вычитателя соединен с первым информационным входом пятого сумг матора-вычитателя, второй информационный вход которого соединен с выходом третьего сумматора-вычитателя, вход третьего сдвигающего регистра соединен с выходом пятого сумматоравычитателя и с четвертым выходом устройства, разрядные выхода: первого сдвигающего регистра соединен с соответствующими входами шестого коммутатора, выход которого соединен с первым информационным входом седьмого коммутатора, второй вход которого соединен с выходом третьего коммутатора, третий вход седьмого коммутатора соединен с выходом пятого коммутатора, входы которого соединены с соответствукицими разрядными выходами третьего сщвйгаюцего регистра. . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 504197, кл. G 06 F 7/38, 1974. 2.Авторское свидетельство СССР 445042, кл. G 06 F 7/38, 1973 (прототип).

Ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1981 |

|

SU1136147A1 |

| Вычислительное устройство | 1983 |

|

SU1164696A1 |

| Устройство для вычисления тригонометрических функций | 1981 |

|

SU1003079A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU991419A2 |

| Устройство для определения модуля трехмерного вектора | 1983 |

|

SU1142830A1 |

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Устройство для вычисления корня к-ой степени | 1976 |

|

SU736096A1 |

| Устройство для вычисления модуля трехмерного вектора | 1989 |

|

SU1672442A1 |

| Устройство для преобразования сферическихКООРдиНАТ B пРяМОугОльНыЕ | 1978 |

|

SU805308A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1105888A1 |

Авторы

Даты

1982-09-15—Публикация

1981-01-14—Подача