I

Изобретение относится к цифровой вычислительной технике, может найти применение для аппаратной реализации вьршслений функций.

По основному авт. ев, № 744590 известен цифровой функциональный преобразователь, . содержащий четыре сумматора-вьгштателя, два регистра, блок анализа и блок управления. Выход блока анализа соединен с первыми управляющими входами сумматоров-вычитателей и входом блока управления, первый выход блока управления соединен с управляющими входами первого и второго регистров, второй выход - с вторыми управляющими входами сумматоров-вьгштателей, выход первого регистра соединен с первыми входами первого и второго сумматоров-вычитателей, выход второго регистра соединен с первыми входами третьего и четвертого сумматоров-вычитателей,, выходы первого и третьего сумматороввычитателей соединены с первым и вторым входами блока анализа, первый вход преобразователя соединен с входом первого регистра и вторыми входами первого и второго

сумматоров-вычитателей, второй вход преобразователя соединен с входом второго регистра и вторыми входами третьего и четвертого сумматоров-вычятателей, выхсщы сумматороввычитателей являются выходами преобразователя 1.

Этот преобразователь предназначен для вычисления ф)тасщ{й 2ху )

Недостатком устройства является ограниченный класс вычисляемых функций.

Цель изобретения - расширение класса решаемых задач за счет дополнительного вычисления функций вида

(x y lCx-y), ()(уф)а (:у2-ха)Дх4,).

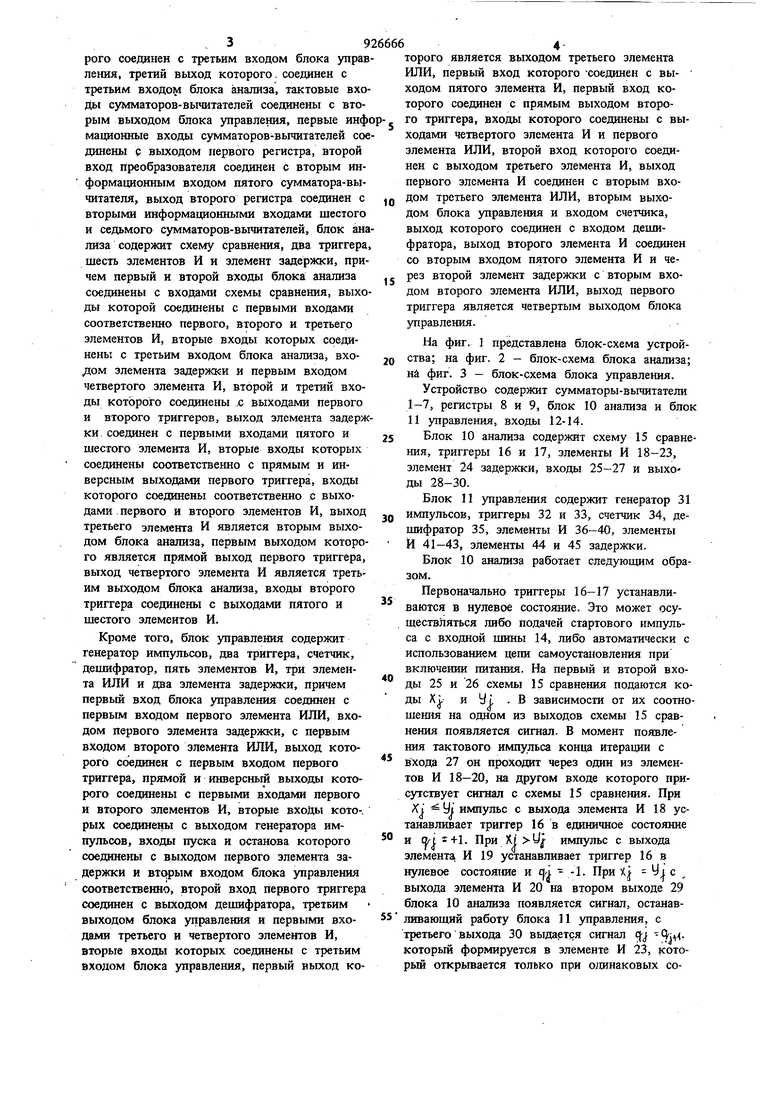

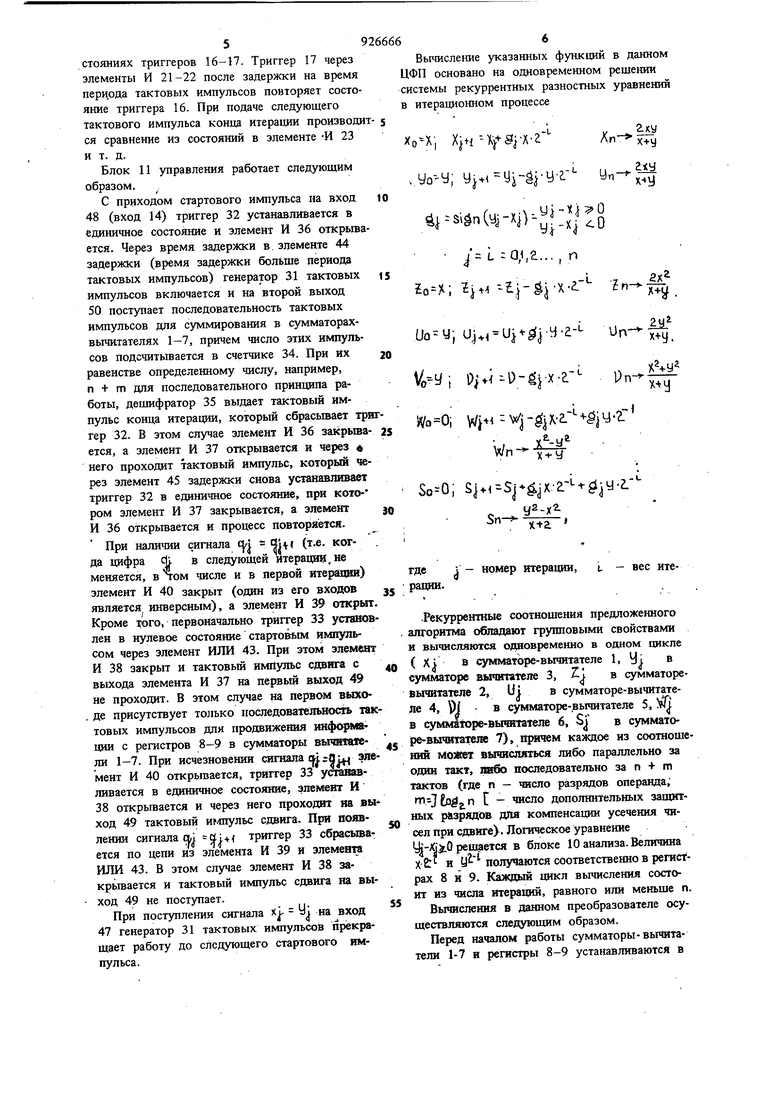

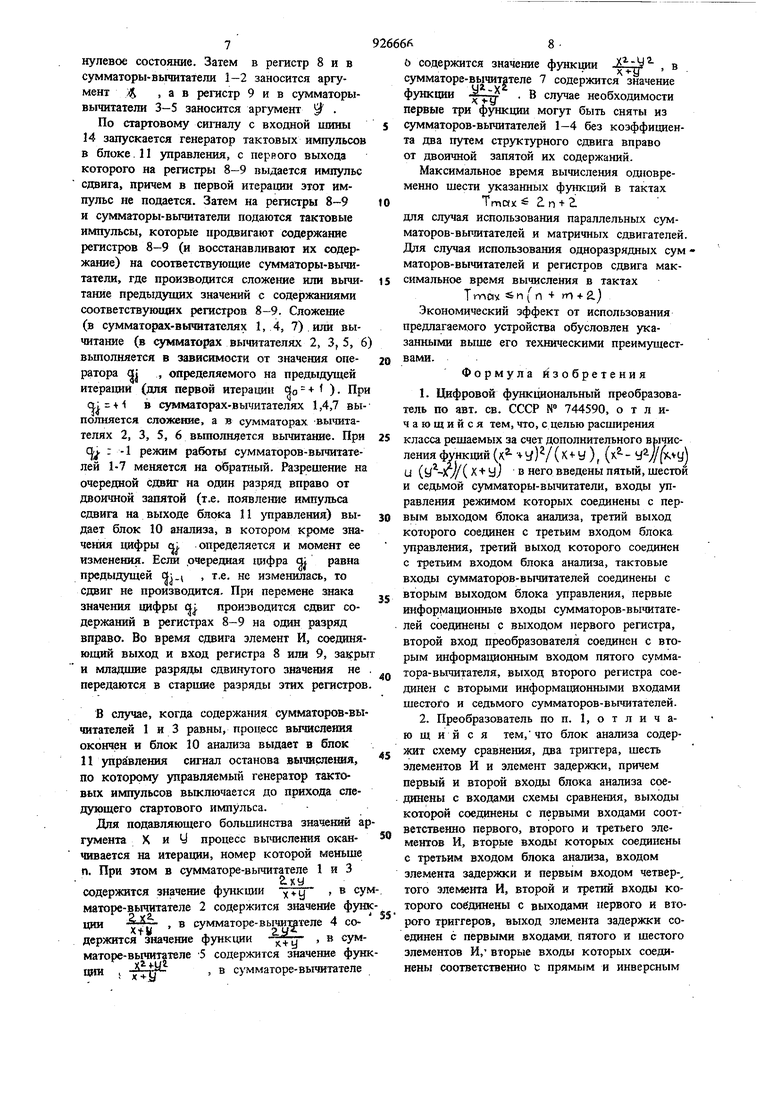

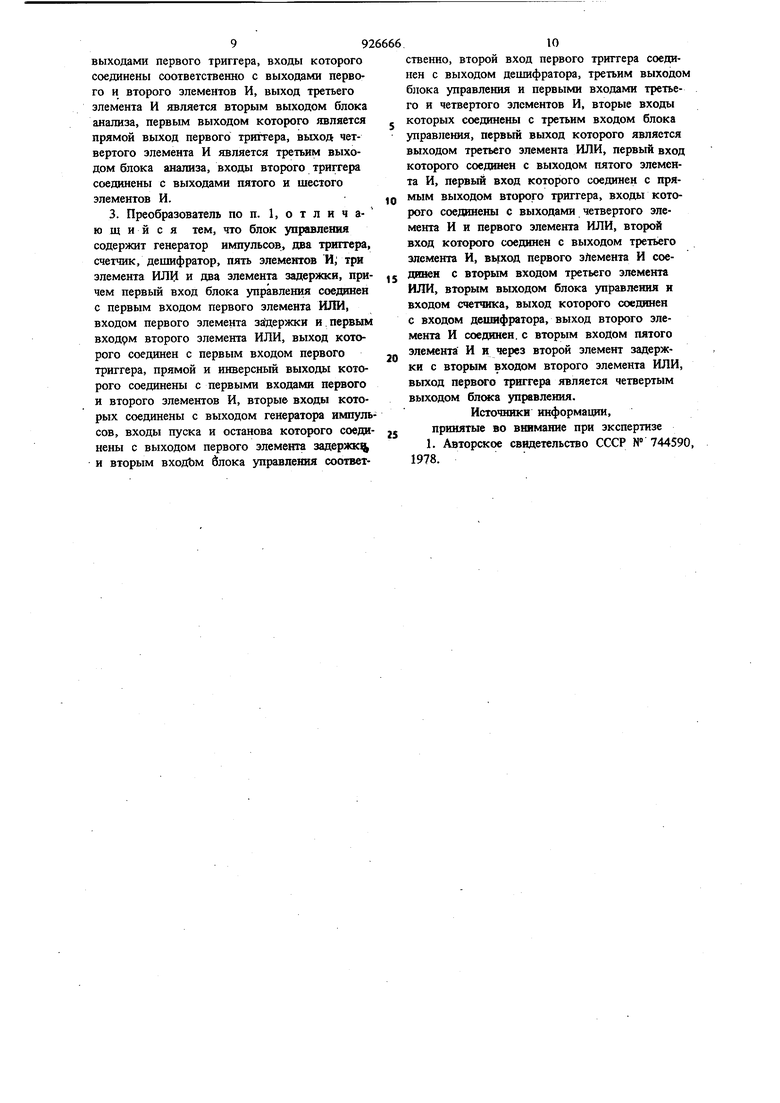

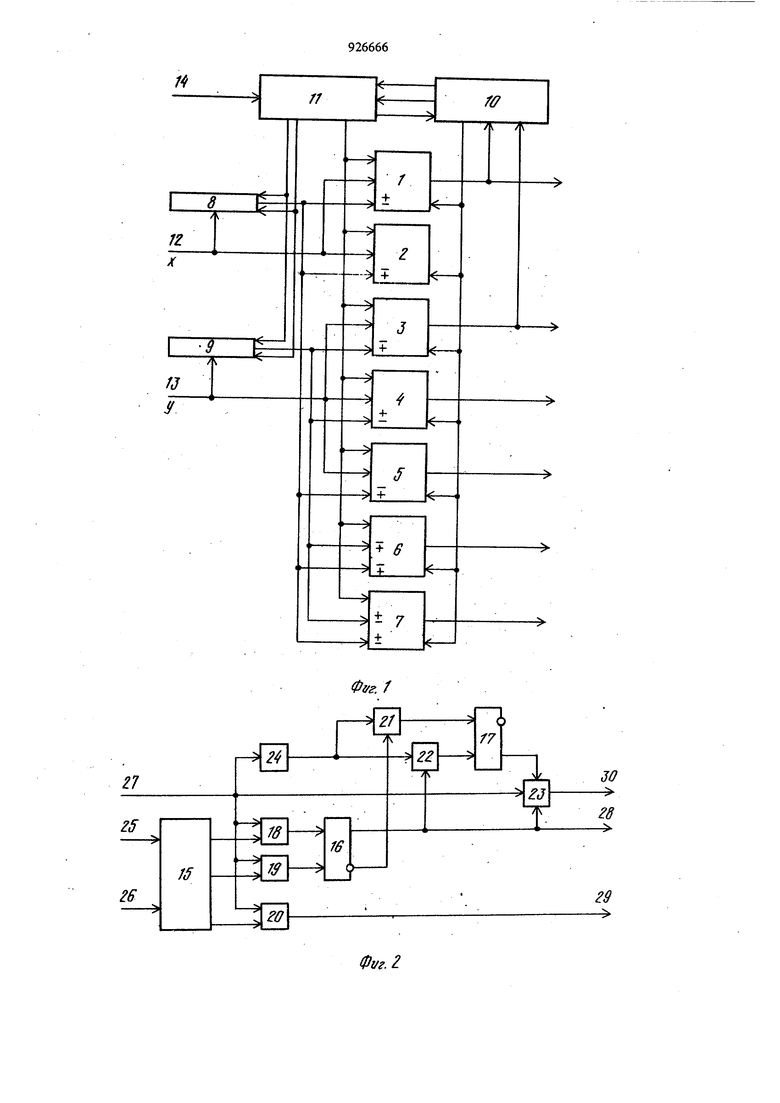

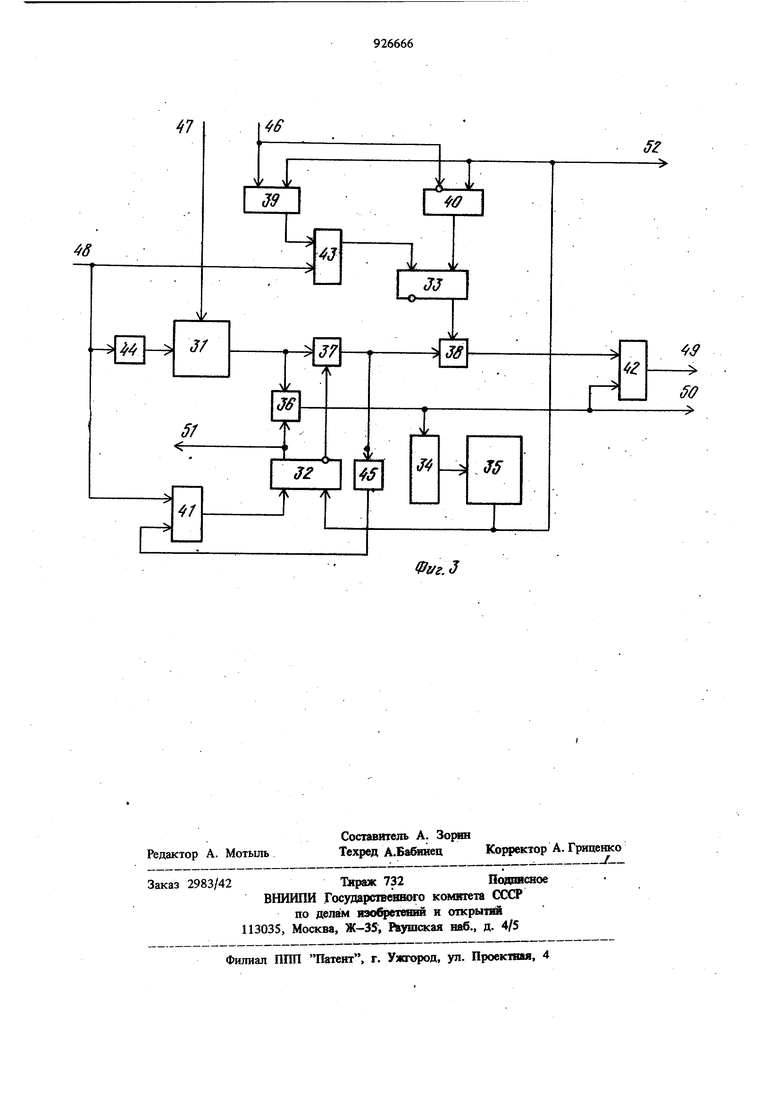

Поставленная цель достигается тем, что в преобразователь введены пятый, шестой и седьмой сумматоры-вычитатели, входы управления режимом которых соединены с первым выходом блока анализа, третий выход котоporo соединен с третьим входом блока управ ления, третий выход которого. соединен с третьим входом блока анализа, тактовые входы сумматоров-вычитателей соединены с вторым выходом блока управления, первые инф мационные входы сумматоров-вычитателей сое динены е выходом первого регистра, второй вход преобразователя соединен с вторым информационным входом пятого сумматора-вычитателя, выход второго регистра соединен с вторыми информационными входами шестого и седьмого сумматоров-вычитателей, блок ана лиза содержит схему сравнения, два триггера шесть элементов И и элемент задержки, причем первый и второй входы блока анализа соединены с входами схемы сравнения, выхо ды которой соединены с первыми входами соответстве шо первого, второго и третьего элементов И, вторые входы которых соединены с третьим входом блока анализа, входом элемента задержки и первым входом четвертого элемента И, второй и третий входы которого соединены .с выходами первого и второго триггеров, выход элемента задерж ки, соединен с первымц входами пятого и шестого элемента И, вторые входы которых соединены соответственно с прямым и инверсным выходами первого триггера, входы которого соединены соответственно с выходами первого и второго элементов И, выход третьего элемента И является вторым выходом блока анализа, первым выходом которого является прямой выход первого триггера, выход четвертого элемента И является третьим выходом блока анализа, входы второго триггера соединены с выходами пятого и шестого элементов И. Кроме того, блок управления содержит генератор импульсов, два триггера, счетчик, дешифратор, пять элементов И, три элемента ИЛИ и два элемента задержки, причем первый вход блока управления соединен с первым входом первого элемента ИЛИ, входом первого элемента задержки, с первым входом второго элемента ИЛИ, выход которого соединен с первым входом первого триггера, прямой и инверсный выходы которого соединены с первыми входами первого и второго элементов И, вторые вхоДы кото-, рых соединены с выходом генератора импульсов, входы пуска и останова которого соединены с выходом первого элемента задержки и вторым входом блока управления соответственно, второй вход первого триггера соединен с выходом дешифратора, третьим выходом блока управления и первыми входа.мн третьего и четвертого элементов И, вторые ВХОХ1Ы которых соединены с третьим входом блока управления, первый выход которого является выходом третьего элемента ИЛИ, первый вход которого соединен с выходом пятого элемента И, первый вход которого соединен с прямым выходом второго триггера, входы которого соединены с выходами четвертого элемента И и первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, выход первого элемента И соединен с вторым входом третьего элемента ИЛИ, вторым выходом блока управления и входом счетчика, выход которого соеданен с входом дешифратора, выход второго элемента И соединен со вторым входом пятого элемента И и через второй элемент задержки с вторым входом второго элемента ИЛИ, выход первого триггера является четвертым выходом блока управления. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок-схема блока анализа; на фиг. 3 - блок-схема блока управления. Устройство содержит сумматоры-вычитатели 1-7, регистры 8 и 9, блок 10 анализа и блок 11 управления, входы 12-14. Блок 10 анализа содержит схему 15 сравнения, триггеры 16 и 17, элементы И 18-23, элемент 24 задержки, входы 25-27 и выходы 28-30. Блок 11 управления содержит генератор 31 импульсов, триггеры 32 и 33, счетчик 34, дешифратор 35, элементы И 36-40, элементы И 41-43, элементы 44 и 45 задержки. Блок 10 анализа работает следующим образом. Первоначально триггеры 16-17 устанавливаются в нулевое состояние. Это может осуществляться либо подачей стартового импульса с входной шины 14, либо автоматически с использованием цепи самоустановления при включении питания. На первый и второй входы 25 и 26 схемы 15 сравнения подаются коды Х| зависимости от их соотнощешш на одном из выходов схемы 15 сравнения появ.пяется сигнал. В момент появления тактового импульса конца итерации с входа 27 он проходит через один из элементов И 18-20, на другом входе которого присутствует сигнал с схемы 15 сравнения. При XJ yi импульс с выхода элемента И 18 устанавливает триггер 16 в единичное состояние и +1. При К| и импульс с выхода элемента И 19 устанавливает триггер 16 в нулевое состоятше и U - -1. При Ч - У t с выхода элемента И 20 на втором выходе 29 блока 10 анализа появляется сигнал, останавливающий работу блока 11 управления, с третьего выхода 30 выдает(;я сигнал cif Jji который формируется в элементе И 23, который открьгоается толвко при одинаковых состояниях триггеров 16-17. Триггер 17 через элементы И 21-22 после задержки на время периода тактовых импульсов повторяет состояние триггера 16. При подаче следующего тактового импульса конца итерации производи ся сравнение из состояний в элементе -И 23 и т. д. Блок 11 управления работает следующим образом. С приходом стартового импульса на вход 48 (вход 14) триггер 32 устанавливается в единичное состояние и элемент И 36 открьша ется. Через время задержки в. элементе 44 задержки (время задержки больше периода тактовых импульсов) генератор 31 тактовых импульсов включается и на второй выход 50 поступает последовательность тактовых импульсов для суммирования в сумматорахвычитателях 1-7, причем число этих импульсов подсчитывается в счетчике 34. При их равенстве определенному числу, например, п + m для последовательного принципа работы, депшфратор 35 выдает тактовый импульс конца итерации, который сбрасьтает три гер 32. В этом случае элемент И 36 закрьтаа ется, а элемент И 37 открывается и через « него проходит тактовый импульс, который через элемент 45 задержки снова устанавливает триггер 32 в единичное состояние, при кото- ром элемент И 37 закрьгоается, а элемент И 36 открьгеается и процесс повторя(ется. При наличии сигнала ty - Jivi (т.е. когда цифра cji. в следующей итерации, не меняется, в том числе и в первой итерации) элемент И 40 закрыт (один из его входов является инверсным), а элемент И 39 открыт Кроме того, первоначально триггер 33 устшов лен в нулевое состояние стартовым импульсом через элемент ИЛИ 43. При этом элемент И 38 закрыт и тактовый имйульс сдвига с выхода элемента И 37 на первый выход 49 не проходит. В этом случае на первом выходе присутствует только последователыккяь так товых импульсов для продвижения инф м&ции с регистров 8-9 в сумматоры Bbnetaieли 1-7. При исчезновении сигнала oj гОи эле мент И 40 открывается, триггер 33 устанавливается в единичное состояние, элемент И 38 открывается и через него проходит на вы ход 49 тактовый импульс сдвига. При появлении сигнала сь1 91+ триггер 33 сбрасывается по цепи из элемента И 39 и элемента ИЛИ 43. В этом случае элемент И 38 закрьгеается и тактовый импульс сдвига иа выход 49 не поступает. При поступлении сигнала xj. У| на вход 47 генератор 31 тактовых, импульсов прекращает работу до следующего стартового импульса. Вычисление указанных функций в данном ЦФП основано на одновременном рещении системы рекуррентных разностных уравнений в итерационном процессе Х nj -Sj-Лг х+у ...Уо--У; y.-yrgj-y-i- ( .0 ,г..., п 2Q)t; --t -gj-x-r - -Zn-lf , uj Uj i-Уг Vo-y; p i D-gj-х.г-- «е.уг Wn- - TySo 0i .. где i - иомер итерации, i, - вес итерадии. .Рекуррентные соотношения предложенного алгоритма обладают групповыми свойствами и вычисляются одвовременно в одном цикле ( Xv в сумматоре-вычитателе 1, У1 в сумматоре лчнтателе 3, 211 в сумматоревычитателе 2, Uj в сумматоре-вычитатеяе 4, Ш в сумматоре-.вычитателе 5, в сумматоре-вь ктателе б, SV в сумматоре-вычитателе 7), причем каждое из соотношений vtOSKet вычисляться либо параллельно за один такт, Ш1&1 последовательно за п + m тактов (где п - число разрядов операнда, TizJEflgj.n Г - число дополнительных защитных р&зрядОв для компенсации усечения чисел при сдвиге). Логическое уравнение решается в блоке 10 анализа. Величина ХСГ и У получаются соответственно в регистрах 8 и 9. Каждый цикл вычисления состоит из числа итераций, равного или меньше п. Вычисления в данном преобразователе осуществляются следующим образом. Перед началом работы сумматоры-вьгчитатели 1-7 и регистры 8-9 устанавливаются в нулевое состояние. Затем в регистр 8 и в сумматоры-вычитатели 1-2 заносится аргумент Д , а в регистр 9 и в сумматорывычитатели 3-5 заносится аргумент . По стартовому сигналу с входной шины 14 запускается генератор тактовых импульсов в блоке. 11 управления, с первого выхода которого на регистры 8-9 выдается импульс сдвига, причем в первой итерации этот импульс не подается. Затем на регистры 8-9 и сумматоры-вычитатели подаются тактовые импульсы, которые продвигают содержание регистров 8-9 (и восстанавливают их содержание) на соответствующие сумматоры-вычитатели, где производится сложение или вычитание предыдущих значений с содержаниями соответствуннцих регистров 8-9. Сложение (в сумматорах-вычитателях 1, 4, 7) или вычитание (в сумматорах вычитателях 2, 3, 5, 6 вьшолняется в зависимости от значения оператора Ш , определяемого на предыдущей итерации (для первой итерации Чо + ) При Q.J г + в сумматорах-вычитателях 1,4,7 выполняется сложение, а в сумматорах вычитателях 2, 3, 5, 6 вьшолняется вычитание. При с : -1 режим работы сумматоров-вычитателей 1-7 меняется на обратный. Разрешение на очередной сдвиг на один разряд вправо от двоичной запятой (т.е. появление импульса сдвига на выходе блока 11 правления) выдает блок 10 анализа, в которого кроме значения дафры aj, определяется и момент ее изменения. Если очередная хшфра gi равна предыдущей 0;..( , т.е. не изменилась, то сдвиг не производится. При перемене знака значения цифры с производится сдвиг содержаний в регистрах 8-9 на один разряд вправо. Во время сдвига элемент И, соединяющий выход и вход регистра 8 или 9, закры и младшие разряды сдвинутого значения не передаются в старшие разряды этих регистров В случае, когда содержания сумматоров-вы читателей 1 и 3 равны, процесс вычисления окончен и блок 10 анализа выдает в блок 11 управления сигнал останова вычисления, по которому управляемый генератор тактовых импульсов вьпслючается до прихода следующего стартового импульса. Для подавляющего большинства значе югй а гумента X и У процесс вычисления оканчивается на итерации, номер которой меньше п. При этом в сумматоре-вычитателе 1 и 3 :,. содержится значение функции хТу в су маторе-вычитателе 2 содержится значение фун ции ц , в сумматоре-вычи теле 4 содержится значение функции . сумматоре-вычитателе 5 содержится значение фун qjjjj в сумматоре-вычитателе Л8 u содержится значение функцни в с}гмматоре-вь1чит§теле 7 содержится значение функции . в случае необходимости первые три функции могут быть сняты из cjnviMaTopoB-вычитателей 1-4 без коэффициента два путем структурного сдвига вправо от двоичной занятой их содержаний. Максимальное время вычисления одновременно шести указанных функций в тактах Ттикё ап + г для случая использования параллельных сумматоров-вычитателей и матричных сдвигателей. Для случая использования одноразрядных сум маторов-вычитателей и регистров сдвига максимальное время вычисления в тактах Т max sn f п m ) Экономический эффект от использования предлагаемого устройства обусловлен указанными выше его техническими преимуществами. Формула изобретения 1.Цифровой функциональный преобразователь по авт. св. СССР № 744590, отличающийся тем, что, с целью расширения класса решаемых за счет дополнительного вь1числения функций (х 4-y)V( ), (- ) U ()0/( X « yj в него введены пятый, шестой и седьмой сумматоры-вычитатели, входы управления режимом которых соединены с первым выходом блока анализа, третий выход которого соединен с третьим входом блока управления, третий выход которого соединен с третьим входом блока анализа, тактовые входы сумматоров-вычитателей соединены с вторым выходом блока )шравления, первые информационные входы сумматоров-вычитателей соединены с выходом первого регистра, второй вход преобразователя соединен с вторым информационным входом пятого сумматора-вьиитателя, выход второго регистра соединен с вторыми информационными входами шестого и седьмого сумматоров-вычитателей. 2.Преобразователь по п. 1, о т л и ч аю щ и и с я тем,что блок анализа содержит схему сравнения, два триггера, шесть элементов И и элемент задержки, причем первый и второй входы блока анализа соединены с входами схемы сравнения, выходы которой соединены с первыми входами соответственно первого, второго и третьего элементов И, вторые входы которых соединены с третьим входом блока анализа, входом элемента задержки и первым входом четвер-, того элел«еита И, второй и третий входы которого соединены с выходами первого и второго триггеров, выход элемента задержки соеданен с первыми входами, пятого и шестого элементов И, вторые входы которых соеданены соответственно с прямым и инверсным

992

выходами первого триггера, входы которого соединены соответственно с выходалш первого и второго элементов И, выход третьего элемента И является вторым выходом блока анализа, первым выходом которого является прямой выход первого триггера, выход четвертого элемента И является третьим выходом блока анализа, входы второго триггера соединены с выходами пятого к шестого элементов И.

3. Преобразователь по п. 1, о т л и ч аю щ и и с я тем, что блок управления содержит генератор импульсов, два триггера, счетчик, дешифратор, пять элементов И; три элемента ИЛИ и два элемента задержки, причем первый вход блока управления соединен с первым входом первого элемента ИЛИ, входом первого элемента задержки и. первым ВХОД9М второго элемента ИЛИ, выход которого соединен с первым входом первоготриггера, прямой и инверсный выходы которого соединены с первыми входами первого и второго элементов И, вторые входы которых соединены с выходом генератора импульсов, входы пуска и останова которого соединены с выходом первого элемента задержку и вторым входЬм блока управления соответVO

ственно, второй вход первого триггера соединен с выходом деишфратора, третьим выходом блока управления и первыми входами третьего я четвертого элементов И, вторые входы которых соединены с третьим входом блока управления, первый выход которого является выходом третьего элемента ИЛИ, первый вход которого соединен с выходом пятого элемента И, первый вход которого соединен с прямым выходом второго триггера, входы которого соединены с выходами четвертого элемента И и первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первого э/1емента И соединен с вторым входом третьего элемента ИЛИ, вторым выходом блока управления и входом счетчика, выход которого соединен с входом дешифратора, выход второго элемента И соединен, с вторым входом пятого элемента И и через второй элемент задержки с вторым входом второго элемента ИЛИ, выход первсмо триггера является четвертым выходом блетса управления.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 744590 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Арифметическое устройство | 1980 |

|

SU903868A2 |

| Цифровой функциональный преобразователь | 1980 |

|

SU991419A2 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU911522A1 |

| Арифметическое устройство | 1980 |

|

SU960802A2 |

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

| Арифметическое устройство | 1977 |

|

SU728127A2 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU920716A2 |

Авторы

Даты

1982-05-07—Публикация

1980-03-14—Подача