I1095169

Изобретение относится к цифровой технике и автоматике и может быть I использовано при построении преобра1зователей в вычислительных устройствах обработки данных. Известен преобразователь двоичнодесятичного кода в двоичный, содержащий группу сумматоров и цепи задания двоичных эквивалентов разрядов десятичного кода. Умножение каждого двоично-десятичного кода цифр на множитель 10 осуществляется разложением множителя 10 на числа, кратные степени числа два, сдвига кода цифр на определенное колигзество разрядов влево и последукяцих суммированием сдвину тых чисел Т 3. Недостаток этого преобразователя состоит в низком быстродействии, что связано с зависимостью времени преобразования от количества цифр в десятичном числе. Наиболее близким по технической сущности к изобретению является преобразователь двоично-десятичного кода в двоичный, содержащий группу разрядных преобразователей десятичных цифр в двоичные-и сумматор, выходь которо го являются выходами преобразователя вхо;9 : которого соединены с входами разрядных преобразователей, выходы которых соединены t входами сумматора С23. Недостаток данного преобразователя состоит в относительно низком быстродействии, что связано с увеличением числа одноименных входов сумкатора при увеличении разрядности преобразователя и, как следствие, увеличением числа ярусов сумматора. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в преобразователь двоичнодесятичного кода в двоичный, содержащий группу разрядных преобразователей десятичных цифр в двоичные и сумматор, выходы которого являются выходами преобразователя, входы которого соединены с входами разрядных преобразователей, выходы первого раз рядного преобразователя группы соеди нены с первыми входами сумматора, вход первого разряда преобразователя является выходом первого разряда пре образователя, дополнительно введены группа умножителей и группа элементов НЕ, а разрядные преобразователи десятичных цифр в двоичные выполнены

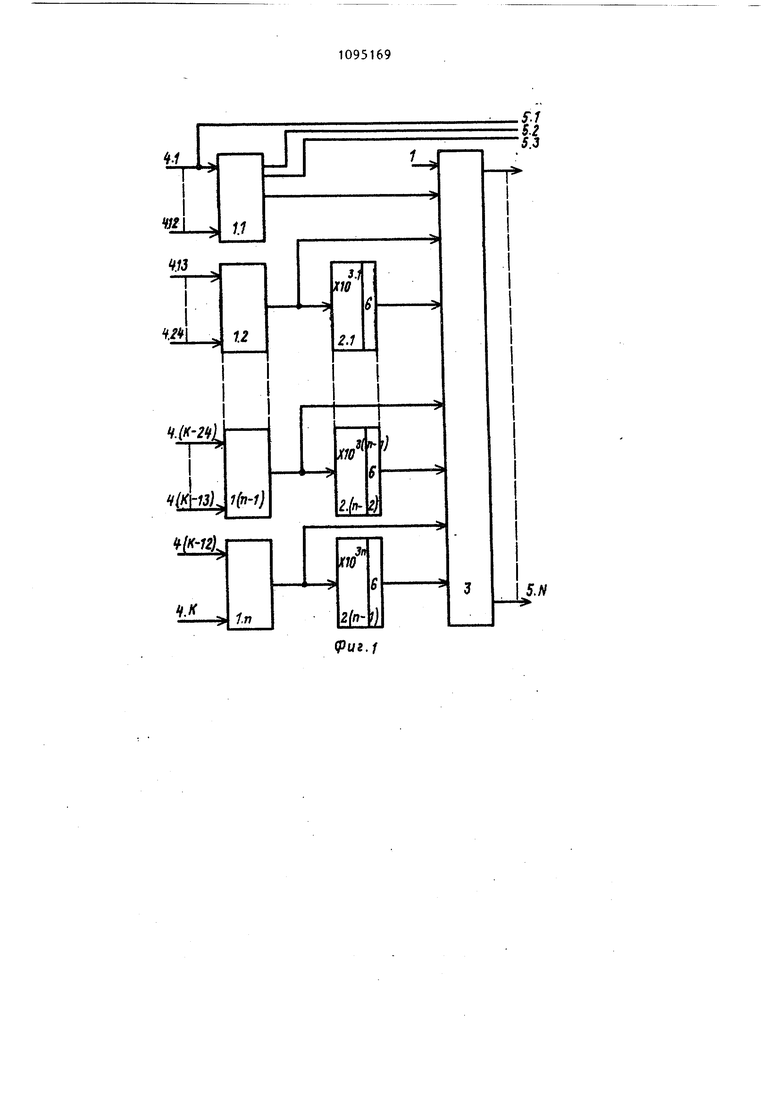

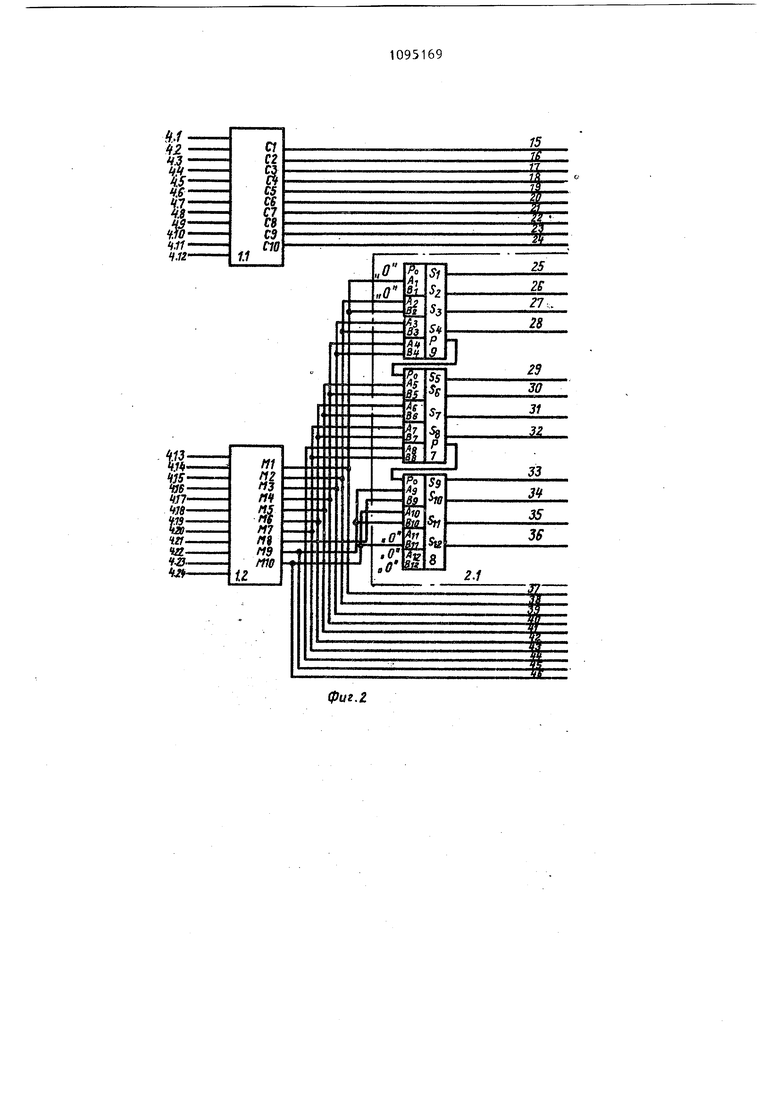

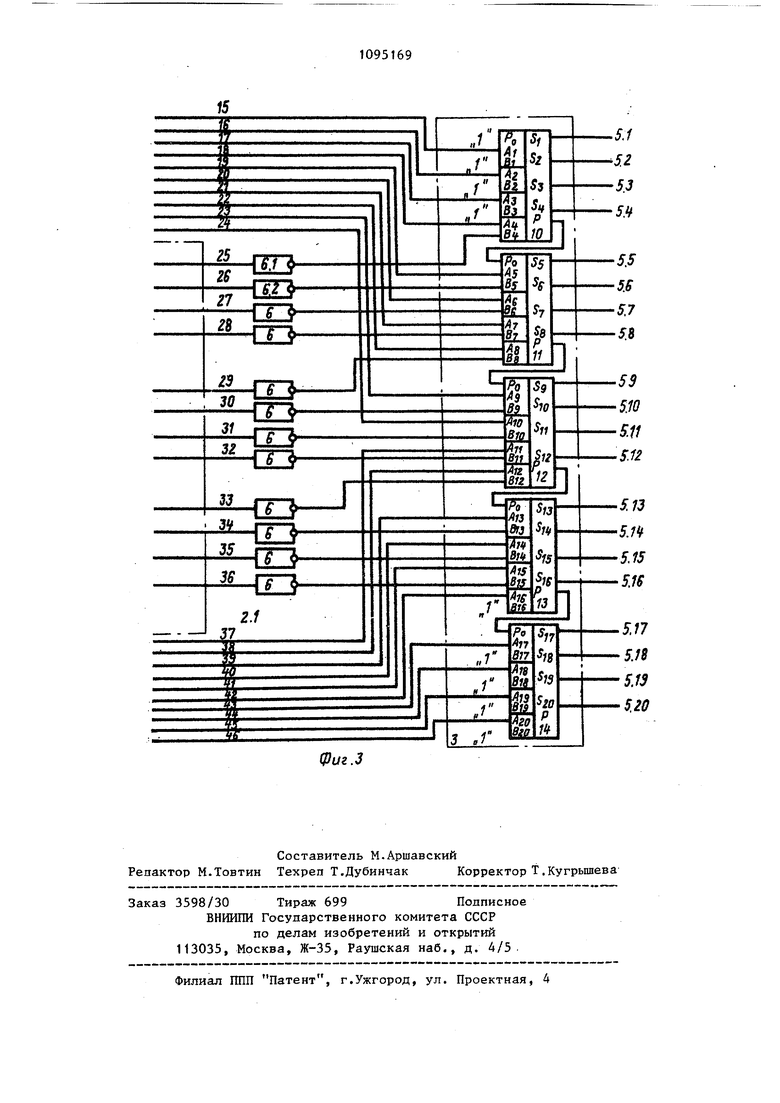

трехразрядными, причем выходы всех трехразрядных преобразователей- группы, кроме первого, соединены соответственно с входами умножителей, выходы которых.соединены с входами элементов НЕ группы, выходы которых соединены с вторыми входами сумматора, выходы i-го трехразрядного преобразователя группы (), где m- число десятичных разрядов преобразователя, соединены с первыми входами сумматора ей сдвигом на 10 (i-1) разрядов в сторону старших разряков, первый и второй выходы первого трехразрядного преобразователя группы являются соответственно выходами второго и третьего разрядов преобразователя, вход логической единицы которого соединен с входом переноса сумматора. На г. 1 приведена структурная схема предлагаемого преобразователя; на фиг. 2 и 3 - пример реализации шестиразрядного двоично-десятичного преобразователя в двоичный код. Предлагаемый преобразователь содержит группу трехразрядных преобразователей 1.1-1.П, каждый из которых осуществляет преобразование трех десятичных цифр в двоичные, группу умножителей 2.1-2 (п-1), сумматор 3, входы 4.1-4 К преобразователя, выходы 5.1-5N преобразователя и группу 6 элементов НЕ. В качестве трехразрядных преобразователей 1.1-1h может быть использован преобразователь, описанный в 3. Количество трехразрядных преобразователей 1 определяется как большее целое число от деления количества входов 4 на число двенадцать. Колич ство умножителей 2 на один меньше, чем количество трехразрядных преобразователей 1. Преобразователь шести десятичных цифр содержит первый 1.1 и второй 1.2 трехразрядные преобразователи, умножитель 2.1, состоящий из четырехразрядных сумматоров 7-9, группу элементов НЕ 6, сумматор 3, состоящий . из четырехразрядных сумматоров 10-14. Входы первого Т.1 трехразрядного преобразователя соединены с входами 4.1... 4.12. Входы второго 1.2 трехразрядного преобразователя соединены с входами 4.13... 4.24, а выходы М1... А/М О соединены с входами Л 1.. .А 10 и входами Б 2...611 четырехразрядньгх сумматоров 7 - 9. На входы Рд, в четырехразрядного сумна входы Л 11, А 12,В 12 матора 9 и четырехразрядного сумматора 8 подан 8 (Сигнал логического нуля. Выход переноса четырехразрядного сумматора соединен с входом переноса Р,, четырехразрядного сумматора 7, выход пе реноса четырехразрядного сумматора 7 соединен с входом переноса Рр четырехразрядного сумматора 8. Выходы сумм S1...S12 четырехразрядных сумматоров 7-9 соединены с входами элементов НЕ группы 6. Выходы первого 1.1 трехразрядного преобразователя соединены с входами А1...А10 четырехразрядных сумматоров 10 - 12.. Выходы второго 1.2 тре разрядного преобразователя соединены с входами All...А20 четырехразряд ных сумматоров 12 - 14. Выходы элементов НЕ группы 6 соединены с входами В4...615 четырехразрядных сумматоров 10 - 13. На входы Рд, В , В Ва четырехразрядного сумматора 10 и на входы В 16.. .в 20 четырехразрядных сумматоров 13 и 14 подан сигнал логической единицы. Выход переноса каждого из четырехразрядных суммато ров 10 - 13 соединен с входом переноса Р последующего четырехразрядного сумматора 11-14. Выходы сумм S1 . . . S20 четырехразрядных сумматоров 10 - 14 соединеньг с выходами 5.1 ... 5.20 преобразователя. Предлагаемый преобразователь рабо тает следующим образом. Исходное число разбито на группы по три цифры в каждой, трехразрядные преобразователи 1.1 - 1п осуществляю преобразование каждой группы цифр в двоичные эквиваленты, затем производится умножение полученных двоичны эквивалентов групп на множитель крат ный 10 и суммирование полученных произведений, где га принимает значе ние натурального ряда чисел от О до числа, значение которого на единицу меньше числа групп по три цифры. После работы преобразователей образуют ся двоичные эквиваленты, которые умножаются на множители 10 , 10, 10 Умножение двоичного эквивалента груп пы на множитель 10°, 10, 10 осуществляется вычитанием из двоичного эквивалента группы, сдвинутого на нуль, десять, двадцать разрядов впра во, результата умножения соответствующего двоичного эквивалента числа, превьшающего множитель 1C , 10 , 10. Пусть преобразованию подлежит число 326656763. Запишем его следующим образом: 326656763 326-10 -i- 656-10 + 326 - 11048576- Г32768Н 4- 763-Ю + 656 flQ24+ 64)1 + 16384-(512 326- -,(16 + 8) + f2 + 2- (2 + 2)Ji +656; . )(2 + 23) + 763-2. Умножители 2.1-2 (h-1) осуществляют сдвиг и суммирование тех частей приведенных чисел, которые входят в вычитаемое соответствующих членов. Операция вычитания осуществляется сумматором 3, для чего результат работы первого трехразрядного преобразователя передается на его входы без сдвига, результат работы второго трехразрядного преобразователя передается на входы сумматора со сдвигом на десять разрядов, результат работы третьего трехразрядного преобразователя передается на входы сумматора со сдвигом на двадцать разрядов и т.д., результат работы первого умножителя, относящийся к второму трехразрядному преобразователю, инвертируется группой элементов НЕ 6 и передается на входы сумматора 3 со сдвигом на три разряда, результат работы второго умножителя, относящийся к третьему трехразрядному преобразователю, инвертируется группой элементов НЕ 6 и передается на входы сумматора со сдвигом на шесть разрядов и т .д. Рассмотрим теперь более подробно работы шестиразрядного преобразователя На выходах С1... СЮ образуется двоичный код числа, эквивалентный поданному по входам 4.1... 4.12. Старшие три цифры подаются по входам 4.13... 4.24. На выходах AM . . .М10 образуется двоичный код числа, эквивалентньй поданному по входам 4.13... 4.24. На выходах 5.1... 5.20 устройства двоичный код числа образуется по формуле 1024+С-М 24-м (М 2 + + М2), где N - двоичный код выходного числа; М - двоично-десятичный код числа, соответствующий старшим трем цифрам; С - двоично-десятичный код числа, соответствующий младшим трем цифрам.

510951696

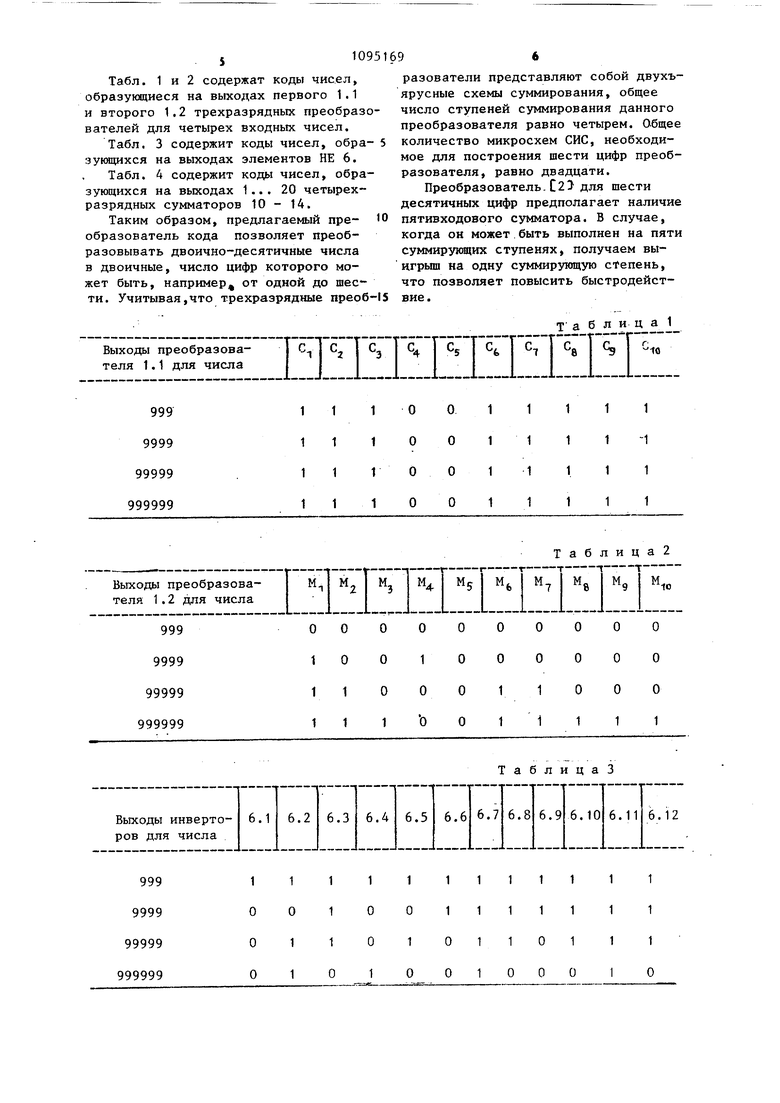

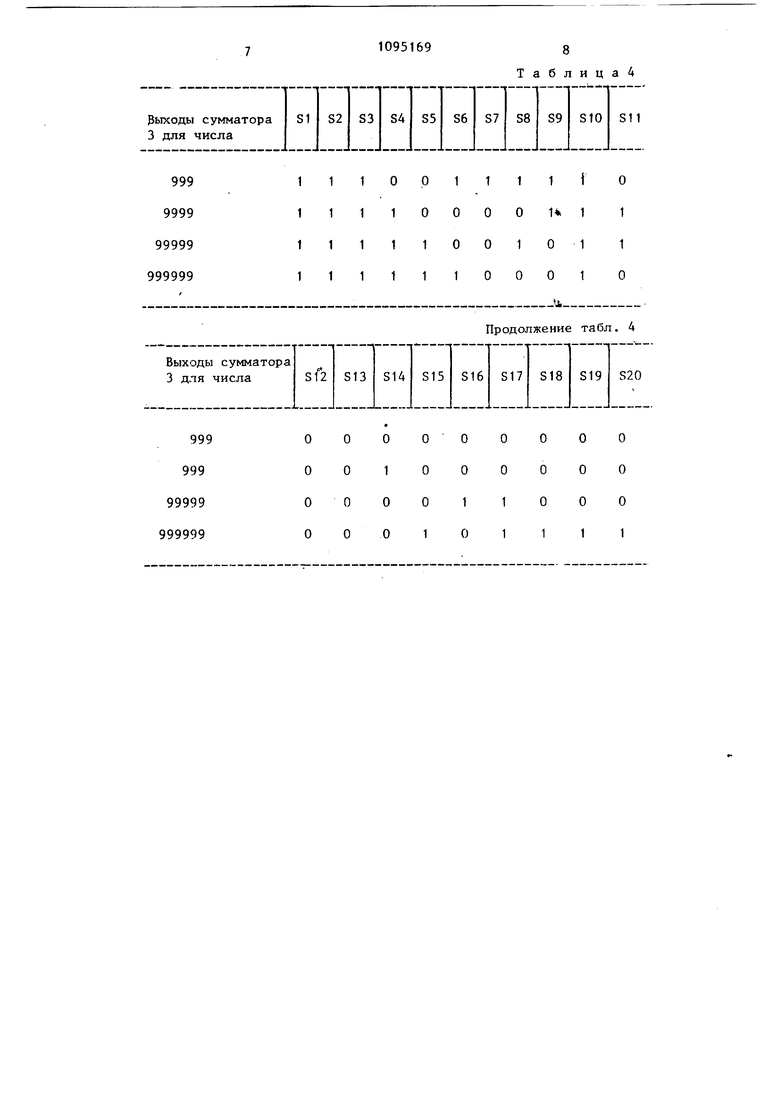

Табл. 1 и 2 содержат коды чисел,раэователи представляют собой двухъобразукяциеся на выходах первого 1.1ярусные схемы суммирования, общее

и второго 1.2 трехразрядных преобразо-число ступеней суммирования данного

вателей для четырех входных чисел.преобразователя равно четырем. Общее

Табл. 3 содержит коды чисел, обра- 5количество микросхем СИС, необходизующихся на выходах элементов НЕ 6.мое для построения шести цифр преобТабл. 4 содержит коды чисел, обра-разователя, равно двадцати, зующихся на выходах 1... 20 четырех- Преобразователь.С2Э для шести

разрядных сумматоров 10 - 14.десятичных цифр предполагает наличие

Таким образом, предлагаемый пре- Юпятивходового сумматора. В случае,

образователь кода позволяет преоб-когда он может быть выполнен на пяти

разовывать двоично-десятичные числасуммирукацих ступенях, получаем выв двоичные, число цифр которого мо-игрыш на одну суммирунлцую степень,

жет быть, например от одной до шее-что позволяет повысить быстродейстти. Учитывая,что трекразрядные преоб-15вне.

Т а б л и ц а 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоично-десятичного кода в последовательный двоичный код | 1975 |

|

SU720424A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU960794A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1292187A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь двоичного кодаВ дЕСяТичНый | 1979 |

|

SU830371A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

| Реверсивный преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1501278A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1624698A1 |

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ, содержащий группу разрядных преобразователей десятичных цифр в двоичные и сумматор, выходы которого являются выходами преобразователя, входы которого соединены с входами разрядных преобразователей, выходы первого разрядного преобразователя группы соединены с первыми входами сумматора, вход первого разряда преобразователя является выходом первого разряда преобразователя, отличающийся тем, что, с целью повышения быстродействия, в него введены группа умножителей игруппа элементов НЕ, а разрядные преобразователи десятичных цифр в двоичные выполнены трехразрядными, причем выходы всех трехразрядных преобразователей группы, кроме первого, соединены соответственно с входами умножителей, выходы которых соединены с входами элементов НЕ группы, выходы которых соединены с вторыми входами сумматора, выходы -го трехразрядного преобразователя группы § (1 2-т j-yj) , где т- число десятичных разрядов преобразователя, соединены (Л с первыми входами сумматора со сдвигом на 10 (-1) разрядов в сторону старших разрядов, первый и второй выходы первого трехразрядного преобразователя группы являются соответственно выходами второго и третьего разрядов преобразователя, вход логической единицы которого соединен с со ел входом переноса сумматора. Oi ф

Таблица2

ТаблицаЗ

ТаблицаД

Риг,

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Будинский Я | |||

| Логические цепи в цифровой технике | |||

| М., Связь, 1977, с | |||

| Рогульчатое веретено | 1922 |

|

SU142A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| G, 06 F 5/02, 1982 | |||

Авторы

Даты

1984-05-30—Публикация

1983-02-10—Подача