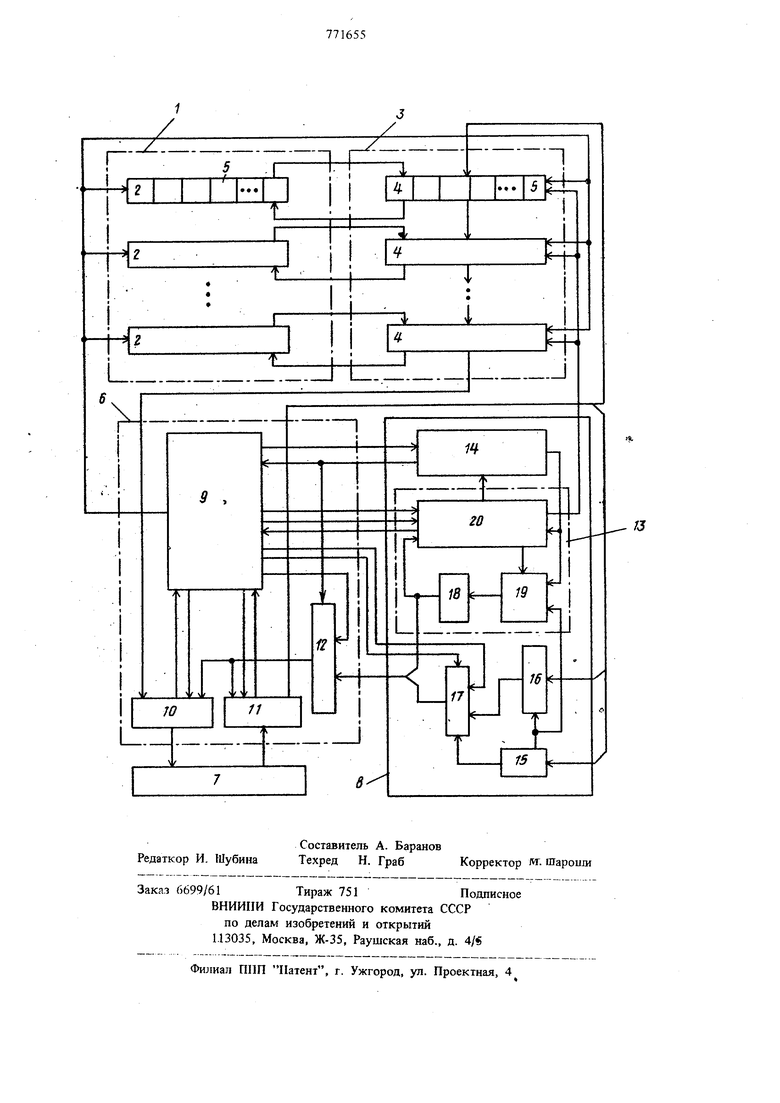

Изобретение относится к области вычислитель ной техники, в частиости к устройствам управления обменом между регистровой и оперативной памятью процессоров, работающих в мультипрограммном режиме и режиме разделения времени. Известны устройства управления обменами, в которых требуется сохранение в оперативной памяти и восстановление в регистровую память служебной информации, необходимой для выпол нения отдельных программ, которая не должна стираться во время замены программ 1. В данных. устройствах указанные действия выполняются посредством перехода на специаль ные подпрограммы записи в оперативную память или считывания в регистровую память, количество выполняемых команд, в которых определяет ся количеством слов, служебной информации, после чего выполняется прерванная программа с точки перехода. Аналогичным образом происхо.цит обращение к подпрограммам из основной программы. Такая организация хранения и в осстановления при замене программ требует значительных затрат времени. Наиболее близким по технической сущности к предлагаемому изобретению является устройство управления обменом, которое содержит приоритетное устройство, счетчик слов служебной информации, схему управления счетчиком и схему выработки управляющих сигналов 2. Такое устройство неэффективно осуществляет подготовку подпрограмм, сопутствующих переключаемым программам. Кроме того, в зтом устройстве используется дополнительная регистровая память с произвольным доступом, что трубет связи каждого дополнительного регистра с цепями записи и считывания вычислительного устройства через индивидуальные пшны, для чего применяется система вентилей, управляемых сложным устройством управления обменом. Для обмена каждого дополнительного регистра с запоминающим устройством требуется два сигнала управления. Аналогично организован- обмен регистров дополнительной и регистровой памяти. Поскольку каждый регистр связан только с одним регистром процессора, то такая организация является неэкономной. Целью настоящего изобретения является сокращение оборудования. Поставленная цель достигается тем, что в устройство, содержащее приоритетный узел, элемент формирования сигналов обмена, счетчик, элемент управления счетчиком, причем первый и второй входы элемента формирования сигналов обмена являются, соответственно первым и вторым входом устройства, третий вход элемента формирования сигналов обмена соединен с выходом счетчика, четвертый вход элемента формирования сигналов обмена и первый вход элемента управления счетчиком соединены с выходом прИоритетного узла, первый выход элемента форми рования сигналов обмена подключен к входу . приоритетного узла, второй выход элемента фор мирования сигналов обмена является первым выходом устройства, третий выход элемента фор мирования сигналов обмена подключен к второму входу элемента управления счетчиком, выход которого соединен с входом счетчика, четвертый выход элемента формирования сигналов обмена является вторым выходом устройства, вход-выход приоритетного узла является выходом-входом устройства, дополнительно введены коммутатор базового адреса, регистр базового адреса, дешифратор признака, причем первый и второй входы коммутатора базового адреса являются соответственно третьим и четвертым вхо дами устройства, выход коммутатора базового адреса объединен с выходом счетчика и является третьим выходом устройства, третий вход коммутатора базового адреса соединен с выходом регистра базового адреса, первый вход которого объединен с входом дешифратора признака и является пятым входом устройства, а второй вход регистра базового адреса объединен с третьим входом элемента управления счет чиком и подключен к первому выходу дешифpafopa признака, второй вход которого подклю чен ,к четвертому входу коммутатора базового адреса. Таким образом, с цепями считывания и запи си вычислительного устройства связаны только соответственно входной и выходной регистры дополнительной памяти, что значительно уменьшает количество информационных шин. При этом ликвидируется система входных и выходных вентилей дополнительных регистров и связанная с ними часть устройства управледая обменами. На чертеже представлена структурная схема устройства управления обменом. Устройство состоит из регистровой памяти 1, регистров 2 регистровой памяти, дополнительной памяти 3, регистров 4 дополнительной памяти, разрядов 5 регистровой и дополнительной памяти, вычислительного блока 6, оперативной памяти 7, блока 8 управления обменом. В состав вычислительного блока 6 входят узел 9 управления процессором, цепи 10 записи, цепи 11 считывания, коммутатор 12 адреса памяти. В состав блока управления обменом входят узел 13 определения последовательности работ, приоритетный узел 14, дешифратор признака 15, регистр 16 базового адреса, коммутатор 17 базового адреса; в свою очередь, в узел 13 определения последовательности работ входят счетчик 18, элемент 19 управления счетчиком, элемент 20 формирования сигналов обмена. В конкретном примере экономичной реализации обменов регистровой и дополнительной памяти каждый их регистр, содержащий слово, разбит на группы, например, по четыре разряда в группе. Каждая группа выполнена на регистрах сдвига. Выход старщего разряда группы регистров процессора соединен со сдвиговым входом соответствующей группы дополнительного регистра, а сдвиговый вход последне- го соединен с выходом старшего разряда группы регистра процессора. В режиме хранение устройство работает следующим образом. При появлении в основной программе команды хранения или при прерывании с необходимостью замены программ при обслуживании потока прерываний или требований на обработку узел 9 формирует сигналы обмена содержимого регистровой 1 и дополнительной 3 памяти, поступающие на входы управления сдвигом всех групп регистров регистровой 1 и дополнительной 3 памяти. Обмен во всех группах про исходит параллельно с последовательным сдвигом внутри группы. Таким образом, при указанном разбиении регистров, полный обмен содержимого регистровой и дополнительной памяти производится за четыре такта вычислительной машины с помощью одного управляющего сигнала, длительность которого состайляет тоже четыре такта. Регистры 4 дополнительной памяти при этом оказываются заполненными служебной информацией, которую необходимо сохранить при замене программ, а регистры 2 регистровой памяти заполнены служебной информацией программы, на которую будет передано управление, и вызванной из оперативной памяти 7 предшествующей командой восстановление, обслуживаемой прерыванием или требованием на обработку. Первое слово служебной информации переключаемой и заменяемой программ при этом должно находиться в нижнем регистре регистровой и выходном регистре дополнительной памяти, соответственно. По окончании йигнала обмена, после заполнения дополнительной памяти, блок управления 8 формирует сигнал запроса храР1ёния, поступающий в узел 13 на элемент 20 формирования сигналов обмена, где запрос фиксируется. При зтом элемент 20 сигналом через элемент 19 уп равления счетчиком обнуляет счетчик 18 (слов служебной информации) и формирует сигнал запуск хранения - восстановления, продолжающийся до полного заверще шя хранения, поступающий в приоритетный узел 14. Одновременно узел 9 устанавливает базовый адрес сохраняемой служебной информации заменяемой программы и подает сигналы управления, поступающие на коммутатор 12. В приоритетном узле сигнал запуска з1ранения - восстановления конкурирует с прошми запросами обращений к памяти, поступающими из вычислительного блока 6. При этом сигналу хранения восстановления отдается низший приоритет, т.е. хранение - восстановление происходит в промежутки времени, когда процессор не обращается к памяти 7. Приоритетный узел 14 сообщает вычислитель ному блоку 6 о виде допущенного обращения в память, открывая одновременно один из вхо дов коммутатора 12 адреса памяти, выход которого связан с адресными входами цепями записи и считывания 11. Если в конкретный момент времени нет обращений устройства к памяти и оно свободно для обращений, то на вход цепи 10 и И посту пает адрес слова служебной информации с вы-ходов счетчика 18 и коммутатора 17. Одновременно запускается временная диаграмма обращения к памяти, находящаяся в узле 9. При этом содержимое выходного регистра дополнительной памяти 3 через цепи записи 10 переписывается в ячейки памяти 7 с адресом, равным базовому адресу служебной информаци скоммутированному коммутаторами 17 и 12. После заверщения работы памяти 7 узел 9 информирует приоритетный узел 14 о заверщении операции обращения к запоминающему уст ройству. Узел 14, в свою очередь, информирует об этом элемент 19 управления счетчиком, который добавляет единицу к счетчику 18, а также элемент 20 формирования сигналов обме на, который вырабатывает сигнал управления, поступающий на вторые управляющие входы всех регистров 4 дополнительной памяти 3 и осуществляющий передачу содержимого всех ре гистров 4 на один регистр вниз, благодаря тому, что выходы всех разрядов каждого вер него, регистра дополнительной памяти непосре ственно соединены со входами следующего (нижнего) регистра. Аналогич}10 осуществляется хранение всех следующих слов, находяпшхся в дополнительной памяти. При этом содержимое счетчика 18 nocTynaei в элемент 20. Когда после очередного прибавления единицы к счетчику 18, его содержимое адресует последнее слово служебной информации, блок 20 вырабатывает .сигнал запуска хранения восстановления и посылает в элемент 9 сигнал о завершении команды хранения. Аналогично производится восстановление содержимого регистровой памяти процессора с той разницей что запрос восстановления посылает узел 9 в элемент 19, а заполнение регистров 4 дополнительной памяти 3 производится через цепи считывания 11 вычислительного блока 6. Кроме того, сигнал обмена содержимого регистровой и дополнительной памяти вырабатывается узлом 9 после завершения заполнения всех регистров дополнительной памяти служебной информацией, считанной из памяти. Подготовка сопутствующих подпрограмм производится следующим образом. При напитай в одном из слов, считанном из памяти 7 при восстановлении служебной информации программы, признака сопутствующей подпрограммы, дешифратор признака 15 вырабатывает сигнал, разрешающий прием базового адреса служебной информации сопутствующей подпрограммы, содержащиеся в данном слове основной программы, на регистр базового адреса 16, и обнулящий через элемент 19 счетчик -18. Кроме того, дешифратор признака 15 коммутирует выходы регистра 16 коммутатора 17. Таким образом, на вход коммутатора 12 адреса памяти поступает адрес первого слова служебной информащш сопутствующей подпрограммы. Далее устройство работает аналогично простому восстановлению, заполняя регистры дополнительной памяти служебной информа1щей сопутствующей подпрограммы. Таким образом, не дожидаясь полного эаполне шя регистров дополнительной памяти служебной информацией заменяемой программы и не начиная выполнение этой программы, устройство обеспечивает заполнение дополнительной памяти служебной информацией сопутствующей подпрограммы, как только на выходе цепей сщпывания вычислительного устройства будет обнаружен признак сопутствующей noRiiporpaMNtbi. Введение дешифратора признака, регистра и коммутатора базового адреса служебной информации позволяет значительно уменьшить время подготовки сопутствующих подпрограмм, т.е. заполнения регистровой памяти процессора служебной информацией сопутствующих подпрограмм, сохраняемой в запоминающем устройстве во время замены программ. Кроме того, использование регистровой памяти конвейерно1о типа в качестве дополнительной памяти позволяет сократить логическое оборудование на реализацию дополнительной памяти, уменьимть- количество информяUHOHHiix ишн, связывающих цепи записи и считывания вычислительного устройства с допблнительной памятью в число раз, равное числу регистров дополнительной памяти, уменьшить разрядность шин, связывающих регистры регистровой и дополнительной памяти, до числа, равного числу rpjmn, на которые разбит каждый регистр, упростить устройство управления обменами, сократить количество сигналов управления обменами всех регистров дополнительной и регистровой памяти до одного сигнала и сигналов обмена дополнительной памяти и запоминающего устройства также до одного сигнала. мула изобретения Устройство управления обменом, содержащее приоритетный узел, элемент формирования сигналов обмена, счетчик, элемент управления счетчиком, причем первый и второй входы эле . мента формирования сигналов обмена являются соответственно первым и вторым входом устройства, третий вход элемента формирования сигналов обмена соединен с выходом счет чика, четвертый вход элемента формирования сигналов обмена и первый вход элемента управления счетчиком соединены с выходом при оритетного узла, .первый выход элемента формирования сигналов обмена подключен к входу приоритетного y3Jja второй выход элемента формирования сигналов обмена является первым выходом устройства, третий выход элеме та формирования сигналов обмена под1Й1ючен к второму входу элемента управления счетчиком, выход которого соединен с входом счетчика, четвертый выход элемента формирования сигналов обмена является вторым выходом устройства, вход-выход приоритетного узла является выходом-входом устройства, отличающееся тем, что, с целью сокращения оборудования и повышения быстродействия, в него введены коммутатор базового адреса, регистр базового адреса и дешифратор признака, причем первый и второй входы коммутатора базового адреса являются соответственно третьим и четвертым входами устройства, выход коммутатора базового адреса объединен с выходом счетчика и является третьим выходом устройства, третий вход коммутатора базового адреса соединен с выходом регистра базового адреса, первый вход которого объединен со входом дешифратора признака и является пятым входом устройства, а второй вход регистра базового адреса объединен с третьим входом элемента управления счетчиком и подключен к первому выходу дешифратора признака, второй выход которого подключен к четвертому входу коммутатора базового адреса. Источники информации, принятые во внимание при экспер.тизе 1.Коган Б. М., Каневский М. М. Цифровые вычислительные машины и системы. М., Энергия, 1974. 2.Патент США N 3731810, кл. 340-172.5, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор ввода-вывода | 1980 |

|

SU934465A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обмена информацией | 1983 |

|

SU1142824A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство обмена данными | 1989 |

|

SU1697083A2 |

| Процессор ввода-вывода | 1983 |

|

SU1149240A2 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для обмена информацией | 1979 |

|

SU826330A1 |

Авторы

Даты

1980-10-15—Публикация

1977-09-21—Подача