(54) УСТРОЙСТВО АДРЕСАЦИИ ОПЕРАТИВНОЙ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адресации памяти | 1984 |

|

SU1251076A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для обмена данными между оперативной памятью и внешними устройствами | 1985 |

|

SU1295404A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1751772A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при проектировании ЭВМ с оперативными памятями, объем которых больше, чем область адресации операндов в системе команд.

Известна система расширения объема памяти, содержапшя два блока памяти, схему возбуждения, входы которой под управлевием схемы управления циклами через логику определения активизируют один блок оперативной памяти по содержимому регистра адреса. Длина адресной константы соответствует объему одного блока памяти l.

Недостаток этой системы состоит в том, что схема возбуждения и схема управления циклами требуют больших аппач ратурных затрат. Сложна также организация активизации блока памяти.

Наиболее близким к изобретению я ляется устройство для формирования адресов, содержащее дешифратор, группы элементов И, сдвигающий регистр, грутьпу индексных регистров, сумматор адр са, элемент И С2 J.

Недостатком устройства является то, что оно не позволяет использовать опера тивную память с о&ьемам, превышающим количество констант.

Целью изобретения является расширение функциональных возможностей за счет обеспечения возможности адресации one- ,Q ративной памяти, своим объемом превышающей количество располагаемых адреоных констант.

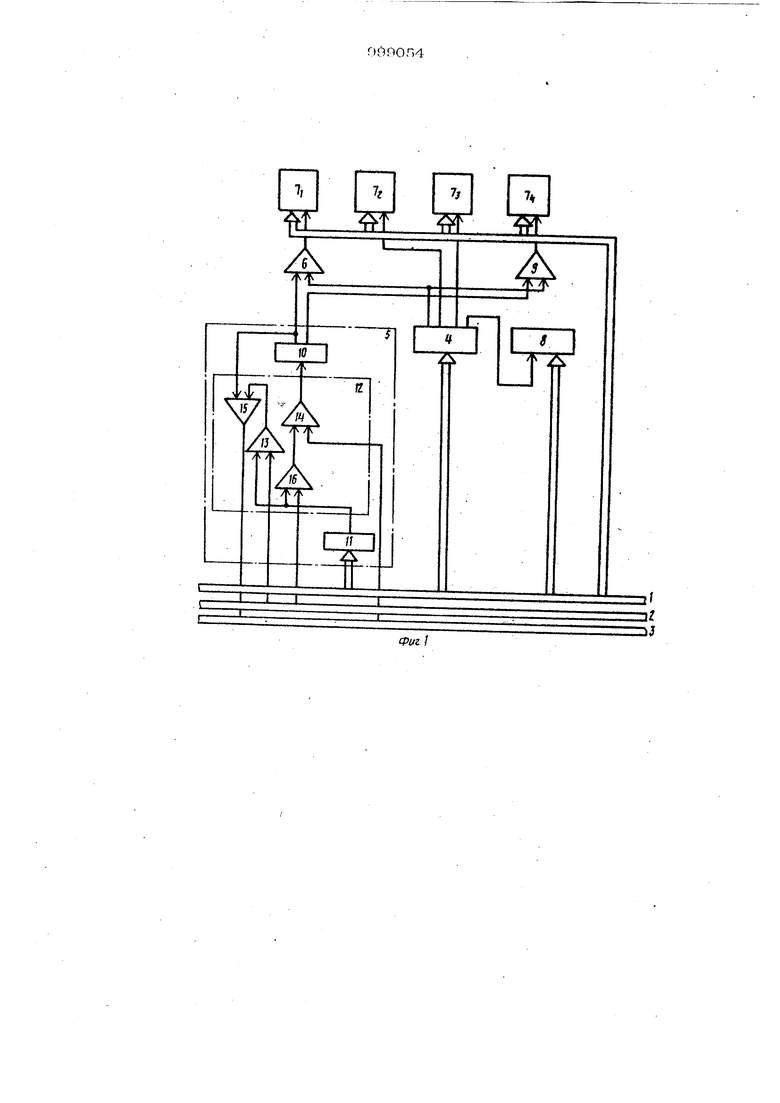

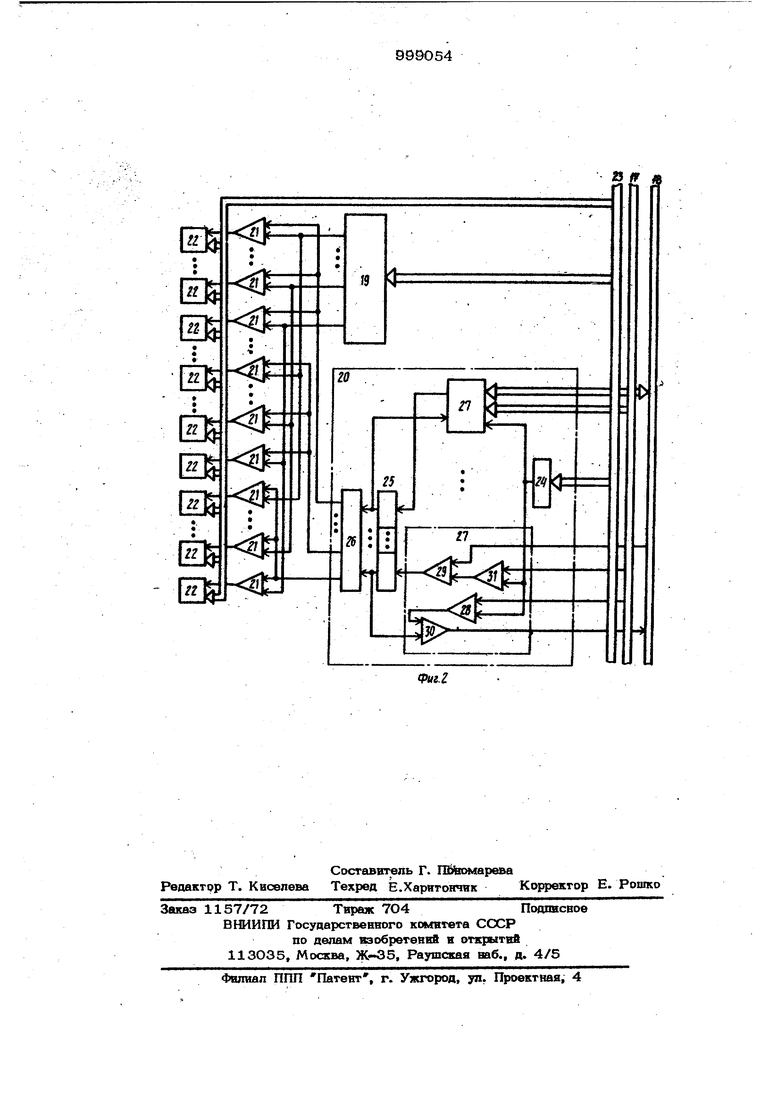

Эта цель достигается тем, что в устройство адресации оперативной памяти, )5 содержащее первый дешифратор и К групп элементов И (К - число групп- блоков оперативной памяти), причем i -и ( i 1...К) выход первого дешифратора соединен с первыми входами элементов. И 20 i -и группы, введены два дешифратора, регистр, К блоков управления, каждый из которых содержит четыре элемента И, причал каждый 1 -и разрядный выход р&гистра соединен с i -Ъ1М входом первого дешифратора и первым вхадом первого элемента И f-ro блока уг авяенш, выход второго дешифратора соединен с первыми входами второго и третьего элемен тов И каждого блока управления, вторые входы которых соединены с группой управляющих входов устройства, первый вход четвертого элемента И и выход первого элемента И блока управления соединены с группой входоь-вьтходов данных устройства, выход четвертого элемента И i-го блока управления соединен с 1-ым входом регистра, группа входов второго дешифратора соединена с группой адресных входов устройства, старшие разряды группы адресных входов устройства соединены с группой входов третьего дешифратора, i-и выход ( .., 2, где i - чспо элементов И в группе) которого соединен с вторыми входами t -ых элементов И каждой грутшы, выходы которых являются выходами устройства, выход второго элемента И i -го блок управления соединен с вторым входом первого элемента И i -го блока уяравления, выход третьего элемента И i-ro блока управления соединен с вторым входом четвертого элемента И -го блока управления. На фиг. 1 представлена блок-схема устройства адресации оперативной памяти в котором адресные константы в объеме одного модуля отведены для адресации регистров внешних устройств; на фиг. 2 то же, в котором при помощи П разрядо адресуется 2 модулей оперативной памяти (К - количество разрядов регистра, входящего в блок выборки устройства Устройство (фиг. 1) содержит адреса ные входы 1 группы, управляющие входы 2группы, входы-выходы 3 данных группы, дешифратор 4, блок 5.выборки, элемент И 6, блоки 7 памяти группы, блок 8 памяти регистров внешних устройств, элемент И 9, Блок 5 выборки содержит триггер 10 дешифратор 11, блок 12 управления содержит элементы И 13-16. Устройство (фиг. 2) содержит управляющие входы 17 группы входы-выходы 18 данных группы, дешифратор 19, блок 20 выборки, элементы И 21 группы, блоки 22 памяти группы, адресга 1е входы 23 группы. Блок 20 выборки содержит первый дешифратор 24, регистр 25, второй дешифратор 26, блоки 27 управления. Блок 27 управления содержит эл мсешы И 2831. Устройство работает следующим образом. Триггер 1О имеет определенный адрес из области адресов памяти регистров внешних устройств 8, Этот адрес дешифрируется дешифратором 11, на первые входы элементов И 16 и 13 подаются единичные сигналы. Если на входе управления 2 был сигнал Запись, открывается элемент И 16. На второй вход элемента И 14 подается , и по содержимому определенного разряда входа 3 данных триггер 10 устанавливается в Нулевое или единичное состояние. Если на управляющем входе 2 был сигнал Считывание, открывается элемент И 13. На второй вход элемента И 15 подается 1 и в зависимости от состояния триггера 10 на вход данных 3 поступает информация о состоянии триггера 10, Так как триггер 10 имеет определенный адрес, это позволяет рассматривать триггер как активную ячейку оперативной памяти, н обращаться к нему с помощью адресных инструкций, т.е. программным путем. Допустим, что триггер 10 блока 5 выборки находится в состоянии О. Если адресная константа на входе 1 адреса из области адресов блоков 7 - 7 j , дешифратор 4 по двум старшим битам этой константы формирует единицу на одним из лервых трех выходов соответственно. Если единица была сформирована на первом выходе дешифратора 4, при наличии на управляющем входе элемента И 6 выбирается блок 7. Выборка блоков 7 2 или 7 происходит по единичному сигналу второго или третьего выходов дешифра тора 4. Если адресная константа на входе адреса 1 из области адресов блока 7 дешифратор 4 выдает единицу на четвертом выходе и происходит выборка блока памяти регистров внешних устройств 8. Выборка блока 7 возможна лишь при единичном состоянии триггера 10, входящего в блок 5 выборки. При включенном триггере 10 первый выход блока 5 выборки находится в нулевом состоянии, а второй - в единичном состоянии. Таким образом, отсутствие управляющего СИ1 нала На первсим входе элемента И 6 запрещает выборку блока 7. Единичный второй выход блока 5 вщборки и первый выход дешифратора 4 в состоянии через элемент И 9 выбирают блок 74. Выбранный блок является открытым для адресации его ячеек при помощи млалшкк разряде адресной константы, посту пающей по входу 1 на другой вход На фиг. 2 представленная схема устройства адресации оперативной памяти отличается от устройства, показанного на фиг. 1 тем, что вместо триггера 10 имеется, регистр и дешифратор 26 для выявления состояний этого регистра. Бл 27 управления в соответствии с адреоной инструкцией, поступающей по входу 23, и содержимому определенных разрядов входа-4ыхода 18 под управлением сигналов на входе 17 определяет состоя ние триггеров регистра 25 и в соответствии с этим на одном вз выходов де- шифратора 26 появляется . Она откр вает соответствующие элементы И 21 группы, обеспечивай выборку одного из блока 22 памяти дешифраторе 19, состояние которого определяется старшими разрядами адресной константы на входе 2с. . Описанное устройство позволяет ио. пользование оперативной памяти с o6i емом, превышающим число располага0 ы адресных констант. Максимальное раоширение памя1 определяется количество разрядов регистра блока 5 выборки. При помощи К разрядов оперативная память может быть расширена 2 раз.. Изобретение позволяет использовать оперативнуюпамять с объемом, достаточ ным для размещения всех программ со своими данньпга, и поэтому процессор имеет дело только с быстродействующей оперативной памятью. Вариант реалтаации изобретения, в котором блок ы 1бо1жи содержит только один триггер, позволяет при сравнител но незначительных затратах аппаратуры использовать ту часть оперативной памяти, которая вводится принудительно в связи с выпуском блоков памяти опр&деленного объема, который не 5шляется кратным проектному оперативной памяти. При этом не только становится эффективной эта часть памяти, но и осво бождается определенное количество адрес нъ1х констант для обращения к внешним гстройствам, что дает возможность иофору ашоо для управления внешними yci рэйствами обрабатывать также, как и об рабатываются данные. Формула изобрете ни я . Устройство адреоа1ШИ оперативной памяти, содержащее первый дешифратор и К групп элементов И (К - число групп блоксю оперативной. памяти), причем i-й( 1...К) выход первого депгафрато соединен с первыми входами элементов И - i -и группы, о т л и ч а ю щ е е с я тем; что, с целью расширения функциональных возможностей за счет обеспечения возможиости адресации оперативной памяти, cBOAf объемом превышаку щей количество рвспотшгаемьк адресный констант, в него введены два яешсфратора, регистр, К блоков управления, каж дый из которых содержит четыре эломевта И, причем каждый i-й разрядный выход регистра соединен с - входам первого дешифратора и первым входом первого элемента И i-ro блока управлеи ния, выход второго {дешифратора соединен с первыми второго и третьего алемеетов И каждого блока у1фавления, вторые входъ кото1 лх соедииены с груян пой управляющих входов устройства, п ршлй вход четвертого элемента И и выход nefffioro элемента И блока утфавл&ния соединенъ с группой входов-«ыходов данных устройства, выход четвертого элемента И блока управления сое11инеи с -ым входом регистра, группа входов второго дешифратора соединена с группой адресных входов устройства, старшие разряды группы адресных входов устройств соедииеиы с грутшой входов третьего , 4-й выход (i 1... Е , где Е - число элементов И в группе) которого соединен с втор|11ми входами ( -ых элементов И каждой группы, выходы которых являются выходами устройства, выход второго элемента И i -го блока управления соединен с вторым вкодом первого элемента И i нгр блока управления, а выход третьего алемевта И inro блока управления - с вторым , входом четвертого элемента И 1 -го блока управления. Источники ииформацгоЕ, принятые во внимание при экспертизе 1.Патент США М 3395392, кл. 34О-172.5, 1968. 2.Авторское свижетельство ССС № 446880, кл. Q 06 F 9/36, 1972 (прототип).

Авторы

Даты

1983-02-23—Публикация

1981-07-06—Подача