Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств высокой производительности.

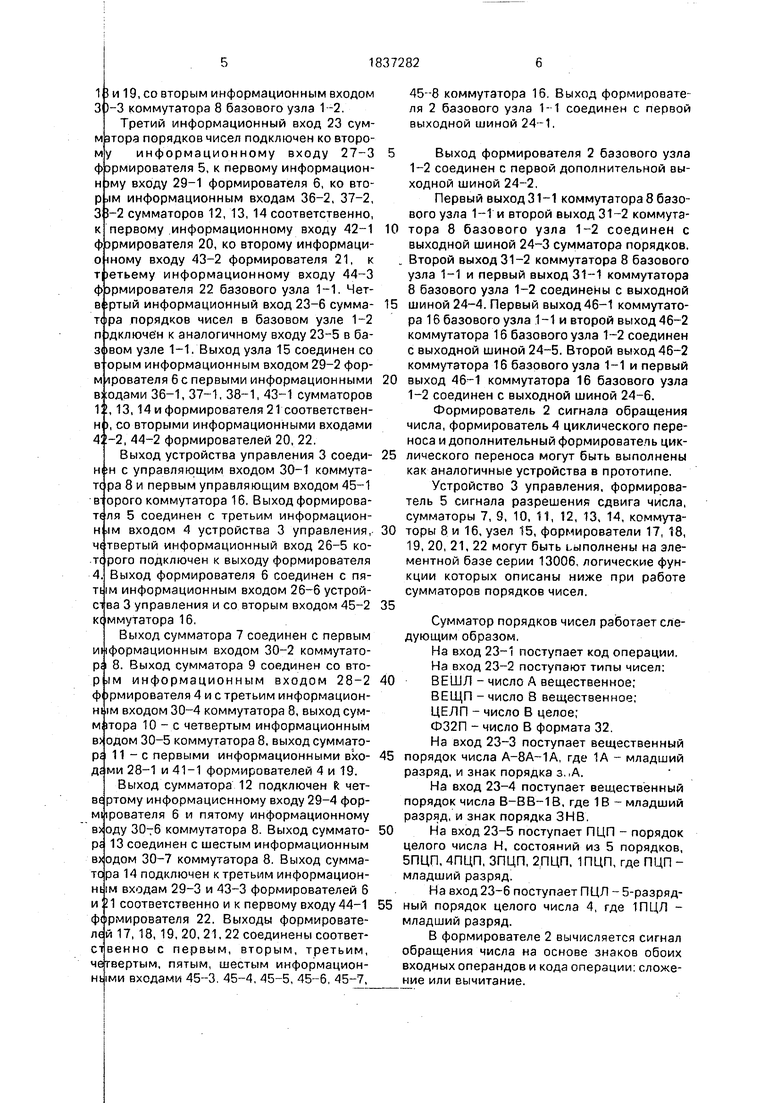

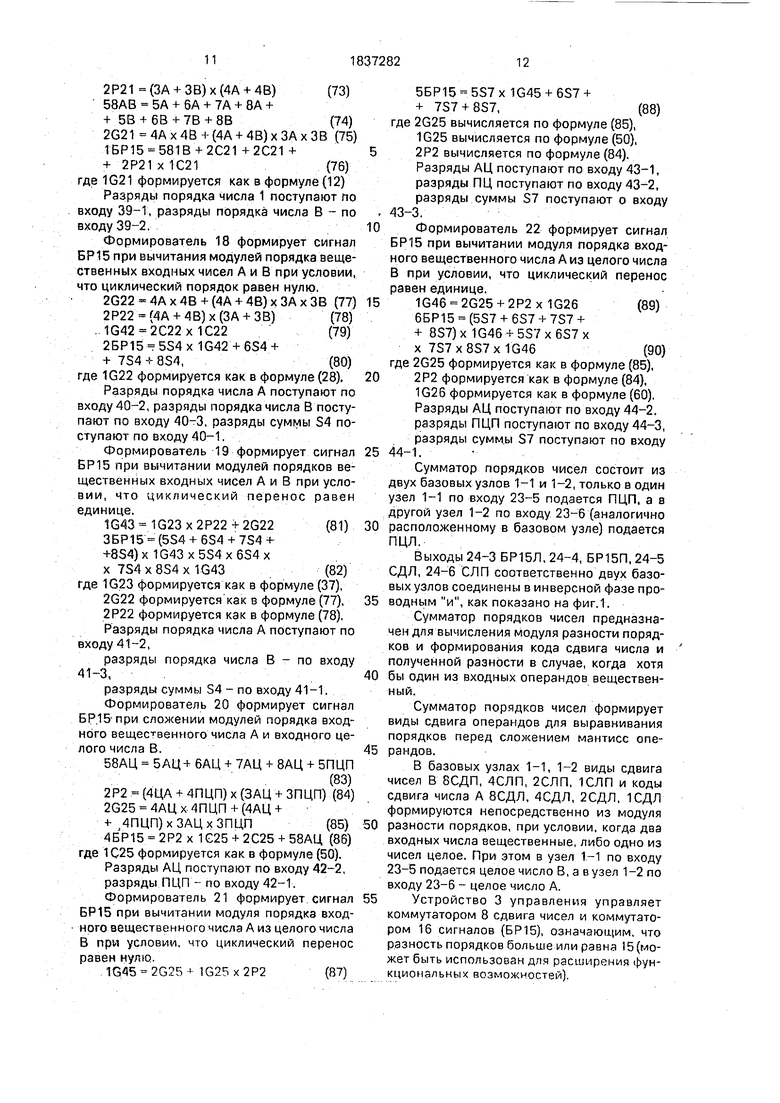

Цель изобретения - повышение быстродействия за счет сокращения логических уровней.На фиг.1а и 16 представлена функциональная схема сумматора порядков чисел; на фиг.2 - схема устройства управления.

Сумматор порядка состоит из двух базовых узлов 1-1 и 1-2, каждый из которых содержит формирователь 2 сигнала обращения числа, устройство 3 управления, формирователь 4 циклического переноса в случае, когда оба входных числа вещественные, формирователь 5 сигнала разрешения сдвига числа, дополнительный формирователь 6 циклического переноса в случае, когда одно

из чисел - целое, первый сумматор 7, первый коммутатор 8, первый дополнительный сумматор 9, второй дополнительный сумматор 10, второй сумматор 11, третий дополни- тельный сумматор 1.2, четвертый дополнительный сумматор 13, пятый дополнительный сумматор 14, узел 15 обращения порядка числа, второй коммутатор 16, первый формирователь 17 информационного сигнала, второй формирователь 18 информационного сигнала, третий формирователь 19 информационного сигнала, четвертый формирователь 20 информационного сигнала, пятый формирователь 21 информационного сигнала, шестой формирователь 22 информационного сигнала, первую управляющую шину 23-1, вторую управляющую шину 23-2, первую информационную шину 23-3, вторую информационную шину 23-4,

00

со 1

ю

00

ю

третью информационную шину 23-5, дополнительную информационную шину 23-6, первую выходную шину 24-1, вторую выходную шину 24-2, третью выходную шину 24- .3, первую дополнительную выходную шину 24-4, вторую дополнительную выходную шину 24-5, третью дополнительную выходную шину 24-6.

Формирователь 2 сигнала обращения числа имеет управляющий вход 25-1, первый и второй информационные входы 25-2, 25-3, устройство 3 управления - первый, второй информационные входы 26-1, 26-2, управляющий вход 26-3, третий, четвертый, пятий информационные входы 26-4, 26-5, 26-6, формирователь 4 циклического переноса - первый и второй информационные входы 28-1, 28-2, формирователь 5 сигнала разрешения сдвига числа - управляющий вход 27-1, первый и второй информационные входы 27-2,27-3, дополнительный формирователь 6 циклического переноса - первый, второй, третий и четвертый информационные входы 29-1, 29-2. 29-3, 29-4, первый коммутатор 8 - управляющий вход 30-1, первый, второй, третий, четвертый, пятый и шестой информационные еходы 30- 2, 30-3, 30-4, 30-5, 30-6, 30-7, первый и втором выходы 31-1,31-2, первый сумматор 7 - первый и второй информационные входы 32-1, 32-2, первый дополнительный сумматор 9 - первый и второй информационные входы 33-1, 33-2, второй дополнительный сумматор 10 - первый и второй информационные входы 34-1, 34-2, второй сумматор 11 - первый и второй информационные входы 35-1, 35-2, третий дополнительный сумматор 12 - первый и второй информационные входы 36-1, 36- 2, четвертый дополнительный сумматор 13 - первый и второй информационные входы 37-1, 37-2, пятый дополнительный сумматор 14 - первый и второй информационные входы 38-1,38-2, первый формирователь 17 информационного сигнала - первый и второй информационные входы 39-1,39-2, второй формирователь 18 информационного сигнала - первый, второй, третий информационные входы 40-1, 40-2, 40-3, третий формирователь 19 информационного сигнала - первый, второй, третий информационные входы 41-1, 41-2, 41-3, четвертый формирователь 20 - первый и второй информационные входы 42-1, 42-2, пятый формирователь информационного сигнала 21 - первый, второй и третий информационные входы 43-1, 43-2, 43-3, шестой формирователь информационного сигнала 22 - первый, второй, и третий информационные входы 44-1, 44-2, 44-3, второй коммутатор

16 - первый и второй управляющие входы 45-1, 45-2, первый, второй, третий, четвертый, пятый, шестой информационные входы 45-3, 45-4, 45-5,45-6, 45-7, 45-8, первый и

второй выходы 46-1, 46-2.

Первый управляющий вход 23-1 сумматора порядков чисел соединен с управляющим входом 25-1 формирователя 2 сигнала обращения числа базовых узлов 1-1 и 1-2.

Второй управляющий вход 23-2 сумматора порядков чисел подключен к управляющему входу 26-3 устройства 3 управления и управляющему входу 27-1 формирователя 5 базовых узлов 1-1 и 1-2. Первый информационный вход 23-3 сумматора порядков чисел соединен со вторым информационным входом 25-3 узла 2, со вторым инфор- мационным входом 26-2 устройства 3 управления, вторыми информационными

входами , 33-2, 34-2 сумматоров 7, 9, 10 соответственно с первым информационным входом 35-1 сумматора 11, входом узла 15, с первым информационным входом 39-1 формирователя 17, со вторыми информационными входами 40-2, 41-2 формирователей 18 и 19 вторых.информационных входов 30-3, коммутатора 8 базового узла 1-1 и с первым информационным входом 26-1 устройства управления 3, с первыми информационными входами 25-2, 27-2 формирователей 2 и 5, с первыми информационными входами 32-1, 33-1, 34-1 сумматоров 7, 9, 10 соответственно, со вторым информационным входом 35-2 сумматора

11, со вторым информационным входом 39 формирователя 17, с третьими информационными входами 41-3, и 41-3 узла 18 и 19 базового узла 1-2.

Второй информационный вход 23-4

сумматора порядков чисел соединен с первым информационным входом 26-1 узла 3, с первыми информационными входами 25- 2, 27-2 формирователей 2 и 5, с первыми информационными входами 32-1, 33-1, 34-1

5 сумматоров 7, 9, 10 соответственно, со-вторым информационным входом 35-2 сумматора 11, со вторым информационным входом 39-2 формирователя 17, с третьими информационными входами 40-3,41-3 фор0 мирователей 18 и 19 базового узла 1-1 и со вторым информационным входом 25-3 формирователя 2, со вторым информационным входом 26-2 устройства управления 3, со вторыми информационными входами 32-2,

5 33-2, 34-2, сумматоров 7, 9, 10 соответственно с первым информационным входом 35-1 сумматора 11, с входом узла 15, с первым информационным входом 39-1 формирователя 17, со вторыми информационными входами 40-2, 41-2 формирователей узпов

ф

1 и 19, со вторым информационным входом

-3 коммутатора 8 базового узла 1-2.

Третий информационный вход 23 сумматора порядков чисел подключен ко второму информационному входу 27-3 формирователя 5, к первому информацион- н )му входу 29-1 формирователя 6, ко втоIM информационным входам 36-2, 37-2,

3-2 сумматоров 12, 13, 14 соответственно,

первому .информационному входу 42-1 формирователя 20, ко второму информационному входу 43-2 формирователя 21, к

етьему информационному входу 44-3 формирователя 22 базового узла 1-1. Четртый информационный вход 23-6 сумма- тфра порядков чисел в базовом узле 1-2

щключе н к аналогичному входу 23-5 в бавом узле 1-1. Выход узла 15 соединен со

орым информационным входом 29-2 формирователя 6 с первыми информационными

одами 36-1, 37-1, 38-1, 43-1 сумматоров 1 ,13,14 и формирователя 21 соответственI, со вторыми информационными входами

-2, 44-2 формирователей 20, 22.

Выход устройства управления 3 соединен с управляющим входом 30-1 коммута- тс ра 8 и первым управляющим входом 45-1

орого коммутатора 16. Выход формирова- 5 соединен с третьим информационим входом 4 устройства 3 управления, четвертый информационный вход 26-5 коте рого подключен к выходу формирователя

Выход формирователя 6 соединен с пя- т м информационным входом 26-6 устройва 3 управления и со вторым входом 45-2 коммутатора 16.

Выход сумматора 7 соединен с первым

формационным входом 30-2 коммутато- 8. Выход сумматора 9 соединен со вто,IM информационным входом 28-2 формирователя 4 и с третьим информационIM входом 30-4 коммутатора 8, выход сум- 10 - с четвертым информационным

одом 30-5 коммутатора 8, выход суммато- р4 11 - с первыми информационными вхоми 28-1 и 41-1 формирователей 4 и 19.

Выход сумматора 12 подключен к чет- ве ртому информационному входу 29-4 формирователя 6 и пятому информационному

оду 30-6 коммутатора 8. Выход суммато13 соединен с шестым информационным вводом 30-7 коммутатора 8. Выход сумматора 14 подключен к третьим информационIM входам 29-3 и 43-3 формирователей 6

1 соответственно и к первому входу 44-1

рмирователя 22. Выходы формирователе 17, 18, 19, 20, 21, 22 соединены соответ- венно с первым, вторым, третьим,

четвертым, пятым, шестым информационен входами 45-3. 45-4, 45-5, 45-6, 45-7,

45-8 коммутатора 16. Выход формирователя 2 базового узла 1-1 соединен с первой выходной шиной 24-1.

5Выход формирователя 2 базового узла

1-2 соединен с первой дополнительной выходной шиной 24-2.

Первый выход 31-1 коммутатора 8 базового узла 1-1 и второй выход 31-2 коммута- 0 тора 8 базового узла 1-2 соединен с выходной шиной 24-3 сумматора порядков. , Второй выход 31-2 коммутатора 8 базового узла 1-1 и первый выход 31-1 коммутатора 8 базового узла 1-2 соединены с выходной 5 шиной 24-4. Первый выход 46-1 коммутатора 16 базового узла 1-1 и второй выход 46-2 коммутатора 16 базового узла 1-2 соединен с выходной шиной 24-5. Второй выход 46-2 коммутатора 16 базового узла 1-1 и первый 0 выход 46-1 коммутатора 16 базового узла 1-2 соединен с выходной шиной 24-6.

Формирователь 2 сигнала обращения числа, формирователь 4 циклического переноса и дополнительный формирователь цик- 5 лического переноса могут быть выполнены как аналогичные устройства в прототипе.

Устройство 3 управления, формирователь 5 сигнала разрешения сдвига числа, сумматоры 7, 9, 10, 11, 12, 13, 14, коммута- 0 торы 8 и 16, узел 15, формирователи 17, 18, 19, 20, 21, 22 могут быть ьыполнены на элементной базе серии 13006, логические функции которых описаны ниже при работе сумматоров порядков чисел. 5

Сумматор порядков чисел работает следующим образом.

На вход 23-1 поступает код операции. На вход 23-2 поступают типы чисел: 0 ВЕШЛ - число А вещественное; ВЕЩП - число В вещественное; ЦЕЛП - число В целое; Ф32П - число В формата 32. На вход 23-3 поступает вещественный 5 порядок числа А-8А-1А, где 1А - младший разряд, и знак порядка з.,А.

На вход 23-4 поступает вещественный порядок числа В-ВВ-1В, где 1В - младший разряд, и знак порядка ЗНВ. 0На вход 23-5 поступает ПЦП - порядок

целого числа Н, состояний из 5 порядков, 5ПЦП, 4ПЦП, ЗПЦП, 2ПЦП, 1ПЦП, где ПЦП - младший разряд.

На вход 23-6 поступает ПЦЛ - 5-разряд- 5 ный порядок целого числа 4, где 1ПЦЛ - младший разряд.

В формирователе 2 вычисляется сигнал обращения числа на основе знаков обоих входных операндов и кода операции: сложение или вычитание.

В устройстве 3 управления формируются сигналы коммутации для коммутаторов 8 и 16.

ВЕРС ВЕЩЛ х ВЕЩП х РСД(1)

1 КСП ВЕРС х ЗНА хЗНВ(2)

2КСП ВЕРСхЗНАхЗНВ(3)

ЗКСП ВЕРСхЗНАхЗНВ(4)

4КСП ВЕЩЛ х ЦЕЛП х ЗНА и РСД (5) 1КСЛ ВЕЩЛ х ЦЕЛП х ЗНА х РСД (6) РАЗПР 2КСП х ЦПВ + 1КСП + ЗКСП х хЦПВ + 4КСПхЦПЦ(7)

РАЗРЛ 1КСЛ х ЦПЦ + 4КСП х ЦП Ц, (8) гдо РСД - сигнал разрешения сдвига, формирующийся о узле 5 (вход 26-4 устройства 3); ЦПВ - циклический перенос в случае двух вещественных чисел, формируемый в формирователе 4 (вход 26-5);

ЦПЦ - циклический перенос в случае, когда одно из чисел - целое, формируемый в формирователе 6 (вход 26-6);

ВЕЩЛ, ВЕЩП, ЦЕЛП (вход 26-3); ЗНА (вход 26-2); ЗНВ (вход 26-1);

1КСП-4КСП - сигналы коммутации сдвигов числа В;

1КСЛ - сигнал коммутации сдвига числа А; РАЗРП - разрешение сдвига числа В; РАЗРЛ - разрешение сдвига числа А, Сигналы управления коммутаторов формируются все одновременно каждый такт, так как сумматор порядков работает в конвейерном режиме.

Сигналы управления 1 КСП, 2КСП, ЗКСП, 4КСП, РАВРП необходимы для формирования сигналов сдвига числа В, а 1КСЛ, РАЗРЛ - числа А.

Необходимость нескольких сигналов; 1КСП, 2КСП, ЗКСП, 4КСП обусловлена различными ситуациями, реализуемыми сумматорами, функции и смысл которых указаны ниже.

В формирователе 5 формируется сигнал разрешения сдвига числа (РСЛ). Если РСЛ 0, то число при выравнивании порядков не сдвигается.

РСД РСДЦхРСДФ32(9)

При анализе целого числа формируется: РСДЦ ПЦП х ЦЕЛП(10)

При анализе вещественного числа формата 32 для случая, когда порядок минимальный:

РСДФ ПЦП х Ф32П х ВЕЩП х 5В, (11) где сигналы поступают: ПЦП-по входу 27-3 Ф32В, ВЕЩП, ЩЕЛП - по входу 27-1 5В-по входу 27-3. Обозначим: П - полусумма; G - перенос; Р - условия переноса через разряды.

Цифра перед обозначением Н, G, P указывает, какие пары разрядов участвует в формировании операции, первая цифра после буквенного обозначения указывает ко- личество разрядов, участвующих в формировании операции,

вторая цифра - номер сумматора. Сумматор 7 складывает четыре младших разряда модулей порядка веществен- 0 ных входных А и В чисел:

1С21 2Аи2В + (2А + 2В)х 1Ах 1В (12) + ЗВ(13)

1S1 1A+1B(14)

251 2А + 2В + 1Ах 1В(15)

5 + 1С21(16)

4S1(3H1 x1G21) + 41 +4B+3Ax хИхЗВ,(17)

где разряды порядка числа 4 поступают по входу 32-1,

0 разряды порядка числа В - по входу 32-3.

В коммутаторе В формируются сигналы сдвига ВС1Л, 4СДЛ, 2СДЛ, 1СДЛ (выход 31- 1) для сдвига числа А и ВСДП, 4СДП, 2СДП, 5 1СДП (выход 31-2) для сдвига числа В.

СТР 1 КСП х 2КСП х ЗКСП(18)

1СДП 2АЗРПх(153х2КСП + +153 х 1 КСП + 153 х ЗКСП + + 1S6xCTP)(19)

0 2СД РАЗПР х (252 Х2КСП + + 151 х 1 КСП + 2S3x ЗКСП + + 2S5xCTP)(20)

4СЛП РАЗРП х (3S2 х 2КСП + + 3S1 х 1 КСП + 353 х ЗКСП + 5 + 3S5xCTP)(21)

БСЛП РАЗПР х (452 х 2КСП- + +451 х 1 КСП + 453 х ЗКСП + + 455 х СТР)(22)

1СДП РАЗРЛ х (1S5 х ЗНА +. 0 + 1S6x3HA)(23)

2СДЛ РАЗРЛ х (2S5 х ЗНА + + 2S6x3HA)(24)

4СДЛ РАЗРЛ х (3S5 х ЗНА + + 356x3 НА)(25)

5 ВСДЛ РАЗРЛ (455 х ЗНА +

+ 4S6 х ЗНА),(26)

где разряды сумм 1S1, 2S1, 3S1, 4S1 поступают по входу 30-2, разряды сумм 152,252, 352,452-по входу30-4, разряды сумм 153, 0 253,353,453 - по входу 30-5, разряды сумм 155, 255, 355, 455 - по входу 30-6, разряды сумм 156,256,356,456 - по входу 30-7,3 НА - по входу 30-3.

1КСП. 2КСП, ЗКСП, РАЗРП, РАЗРЛ по- 5 ступают по входу 30-1.

Сумматор 9 вычитает четыре младших разряда модулей порядков вещественных входных чисел А и В при условии, что циклический перенос равен нулю.

ЗНАК ЗА ЗВ(27)

1C22 2Ax2B + (2A + 2B)x1Ax1B (28) 1S2-1A+1B(29)

2S2 2A + 2B + 1Ax 1B(30)

3S2 3H2 + 1C22(31)

4S2 (3H2x1C22) + 4A + + 4B+3Ax3B(32)

где разряды порядка числа А поступают по входу 23-2, разряды порядка числа В поступают по входу 33-1,

Сумматор 10 вычитает четыре младших разряда модулей порядка вещественных входных чисел А и В при условии, что циклический перенос равен 1, т.е. к младшему разряду суммы прибавляется единица цикического переноса

1Р13 1Ах 1В(33)

2С13 2А + 2В(34)

2НЗ 2А + 2В(35)

1Р23 (1А+1В)х(2А + 2В)(36)

1С23 2С13 + 1Р23(37)

1S3 1A+ 1В(38)

2S3 tP23+2H3(39)

3S3 2C13 + (1P13x2H3) + 3H2 (40) 4S3 (3H2x 1C23) + 4S2A,(41)

где разряды порядка числа А поступают по входу 34-2, разряды порядка числа В - по входу 34-1.

Сумматор 11 вычитает четыре старших разряда модулей порядка вещественных ходных чисел А и В для определения того, что разность порядков больше или равна 15. ЗС24 6А х 6В + (6А + 6В) х 5А х 5В (42) 7Н4 7А + 7В(43)

8S4A 8А + 8В+(7А х 7В) (44)

5S4 5A + 5B(45)

6S4 6А + 6В (5А х 5В)(46)

7S4 7E4 3C24(47)

8S4 (7Н4 х ЗС24) + 8S4A,(48)

где разряды порядка числа А поступают по входу 35-1, разряды порядка числа В - по входу 35-2.

Сумматор 12 складывает или вычитает етыре младших разряда модулей порядков входных чисел вещественного А и целого В при условии, что циклический перенос равен нулю.

ЗН5 ЗАЦ + ЗПЦП(49)

1С23 2АЦ х 2ПЦП + (2АЦ + + 2ПЦП)х 1АЦх 1ПЦП(50)

4S5C 4АЦ + 4ПЦП + (ЗАЦ х ЗПЦП) (51) 1ПЦП(52)

255 2АЦ + 2ПЦП+(1АЦх1ПЦП) (53) 3S5 1C25 + 3H5 .(54)

4S5 (ЗН5 х 1С25) + 3S5C,(55)

где разряды АП поступают по входу 36-1, азряды ПЦП - по входу 36-2.

Сумматор 13 вычитает четыре младших азрядов модулей порядков входных чисел ещественного А и целого В при условии,

чем циклический перенос равен 1. т.е. к младшему разряду суммы прибавляется единица циклического переноса.

1Р16 1АЦ+ 1ПЦП(56)

52С16 2АЦх2ПЦП(57)

2И6 2АЦ + 2ПЦП(58)

1Р26 (1АЦ+1ПЦП)х(2ЦА + 2ПЦП) (59) 1С26 2С16+1Р26(60)

156 1АЦ + ПЦП(61)

0 2S6 1P16 + 2H6(62)

356 2С16 + (1Р16х2Н6) + ЗНП (63) 4S6 (3H5x1C26) + 4S5C,(64)

где разряды АЦ поступают во входу 37-1 i разряды П ЦП - по входу 37-2, 5 Сумматор 14 вычитает четыре старших разряда модуля порядка вещественного входного числа А из старшего разряда порядка целого входного числа В.

557 5АЦ + 5ПЦП(65)

0 6S7 (5АЦ х 5ПЦП) + 6АЦ(66)

ЗС27 6АЦх5АЦх5ПЦП(67)

757 7АЦ + ЗС27(68)

8S7 (7АЦ х ЗС27) + 8АЦ,(69)

где разряды АЦ поступают о входу 38-1, 5 разряды ПЦП - по входу 38-2.

Узел 15 обращает порядок входного числа А

+ А,(70)

где 1-8

0 Если разность порядков больше или равна 15, в коммутаторе 16 формируются сигналы БР15 1 (выход 46-1) для числа А и БР 15 П (выход 45-2) для числа В, выдвигающие числа А, В за разрядную сетку. Сигна- 5 лы БР 15Л и БР15П формируются коммутацией результатов формирователе 17-22, управляемых сигналом управления на устройства 3.

БР15П РАЗРП х (2БР15 х 2КСП + 0 +1БР15х 1КСП + ЗБР15хЗКСП +

+ 5БР15хСТР)(71)

БР15Л 4БР15х1КСП + +6БР15хЦПЦх4КСП + + ЦПЦх 1КСЛ(72)

5 где СТР формируется по формуле (18), РАЗР формируется по формуле (7), РАЗРП. 1КСП, 2КСП, ЗКСП, 4КСП,1КСЛ поступает по входу 45-1,

ЦП Ц поступает по входу 45-2,

0 1БР15 поступает по входу 45-3,

2БР15 поступает по входу 45-4,

ЗБР15 поступает по входу 45-5,

4БР15 поступает по входу 45-6.

5БР15 поступает по входу 45-7,

5 6БР15 поступает по входу 45-8.

Формирователь 17 формирует сигнал БР15, указывающий, что разность порядка больше или равна 15 при сложении модулей порядков вещественных входных чисел А и В.

2Р21(ЗА + ЗВ)х(4А + 4В)(73)

58АВ 5А + 6А + 7А + 8А + + 5В + 6В + 7В + 8В(74)

2G21 4Ах4В + (4А + 4В)хЗАхЗВ (75) 1БР15 581В + 2С21+2С21+

+ 2Р21 х 1С21(76)

где 1G21 формируется как в формуле (12)

Разряды порядка числа 1 поступают по входу 39-1, разряды порядка числа В - по входу 39-2.

Формирователь 18 формирует сигнал БР15 при вычитания модулей порядка вещественных входных чисел А и В при условии, что циклический порядок равен нулю.

2G22 - 4А х 4В + (4А + 4В) х ЗА х 3В (77) 2Р22(4А + 4В)х(ЗА + ЗВ)(78)

. 1G42 2C22x1C22(79)

2БР15 554х 1G42 + 6S4 + + 7S4 + 8S4,(80)

где 1G22 формируется как в формуле (28).

Разряды порядка числа А поступают по входу 40-2, разряды порядка числа В поступают по входу 40-3, разряды суммы S4 поступают по входу 40-1.

Формирователь 19 формирует сигнал БР15 при вычитании модулей порядков вещественных входных чисел А и В при условии, что циклический перенос равен единице.

1G43 1G23x2P22+2G22(81)

35P15 (5S4 + 6S4 + +8S4)x1G43x5S4x6S4x х 7S4x8S4x1G43(82)

где 1G23 формируется как в формуле (37), 2G22 формируется как в формуле (77), 2Р22 формируется как в формуле (78). Разряды порядка числа А поступают по входу 41-2,

разряды порядка числа В - по входу 41-3,

разряды суммы S4 - по входу 41-1. Формирователь 20 формирует сигнал БР.1& при сложении модулей порядка входного вещественного числа А и входного целого числа В.

58АЦ 5АЦ + 6АЦ + 7АЦ + 8АЦ + 5ПЦП

.(83)

2Р2 (4ЦА + 4ПЦП) х (ЗАЦ + ЗПЦП) (84) 2G25 4АЦ х 4ПЦП + (4АЦ + + 4ПЦП)х ЗАЦ х ЗПЦП(85)

4БР15 2Р2х 1С25 + 2С25 + 58АЦ (86) где 1С25 формируется как в формуле (50). Разряды АЦ поступают по входу 42-2, разряды Г)ЦП - по входу 42-1. Формирователь 21 формирует, сигнал БР15 при вычитании модуля порядка вход- нрго вещественного числа А из целого числа В прм условии, что циклический перенос равен нулю.

. 1G45 2G25 + 1G25 х 2Р2(87)

5БР15 5S7 х 1G45 + 6S7 +

+ 7S7 + 8S7,(88)

где 2G25 вычисляется по формуле (85),

1G25 вычисляется по формуле (50), 2Р2 вычисляется по формуле (84).

Разряды АЦ поступают по входу 43-1,

разряды ПЦ поступают по входу 43-2,

разряды суммы S7 поступают о входу . 43-3.

0 Формирователь 22 формирует сигнал БР15 при вычитании модуля порядка входного вещественного числа А из целого числа В при условии, что циклический перенос равен единице. 51G46 2G25 + 2P2x 1G26(89)

65P15-(5S7 + 6S7 + 7S7 +

+ 8S7)x 1G46 + 5S7x6S7x

x 7S7x8S7x1G46(90)

где 2G25 формируется как в формуле (85), 0 2Р2 формируется как в формуле (84),

1G26 формируется как в формуле (60).

Разряды АЦ поступают по входу 44-2.

разряды ПЦП поступают по входу 44-3,

разряды суммы S7 поступают по входу 5 44-1.

Сумматор порядков чисел состоит из двух базовых узлов 1-1 и 1-2, только в один узел 1-1 по входу 23-5 подается ПЦП, а в другой узел 1-2 по входу 23-6 (аналогично 0 расположенному в базовом узле) подается ПЦЛ.

Выходы 24-3 БР15Л, 24-4, БР15П, 24-5 СДЛ, 24-6 СЛП соответственно двух базовых узлов соединены в инверсной фазе про- 5 водным и, как показано на фиг.1.

Сумматор порядков чисел предназначен для вычисления модуля разности порядков и формирования кода сдвига числа и полученной разности в случае, когда хотя 0 бы один из входных операндов вещественный.

Сумматор порядков чисел формирует виды сдвига операндов для выравнивания порядков перед сложением мантисс опе- 5 рандов.

В базовых узлах 1-1, 1-2 виды сдвига чисел В 8СДП, 4СЛП, 2СЛП, 1СЛП и коды сдвига числа А 8СДЛ, 4СДЛ, 2СДЛ, 1СДЛ формируются непосредственно из модуля 0 разности порядков, при условии, когда два входных числа вещественные, либо одно из чисел целое. При этом в узел 1-1 по входу 23-5 подается целое число В, а в узел 1-2 по входу 23-6 - целое число А. 5 Устройство 3 управления управляет коммутатором 8 сдвига чисел и коммутатором 16 сигналов (БР15), означающим, что разность порядков больше или равна 15 (может быть использован для расширения функциональных возможностей).

I Коммутатор 8 формирует сигналы сдвига чисел А и В коммутацией сумм суммато- F.OB 7, 9, 10, 12, 13 посредством сигналов, Нормируемых в устройстве 3 управления.

Коммутатор 16 формирует сигнал (Б Р15) для левого и правого чисел коммутаций ре- гультатов, формируемых в узлах 17-22, по- средством сигналов формируемых в устройстве 3 управления.

Во входном сумматоре 20 порядков нет коммутатора сборок нулей и коммутатором порядка целого и вещественного чисел. Та- i им образом, порядок целого числа поступает непосредственно на сумматоры, иычисляющие модуль разности порядков. Нет шифратора, получающего сдвиг числа из модуля разности порядков. Таким обра- ном, сдвиги чисел получаются непйсредст- оен-но с коммутатора сдвигов. Это позволяет ускорить работу как сумматора, ак и всего устройства сложения в целом.

Все входящие в устройство сложения узлы, синхронизированы единой системой синхронизации.

Формул а изобретения

Сумматор порядков чисел, содержа- ций базовый узел, включающий в себя формирователь сигнала обращения числа, устройство управления, формирователь циклического переноса, формирователь :игнала разрешения сдвига числа, два сум- иатора, два коммутатора, две управляющие зходные шины, три информационные входные шины, три выходные шины, первая управляющая входная шина соединена с правляющим входом формирователя сигнала обращения числа, к первому и второму нформационным входам которого, перво- у и второму информационным входам уст- ойства управления подключены оответственио вторая и первая информационные входные шины, вторая управляющая шина соединена с управляющими входами устройства управления и формирователя сигнала разрешения сдвига числа, к первому и второму информационным входам которого подключены соответственно вторая и третья информационные входные шины, выход формирователя сигнала разрешения сдвига числа соединен с третьим информационным входом устройства управления, выход которого подключен к управляющему входу первого коммутатора и первому управляющему входу второго коммутатора, первый информационный вход первого коммутатора соединен с выходом первого сумматора, выход второго сумматора подключен к первому входу формирователя циклического переноса, выход которого соединен с четвертым информационным входом устройства управления, выход формирователя сигнала обращения числа соединен с первой выходной шиной, отличающийся тем, что, с целью повышения быстродействия за счет сокращения логических уровней, введены второй базовый узел, дополнительная информационная входная шина, три дополнительные выходные шины, а в каждый базовый узел

0 включены дополнительный формирователь циклического переноса, пять дополнительных сумматоров, узел обращения порядка числа, шесть формирователей информационного сигнала, причем в первом базовом

5 узле первая информационная входная шина соединена с первым информационным входом второго сумматора, с вторыми информационными входами основного первого и второго дополнительных сумматоров, пер0 вого коммутатора и входом узла обращения порядка числа, выход которого подключен к второму информационному входу дополнительного формирователя циклического переноса, к первым информационным входам

5 третьего, четвертого и пятого дополнительных сумматоров пятого формирователя информационного сигнала и к вторым информационным входам четвертого и шестого формирователей информационного

0 сигнала, вторая информационная входная шина подключена к первым входам первого основного, первого и второго дополнительных сумматоров и к второму входу второго сумматора, третья информационная вход5 ная шина соединена с первым информационным входом дополнительного формирователя циклического переноса, с вторыми информационными входами третьего, четвертого и пятого дополнительных

0 сумматоров и пятого формирователя информационного сигнала, с первым входом четвертого и с третьим входом шестого формирователей информационного сигнала, во втором базовом узле первая управля5 ющая входная шина соединена с управляющим входом формирователя сигнала обращения числа, к первому и второму информационным входам которого, первому и второму информационным входам уст0 ройства управления подключены соответственно первая и вторая информационные входные шины, вторая управляющая входная шина соединена с . управляющими входами устройства управ5 ления и формирователя сигнала разрешения сдвига числа, к первому и второму информационным входам которого подключены соответственно первая и дополнительная информационные входные шины, выход формирователя сигнала разрешения сдвига

числа соединен с третьим информационным входом устройства управления, выход которого подключен к управляющему входу первого коммутатора и к первому управ- л я ю идем у входу второго коммутатора, первый информационный вход первого коммутатора соединен с выходом первого сум- мэтора, выход второго сумматора подключен к первому входу формирователя циклического переноса, выход которого соединен с четвертым информационным входом устройства управления, вторая информационная входная шина соединена с первым информационным входом второго сумматора, с вторыми информационными входами первого основного, первого и второго дополнительных сумматоров, первого Коммутатора и входом узла обращения порядка числа, выход которого подключен к второму информационному входу дополнительного формирователя циклического переноса, к первым информационным входам третьего, четвертого и пятого дополнительных сумматоров, пятого формирователя ин- формационного сигнала и к вторым информационным входам четвертого и шестого формирователей информационного сигнала, первая информационная входная шина подключена к первым входам первого основного, первого и второго дополнительных сумматоров и к второму входу второго сумматора, дополнительная информационная входная шина соединена с вторым информационным входом формирователя сигнала разрешения сдвига числа,- с первым информационным входом дополнительного формирователя циклического переноса, с вторыми информационными входами третьего, четвертого и пятого дополнительных сумматоров и пятого формирователя информационного сигнала с первым входом четвертого и с третьим входом шестого формирователей информационного сигнала, оыход формирователя сигнала обращения числа соединен с первой дополнительной выходной шиной, при этом в каждом базовом узле выход первого дополнительного сумматора подключен к второму информационному входу формирователя циклического переноса и третьему

информационному входу первого коммутатора, четвертый информационный вход которого соединен с выходом второго дополнительного сумматора, выход второго сумматора подключен к первым информационным входам второго и третьего формирователей информационного сигнала, выход третьего дополнительного сумматора соединен с четвертым информационным входом дополнительного формирователя

циклического переноса и с пятым информационным входом первого коммутатора, шестой информационный вход которого подключен к выходу четвертого дополни тельного сумматора, выход пятого дополнительного сумматора соединен с третьими информационными входами дополнительного формирователя циклического переноса и пятого формирователя информационного сигнала и с первым информационным входом шестого формирователя информационного сигнала, выходы всех формирователей информационных сигналов соединены с соответствующими информационными входами второго

коммутатора, первый вход первого коммутатора, первый вход первого коммутатора первого базового узла и второй выход первого коммутатора второго базового узла соединены с второй выходной шиной, второй

выход первого коммутатора первого базового узла и первый выход первого коммутатора второго базового узла соединены с второй дополнительной выходной шиной, первый выход второго коммутатора первого базового узла и второй выход второго коммутатора второго базового узла соединены с третьей выходной шиной, второй выход второго коммутатора первого базового узла и первый выход второго коммутатора

второго базового узла соединены с третьей дополнительной выходной шиной.

N

s

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения (I) | 1989 |

|

SU1837281A1 |

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| Устройство для побитовой обработки чисел,представленных в форме с плавающей запятой | 1980 |

|

SU938284A1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ И ОКРУГЛЕНИЯ ВЕЩЕСТВЕННЫХ ЧИСЕЛ | 1992 |

|

RU2018921C1 |

| Генератор псевдослучайных узкополосных сигналов | 1980 |

|

SU940157A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств высокой производительности. Цель изобретения - повышение быстродействия. Сумматор порядков состоит из двух базовых узлов, каждый из которых содержит формирователь сигнала обращения тела, устройство управления, формирователь циклического переноса, формирователь сигнала разрешения сдвига числа, дополнительный формироват ь циклического переноса, два сумматора, два коммутатора, пять дополнительных сумматоров, узел обращения порядка числа, шесть формирователей информационного сигнала, 2 ил. |с/ t

гъит

; ; . Ј #.#

23-1

&l

JЈ-t

tf-4

ЈT-J

фиг1,$

| Процессор | |||

| Техническое описание MB К Эльбрус-Б | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Процессор центральный | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

Авторы

Даты

1993-08-30—Публикация

1989-12-29—Подача