Изобретение относится к вычислительной технике и может быть использовано при построении легкотестируемых устройств.

Цель изобретения - упрощение дешифратора.

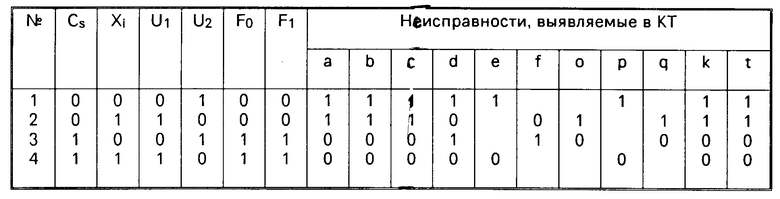

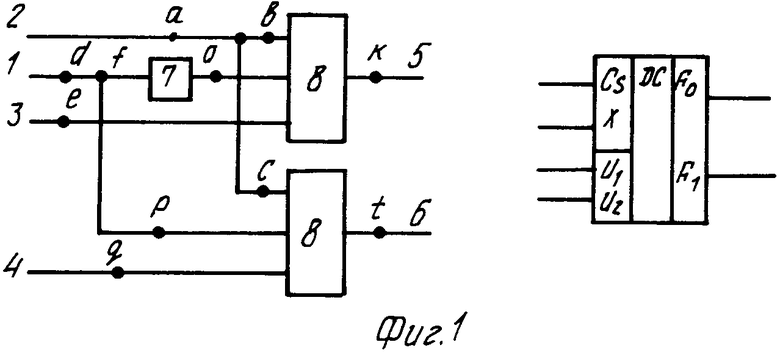

На фиг. 1 приведена функциональная схема узла дешифрации с разрядностью информационного входа; на фиг. 2 - функциональная схема пирамидального дешифратора с разрядностью информационного входа и числом уровней К = 3.

Узел дешифрации (фиг. 1) содержит информационный вход Х - 1, вход Сs - 2 выборки, первый и второй входы U1, U2 - 3, 4 управления узлом дешифрации , выходы Fo, F1 - 5, 6, инвертор 7, первый и второй элементы 8 и 9 МАЖОРИТАРНОСТЬ.

Пирамидальный дешифратор (фиг. 2) содержит три уровня узлов 10 дешифрации и 23 выходов 11.

Пирамидальный дешифратор имеет два режима работы - основной и тестовый.

В основном режиме на входы U1, U2 - 3, 4 управления подается комбинация 0, 0. При этом каждый узел дешифрации реализует функции

Fo = C ; F1 = CsX, а все устройство выполняет функцию полного дешифратора. На информационный вход (разряды Х1-Х3) в основном режиме подается дешифрируемое слово.

; F1 = CsX, а все устройство выполняет функцию полного дешифратора. На информационный вход (разряды Х1-Х3) в основном режиме подается дешифрируемое слово.

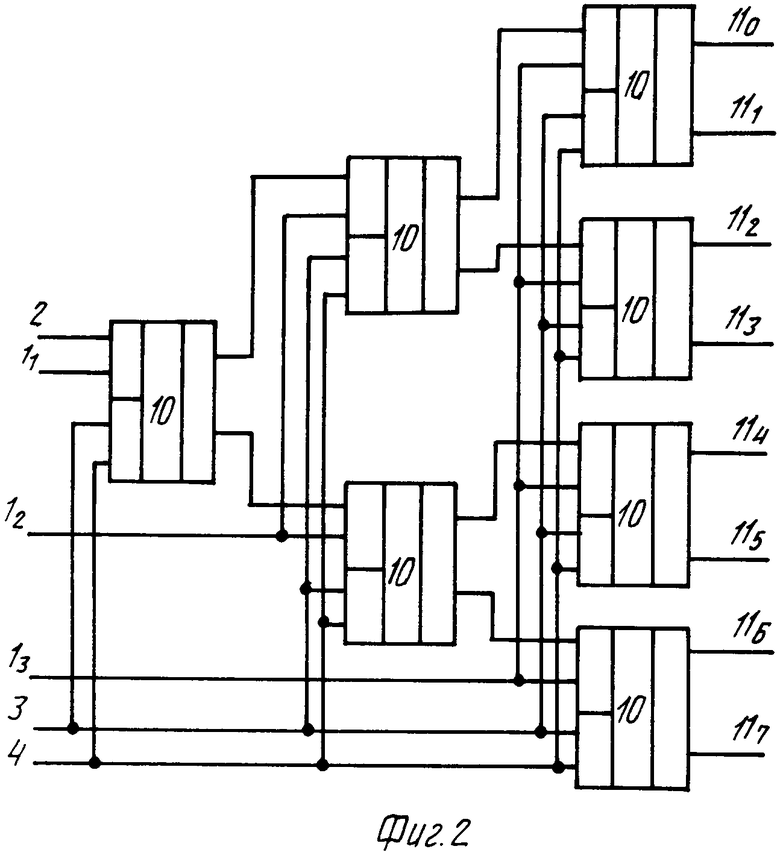

В тестовом режиме на информационные входы Х1 дешифратора подаются всего две комбинации: все нули или все единицы. На входы U1, U2управления пирамидальным дешифратором подается тест, состоящий из четырех комбинаций и являющийся полным в классе одиночных константных неисправностей. Проверяющий тест и доказательство его полноты приведены в таблице. Четыре тестовых набора выявляют константные неисправности во всех одиннадцати контрольных точках (КТ) узла дешифрации. При этом путь, включающий вход Сs, в каждом тестовом наборе является активизированным, а последовательность сигналов Cs совпадает с Fo и F1.

Сделанные замечания позволяют утверждать, что слайсевый пирамидальный дешифратор, схема которого для случая К = 3 приведена на фиг. 2, имеет стандартный тест (см. таблицу).

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛИНЕЙНЫЙ ДЕШИФРАТОР | 1991 |

|

RU2032937C1 |

| Пирамидальный дешифратор | 1989 |

|

SU1727123A1 |

| УСТРОЙСТВО ДИНАМИЧЕСКОГО ИЗМЕНЕНИЯ АДРЕСОВ ПАМЯТИ | 1993 |

|

RU2115160C1 |

| ПАРАЛЛЕЛЬНЫЙ ДЕШИФРАТОР УПРАВЛЯЕМОЙ ТРАНСПОЗИЦИИ ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2008 |

|

RU2390049C1 |

| ДЕШИФРАТОР УПРАВЛЯЕМОЙ ПОБИТОВОЙ ТРАНСПОЗИЦИИ ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2007 |

|

RU2320000C1 |

| Устройство для дешифрации команд | 1987 |

|

SU1532932A1 |

| Резервированное устройство для управления электропневмоклапанами | 1989 |

|

SU1647512A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1305687A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Устройство для контроля логических узлов | 1981 |

|

SU1024924A1 |

Изобретение относится к вычислительной технике. Цель изобретения - упрощение устройства. Цель достигается тем, что пирамидальный дешифратов имеет два входа управления, соединенные с первыми и вторыми входами управления всех узлов дешифрации, а каждый узел дешифрации содержит два элемента МАЖОРИТАРНОСТЬ и инвертор, причем вход выборки соединен с первыми входами первого и второго элементов МАЖОРИТАРНОСТЬ, информационный вход соединен с инвертором и вторым входом второго элемента МАЖОРИТАРНОСТЬ, первый и второй входы управления соединены с третьими входами первого и второго элементов МАЖОРИТАРНОСТЬ соответственно. 1 табл., 2 ил.

ПИРАМИДАЛЬНЫЙ ДЕШИФРАТОР, содержащий K уровней дешифрации (K - разрядность информационного входа дешифратора), причем j-й разряд информационного входа дешифратора подключен к информационным входам узлов дешифрации j-го уровня (j =  ), каждый выход узла дешифрации j-го уровня подключен к входу выборки узла дешифрации (j+1)-го уровня, первый и второй входы управления дешифратора подключены соответственно к первым и вторым входам управления всех узлов дешифрации, каждый узел дешифрации содержит два элемента МАЖОРИТАРНОСТЬ, отличающийся тем, что, с целью упрощения дешифратора, каждый узел дешифрации содержит инвертор, причем вход выборки узла дешифрации соединен с первыми входами первого и второго элементов мажоритарность, информационный вход узла дешифрации соединен с вторым входом второго элемента мажоритарность и входом инвертора, выход которого соединен с вторым входом первого элемента МАЖОРИТАРНОСТЬ, первый и второй входы управления узла дешифрации соединены с третьими входами первого и второго элементов МАЖОРИТАРНОСТЬ соответственно, первый и второй выходы узла дешифрации - с выходами первого и второго элементов МАЖОРИТАРНОСТЬ соответственно.

), каждый выход узла дешифрации j-го уровня подключен к входу выборки узла дешифрации (j+1)-го уровня, первый и второй входы управления дешифратора подключены соответственно к первым и вторым входам управления всех узлов дешифрации, каждый узел дешифрации содержит два элемента МАЖОРИТАРНОСТЬ, отличающийся тем, что, с целью упрощения дешифратора, каждый узел дешифрации содержит инвертор, причем вход выборки узла дешифрации соединен с первыми входами первого и второго элементов мажоритарность, информационный вход узла дешифрации соединен с вторым входом второго элемента мажоритарность и входом инвертора, выход которого соединен с вторым входом первого элемента МАЖОРИТАРНОСТЬ, первый и второй входы управления узла дешифрации соединены с третьими входами первого и второго элементов МАЖОРИТАРНОСТЬ соответственно, первый и второй выходы узла дешифрации - с выходами первого и второго элементов МАЖОРИТАРНОСТЬ соответственно.

| Заявка N 4755027/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-07-30—Публикация

1991-06-04—Подача