Изобретение относится к вычислительной технике и может быть использовано для построения надежных цифровых устройств.

Известна программируемая логическая матрица на инверторах интегрально-инжекционной логики [1], имеющая программируемые логические связи между инверторами, а также между инверторами и внешними полюсами матрицы.

Прототипом предлагаемого решения является разновидность указанной матрицы, ориентированная на реализацию системы функций И-ИЛИ. Для этого инверторы прототипа разбиты на две группы и в пределах одной группы не имеют логических связей друг с другом.

Недостаток прототипа - низкая надежность ввиду возникновения перемежающихся отказов при пробоях p-n-переходов.

Так, если в прототипе некоторый инвертор Х соединен выходом (в качестве которого используется некоторый коллектор Y транзистора инвертора Х) с входом некоторого инвертора Z, то пробой перехода база-коллектор Y транзистора инвертора Х приведет к тому, что переходы база-эмиттер транзисторов инверторов Х и Z окажутся включенными параллельно, хотя это запрещено в рамках схемотехники интегрально-инжекционных схем.

В результате инвертор Х будет работать неустойчиво, генерируя перемежающийся отказ.

Цель изобретения - повышение надежности программируемой логической матрицы за счет уменьшения числа возможных перемежающихся отказов.

Для достижения цели в программируемой логической матрице, содержащей два накопителя и две группы инверторов, каждый инвертор содержит транзистор и источник тока, причем анод источника тока соединен с входом инвертора, катод источника тока соединен с эмиттером транзистора, а коллекторы транзистора являются выходами инвертора, в каждом инверторе первой группы анод источника тока соединен с базой транзистора, вход каждого инвертора первой группы соединен с отдельной разрядной шиной первой группы разрядных шин первого накопителя, каждый выход каждого инвертора первой группы соединен с отдельной адресной шиной второго накопителя, вход каждого инвертора второй группы соединен с отдельной разрядной шиной второго накопителя, каждый выход каждого инвертора второй группы соединен с отдельной адресной шиной первой группы адресных шин первого накопителя, входами матрицы является вторая группа адресных шин первого накопителя, выходами матрицы является вторая группа разрядных шин первого накопителя, эмиттеры транзисторов инверторов первой группы соединены с первой шиной питания матрицы, в каждый инвертор второй группы введен источник напряжения, включенный между анодом источника тока и базой транзистора, а эмиттеры транзисторов инверторов второй группы соединены с второй шиной питания матрицы.

Признаками, отличающими предлагаемое решение от прототипа, являются следующие: вторая шина питания матрицы, с которой соединены эмиттеры транзисторов инверторов второй группы, и источник напряжения в каждом инверторе второй группы, включенный между анодом источника тока и базой транзистора.

Хотя эти признаки по отдельности и встречаются в известных решениях, но в той совокупности признаков, которая характеризует предлагаемое решение, они встречаются впервые, обеспечивая появление у предлагаемого решения нового свойства, отсутствующего у известных решений, а именно: если в известных программируемых логических матрицах вероятные катастрофические отказы электронных приборов вызывают как перемежающиеся, так и константные отказы внутренних инверторов, то в предлагаемой матрице - только константные.

(Под электронными приборами понимаются диоды, транзисторы, резисторы, источники тока и источники напряжения; под вероятными катастрофическими отказами понимаются пробой между полюсами электронного прибора, пробой полюса на шину питания и обрыв полюса, возможные с учетом топологии программируемой логической матрицы; внутренними считаются инверторы, не имеющие логических связей с входами и выходами программируемой логической матрицы).

Это свидетельствует о соответствии предлагаемого решения критерию "существенные отличия".

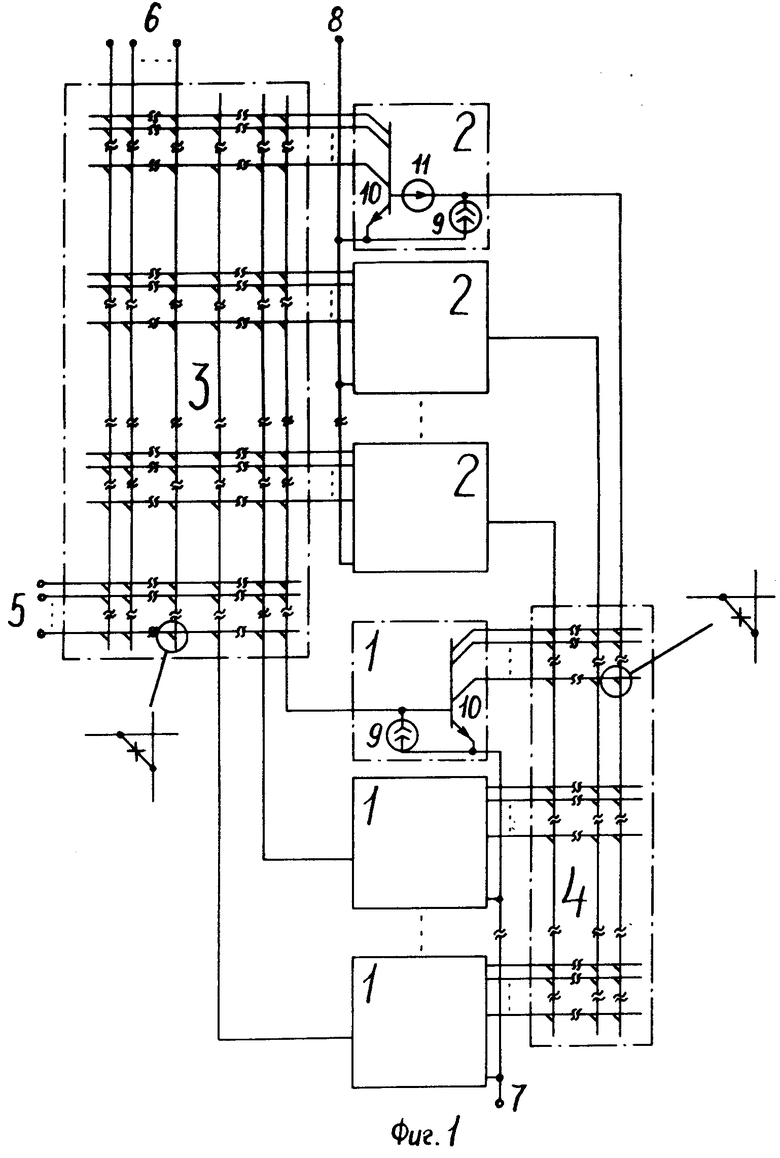

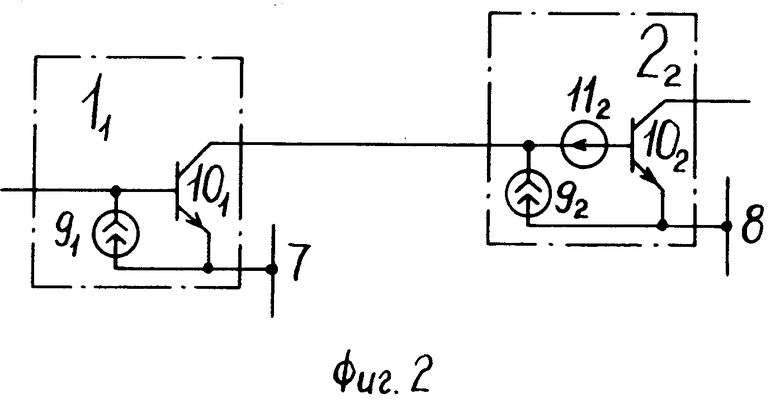

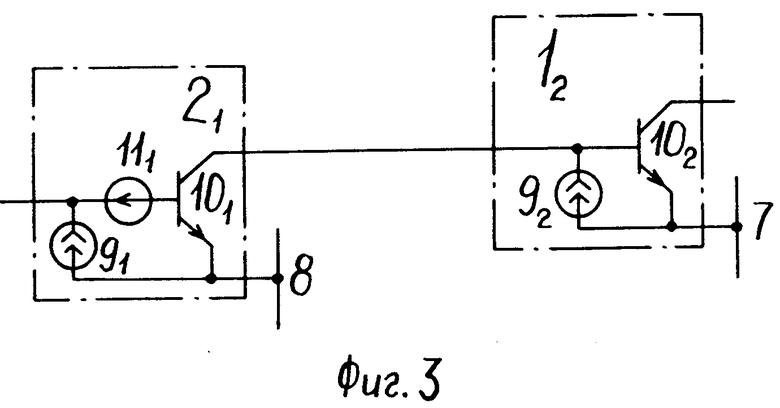

На фиг.1 приведена электрическая схема предлагаемой матрицы; на фиг.2 и 3 приведены электрические схемы элементарных двухинверторных цепочек, возможных в предлагаемой матрице (на фиг.2 или 3 цифровые обозначения первого инвертора цепочки, а также его элементов снабжены индексом 1, а цифровые обозначения второго инвертора цепочки, а также его элементов - индексом 2).

Предлагаемая программируемая логическая матрица выполняется в виде интегральной схемы и содержит (фиг.1) первую 1 и вторую 2 группы инверторов, а также первый 3 и второй 4 накопители. Кроме того, она имеет входы 5, выходы 6, первую 7 и вторую 8 шины питания.

Каждый инвертор 1 или 2 содержит источник 9 тока, транзистор 10. Каждый инвертор 2 содержит, помимо этого, источник 11 напряжения.

Накопитель 3, как и накопитель 4, содержит не связанные между собой адресные шины и не связанные между собой разрядные шины, причем каждая адресная шина соединена с каждой разрядной шиной через перемычку, которая может быть при желании разорвана в точке, показанной на фиг.1 крестиком.

Эмиттеры транзисторов инверторов группы 1 и шина 7 не просто соединены, но выполнены в виде единой n+-области кристалла. Аналогично этому эмиттеры транзисторов инверторов группы 2 и шина 8 не просто соединены, но выполнены в виде единой n+-области кристалла.

Источник 11 может быть выполнен в виде диода, стабилитрона, а также цепочки из диодов и/или стабилитронов.

Программирование предлагаемой матрицы заключается в выборочном разрыве перемычек накопителей 3 и 4 таким образом, чтобы в каждом из этих накопителей каждая адресная шина осталась соединенной не более чем с одной неразорванной перемычкой. За счет этого предлагаемая матрица настраивается на реализацию произвольной системы функций И-ИЛИ, задающей конечный или комбинационный автомат.

Запрограммированная матрица работает следующим образом.

Каждый источник 9 генерирует ток I, каждый источник 11 генерирует напряжение е. На шину 7 подается нулевой потенциал, а на шину 8 - потенциал Е, причем соблюдаются неравенства

Uкэ < E + e + U*, (1)

E + Uкэ < U*, (2)

E + U* ≠ U* (3)

E + U* ≠ 0, (4) где Uкэ - напряжение между коллектором и эмиттером транзистора 10 при протекании через переход база-эмиттер транзистора тока I; U* - напряжение на открытом переходе база-эмиттер транзистора 10.

В случае исправности предлагаемой матрицы неравенства (1) и (2) обеспечивают согласование логических уровней инверторов 1 и 2, с тем чтобы (см. фиг.2 и фиг.3):

при протекании тока I, генерируемого источником 91, через переход база-эмиттер транзистора 101 транзистор 101 отпирался, ток I, генерируемый источником 92, стекал через коллектор и эмиттер транзистора 101 на шину 7 (фиг. 2) или 8 (фиг.3), в связи с чем транзистор 102запирался; при запертом транзисторе 101 ток I, генерируемый источником 92, стекал через переход база-эмиттер транзистора 102 на шину 8 (фиг.2) или 7 (фиг.3), в связи с чем транзистор 102 отпирался.

Что касается случая неисправности матрицы, то для любого внутреннего инвертора 1 или 2 вероятны следующие катастрофические отказы электронных приборов: обрывы полюсов источника 9; обpывы полюсов источника 11 (для инверторов 2); обрывы одного или нескольких коллекторов и/или базы транзистора 10 (тогда как обрыв эмиттера исключен ввиду того, что эмиттер совмещен с шиной 7 питания (для инверторов 1) или 8 (для инверторов 2)); пробой между полюсами электронных приборов, а также между полюсами электронных приборов и любой шиной питания матрицы.

Указанные катастрофические отказы приводят к генерации инвертором 11 (фиг.2) или 21 (фиг.3) перемежающегося отказа только в случае непредсказуемого распределения тока I, генерируемого источником 92 между такими p-n-переходами, как база-эмиттер транзистора 101 и база-эмиттер транзистора 102. Но неравенства (3) и (4) исключают этот случай, поскольку благодаря им при пробоях источника 112 (фиг.2) и/или перехода база-эмиттер транзистора 101 ток I, генерируемый источником 92, течет или через переход база-эмиттер транзистора 101, или через переход база-эмиттер транзистора 102.

Таким образом, во внутренних инверторах предлагаемой матрицы вероятные катастрофические отказы электронных приборов способны вызвать только константные отказы.

В связи с этим предлагаемая схема имеет меньшее множество возможных отказов, чем прототип, то есть характеризуется большей надежностью.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Усилитель считывания для программируемого постоянного запоминающего устройства | 1976 |

|

SU780033A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Матричный накопитель для интегральных запоминающих устройств | 1977 |

|

SU710075A1 |

| Формирователь сигнала выборки шины матрицы накопителя | 1981 |

|

SU1027824A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения надежных цифровых усройств. Целью изобретения является повышение надежности матрицы. Программируемая логическая матрица содержит первую и вторую группы инверторов, а также первый и второй накопители, входы, выходы, первую и вторую шины питания. Каждый инвертор содержит источник тока и транзистор. Каждый инвертор содержит, помимо этого, источник напряжения. 3 ил.

ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ МАТРИЦА, содержащая два накопителя и две группы инверторов, каждый инвертор первой и второй группы состоит из транзистора и источника тока, анод которого является входом инвертора, а коллекторы транзистора являются выходами инвертора, анод источника тока каждого инвертора первой группы подключен к соответствующей разрядной шине первой группы первого накопителя и к базе транзистора, эмиттер которого соединен с катодом источника тока и с первой шиной питания, а коллекторы транзистора соединены с соответствующими адресными шинами второго накопителя, анод источника тока каждого инвертора второй группы подключен к соответствующей разрядной шине второго накопителя, а катод - к эмиттеру транзистора, коллектор которого соединен с соответствующими адресными шинами первой группы первого накопителя, адресные шины второй группы которого являются входами матрицы, а разрядные шины второй группы являются выходами матрицы, отличающаяся тем, что, с целью повышения надежности матрицы, каждый инвертор второй группы содержит источник напряжения, первый вывод которого соединен с анодом источника тока, а второй вывод - с базой транзистора, эмиттер которого подключен к второй шине питания.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Шагурин И.И., Петросянц К.О | |||

| Проектирование цифровых микросхем на элементах инжекционной логики | |||

| М.: Радио и связь, 1984, с.190. | |||

Авторы

Даты

1994-09-30—Публикация

1990-02-20—Подача