1 . 13

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих специализированных вычислителях.

Цель изобретения - повышение быст родействия.

Преобразователь многорядного кода содержит п+1 одноразрядных трехвхо- довьк сумматоров, входы которых соединены с шинами разрядов соответст- вующего веса первого, второго и третьего входов преобразователя, а выходы сумм и переносов - с шинами соответствующего веса первой и второй групп выходов преобразователя соответственно.

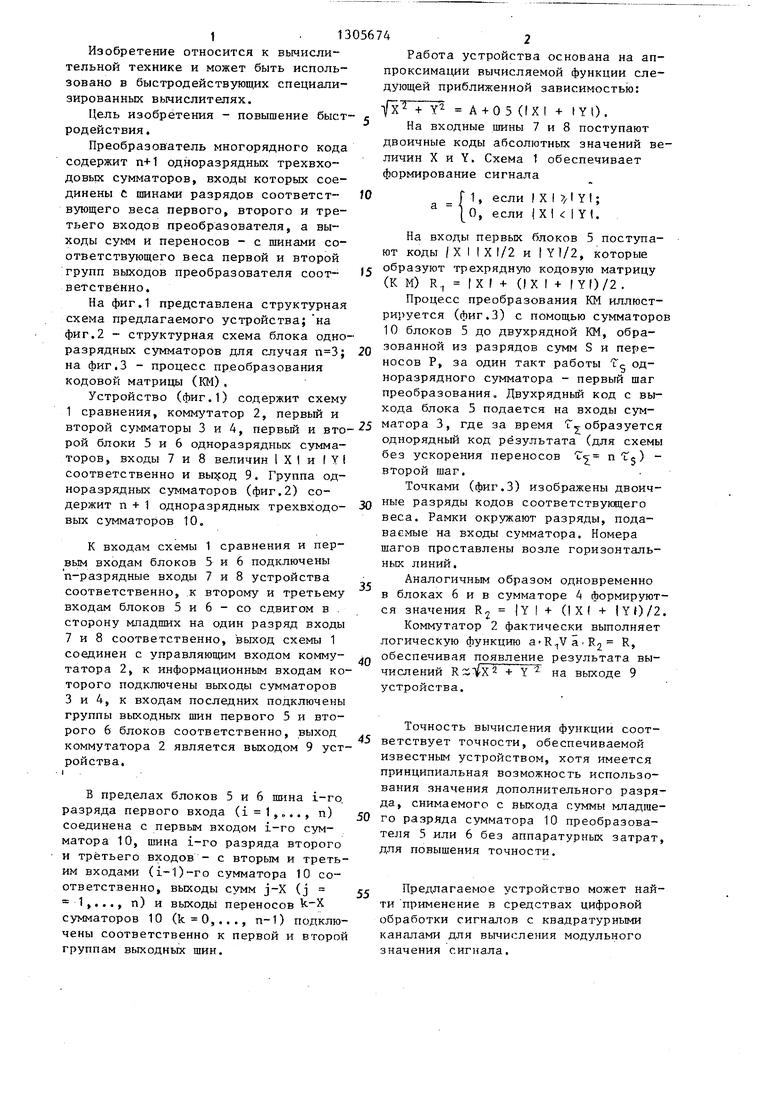

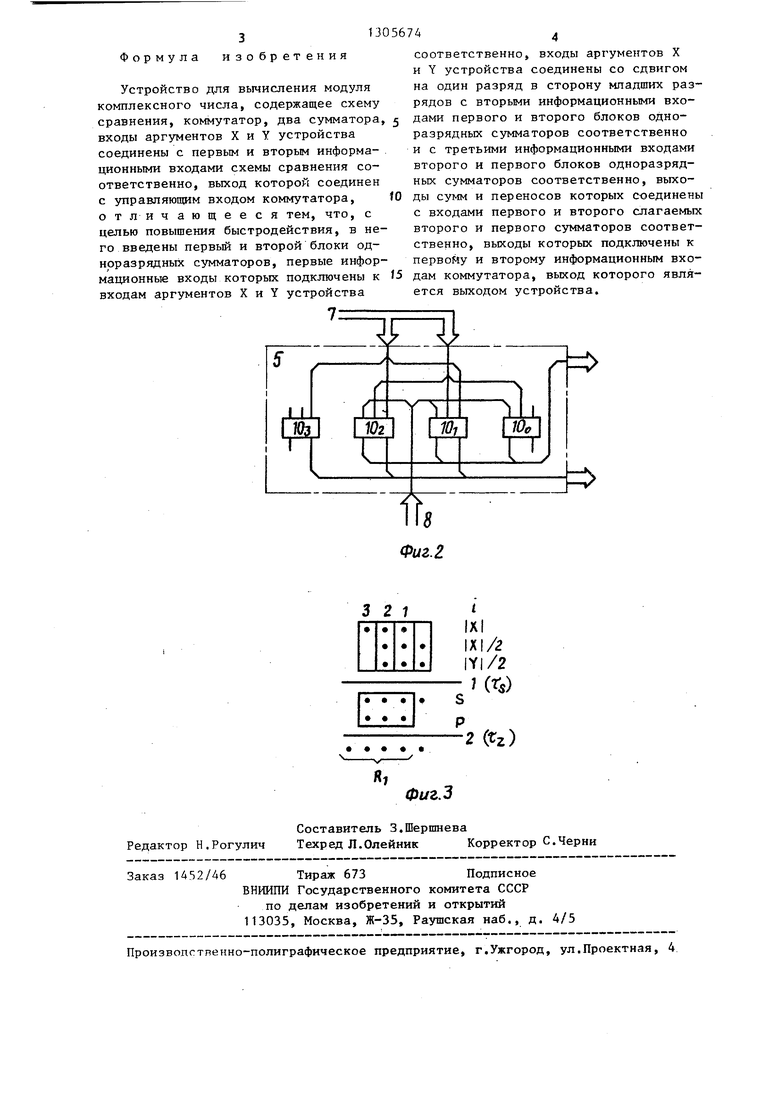

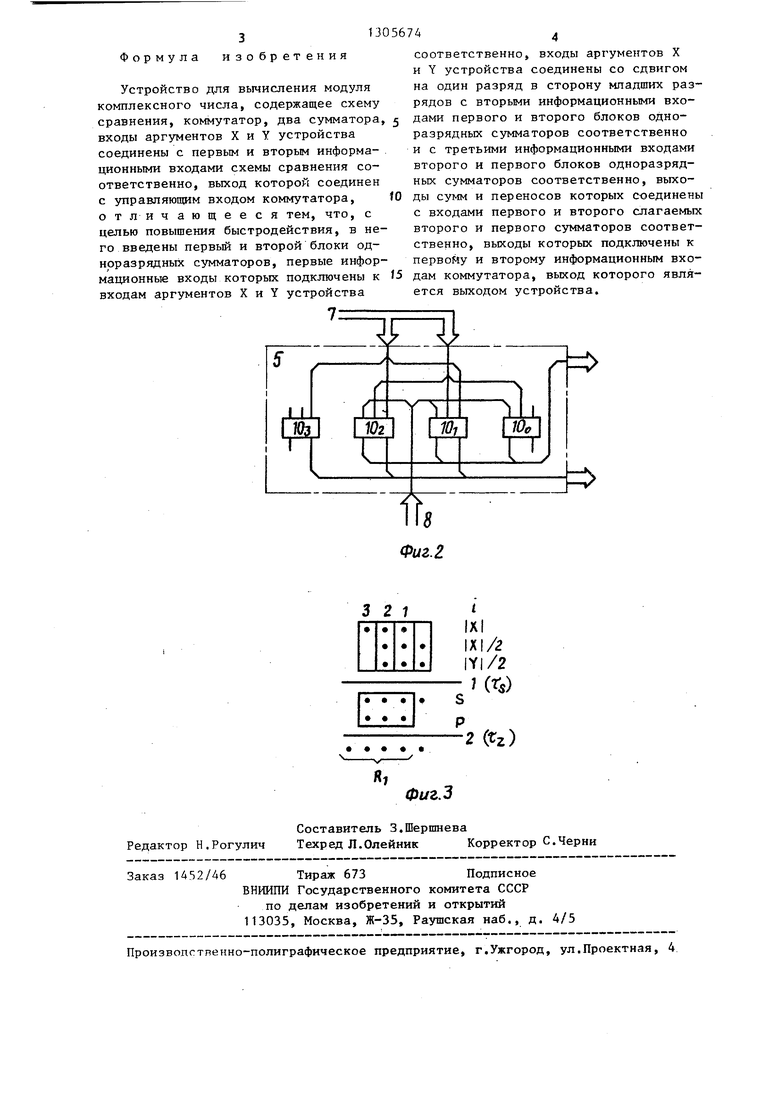

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - структурная схема блока одноразрядных сумматоров для случая на фиг.З - процесс преобразования кодовой матрицы (КМ),

Устройство (фиг.1) содержит схему 1 сравнения, коммутатор 2, первый и второй сумматоры 3 и 4, первьй и вто рой блоки 5 и 6 одноразрядных сумматоров, входы 7 и 8 величин 1X1 и f Yi соответственно и 9. Группа одноразрядных сумматоров (фиг.2) содержит п +1 одноразрядных трехвходо- вых сумматоров 10.

К входам схемы 1 сравнения и первым входам блоков 5 и 6 подключены

и 8 устройства

п-разрядные входы .к и

второму и третьему 6 - со сдвигом в .

соответственно, входам блоков 5 сторону младших на один разряд входы 7 и 8 соответственно, выход схемы 1 соединен с управляющим входом коммутатора 2, к информационным входам которого подключены выходы сумматоров 3 и 4, к входам последних подключены группы выходных шин первого 5 и второго 6 блоков соответственно, выход коммутатора 2 является выходом 9 устройства, 1

В пределах блоков 5 и 6 шина i-ro. разряда первого входа (1 1,„.., п) соединена с первым входом i-ro сумматора 10, шина i-ro разряда второго и третьего входов - с вторым и третьим входами (i-l)-ro сумматора 10 соответственно, выходы сумм J-X (J 1,..., п) и выходы переносов k-X сумматоров 10 (k Оп-1) подключены соответственно к первой и второй группам выходных шин.

Работа устройства основана на аппроксимации вычисляемой функции следующей приближенной зависимостью:

fx + Y А + 05(1Х1 + IYI).

На входные шины 7 и 8 поступают двоичные коды абсолютных значений величин X и Y, Схема 1 обеспечивает формирование сигнала

f 1, если I X I /1 Y I; О, если |Х1 I YI.

JO

20

На входы первых блоков 5 поступают коды / X И X 1/2 и I Y1/2, которые ( образуют трехрядную кодовую матрицу (К М) R I X I + (IX I + I Yf)/2 .

Процесс преобразования КМ иллюстрируется (фиг.З) с помощью сумматоров 10 блоков 5 до двухрядной КМ, образованной из разрядов сумм S и переносов Р, за один такт работы Т одноразрядного сумматора - первый шаг преобразования. Двухрядньй код с выхода блока 5 подается на входы сум- 25 матора 3, где за время Т -образуется однорядный код результата (для схемы без ускорения переносов i второй шаг.

Точками (фиг.З) изображены двоичные разряды кодов соответствующего веса. Рамки окружают разряды, подаваемые на входы сумматора. Номера шагов проставлены возле горизонтальных линий.

Аналогичным образом одновременно в блоках бив сумматоре 4 формируют30

35

ся значения Rj |Y I + ( X ( + I Y О/2. Коммутатор 2 фактически выполняет логическую функцию a R Va R2 R, обеспечивая появление результата вычислений + Y на выходе 9 устройства.

Точность вычисления функции соот- ветствует точности, обеспечиваемой известным устройством, хотя 1 меется принципиальная возможность использования значения дополнительного разряда, снимаемого с выхода суммы мпадше- го разряда сумматора 10 преобразователя 5 или 6 без аппаратурных затрат, для повышения точности.

Предлагаемое устройство может найти применение в средствах цифровой обработки сигналов с квадратурными каналами для вычисления модульного значения сигнала.

Формула изобретения

Устройство для вычисления модуля комплексного числа, содержащее схему сравнения, коммутатор, два сумматора, входы аргументов X и Y устройства соединены с первым и вторым информационными входами схемы сравнения соответственно, выход которой соединен с управляющим входом коммутатора.

отличающееся тем, что, с целью повышения быстродействия, в него введены первьй и второй блоки од- норазр5здных сумматоров, первые информационные входы которых подключены к входам аргументов X и Y устройства

-1Г

56744

соответственно, входы аргументов X и Y устройства соединены со сдвигом на один разряд в сторону младших разрядов с вторыми информационными вхос дами первого и второго блоков одноразрядных сумматоров соответственно и с третьими информационными входами второго и первого блоков одноразрядных сумматоров соответственно, выхоfO ды сумм и переносов которых соединены с входами первого и второго слагаемых второго и первого сумматоров соответственно, выходы которых подключены к первому и второму информационным вхо15 дам коммутатора, выход которого является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля вектора | 1989 |

|

SU1635182A1 |

| Вычислительное устройство | 1985 |

|

SU1262485A1 |

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

| Устройство для одновременного вычисления двух многочленов | 1987 |

|

SU1439580A1 |

| Устройство для вычисления логарифма | 1979 |

|

SU783798A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU999046A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ ВЕКТОРА | 1991 |

|

RU2022340C1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Устройство для вычисления модуля вектора | 1988 |

|

SU1541602A1 |

| Матричный вычислитель экспоненты | 1981 |

|

SU1024911A1 |

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих специализированных вычислителях. Цель изобретения - повышение быстродействия. Устройство содержит схему сравнения 1, коммутатор 2 и два сумматора 3 и 4. Новым в устройстве является использование двух блоков 5 и 6 одноразрядных сумматоров, состоящих из одноразрядных трехвходовых сумматоров. Предлагаемое устройство может найти применение в средствах цифровой обработки сигналов с квадратурными каналами для вычисления модульного значения сигнала. 2 ил. СО О СЛ О5 4 Фаг.1

Редактор Н.Рогулич

Фиг.З

Составитель З.Шершнева Техред Л.Олейник

Заказ U52/46 Тираж 673Подписное

ВНИЙГГИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Произвопстпенно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор С.Черни

| Устройство для вычисления модуля комплексного числа | 1976 |

|

SU623202A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления квадратного корня из суммы квадратов двух чисел | 1981 |

|

SU997034A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1985-12-16—Подача