8

-V

12

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях,

Цель изобретения - повышение быстродействия .

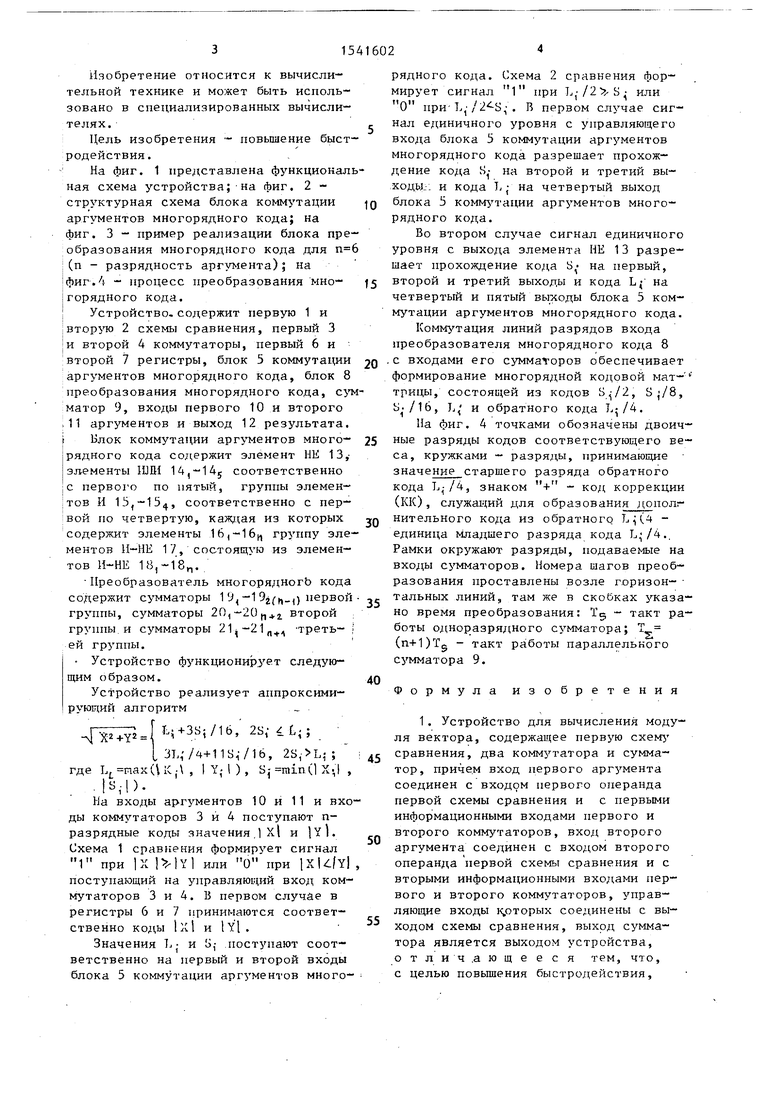

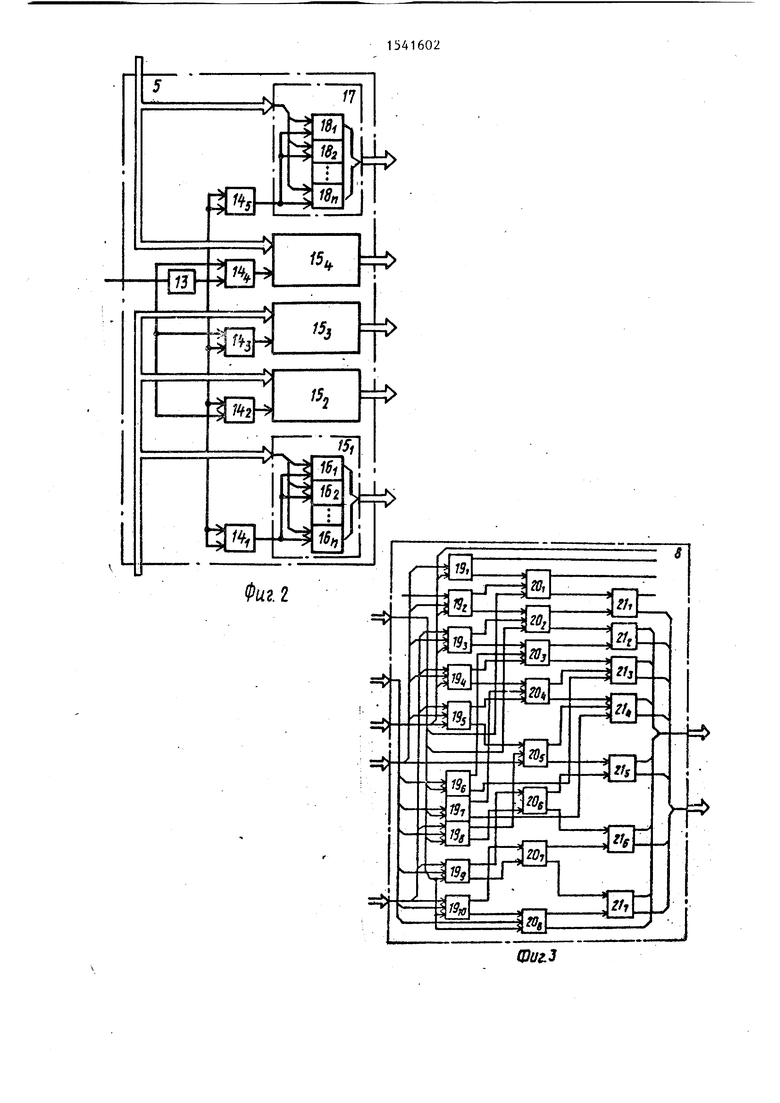

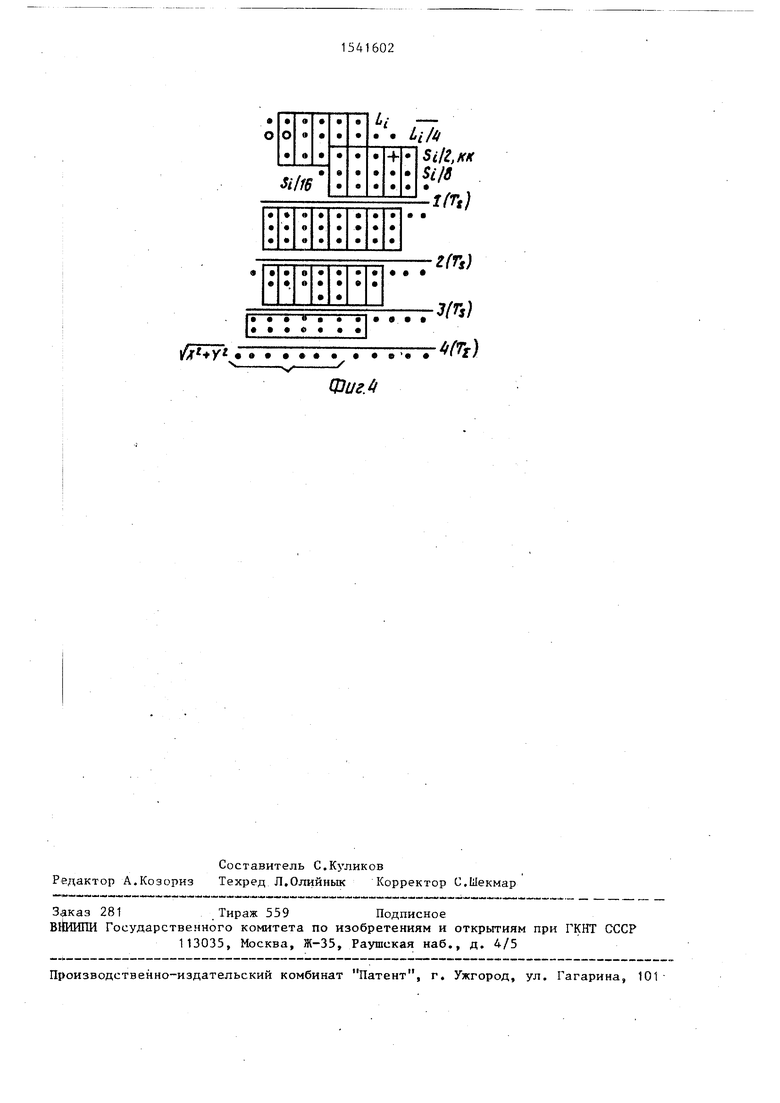

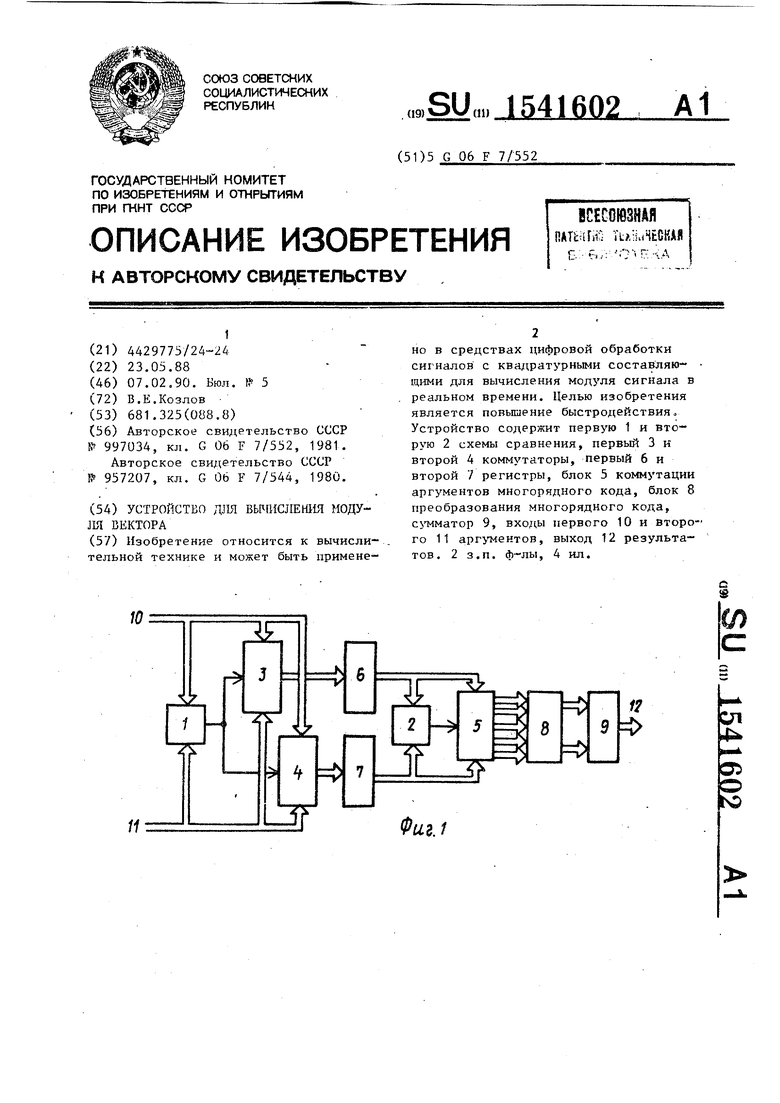

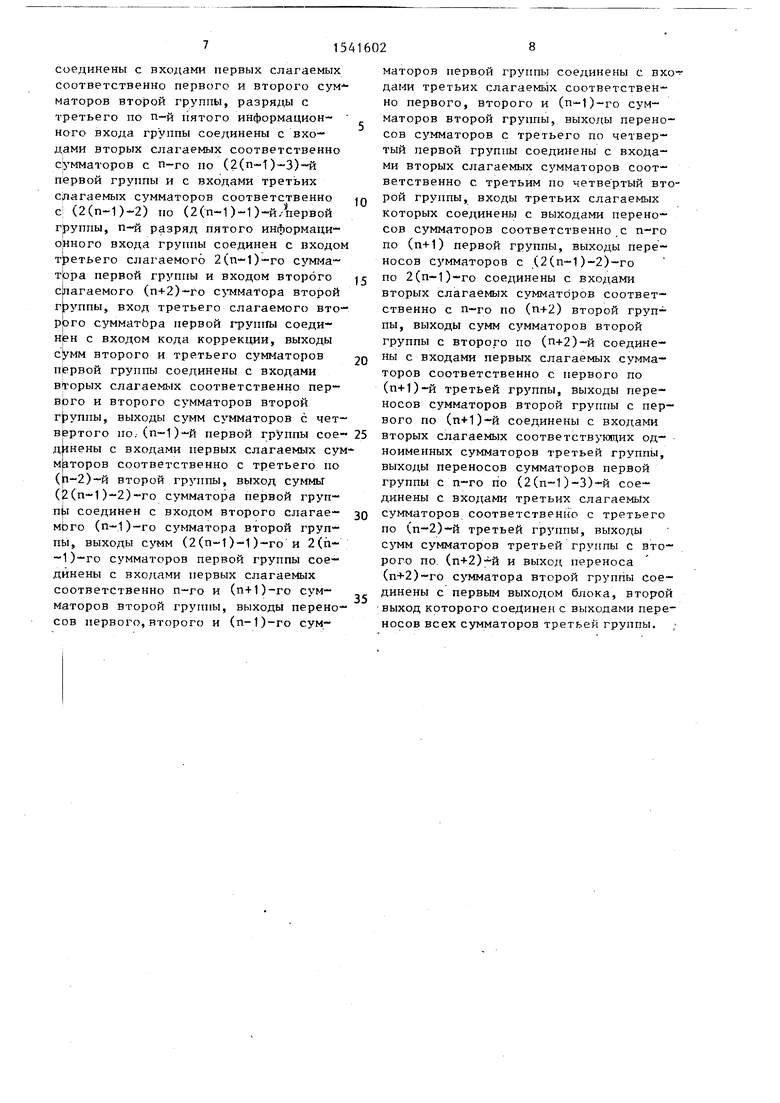

На фиг. 1 представлена функционалная схема устройства; на фиг. 2 - структурная схема блока коммутации аргументов многорядного кода; на фиг. 3 - пример реализации блока преобразования многорядного кода для п (п - разрядность аргумента); на фиг.4 - процесс преобразования мно- горядного кода.

1 Устройство, содержит первую 1 и вторую 2 схемы сравнения, первый 3 и второй 4 коммутаторы, первый 6 и второй 7 регистры, блок 5 коммутации аргументов многорядного кода, блок 8 преобразования многорядного кода, сумматор 9, входы первого 10 и второго

,11 аргументов и выход 12 результата.

i Блок коммутации аргументов много- рядного кода содержит элемент НК 13,- элементы ШШ 14,145 соответственно с первого по пятый, группы элементов И 15,-15, соответственно с первой по четвертую, каждая из которых содержит элементы 16,-16 группу элементов И-НЕ 17, состоящую из элементов И-НЕ 18,l 8n.

- Преобразователь многорядного кода содержит сумматоры 1 У4 -1 92fh,) первой группы, сумматоры 20,-20П4.г второй группы и сумматоры 21,-21niM -треть- ей группы.

Устройство функционирует следующим образом.

Устройство реализует аппроксимирующий алгоритм

4+3si/16 2S,- ;;

3L, /4+11 Si /16, 2S,L{ ; где ( 1С(Л , I Y,- 1 ) , (l X-l ,

|a,-l).

На входы аргументов 10 и 11 и входы коммутаторов 3 и 4 поступают п- разрядные коды значения I Х| и IY). Схема 1 сравнения формирует сигнал 1 при |Х или О при jXU/Yl поступающий на управляющий вход коммутаторов 3 и 4. В первом случае в регистры 6 и 7 принимаются соответственно коды 1x1 и lY l.

Значения L; и Ц,- поступают соответственно на первый и второй входы блока 5 коммутации аргументов много

5

0

5 Q

5

0

5

0

5

рядного кода. Схема 2 сравнения формирует сигнал 1 при L( или О при- Lj ,- . В первом случае сигнал единичного уровня с управляющего входа блока 5 коммутации аргументов многорядного кода разрешает прохождение кода ti- на второй и третий выходы, и кода L (- на четвертый выход блока 5 коммутации аргументов многорядного кода.

Во втором случае сигнал единичного уровня с выхода элемента НЕ 13 разрешает прохождение кода S,- на первый, второй и третий выходы и кода LJ на четвертый и пятый выходы блока 5 коммутации аргументов многорядного кода.

Коммутация линий разрядов входа преобразователя многорядного кода 8 .с входами его сумматоров обеспечивает формирование многорядной кодовой мат- трицы, состоящей из кодов , Sj/8, /16, L, и обратного кода L-/4.

На фиг. 4 точками обозначены двоичные разряды кодов соответствующего веса, кружками - разряды, принимающие значение старшего разряда обратного кода Т-1,/4, знаком + - код коррекции (КК), служащий для образования дополг нительного кода из обратного L(4 - единица младшего разряда кода L-/4.. Рамки окружают разряды, подаваемые на входы сумматоров. Номера шагов преобразования проставлены возле горизон- тальных линий, там же в скобках указано время преобразования: Т5 - такт работы одноразрядного сумматора; Т (n+1)Tg - такт работы параллельного сумматора 9.

Формула изобретения

1. Устройство для вычисления модуля вектора, содержащее первую схему сравнения, два коммутатора и сумматор, причем вход первого аргумента соединен с входом первого операнда первой схемы сравнения и с первыми информационными входами первого и второго коммутаторов, вход второго аргумента соединен с входом второго операнда первой схемы сравнения и с вторыми информационными входами первого и второго коммутаторов, управляющие входы к.оторых соединены с выходом схемы сравнения, выход сумматора является выходом устройства, отличающееся тем, что, с целью повышения быстродействия,

в него дополнительно введены блок коммутации аргументов многорядного кода, блок преобразования многорядного кода, вторая схема сравнения и два регистра, причем выходы первого и второго коммутаторов соединены с информационными входами соответственно первого и второго регистров, выход первого регистра соединен с входом первого операнда второй схемы сравнения и с первым информационным входом блока коммутации аргументов многоряд- ного кода, выход второго регистра соединен с входом второго операнда второй схемы сравнения и с вторым информационным входом блока коммутации аргументов многорядного кода, управляющий вход которого соединен с выходом второй схемы сравнения и выход группы блока коммутации аргументов многорядного кода соединен с информационными входами группы блока преобразования многорядн ого кода, первый и второй выходы которого соединены с входами перрого и второго слагаемых

сумматора.

i

2. Устройство по п. отличающееся тем, что, с целью реализации коэффициентов аппроксимации, равных (1 и 3/16) и (3/4 и 11/16), блок коммутации аргументов многорядного кода содержит четыре группы элементов И, группу элементов И-НЕ, пять элементов ИЛИ, элемент НЕ, причем разряды второго информационного входа блока соединены с первыми входами соответствующих элементов И групп с первой по третью, вторые входы элементов И групп с первой по третью объединены и соединены с выходами элементов ИШ1 соответственно, с первого но третий разряды первого информационного входа блока соединены с первыми входами соответствующих элементов И четвертой группы и с первыми входами соответствующих элементов И-НЕ группы, вторые входы элементов И четвертой группы объединены и соединены с выходом четвертого элемента ИЛИ, вторые входы элементов И-НЕ объединены и соединены с выходом четвертого элемента ШШ, вторые входы элементов И-НЕ объединены и соединены с выходом пятого элемента 11)Ш, первый и второй входы первого и пятого эле- ментов ИЛИ объединены и соединены с выходом элемента НЕ, вход которого объединен с первыми входами элементов

10

20

25

.

,,

541602

ШШ

с второго по четвертый и соединен с управляющим входом блока, вторые входы элементов ИЛИ с второго по четвертый объединены и соединены с выходом элемента НЕ, выходы элементов И групп с первой по четвертую и выходы элементов И-НЕ группы-соединены с выходами соответственно с первого по пятый группы.

3. Устройство по п. отличающееся тем, что, с целью реализации коэффициентов аппроксимации, равных (1 и 3/14) и (3/4 и 5 11/-4 6), блок преобразования многорядного кода содержит первую группу сумматоров из 2(п-1) элементов (п - разрядность аргументов), вторую группу сумматоров из (п+2) элементов и третью группу сумматоров из (п+1) элементов, причем разряды с первого по (п-З)-й первого информационного вхо да группы соединены с входами первых слагаемых сумматоров первой группы с третьего по (п-1) соответственно, (п-2)-й (п-1)-й и n-й разряды первого информационного входа группы соединены с входами первых слагаемых соответственно (2(п-1)-2)-го, (2(п-1)- -1)-го и 2(п-1)-го сумматоров первой группы, разряды с первого по (п-1)-и второго информационного входа группы соединены с входами первых слагаемых соответственно первого и второго и входами вторых слагаемых соответст- венно с третьего но (п-Т)-й сумматоров первой группы, n-й разряд второго информационного входа группы соединен с входом первого слагаемого (п-1)-го сумматора второй группы, разряды с второго по n-й третьего информационного входа группы соединены с входами вторых слагаемых соответственно первого и второго и входами третьих слагаемых соответственно с третьего по (п-1)-и сумматоров пер- ,вой группы, разряды с первого по (п-1)й четвертого информационного входа группы соединены с входами первых слагаемых сумматоров первой группы соответственно с п-го по (2(п-1)- -3),и с входами вторых слагаемых сумматоров первой группы соответственно с (2(п-1)-2)-го по (2(п-1)-1)й, п-и разряд четвертого информационного входа-группы соединен с входом первого слагаемого (п+2)-го сумматора второй группы, первый и второй разряды пятого информационного входа группы

30

40

45

50

соединены с входами первых слагаемых соответственно первого и второго маторов второй группы, разряды с третьего по n-й пятого информацией- г ного входа группы соединены с входами вторых слагаемых соответственно сумматоров с п-го по (2(п-Т)-3)-й первой группы и с входами третьих слагаемых сумматоров соответственно с (2(п-1)-2) по (2(п-1)-1)-йАервой группы, n-й разряд пятого информационного входа группы соединен с входом третьего слагаемого 2(п-1)-го сумма- тора первой группы и входом второго спагаемого (п+2)-го сумматора второй группы, вход третьего слагаемого второго сумматЬра первой группы соединён с входом кода коррекции, выходы cjyMM второго и третьего сумматоров первой группы соединены с входами вторых слагаемых соответственно первого и второго сумматоров второй группы, выходы сумм сумматоров с четвертого по.(п-1)-й первой группы сое- длнены с входами первых слагаемых сумматоров соответственно с третьего по

(

п-2)-й второй группы, выход суммы

(2(п-1)2)-го сумматора первой труп- соединен с входом второго слагав- мЬго (п-1)го сумматора второй группы, выходы сумм (2(п-1)-1)-го и 2(п- -1)-го сумматоров первой группы соединены с входами первых слагаемых соответственно n-го и (п+1)-го сум

маторов второй группы, выходы переносов первого,второго и (n-l)-ro сумQ 5

0

5

маторов первой группы соединены с вхо- дами третьих слагаемых соответственно первого, второго и (п-1)-го сумматоров второй группы, выходы переносов сумматоров с третьего по четвертый первой группы соединены с входами вторых слагаемых сумматоров соответственно с третьим по четвертый второй группы, входы третьих слагаемых которых соединены с выходами переносов сумматоров соответственно с п-го по (п+1) первой группы, выходы переносов сумматоров с (2(п-1)-2)-го по 2(п-1)-го соединены с входами вторых слагаемых сумматоров соответственно с п-го по (п+2) второй группы, выходы сумм сумматоров второй группы с второго по (п+2)-и соединены с входами первых слагаемых сумматоров соответственно с первого по (п+1)-и третьей группы, выходы переносов сумматоров второй группы с первого по (п+1)-й соединены с входами вторых слагаемых соответствующих одноименных сумматоров третьей группы, выходы переносов сумматоров первой группы с n-го по (2(п-1)3)-й соединены с входами третьих слагаемых сумматоров соответственно с третьего по (п-2)-й третьей группы, выходы сзтмм сумматоров третьей группы с второго по (п+2)-и и выход переноса (п+2)-го сумматора второй группы соединены с первым выходом блока, второй выход которого соединен с выходами переносов всех сумматоров третьей группы.

ШН

М

т

%

41

Ј

.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ ВЕКТОРА | 1991 |

|

RU2022340C1 |

| Устройство для вычисления модуля вектора | 1987 |

|

SU1429112A1 |

| Устройство для вычисления модуля вектора | 1989 |

|

SU1635182A1 |

| Устройство для деления @ -разрядных чисел | 1984 |

|

SU1223224A1 |

| Устройство для вычисления гиперболических функций у = @ и у = с @ | 1990 |

|

SU1735845A1 |

| Устройство для возведения в квадрат в избыточном коде | 1985 |

|

SU1307457A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Устройство для потенцирования | 1986 |

|

SU1348833A1 |

| Устройство для извлечения квадратного корня | 1982 |

|

SU1136155A1 |

| Устройство для вычисления квадратного корня из суммы квадратов | 1990 |

|

SU1751751A1 |

Изобретение относится к области вычислительной техники и может быть применено в средствах цифровой обработки сигналов с квадратурными составляющими для вычисления модуля сигнала в реальном времени. Целью изобретения является повышение быстродействия. Устройство содержит первую 1 и вторую 2 схемы сравнения, первый 3 и второй 4 коммутаторы, первый 6 и второй 7 регистры, блок 5 коммутации аргументов многорядного кода, блок 8 преобразования многорядного кода, сумматор 9, входы первого 10 и второго 11 аргументов, выход 12 результатов. 2 з.п. ф-лы, 4 ил.

Z09lV l

Si/16

W+Y

Фиг. 4

- Lilt

Sill.KK Si/8

-ito)

г to)

№) -4(Ъ)

| Устройство для вычисления квадратного корня из суммы квадратов двух чисел | 1981 |

|

SU997034A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство для вычисления функций @ | 1980 |

|

SU957207A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1990-02-07—Публикация

1988-05-23—Подача