Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных системах с общей многомодульной памятью.

Известны устройства для приоритетного обращения к общей памяти, содержащие блок анализа состояния запрашиваемых модулей памяти, блок приоритета (арбитр запросов на обращение к памяти), коммутатор адресов блоков памяти, соединенный с дешифратором обращения к модулю памяти [1]

Наиболее близким по технической сущности к предложенному изобретению является устройство для приоритетного обращения к общей многомодульной памяти, содержащее последовательно соединенные блок приоритета (арбитр запросов на обращение к памяти), коммутатор адреса и дешифратор [2]

Недостатком данных устройств является невозможность изменять адрес основного модуля памяти на адрес резервного при отказе основного модуля.

Сущность изобретения заключается в том, что предложенное устройство, помимо формирования адреса модуля, к которому обращен процессоp, осуществляет в зависимости от состояния кода подмены, подмену этого адреса на адрес соответствующего резеpвного модуля.

Обычная функция формирования адреса модуля осуществляется за счет общих признаков заявленного устройства, к которым относятся блок приоритета, коммутатор адреса модуля и первый дешифратор (дешифратор обращения). Для решения ранее сформированной задачи в устройство введены регистр подмены, мультиплексор, второй дешифратор (многовходовой элемент И) и элементы НЕ. При этом регистр подмены, принимающий код подмены со стороны любого из процессоров, имеет статус модуля в составе общей памяти вычислительной системы с собственным адресом модуля, не подлежащим никакой подмене. Введенный второй дешифратор подключен так, что обеспечивает адресацию только регистра подмены. Введенный мультиплексор с соответствующими связями обеспечивает в зависимости от кода подмены изменение старшего разряда модуля.

В результате этого реализуется автоматическое дублирование каждого основного модуля памяти резервным. При этом условие переключения или подмены основного модуля на резервный вырабатывает любой из процессоров по определенной программе. И это условие выражается в определенном коде подмены.

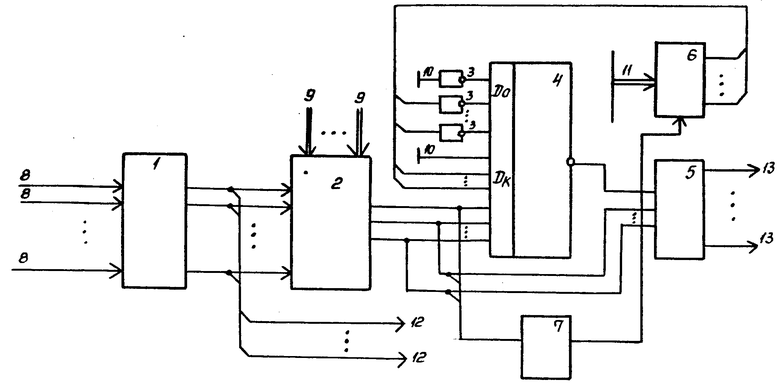

На чертеже представлена функциональная схема устройства для обращения к общей памяти.

Устройство содержит блок приоритета 1, коммутатор 2 адресов модулей памяти, элементы НЕ 3, мультиплексор 4, первый дешифратор 5 обращения к памяти, входы 9 адресов модулей памяти, шины 10 нулевого потенциала, общая шина 11, выходы 12 ответных сигналов и выходы 13 сигналов обращения.

Выходы блока приоритета 1 соединены с соответствующими управляющими входами коммутатора 2, входы 9 которого являются для него информационными входами. Выходы коммутатора 2 соединены с соответствующими управляющими входами мультиплексора 4 и входами второго дешифратора 7, выход которого соединен с управляющим входом регистра 6 подмены, входы которого соединены с общей шиной 11, а выходы соединены через элементы НЕ 3 с младшей группой информационных входов мультиплексора 4, кроме первого входа, и непосредственно со старшей группой аналогичных входов, кроме первого входа в этой группе, который соединен с шиной 10 нулевого потенциала. При этом первый вход младшей группы входов мультиплексора 4 соединен с шиной нулевого потенциала через соответствующий элемент НЕ 3. Выход мультиплексора соединен со старшим адресным входом первого дешифратора 5, остальные входы которого соединены с соответствующими выходами коммутатора 2.

Назначение вновь введенных узлов следующее. Мультиплексор 4 в зависимости от содержания соответствующего разряда регистра 6 подмены устанавливает такое значение старшего разряда адреса модуля, при котором происходит обращение либо в резервный модуль памяти, либо в основной. Второй дешифратор 7 обеспечивает обращение выбранного арбитром 1 процессора к регистру подмены, для того чтобы подключить его к общей шине 11 и сформировать необходимый код подмены.

Каждый разряд кода подмены задает режим подмены для соответствующей пары модулей памяти и в зависимости от его состояния происходит обращение либо к основному (резервируемому) модулю, либо к резервному.

Для данной схемы резервирования разрядность регистра подмены вычисляется по формуле:

n  где а разрядность адреса модуля.

где а разрядность адреса модуля.

Так, для а 4, n 7; для а 3, n 3.

При этом количество модулей памяти, охваченных подменой, будет равно 2а 2, максимальное количество модулей, которое способно обслужить заявленное устройство, равно 2а 1. Это происходит из-за того, что один из адресов модулей памяти используется для обращения с помощью второго дешифратора 7 к регистру подмены 6.

Использовать первый дешифратор для обращения к регистру подмены не представляется возможным, так как регистр подмены становится неуправляемым.

В заявке условно принято считать, что к младшей группе информационных входов мультиплексора относятся входы с номерами (0  ), а к старшей с остальными номерами (

), а к старшей с остальными номерами ( K)

K)

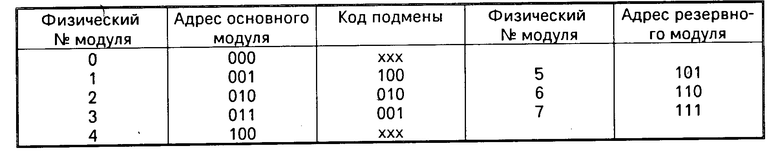

Рассмотрим вариант предложенного устройства, обрабатывающего трехразрядный адрес модуля памяти (а 3). Как было раньше показано, такое устройство обслуживает 7 модулей памяти, из которых шесть охвачены подменой. Можно условно считать, что три из них резервируемые или основные и три резервные. Предполагается, что адреса трех резервируемых модулей имеют значения 001-011 и трех резервных соответственно 101-111. При этом адрес модуля "000" используется для обращения к регистру подмены посредством второго дешифратора 7, адрес "100" соответствует основному нерезервному модулю. Соотношения адресов основных, резервных модулей и кода подмены для данного случая показаны в таблице.

Из таблицы следует, что если откажет первый модуль, его должен заменить пятый при коде подмены "Iхх", если откажет второй модуль его заменяет шестой при коде подмены "хIх" и т.д.

Итак, устройство, помимо основных функций, реализует режим резервирования с дублированием и работает следующим образом.

По входам 8 на блок приоритета 1 поступают от процессоров сигналы запросов на обращение к модулям памяти. При этом по входам 9 на коммутатор 2 поступают адреса запрашиваемых модулей памяти.

Блок приоритета 1, преобразуя запросы, выдает ответный сигнал наиболее приоритетному процессору по соответствующему выходу 12 и этим же сигналом разрешает коммутатору 2 пропустить адрес запрашиваемого этим процессором модуля памяти. Если все разряды кода подмены равны нулю, то мультиплексор 2 формирует старший разряд адреса модуля в соответствии с его физическим номером и преобразования адреса не происходит.

Единица в любом разряде кода подмены приведет к перемене старшего разряда адреса модуля в соответствии с ранее определенным правилом подмены адресов. Очевидно, что для адресов "000" и "001" подмены не будет при любом состоянии регистра подмены, так как на 0-й информационный вход мультиплексора подается константа "1", а на 4-й константа "0".

Формирование кода подмены может осуществлять любой из процессоров системы, который входит в состав общей памяти вычислительной системы.

Следует отметить, что преобразование адресов обладает симметрией в том смысле, что при обращении к резервным модулям в режиме подмены будут включаться соответствующие основные модули. Например, при обращении к шестому модулю при единичном втором разряде кода подмены будет включен второй модуль и т.д.

Введение мультиплексора, регистра подмены и дополнительного дешифратора с соответствующими связями дает возможность с помощью преобразования адресов модулей памяти обеспечить работу многомодульной памяти в дублированном режиме. Это, в свою очередь, дает возможность повысить в конечном итоге отказоустойчивость вычислительной системы, имеющей многомодульную память.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обращения к общей многомодульной памяти | 1988 |

|

SU1501069A1 |

| Устройство для приоритетного обращения к общей многомодульной памяти | 1988 |

|

SU1539786A1 |

| Устройство для подмены информации в постоянной памяти | 1989 |

|

SU1645998A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2054796C1 |

| Запоминающее устройство | 1990 |

|

SU1805500A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1571599A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для подмены информации в постоянной памяти | 1988 |

|

SU1536443A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Генератор двоичной последовательности | 1990 |

|

SU1709505A1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных системах с общей многомодульной памятью расширить функциональные возможности путем изменения адреса основного модуля памяти на адрес резервного при отказе основного модуля. Введение элементов НЕ 3, мультиплексора 4, регистора подмены 6 и дополнительного дешифратора 7 в предлагаемое устройство дает возможность повысить в конечном итоге отказоустойчивость вычислительной системы, имеющей многомодульную память. 1 ил. 1 табл.

УСТРОЙСТВО ДЛЯ ОБРАЩЕНИЯ К ОБЩЕЙ ПАМЯТИ, содержащее коммутатор адреса, первый дешифратор и блок приоритета, входы которого являются входами запросов к памяти устройства, выходы блока приоритета соединены с управляющими входами коммутатора адреса и являются выходами ответных сигналов устройства, входы адресов модулей памяти которого подключены к информационным входам коммутатора адреса, выходы которого соединены с входами младших разрядов первого дешифратора, выходы которого являются выходами сигналов обращения устройства, отличающееся тем, что в него введены мультиплексор, группа элементов НЕ, второй дешифратор и регистр подмены, информационные входы которого подключены к входу кода подмены устройства, управляющие входы мультиплексора соединены с выходами коммутатора адреса и входами второго дешифратора, выход которого соединен с входом записи регистра подмены, информационный вход первого младшего разряда мультиплексора через первый элемент НЕ группы соединен с шиной нулевого потенциала устройства, информационные входы остальных младших разрядов мультиплексора через остальные элементы НЕ группы соединены с выходами младших разрядов регистра подмены, информационный вход первого старшего разряда мультмплексора подключен к шине нулевого потенциала устройства, информационные входы остальных старших разрядов мультиплексора соединены с выходами старших разрядов регистра подмены.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для приоритетного обращения к общей памяти | 1986 |

|

SU1425669A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-11-27—Публикация

1992-11-17—Подача