Изобретение относится к вычислительной технике и может быть использовано1 в многопроцессорных вычислительных системах с общей многомодульной памятью.

Целью изобретения является расширение области применения путем, изменения адреса основного модуля памяти на адрес резервного при отказе основного модуля.

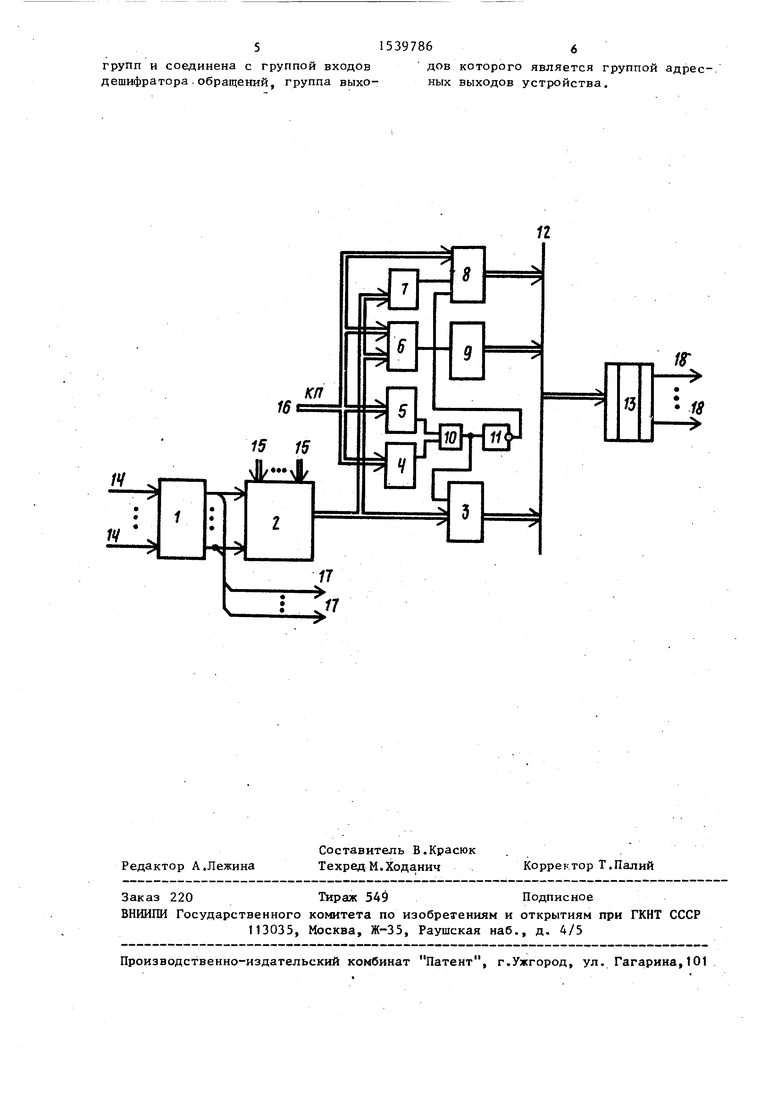

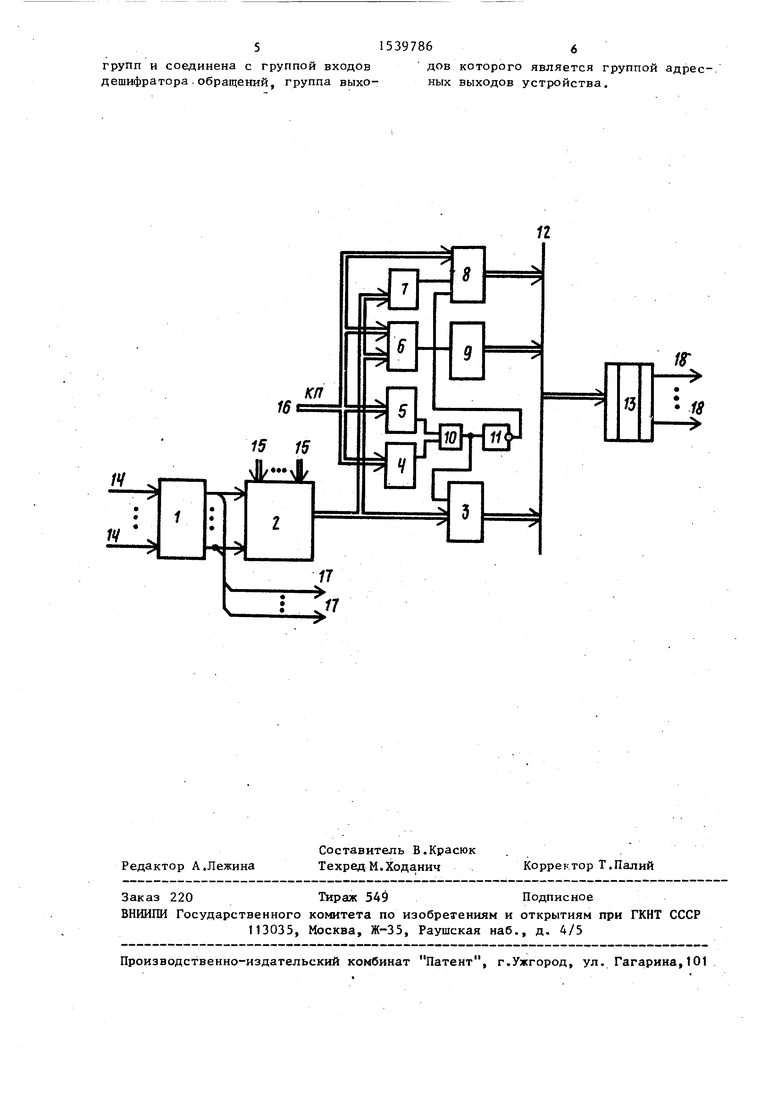

На чертеже дана схема предлагаемого устройства.

Устройство содержит арбитр 1 запросов на обращение к памяти, коммутатор 2 адресов модулей памяти, первую группу элементов И 3, первый элемент И 4, второй элемент И 5, схему 6 сравнения, третий элемент И 7, вторую группу элементов И 8, формирователь 9 единиц,

элемент ИЛИ 10, элемент НЕ 11, шину 12 адреса модуля, дешифратор 13 обращения, входы 14 запросов на обращение к памяти, входы 15 адресов модулей памяти, входы 16 кода подмены адресов, выходы 17 ответных сигналов и выходы 18 сигналов обращения.

Предлагаемое устройство обслуживает запросы на обращение к общей многомодульной памяти, в которой организовано скользящее резервирование модулей, причем в качестве резервного выбран модуль с максимальным адресом. Например, при трехразрядном адресе адрес резервного модуля равен 111. Остальные модули являются основными.

Подмена основного модуля резервным происходит при отказе первого путем

О1

оэ со

Ч

оо о

преобразования адреса отказавшего модуля адресом резервного. Правила преобразования (подмены) адресов модулей задаются кодом подмены, который вырабатывается центральным устройством (не показано) в результате диагностического анализа. Код подмены по существу является адресом того модуля памяти, который надо заменить при обраще-J нии на резервный. Нулевое значение кода подмены так же, как и единичное, означает отсутствие подмены. Таким образом, при наличии 2 модулей памяти, где к - количество разрядов адреса мо- дуля, скользящим резервированием может быть охвачено (2 - 2) модулей. Предположим, что адрес модуля является трехразрядным.

Устройство работает следующим об- J разом.

При появлении одновременно нескольких запросов на входах 14 арбитр 1 запросов на обращение к памяти выдает ответный сигнал процессору по одному 2 из выходов 17 ответных сигналов и этим же сигналом с помощью коммутатора 2 адресов модулей памяти инициирует прохождение требуемого адреса модуля с соответствующего входа 15 адресовмодулей памяти на информационные входы первой группы элементов И 3. В случае наличия нулевого кода подмены на входах 16 кода подмены адресов, что фиксируется вторым элементом И 5, осуществляющим функцию И на основе отри- цательной логики, с помощью элемента ИЛИ 10 открывается первая группа элементов И 3 и адрес модуля без преобразования через шину 12 адреса модуля поступает на входы дешифратора 13 обращения, на соответствующем выходе 18 которого образуется сигнал обращения. То же самое происходит при значении кода подмены, равном 111, только прохождение адреса модуля через первую группу вентилей на входы дешифратора 13 обращения обеспечивает первый элемент И А. Пусть код подмены равен 001. Это означает, что модуль с этим адресом находится в/состоянии отказа и необходимо при обращении к нему подменить его резервным модулем. Для этого необходимо преобразовать адрес модуля 001 в адрес 111.. Факт обращения к модулю с адресом 001 устанавливает- ся схемой 6 сравнения, которая с помощью формирователя 9 единиц формирует адрес модуля 111. В результате

4

4

5

Q

5 -

0

5

0

дешифратор 13 обращения формирует сигнал обращения к резервному модулю по соответствующему выходу 18 сигналов обращения. При данном значении кода подмены в случае обращения к резервному модулю адрес модуля с помощью третьего элемента И 7, элемента НЕ 11 и второй группы элементов И 8 преобразуется в 001.

Аналогичный процесс преобразования адреса происходит и при любом другом коде подмены.

Формула изобретения

Устройство для приоритетного обра.- щения к общей многомодульной памяти, содержащее арбитр запросов, коммута-т тор адресов модулей памяти и дешифратор обращения, причем входы запросов на обращение устройства соединены с входами арбитра запросов, выходы которого соединены с ответными выходами устройства и с управляющими входами коммутатора адресов модулей памяти, информационные входы которого соединены с входами адресов модулей памяти устройства, отличающееся тем,, что, с целью расширения области применения путем изменения адреса основного модуля памяти на адрес резервного при отказе основного модуля, в него введены с перво- го по третий элементы И, схема сравнения, формирователь единиц, элемент ИЛИ, элемент НЕ, первая и вторая группы элементов И, причем группа входов кода подмены адреса устройства соединена с входами первого и второго элементов И, первой группой входов схемы сравнения и первыми входами элементов И первой группы, группа выходов коммутатора адресов модулей памяти соединена с первыми входами элементов И второй группы, второй группой входов схемы сравнения и входами третьего элемента И, выход которого соединен с вторыми входами элементов И первой группы, третьи вхо- ды которых соединены через элемент НЕ с выходом элемента ИЛИ и вторыми входа- ми элементов И второй группы, выходы первого и второго элементов И соединены с соответствующими входа- ми элемента ИЛИ, выход схемы сравнения соединен с входом формирователя единиц, группа выходов которого поразрядно объединена через МОНТАЖНОЕ ИЛИ с вы- ходами элементов И первой и второй

групп и соединена с группой входов дешифратора обращений, группа выходов которого является группой адресных выходов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обращения к общей многомодульной памяти | 1988 |

|

SU1501069A1 |

| УСТРОЙСТВО ДЛЯ ОБРАЩЕНИЯ К ОБЩЕЙ ПАМЯТИ | 1992 |

|

RU2049348C1 |

| Устройство для приоритетного обращения к общей памяти | 1986 |

|

SU1425669A1 |

| Резервированная система | 1990 |

|

SU1785087A1 |

| Микропроцессорная система | 1989 |

|

SU1686454A1 |

| Постоянное запоминающее устройство с резервированием | 1986 |

|

SU1372363A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ НЕПРЕРЫВНОГО КАНАЛА МНОГОЗНАЧНОЙ СИСТЕМЫ АВТОМАТИЧЕСКОЙ ЛОКОМОТИВНОЙ СИГНАЛИЗАЦИИ (ФС-ЕН) | 2006 |

|

RU2327590C1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных системах с общей многомодульной памятью. Целью изобретения является расширение области применения путем изменения адреса основного модуля памяти на адрес резервного при отказе основного модуля. Устройство для приоритетного обращения к общей многомодульной памяти содержит арбитр запросов на обращение к памяти, коммутатор адресов модулей памяти, две группы элементов И, три элемента И, схему сравнения, формирователь единиц, элемент ИЛИ, элемент НЕ и дешифратор обращения. Устройство обеспечивает обращение к модулю с максимальным адресом, выбранному в качестве резервного, при отказе одного из основных модулей общей многомодульной памяти, в которой организовано скользящее резервирование модулей. 1 ил.

16

15 15

§/

2

Ft

| Устройство для приоритетного обращения процессоров к общей памяти | 1979 |

|

SU883905A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования адреса | 1978 |

|

SU729589A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1990-01-30—Публикация

1988-02-01—Подача