Изобретение относится к области ЭРТО- матики и вычислительной техники и может быть-использовано при проектировании энергонезависимых постоянных запоминающих устройств, предназначенных для хранения определенных кодовых последовательностей.

Целью изобретения является упрощение устройства.

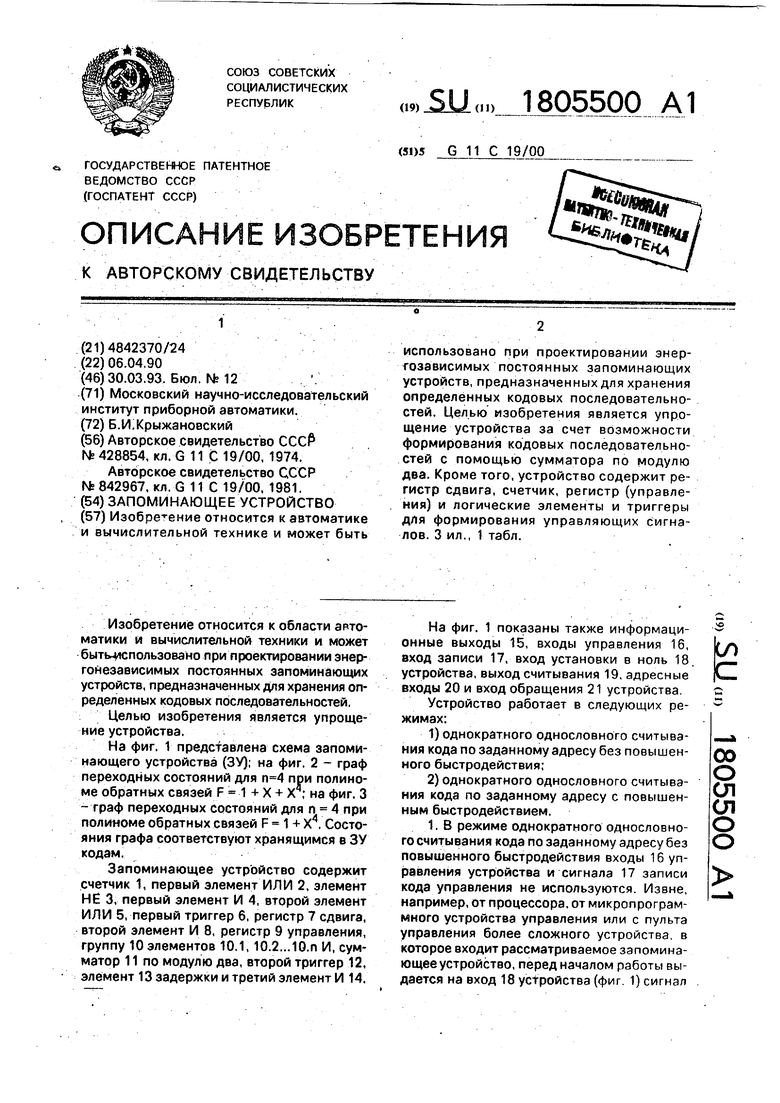

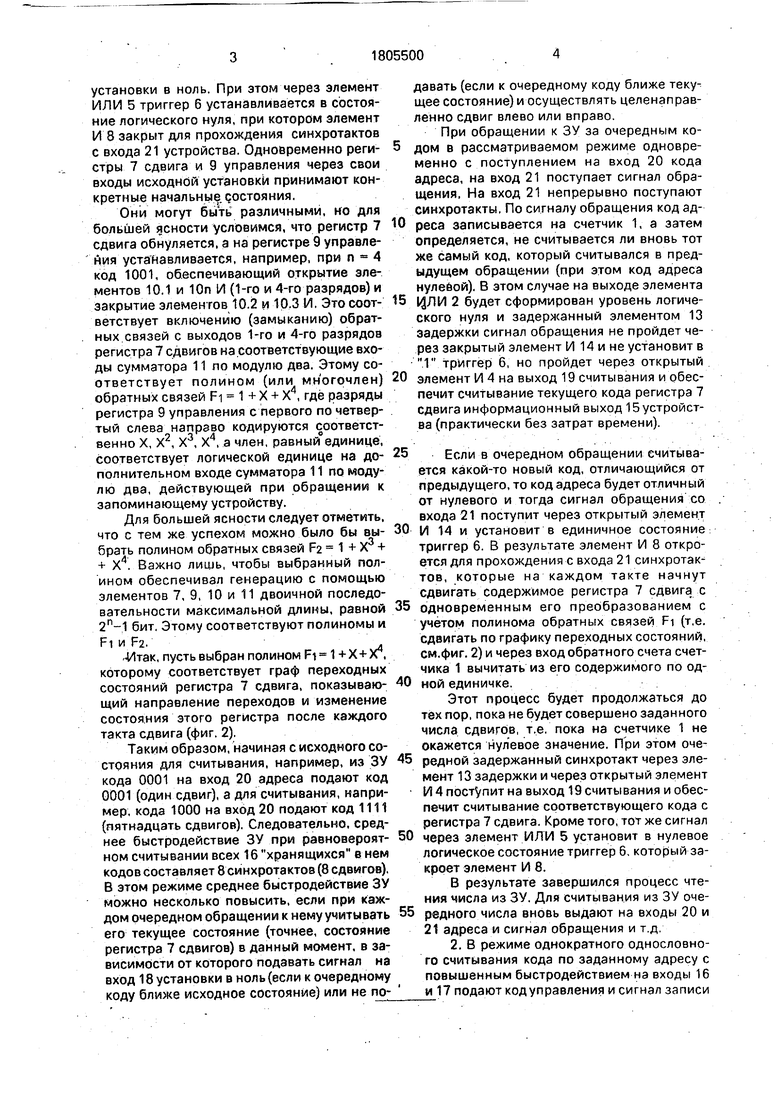

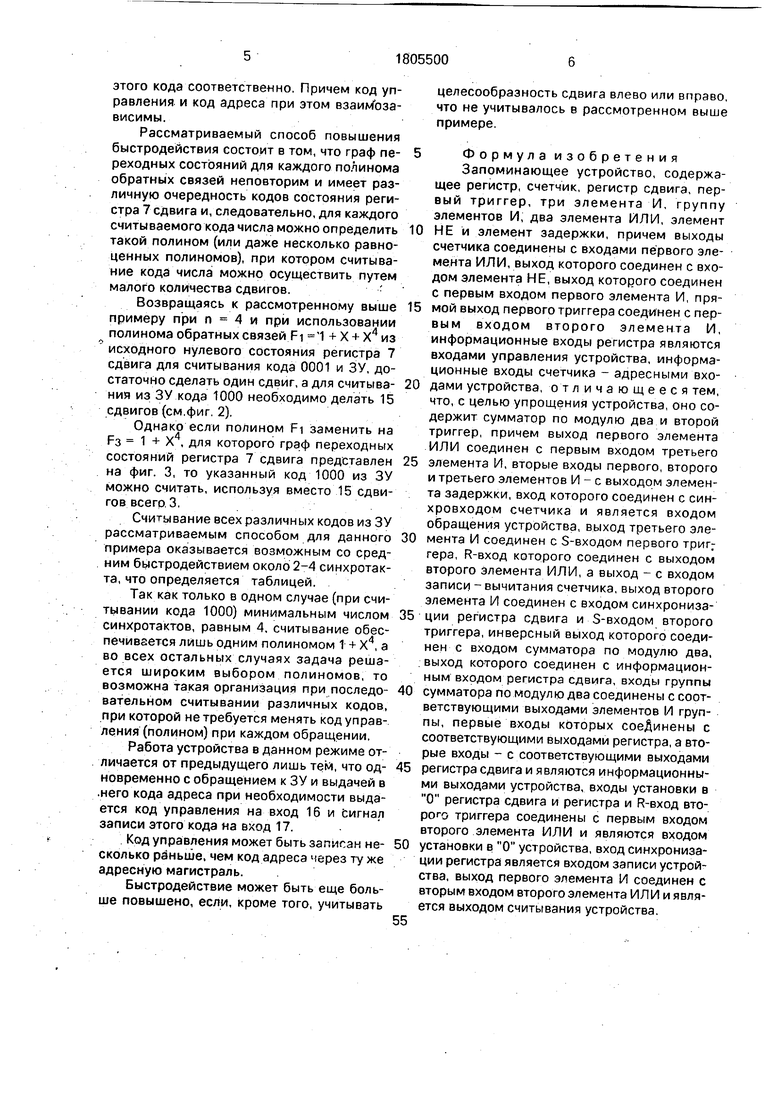

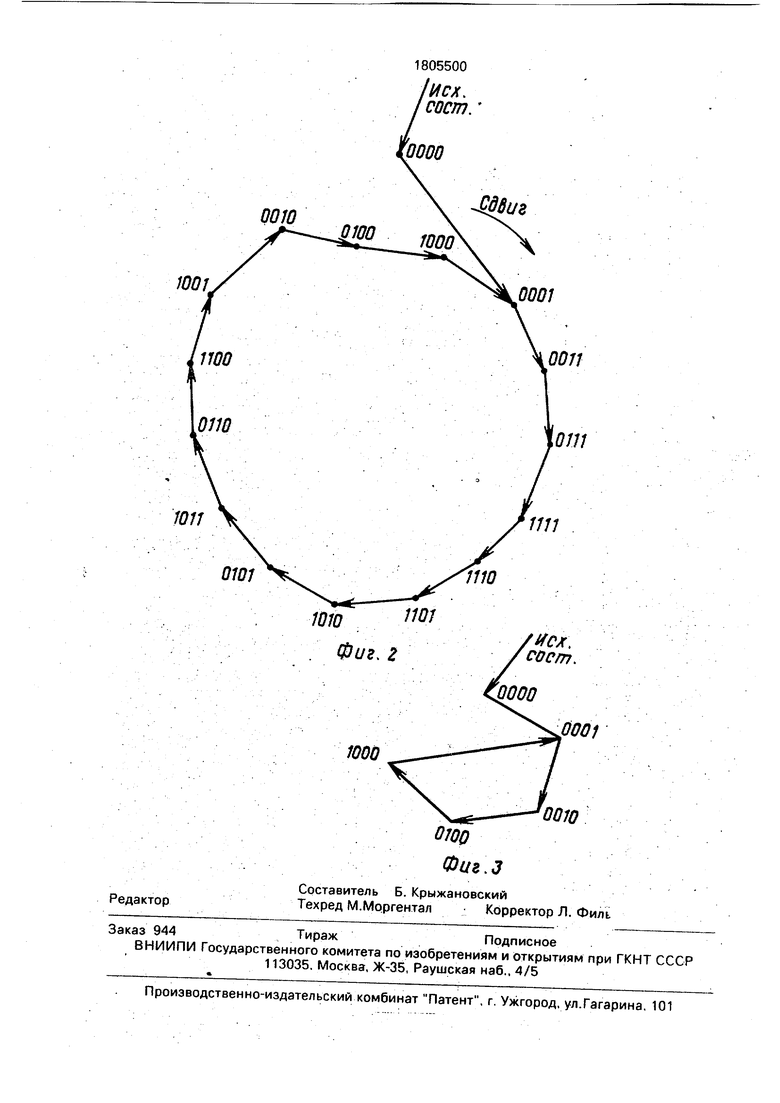

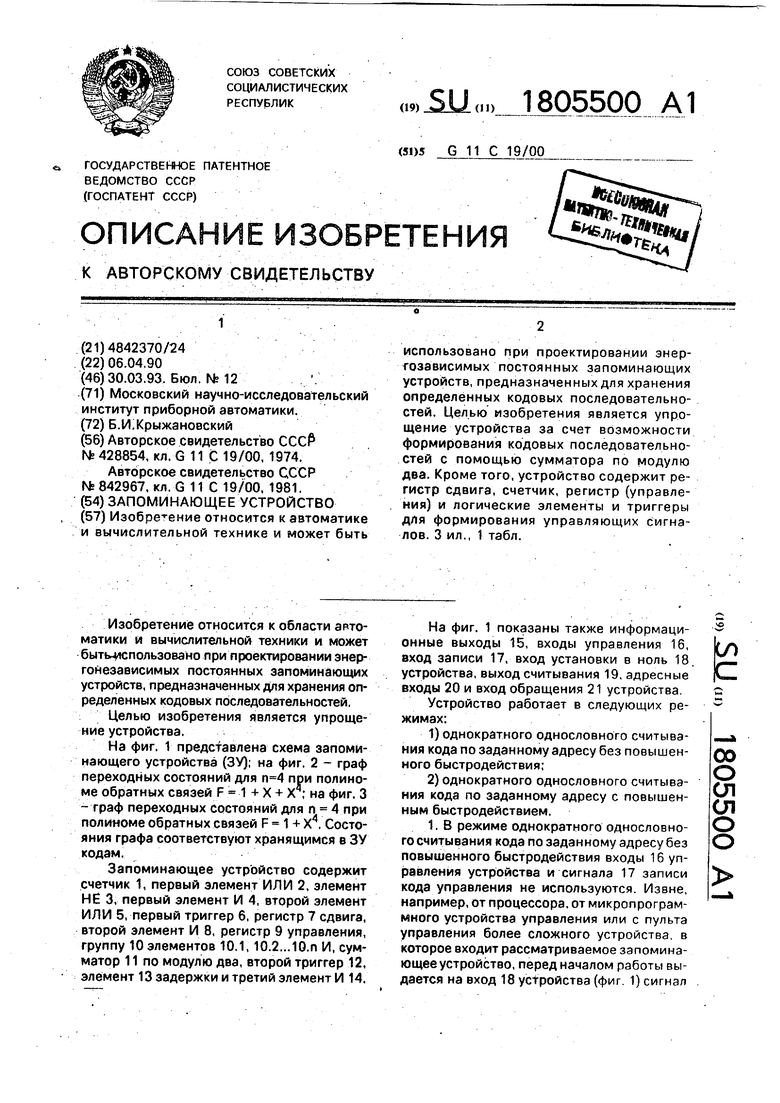

На фиг. 1 представлена схема запоминающего устройства (ЗУ); на фиг. 2 - граф переходных состояний для при полиноме обратных связей F 1 + X + X ; на фиг. 3 - граф переходных состояний для п 4 при полиноме обратных связей F 1 + X4. Состояния графа соответствуют хранящимся в ЗУ кодам.

Запоминающее устройство содержит счетчик 1, первый элемент ИЛИ 2, элемент НЕ 3, первый элемент И 4, второй элемент ИЛИ 5, первый триггер 6, регистр 7 сдвига, второй элемент И 8, регистр 9 управления, группу 10 элементов 10.1,10.2...Ю.п И, сумматор 11 по модулю два, второй триггер 12, элемент 13 задержки и третий элемент И 14.

На фиг. 1 показаны также информационные выходы 15, входы управления 16, вход записи 17, вход установки в ноль 18. устройства, выход считывания 19, адресные входы 20 и вход обращения 21 устройства.

Устройство работает в следующих режимах:

1) однократного однословного считывания кода по заданному адресу без повышенного быстродействия;

2) однократного однословного считывания кода по заданному адресу с повышенным быстродействием.

1. В режиме однократного однословного считывания кода по заданному адресу без повышенного быстродействия входы 16 управления устройства и сигнала 17 записи кода управления не используются. Извне, например, от процессора, от микропрограммного устройства управления или с пульта управления более сложного устройства, в которое входит рассматриваемое запоминающее устройство, перед началом работы выдается на вход 18 устройства (фиг. 1) сигнал

Чя

Ј

00

о ел ел о о

установки в ноль. При этом через элемент ИЛИ 5 триггер 6 устанавливается в состояние логического нуля, при котором элемент И 8 закрыт для прохождения синхротактов с входа 21 устройства. Одновременно регистры 7 сдвига и 9 управления через свои входы исходной установки принимают конкретные начальные состояния.

Они могут быть различными, но для большей ясности условимся, что регистр 7 сдвига обнуляется, а на регистре 9 управления устанавливается, например, при п 4 код 1001, обеспечивающий открытие элементов 10.1 и 10п И (1-го и 4-го разрядов) и закрытие элементов 10.2 и 10,3 И. Это соответствует включению (замыканию) обратных связей с выходов 1-го и 4-го разрядов регистра 7 сдвигов на соответствующие входы сумматора 11 по модулю два. Этому соответствует полином (или многочлен) обратных связей FI 1 + X + X4, где разряды регистра 9 управления с первого по четвертый слева направо кодируются соответственно X, X2, X3, X4, а член, равный единице, соответствует логической единице на дополнительном входе сумматора 11 по модулю два, действующей при обращении к запоминающему устройству.

Для большей ясности следует отметить, что с тем же успехом можно было бы выбрать полином обратных связей F2 1 + X + + X4. Важно лишь, чтобы выбранный полином обеспечивал генерацию с помощью элементов 7, 9, 10 и 11 двоичной последовательности максимальной длины, равной 2п-1 бит. Этому соответствуют полиномы и FI и Fa.

.-Итак, пусть выбран полином FI 1 +Х+ХЛ которому соответствует граф переходных состояний регистра 7 сдвига, показывающий направление переходов и изменение состояния этого регистра после каждого такта сдвига (фиг. 2).

Таким образом, начиная с исходного состояния для считывания, например, из ЗУ кода 0001 на вход 20 адреса подают код 0001 (один сдвиг), а для считывания, например, кода 1000 на вход 20 подают код 1111 (пятнадцать сдвигов). Следовательно, среднее быстродействие ЗУ при равновероятном считывании всех 16 хранящихся в нем кодов составляет 8 синхротактов (8 сдвигов). В этом режиме среднее быстродействие ЗУ можно несколько повысить, если при каждом очередном обращении к нему учитывать его текущее состояние (точнее, состояние регистра 7 сдвигов) в данный момент, в зависимости от которого подавать сигнал на вход 18 установки в ноль (если к очередному коду ближе исходное состояние) или не подавать (если к очередному коду ближе текущее состояние) и осуществлять целенаправленно сдвиг влево или вправо.

При обращении к ЗУ за очередным кодом в рассматриваемом режиме одновременно с поступлением на вход 20 кода адреса, на вход 21 поступает сигнал обращения, На вход 21 непрерывно поступают синхротакты, По сигналу обращения код адреса записывается на счетчик 1, а затем определяется, не считывается ли вновь тот же самый код, который считывался в предыдущем обращении (при этом код адреса нулевой). В этом случае на выходе элемента

ifl/jH 2 будет сформирован уровень логического нуля и задержанный элементом 13 задержки сигнал обращения не пройдет через закрытый элемент И 14 и не установит в 1 триггер 6, но пройдет через открытый

элемент И 4 на выход 19 считывания и обеспечит считывание текущего кода регистра 7 сдвига информационный выход устройства (практически без затрат времени).

Если в очередном обращении считывается какой-то новый код, отличающийся от предыдущего, то код адреса будет отличный от нулевого и тогда сигнал обращения со входа 21 поступит через открытый элемент

И 14 и установит в единичное состояние триггер 6. В результате элемент И 8 откроется для прохождения с входа 21 синхротак тов, которые на каждом такте начнут сдвигать содержимое регистра 7 сдвига с

одновременным его преобразованием с учётом полинома обратных связей FI (т.е. сдвигать по графику переходных состояний, см.фиг. 2) и через вход обратного счета счетчика 1 вычитать из его содержимого по одной единичке.

Этот процесс будет продолжаться до тех пор, пока не будет совершено заданного числа сдвигов, т.е. пока на счетчике 1 не окажется нулевое значение. При этом очередной задержанный синхротакт через элемент 13 задержки и через открытый элемент И 4 поступит на выход 19 считывания и обеспечит считывание соответствующего кода с регистра 7 сдвига. Кроме того, тот же сигнал

через элемент ИЛИ 5 установит в нулевое логическое состояние триггер 6, который закроет элемент И 8.

В результате завершился процесс чтения числа из ЗУ. Для считывания из ЗУ очередного числа вновь выдают на входы 20 и 21 адреса и сигнал обращения и т.д.

2. В режиме однократного однословного считывания кода по заданному адресу с повышенным быстродействием на входы 16 и 17 подают код управления и сигнал записи

этого кода соответственно. Причем код управления и код адреса при этом взаимозависимы.

Рассматриваемый способ повышения быстродействия состоит в том, что граф переходных состояний для каждого полинома обратных связей неповторим и имеет различную очередность кодов состояния регистра 7 сдвига и, следовательно, для каждого считываемого кода числа можно определить такой полином (или даже несколько равноценных полиномов), при котором считывание кода числа можно осуществить путем малого количества сдвигов.г

Возвращаясь к рассмотренному выше примеру при п 4 и при использовании полинома обратных связей FI 4 + X + X4 из исходного нулевого состояния регистра 7 сдвига для считывания кода 0001 и ЗУ, достаточно сделать один сдвиг, а для считывания из ЗУ кода 1000 необходимо делать 15 сдвигов (см.фиг. 2).

Однако если полином FI заменить на Рз 1 + X , для которого граф переходных состояний регистра 7 сдвига представлен на фиг. 3, то указанный код 1000 из ЗУ можно считать, используя вместо 15 сдвигов всего, 3,

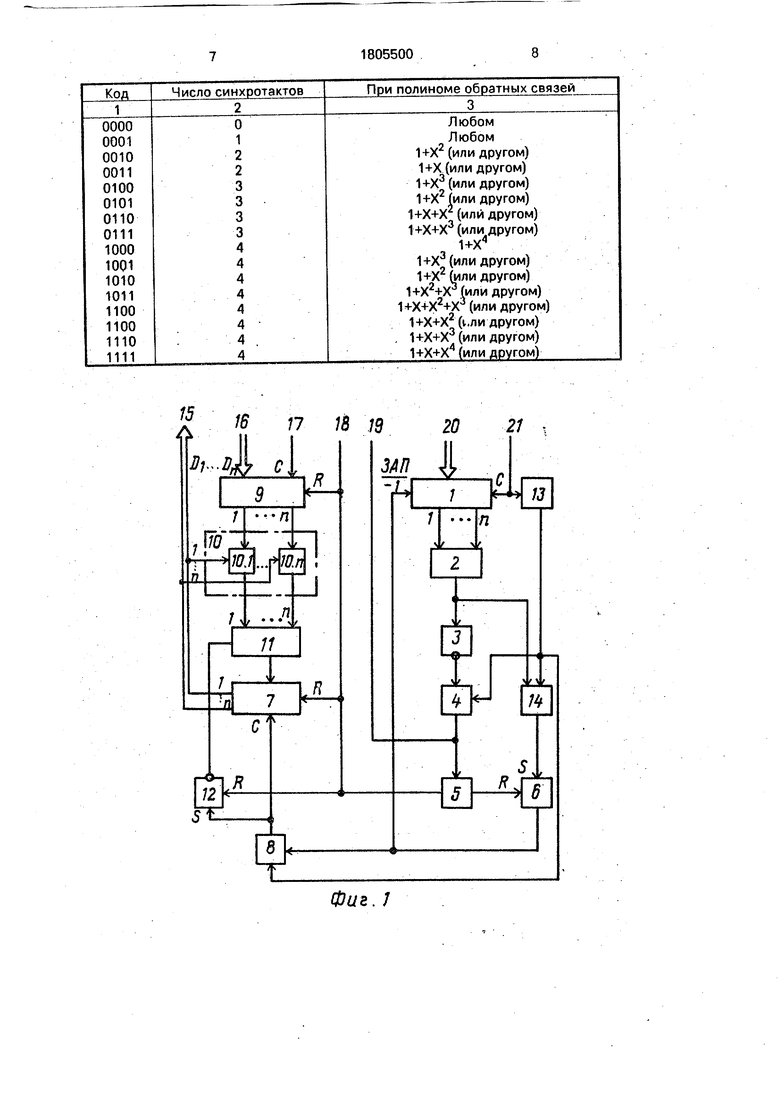

Считывание всех различных кодов из ЗУ рассматриваемым способом для данного примера оказывается возможным со средним быстродействием около 2-4 синхротак- та, что определяется таблицей.

Так как только в одном случае (при считывании кода 1000) минимальным числом синхротактов, равным 4, считывание обеспечивается лишь одним полиномом Т + X , а во всех остальных случаях задача решается широким выбором полиномов, то возможна такая организация при последовательном считывании различных кодов, при которой не требуется менять код управления (полином) при каждом обращении.

Работа устройства в данном режиме отличается от предыдущего лишь тем, что одновременно с обращением к ЗУ и выдачей в .него кода адреса при необходимости выдается код управления на вход 16 и сигнал записи этого кода на вход 17.

Код управления может быть записан несколько рйньше, чем код адреса через ту же адресную магистраль.

Быстродействие может быть еще больше повышено, если, кроме того, учитывать

целесообразность сдвига влево или вправо, что не учитывалось в рассмотренном выше примере.

Формула изобретения

Запоминающее устройство, содержащее регистр, счетчик, регистр сдвига, первый триггер, три элемента И, группу элементов И, два элемента ИЛИ, элемент

НЕ и элемент задержки, причем выходы счетчика соединены с входами первого элемента ИЛИ, выход которого соединен с входом элемента НЕ, выход которого соединен с первым входом первого элемента И, прямой выход первого триггера соединен с пер- вым входом второго элемента И, информационные входы регистра являются входами управления устройства, информационные входы счетчика - адресными входами устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит сумматор по модулю два и второй триггер, причем выход первого элемента ИЛИ соединен с первым входом третьего

элемента И, вторые входы первого, второго и третьего элементов И - с выходом элемента задержки, вход которого соединен с син- хровходом счетчика и является входом обращения устройства, выход третьего элемента И соединен с S-входом первого триг;- гера, R-вход которого соединен с выходом второго элемента ИЛИ, а выход - с входом записи - вычитания счетчика, выход второго элемента И соединен с входом синхронизации регистра сдвига и S-входом второго триггера, инверсный выход которого соединен с входом сумматора по модулю два, . выход которого соединен с информационным входом регистра сдвига, входы группы

сумматора по модулю два соединены с соответствующими выходами элементов И группы, первые входы которых соеДинены с соответствующими выходами регистра, а вторые входы - с соответствующими выходами

регистра сдвига и являются информационными выходами устройства, входы установки в О регистра сдвига и регистра и R-вход второго триггера соединены с первым входом второго элемента ИЛИ и являются входом

установки в О устройства, вход синхронизации регистра является входом записи устройства, выход первого элемента И соединен с вторым входом второго элемента ИЛИ и является выходом считывания устройства.

Фиг. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор двоичной последовательности | 1990 |

|

SU1709505A1 |

| СПОСОБ ХРАНЕНИЯ И ИСПОЛЬЗОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ | 2016 |

|

RU2634227C2 |

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Устройство для обнаружения пакетных ошибок | 1987 |

|

SU1541607A1 |

| Устройство для коррекции ошибок в блоках памяти с последовательным доступом | 1987 |

|

SU1510014A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| УСТРОЙСТВО АДАПТИВНОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ | 2000 |

|

RU2169431C1 |

| Кодирующее устройство | 1983 |

|

SU1239868A1 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1481901A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при проектировании энергозависимых постоянных запоминающих устройств, предназначенных для хранения определенных кодовых последовательностей. Целью изобретения является упрощение устройства за счет возможности формирования кодовых последовательностей с помощью сумматора по модулю два. Кроме того, устройство содержит регистр сдвига, счетчик, регистр (управления) и логические элементы и триггеры для формирования управляющих сигналов. 3 ил., 1 табл.

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГОУПРАВЛЕНИЯ ЗАЛИВКОЙ ПОД РЕГУЛИРУЕМЫМДАВЛЕНИЕМ | 1973 |

|

SU428854A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство | 1979 |

|

SU842967A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-03-30—Публикация

1990-04-06—Подача