Изобретение относится к вычислительной технике и может быть исполь- зовано в многопроцессорных вычисли- тельньЬс системах с общей многомодульной памятью.

Цель изобретения - расширение, функциональных возможностей устройства путем изменения адреса основного модуля памяти на адрес резервного при отказе основного модуля памяти.

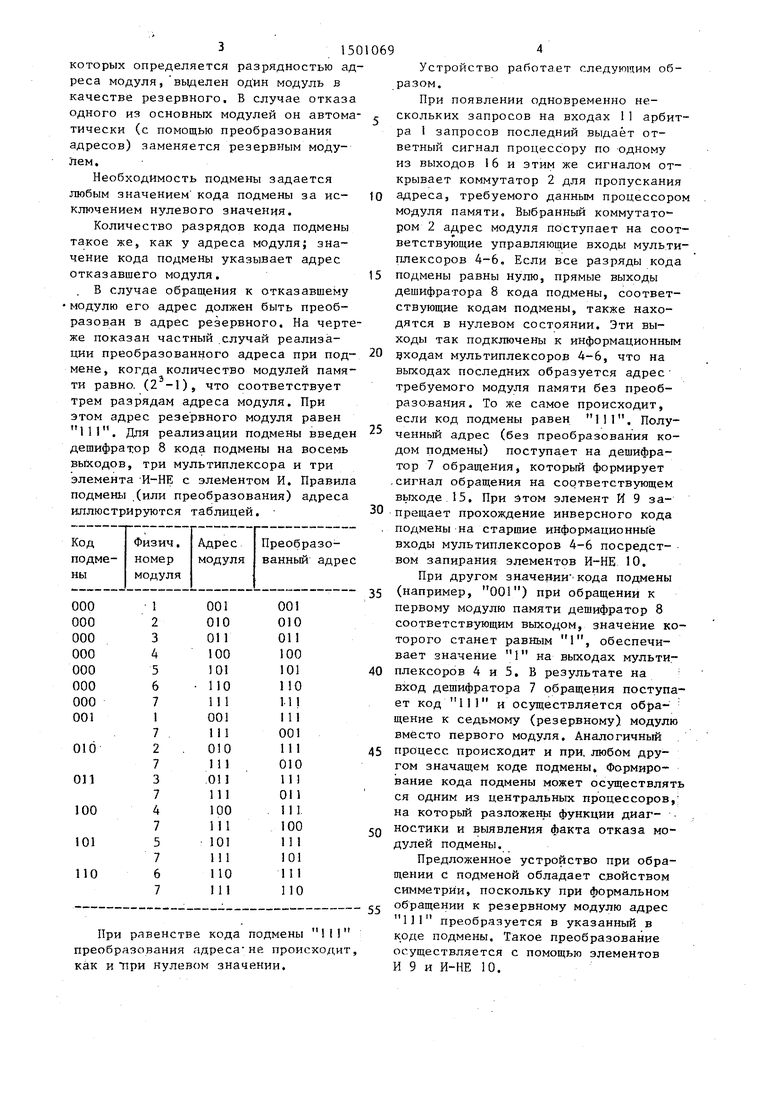

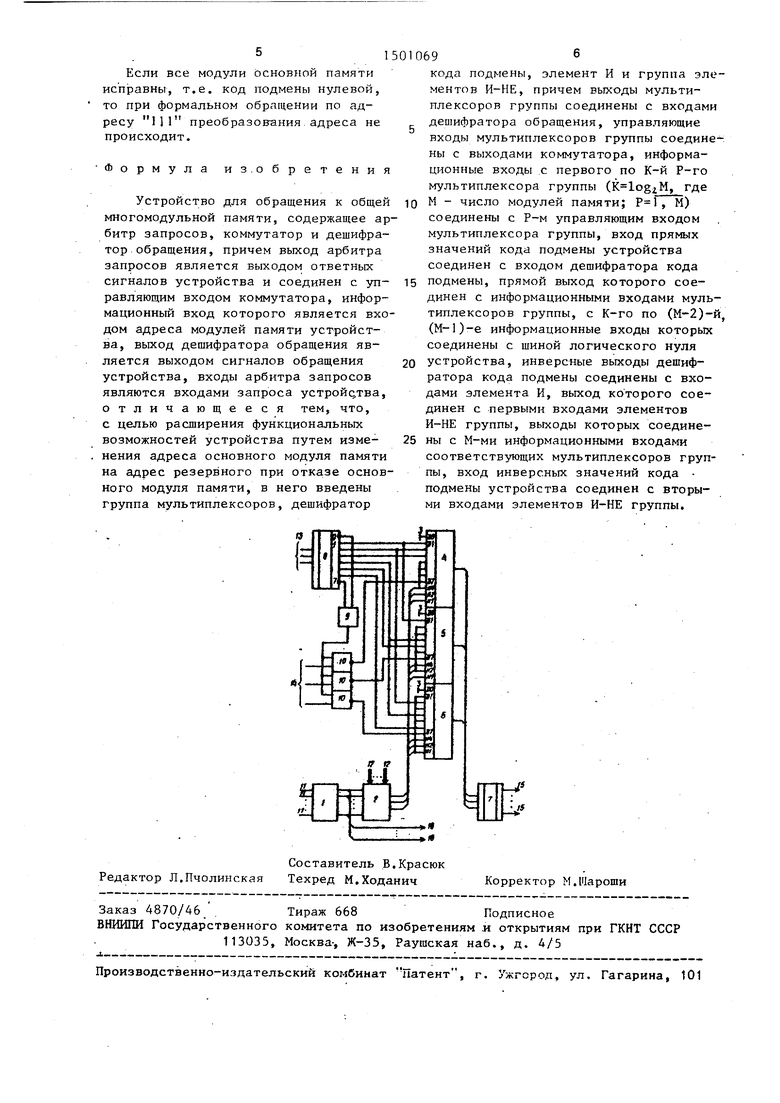

На чертеже представлена схема устройства.:

Устройство содержит арбитр Л запросов, коммутатор 2, шину 3 логического нуля, группу мультиплексоров - 4-6 по числу разрядов адреса модуля

памяти, дешифратор 7 обращения, дешифратор 8 крда подмены,элемент И 9, группу элементов И-НЕ JO по числу разрядов кода подмены, входы 11 запросов, входы J2 адресов модулей памяти, входы 13 прямых значений кода подмены, входы 14 инверсных значений кода подмены, выходы 15 сигналов обращения, выходы 16 ртветных сигна- лов.

Предлагаемое устройство осуществляет приоритетное обращение к модулям общей памяти, обеспечивая при обращении режим со скользящим резервированием. Это означает, что среди множества модулей памяти, количество

сл

о

3150

которых определяется разрядностью адреса модуля, вьщелен од ин модуль в качестве резервного. В случае отказа одного из основных модулей он автома- тически (с помощью преобразования адресов) заменяется резервным модулем.

Необходимость подмены задается любым значением кода подмены за не- ключением нулевого значения.

Количество разрядов кода подмены такое же, как у адреса модуля; значение кода подмены указывает адрес отказавшего модуля.

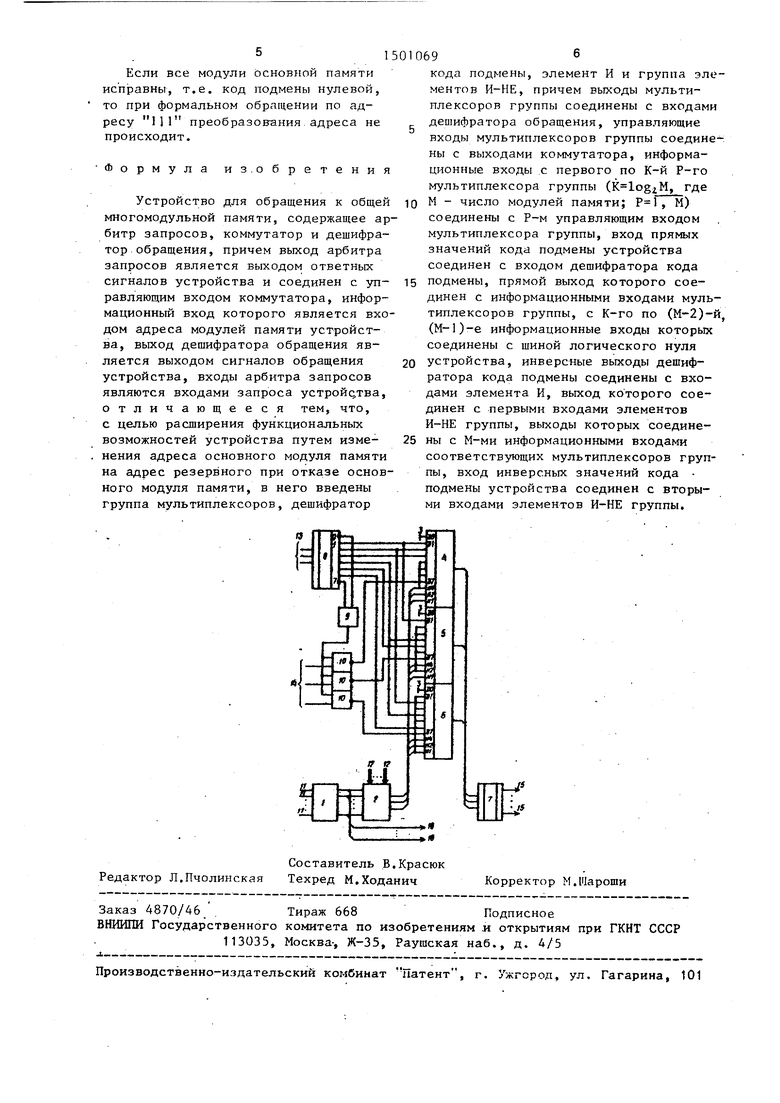

В случае обращения к отказавшему модулю его адрес должен быть преобразован в адрес резервного. На чертеже показан частный случай реализации преобразованного адреса при под- мене, когда количество модулей памяти равно. (2 -1), что соответствует трем разрядам адреса модуля. При этом адрес резервного модуля равен

111. Для реализации подмены введен дещифратор 8 кода подмены на восемь выходов, три мультиплексора и три элемента -И-НЕ с эле1 ентом И. Правила подмены (или преобразования) адреса иллюстрируются таблицей.

При равенстве кода подмены 11 преобразования адреса-не происходит, как и при нулевом значении.

0

5

0

5

0

5

0

5

Устройство работает следующим образом.

При появлении одновременно нескольких запросов на входах 11 арбитра 1 запросов последний выдаёт ответный сигнал процессору по одному из выходов 16 и этим же сигналом открывает коммутатор 2 для пропускания адреса, требуемого данным процессором модуля памяти, Выбранньй коммутато ром 2 адрес модуля поступает на соответствующие управляющие входы мультиплексоров 4-6, Если все разряды кода подмены равны нулю, прямые выходы дешифратора 8 кода подмены, соответствующие кодам подмены, также находятся в нулевом состоянии. Эти выходы так подключены к информационным входам мультиплексоров 4-6, что на выходах последних образуется адрес требуемого модуля памяти без преобразования. То же самое происходит, если код подмены равен 111. Полученный адрес (без преобразования кодом подмены) поступа ет на дешифратор 7 обращения, который формирует .сигнал обращения на соответствующем вькоде 15. При этом элемент И 9 запрещает прохождение инверсного кода подмены на старшие информационные входы мультиплексоров 4-6 посредством запирания элементов И-НЕ 10.

При другом значении кода подмены (например, 001) при обращении к первому модулю памяти дешифратор 8 соответствующим выходом, значение которого станет равным 1, обеспечивает значение 1 на выходах мультиплексоров 4 и 5, В результате на вход дешифратора 7 обращения поступает код 111 и осуществляется обращение к седьмому (резервному) модулю вместо первого модуля. Аналогичный процесс происходит и при. любом другом значащем коде подмены. Формирование кода подмены может осуществлять ся одним из центральных процессоров,; на который разложены функции диаг- КОСТИКИ и выявления факта отказа модулей подмены.

Предложенное устройство при обращении с подменой обладает свойством симметрии, поскольку при формальном обращении к резервному модулю адрес 111 преобразуется в указанный в к.оде подмены. Такое преобразование осуществляется с помощью элементов И 9 и И-НЕ 10.

М

/5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приоритетного обращения к общей многомодульной памяти | 1988 |

|

SU1539786A1 |

| УСТРОЙСТВО ДЛЯ ОБРАЩЕНИЯ К ОБЩЕЙ ПАМЯТИ | 1992 |

|

RU2049348C1 |

| Микропроцессорная система | 1989 |

|

SU1686454A1 |

| Многопроцессорная вычислительная система | 1985 |

|

SU1277129A1 |

| Многопроцессорная система | 1989 |

|

SU1686455A1 |

| Устройство для приоритетного обращения к общей памяти | 1986 |

|

SU1425669A1 |

| Многопроцессорная вычислительная система | 1988 |

|

SU1569843A1 |

| Устройство межмодульной связи для системы коммутации сообщений | 1986 |

|

SU1388883A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1275442A1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных системах с общей многомодульной памятью. Целью изобретения является расширение функциональных возможностей устройства путем изменения адреса основного модуля памяти на адрес резервного при отказе основного модуля памяти. Устройство для обращения к общей многомодульной памяти содержит арбитр запросов, коммутатор, группу мультиплексоров по числу разрядов адреса модулей памяти, группу элементов И-НЕ по числу разрядов кода подмены, элемент И, дешифратор обращения и дешифратор кода подмены. При обращении к отказавшему модулю памяти в устройстве обеспечивается автоматическое преобразование адреса отказавшего модуля памяти в адрес резервного, а при формальном обращении по адресу резервного модуля его адрес преобразуется в код подмены или остается неизменным при нулевом коде подмены, свидетельствующем об исправности всех основных модулей. 1 ил.,1 табл.

| Устройство для формирования адреса | 1978 |

|

SU729589A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для приоритетного обращения к общей памяти | 1986 |

|

SU1425669A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1988-02-01—Подача