Изобретение относится к адаптивному корректирующему фильтру.

Из европейской патентной заявки EP-A-0305708 известен цифровой децимирующий фильтр, содержащийся в котором мультиплексор работает с частотой опроса подведенных к нему сигналов, в то время как подключенные к его выходам цепи передачи сигнала и связанные с ними подсхемы фильтра работают с половинной частотой опроса входного сигнала.

Далее из диссертации Тобиаса Гебхарда Нолля в Рурском университете, Бохум, 1989, под названием "Проект архитектуры и схемы цифрового адаптивного корректора для цифровой направленной радиосвязи с локально систолическим Carry-Save-Arrays в КМОП технологии", стр. 50, известна блок-схема цифрового Zero-Forcing-корректора, в которой коэффициенты фильтрации устройств умножения коэффициентов схемы фильтрации являются подстраиваемыми с помощью частичных корреляторов схемы подстройки коэффициентов в зависимости от сигнала ошибки и выходного сигнала блока принятия решения в качестве опорного сигнала, для образования приближенно инверсного фильтра к изменяющемуся во времени каналу. А также из известного устройства по US 5068873.

В основе изобретения лежит задача создания переключаемого недецимирующего/децимирующего адаптивного корректирующего фильтра, при котором проводка между схемой подстройки коэффициентов и схемой фильтрации с переменными коэффициентами относительно переключения между недецимирующим и децимирующим режимами работы является возможно полезной для обоих режимов работы и требуется только возможно малое количество выключателей или соответственно переключателей и при котором необходима возможно малая площадь кристалла и появляется возможно малая мощность потерь.

Задача согласно изобретению решается с помощью признаков, указанных в пункте 1 формулы изобретения.

Пункт 2 формулы изобретения направлен на предпочтительное выполнение изобретения.

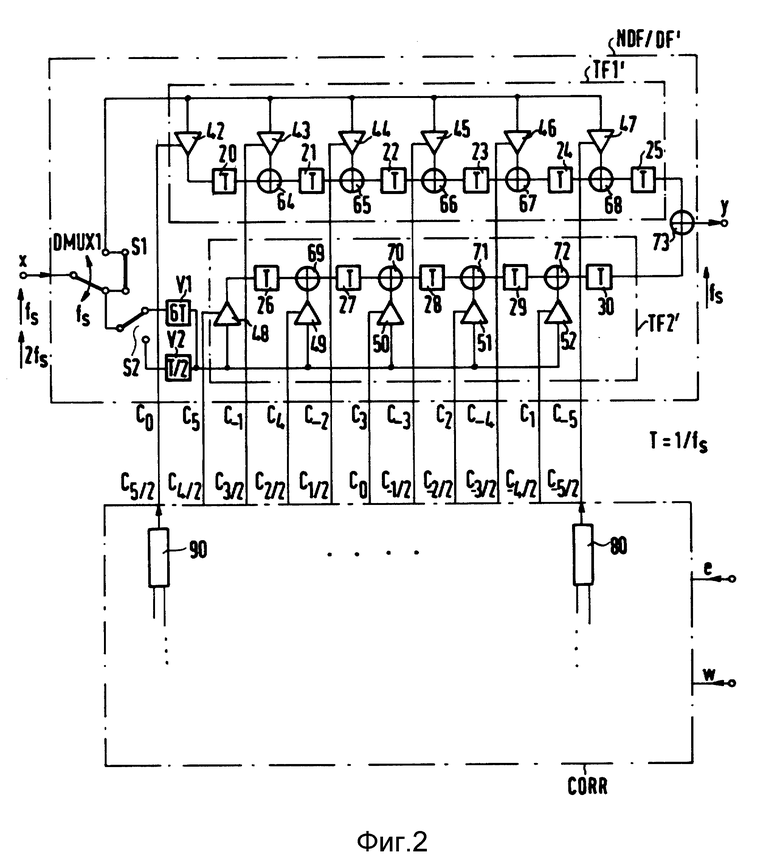

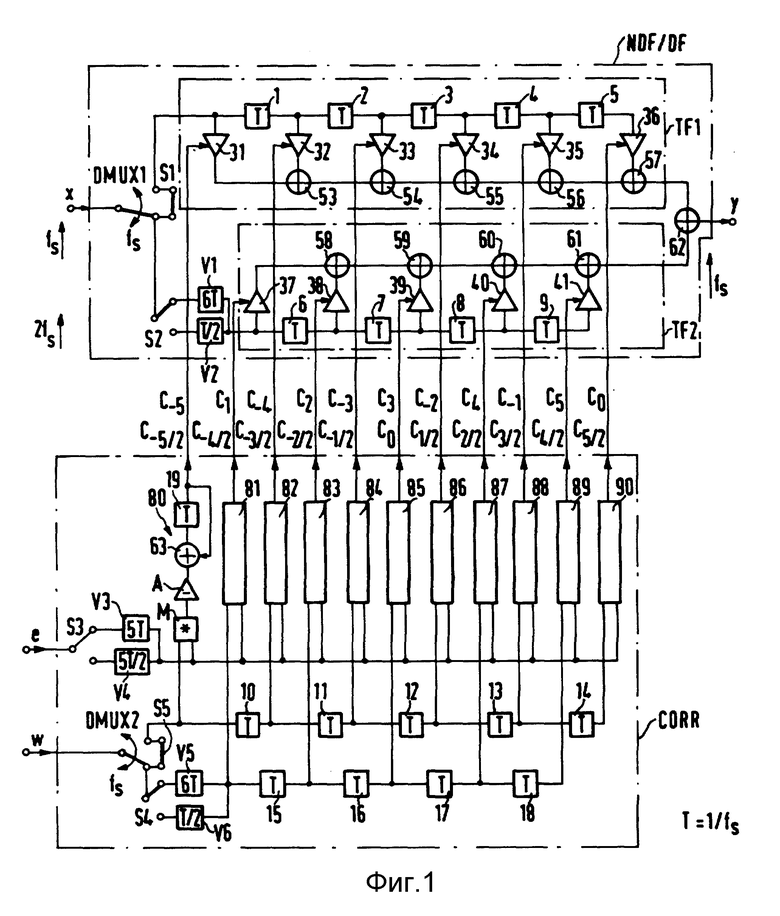

Ниже изобретение поясняется с помощью чертежей, на которых показано: фиг. 1 - блок-схема корректирующего фильтра согласно изобретению со структурой Serial-In/Parallel-Out и фиг. 2 - корректирующий фильтр согласно изобретению со структурой Parallel-In/Serial-Out.

На фиг. 1 показан переключаемый недецимирующий/децимирующий адаптивный корректирующий фильтр с N = 11 коэффициентами, который состоит из переключаемого недецимирующего/децимирующего фильтра с переменными коэффициентами NDF/DF и схемы подстройки коэффициентов CORR, причем фильтр NDF/DF состоит из частичного фильтра TF1 и другого частичного фильтра TF2, которые оба имеют структуру Serial-In/Parallel-Out. Первый частичный фильтр TF1 содержит последовательную схему звеньев задержки 1 . .. 5 с временем задержки T, причем 1/T соответствует частоте символов fS, шесть устройств умножения коэффициентов 31 ... 36 для изменяемых коэффициентов и пять сумматоров 53 ... 57. Другой частичный фильтр TF2 содержит последовательную схему из четырех звеньев задержки 6 ... 9, пять устройств умножения коэффициентов 37 ... 41 и четыре сумматора 58 ... 61. Входной сигнал фильтра TF1 при этом умножается в устройстве умножения коэффициентов 31 с соответствующим коэффициентом и подводится к последовательной схеме из пяти звеньев задержки 1 ...5. Сигналы выходов звеньев задержки 1 ... 5 умножаются в устройстве умножения коэффициентов 32 ... 36 с соответствующими коэффициентами и результат подводится соответственно к первому входу соответствующего сумматора сумматоров 53 ... 57. Второй вход сумматора 53 соединен с выходом устройства умножения коэффициентов 31, а другие вторые входы сумматоров 55 ... 57 связаны поочередно с выходом соответствующего сумматора и выход сумматора 57 соединен с входом сумматора 62. В случае частичного фильтра TF2 входной сигнал подводится к устройству умножения коэффициентов 37, а выходные сигналы звеньев задержки 6 . ..9 являются подводимыми по отдельности поочередно к устройствам умножения коэффициентов 38 ... 41. Первый вход сумматора 58 соединен с выходом устройства умножения коэффициентов 37, а первые входы остальных сумматоров 59 ... 61 соединены с выходом предыдущего сумматора и выход сумматора 61 соединен со вторым входом сумматора 62, выход которого представляет собой выход фильтра y. Вторые входы сумматоров 58 ... 61 соединены поочередно каждый с выходом устройства умножения коэффициентов 38 ... 41. Фильтр NDF/DF содержит демультиплексор DMUX1, на входе которого имеет место входной сигнал фильтра x, а первый выход которого соединен с входом фильтра TF1 и второй выход которого соединен с входом выключателя S2. Демультиплекстор DMUX1 является переключаемым с частотой символов fS, то есть каждое из обоих состояний переключения демультиплексора принимается на время 1/2 • fS, а его оба выхода являются шунтируемыми выключателем S1.

В недецимирующем режиме работы используемая частота опроса или фильтрации соответствует частоте символов fS (скорость в бодах). За счет такого опроса во всех практических применениях нарушается теорема отсчетов (Котельникова), результатом этого опять-таки являются высокие требования к применяемой фазе опроса. В децимирующем режиме по причинам упрощенной синхронизации частота опроса выбирается в большинстве случаев в соответствии с двойной частотой символов 2fS и соответствует тем самым теореме отсчетов. После корректирующего фильтрования частота опросов может быть снижена в большинстве случаев до частоты символов и система фильтрации может таким образом считаться децимирующим фильтром. Недостаток при этом заключается в некоторых нежелательных степенях свободы при установке коэффициентов фильтрации. Выходы демультиплексора DMUX1 шунтированы в недецимирующем режиме выключателем S1, то есть демультиплексор DMUX1 может переключаться дальше, как и в децимирующем режиме работы и не должен отключаться, а вход выключателя S2 через схему предварительной задержки V1 соединяется с входом частичного фильтра TF2 и устройства умножения коэффициентов 31 ... 36 параллельно поочередно снабжаются коэффициентами C-5 ... C0 и устройства умножения коэффициентов 37 ... 41 частичного фильтра TF2 поочередно снабжаются коэффициентами C1 . .. C5. В децимирующем режиме выключатель S1 открыт, то есть демультиплексор DMUX1 является активным, а выход переключателя S2 через схему предварительной задержки V2 соединен с входом частичного фильтра TF2 и устройства умножения коэффициентов 31 ... 36 частичного фильтра TF1 параллельно поочередно снабжаются коэффициентами C-5/2, C-3/2, ... C5/2 и устройства умножения коэффициентов 37 ... 41 частичного фильтра TF2 поочередно снабжаются коэффициентами C4/2, C-2/2, ... C4/2.

Схема подстройки коэффициентов CORR состоит из N = 11 частичных корреляторов 80 ... 90, цепи звеньев задержки 10 ... 14, последующей цепи звеньев задержки 15 ... 18, демультиплексора DMUX2, переключателей S3 и S4. выключателя 5 и звеньев предварительной задержки V3 ... V6. Сигнал ошибки e через переключатель S3, или через звено предварительной задержки V3, или через звено предварительной задержки V4 может подводиться ко всем первым входам частичных корреляторов 80 ... 90. Опорный сигнал W может подводиться к входу демультиплексора DMUX2, который переключается с частотой символов fS. В качестве опорного сигнала W при так называемом Zero-Forcing-способе используется выходной сигнал схемы принятия решения, которая снабжается выходным сигналом фильтра 7, а при так называемом Minimum-Mean-Squere Error-способе для этого используется входной сигнал фильтра x. Первый выход демультиплексора DMUX2 соединен с входом цепи звеньев задержки 10 ... 14, второй выход демультиплексора DMUX2 через переключатель S4, или через схему предварительной задержки V5, или через схему предварительной задержки V6 является соединяемым с входом цепи звеньев задержки 15 ... 18, а оба выхода демультиплексора DMUX2 в недецимирующем режиме работы шунтированы выключателем S5, а в децимирующем режиме работы не шунтированы. Второй вход частичного коррелятора 80 соединен со входом цепи звеньев задержки 10 ... 14, а выходы звеньев задержки 10 ... 14 поочередно соединены со вторым входом частичных корреляторов 80, 84 . . . 90. Вход цепи звеньев задержки 15 ... 18 соединен со вторым входом частичного коррелятора 81 и выходы звеньев задержки 15 ... 18 поочередно соединены каждый с одним из частичных корреляторов 83, 85 ... 89. Частичный коррелятор 80 представлен для примера подробно, причем оба входа частичного коррелятора 80 представляют собой входы устройства умножения M, после которого включены инвертирующий усилитель A, сумматор 63 и звено задержки 19, причем выход звена задержки 19 представляет собой выход частичного коррелятора и подведен обратно на второй вход сумматора 63, так что получается цифровой интегратор.

Если, например, сигнал ошибки e, как это описано в диссертации Тобиаса Нолля, состоит только из знакового бита, то каждый бит опорного сигнала w вместо устройства умножения M может связываться с сигналом e в схеме исключительного ИЛИ-EXOR. Выходы частичных корреляторов 80 ... 90 поставляют поочередно коэффициенты C-5, или соответственно C-5/2, C1, или соответственно C-4/2, C4, или соответственно C-3/2, C2, или соответственно C-2/2, C-3, или соответственно C-1/2, C3, или соответственно C0, C-2, или соответственно C1/2, C4, или соответственно C2/2, C-1, или соответственно C3/2, C5, или соответственно C4/2 и C0, или соответственно C5/2. Отсюда получается, что как в недецимирующем, так и в децимирующем режиме работы существуют одинаковые соединения между частичными корреляторами и устройствами умножения коэффициентов и не требуются никакие дополнительные выключатели или соответственно переключатели.

На фиг. 2 представлен другой соответствующий изобретению корректирующий фильтр, при котором вместо переключаемого недецимирующего/децимирующего фильтра NDF/DF использован переключаемый недецимирующий/децимирующий фильтр NDF/DF', который содержит частичный фильтр TF1' и частичный фильтр TF2', с соответственно выгодной для схемно-технической реализации Parallel-In/Serial-Out-структурой, и в котором проводка между фильтром NDF/DF' и схемой подстройки коэффициентов CORR является зеркальной относительно проводки между фильтром NDF/DF и схемой подстройки коэффициентов CORR, так что представленный в качестве примера на фиг. 2 последний частичный коррелятор 90 соединен с первым устройством умножения коэффициентов 42 для переменных коэффициентов и представленный в качестве примера на фиг. 2 первый частичный коррелятор 80 соединен с последним устройством умножения коэффициентов 47 для переменных коэффициентов первого частичного фильтра TF1'. Входной сигнал частичного фильтра TF1' при этом подводится ко всем устройствам умножения коэффициентов 42 ... 47 для переменных коэффициентов и входной сигнал частичного фильтра TF2' одновременно подводится ко всем устройствам умножения коэффициентов 48 . .. 52 для переменных коэффициентов. В частичном фильтре TF1' предусмотрена цепь из звеньев задержки 20 ... 25 и сумматоров 64 ... 68, причем цепь начинается звеном задержки 20 и соответственно поочередно присоединяется сумматор с включенным за ним звеном задержки. Выход первого устройства умножения коэффициентов 42 через звено задержки 20 соединен с первым входом сумматора 64 и один из выходов устройств умножения коэффициентов 43 ... 47 поочередно соединен с одним из вторых входов сумматоров 64 . ... 68. В частичном фильтре TF2' так же, как и в фильтре TF1', предусмотрены попеременно по порядку звенья задержки 26 ... 30 и сумматоры 69 ... 72, причем входной сигнал фильтра TF2' через первое устройство умножения коэффициентов 48 и звено задержки 26 подведен к первому входу сумматора 69 и соответственно выходной сигнал устройств умножения коэффициентов 41 ... 52 подведен ко второму входу сумматоров 69 ... 72. К устройствам умножения коэффициентов 42 ... 47 частичного фильтра TF1' поочередно подводятся коэффициенты C0, C-1, ... C-5 и к устройствам умножения коэффициентов 48 ... 52 частичного фильтра TF2' поочередно параллельно подводятся в недецимирующем режиме работы коэффициенты C5, C4, ... C1. В децимирующем режиме работы к устройствам умножения коэффициентов 42 ... 44 поочередно параллельно подводятся коэффициенты C5/2, C3/2, ... C-5/2 и к устройствам умножения коэффициентов 48 . . . 52 коэффициенты C4/2, C2/2, ... C-4/2. Проводка между фильтром NDF/DF' и схемой подстройки коэффициентов CORR относительно переключения между недецимирующим и децимирующим режимом работы является также инвариантной.

Наряду с, как правило, используемыми фильтрами с нечетным числом коэффициентов возможны также фильтры с четным числом коэффициентов и фильтр согласно изобретению, например, с N = 10 может быть легко выведен из фиг. 1 и 2 за счет того, что на фиг. 1 нет устройства умножения коэффициентов 31 и частичного коррелятора 80 и на фиг. 2 нет устройства умножения коэффициентов 47 и частичного коррелятора 80.

Недецимирующий фильтр с N коэффициентами может быть разделен на два аддитивно связанных со стороны выхода частичных фильтра, причем второй частичный фильтр является снабжаемым через схему предварительной задержки, обозначенную на фиг. 1 и фиг. 2 V1. Схема предварительной задержки в общем случае имеет время предварительной задержки, которое получается из суммы всех времен задержки первого частичного фильтра и дальнейшего времени задержки T. Время предварительной задержки схемы предварительной задержки составляет Int(N/2), причем Int(x) означает следующее по величине целое число x, если число коэффициентов первого частичного фильтра отличается от числа коэффициентов второго частичного фильтра самое большее на один коэффициент, то есть имеет место по возможности симметричное разделение между двумя частичными фильтрами. Для представленного на фиг. 1 и фиг. 2 фильтра с N = 11 коэффициентами следовательно получается время предварительной задержки для схемы предварительной задержки V1 равным 6T. В децимирующем режиме работы частичный фильтр TF1 и частичный фильтр TF2 попеременно снабжаются тактируемым с частотой символов fS демультиплексором DMUX1 на время 1/2 • fS входным сигналом фильтра x, который имеет двойную частоту символов 2fS, причем для частичного фильтра TF1 это происходит непосредственно, а для частичного фильтра TF2 через схему предварительной задержки с временем задержки T/2. Схема предварительной задержки V2 на фиг. 1 и 2 имеет поэтому также время задержки T/2.

В схеме подстройки коэффициентов CORR для предварительной задержки опорного сигнала w в соответствующих режимах работы получаются такие же времена предварительной задержки, как и при предварительной задержке второго частичного фильтра. Это означает для схемы предварительной задержки V5 на фиг. 1 и 2 время предварительной задержки, равное 6T, а для схемы предварительной задержки V6 на фигуре 1 и 2 время предварительной задержки, равное T/2.

Сигнал ошибки является свободно выбираемым в зависимости от желаемой корреляции между 0 и NT в недецимирующем режиме работы и между 0 и NT/2 в децимирующем режиме работы. Часто однако время предварительной задержки сигнала ошибки в недецимирующем режиме работы выбирают равным (N-Int(N/2))T и время предварительной задержки для предварительной задержки сигнала ошибки в децимирующем режиме работы выбирают равным (N-Int(N/2))T/2, чтобы учесть в равной степени так называемые предшествующие фронту сигнала выбросы в импульсном ответе подлежащего коррекции канала перед основным значением опроса и так называемые следующие за фронтом сигнала выбросы в импульсном ответе канала. Если в канале возникают, например, только запаздывающие эхо, то возможно является целесообразным выбирать более короткие времени предварительной задержки для сигнала ошибки e, чтобы вовлечь по возможности большее число следующих за фронтом сигнала выбросов в процесс коррекции. Для схемы предварительной задержки V3 на фиг. 1 и фиг. 2 отсюда получается время предварительной задержки, равное 5T и для схемы предварительной задержки V4 соответствующим образом время предварительной задержки, равное 5T/2.

Изобретение относится к адаптивному корректирующему фильтру с двумя частичными фильтрами (TF1, ТF2), коэффициенты фильтрации которых являются изменяемыми с помощью схемы подстройки коэффициентов (CORR), чтобы, например, образовать приближенно инверторный фильтр для изменяющегося во времени канала передачи, и при котором с помощью переключения является возможным, как недецимирующий режим работы, при котором частота опроса соответствует частоте символов, так и децимирующий режим работы, при котором частота опроса удовлетворяет теореме отсчетов. Технический результат: преимущество изобретения заключается, в частности, в том, что проводка между устройствами умножения коэффициентов( 31...41) схем частичных фильтров (TF1, TF2) и частичными корреляторами (80...90) схемы подстройки коэффициентов (СОRR) является инвариантной относительно переключения между двумя режимами работы, и, вследствие этого, для переключения требуется только небольшое количество выключателей или соответственно переключателей. 1 з.п.ф-лы, 2 ил.

| 5068873 A, 26.11.91 | |||

| Нолль Тобиас Гебхард | |||

| Диссертация "Проект архитектуры и схемы цифрового адаптивного корректора для цифровой направленной радиосвязи с локально систолическим Carry-Save-Arrays в КНОП технологии", Рурский университет, Бохард, 1989, с | |||

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

| Адаптивный корректор | 1986 |

|

SU1319295A1 |

| Адаптивный цифровой фильтр | 1986 |

|

SU1388896A1 |

| Адаптивный корректор сигнала | 1987 |

|

SU1432730A1 |

| Способ обработки цифровых сигналов по типу предпочтительно адаптивного трансверсального фильтра и устройство для его осуществления | 1984 |

|

SU1655309A3 |

| ОРИЕНТИРНЫЙ БУЙг !- "|.« | 0 |

|

SU331963A1 |

| US 4417314 A2, 22.11.83 | |||

| US 4747068 A, 24.05.88 | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ ЗАМОРАЖИВАНИЯ ГОРНЫХ ПОРОД | 0 |

|

SU201281A1 |

| US 5068873 A, 26.11.91 | |||

| ПРИСПОСОБЛЕНИЕ ДЛЯ ВЗЯТИЯ КРОВИ У СЕЛЬСКОХОЗЯЙСТВЕННЫХ ЖИВОТНЫХ | 0 |

|

SU305708A1 |

Авторы

Даты

1999-01-27—Публикация

1993-09-17—Подача