Изобретение относится к технике связи и вычислительной технике и может быть использовано в адаптивных системах передачи дискретной информации по каналам низкого качества.

Цель изобретения - повышение эффективности декодирования и быстродействия устройства.

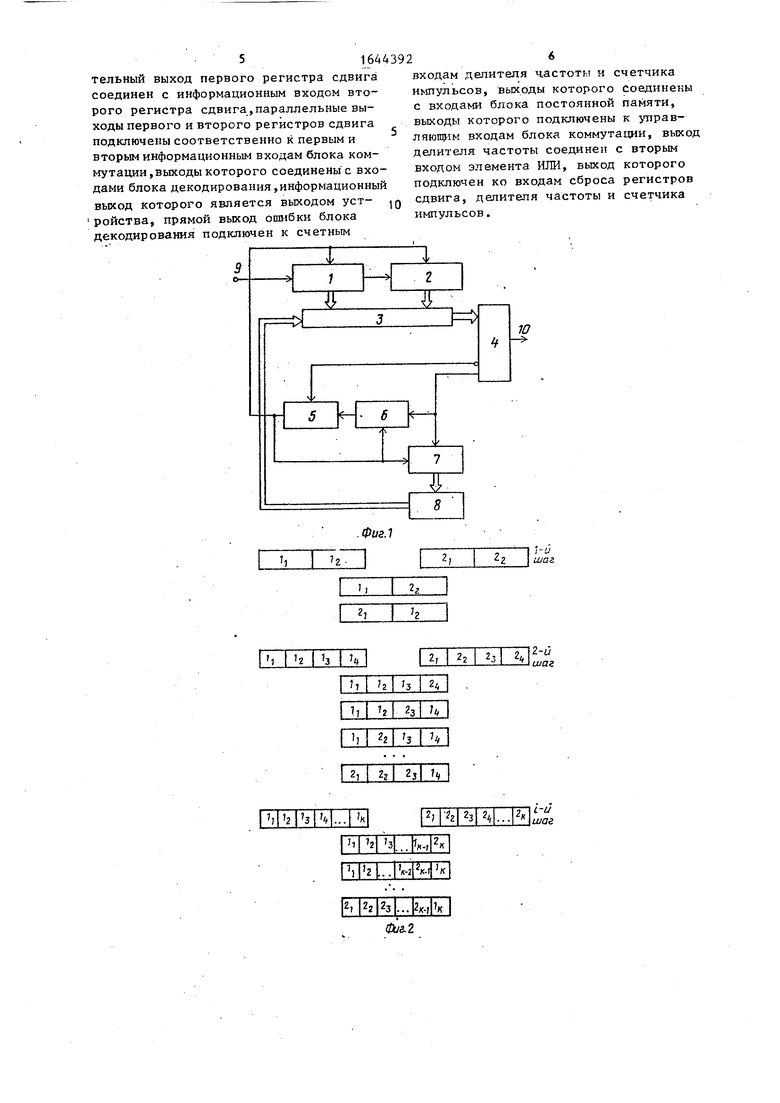

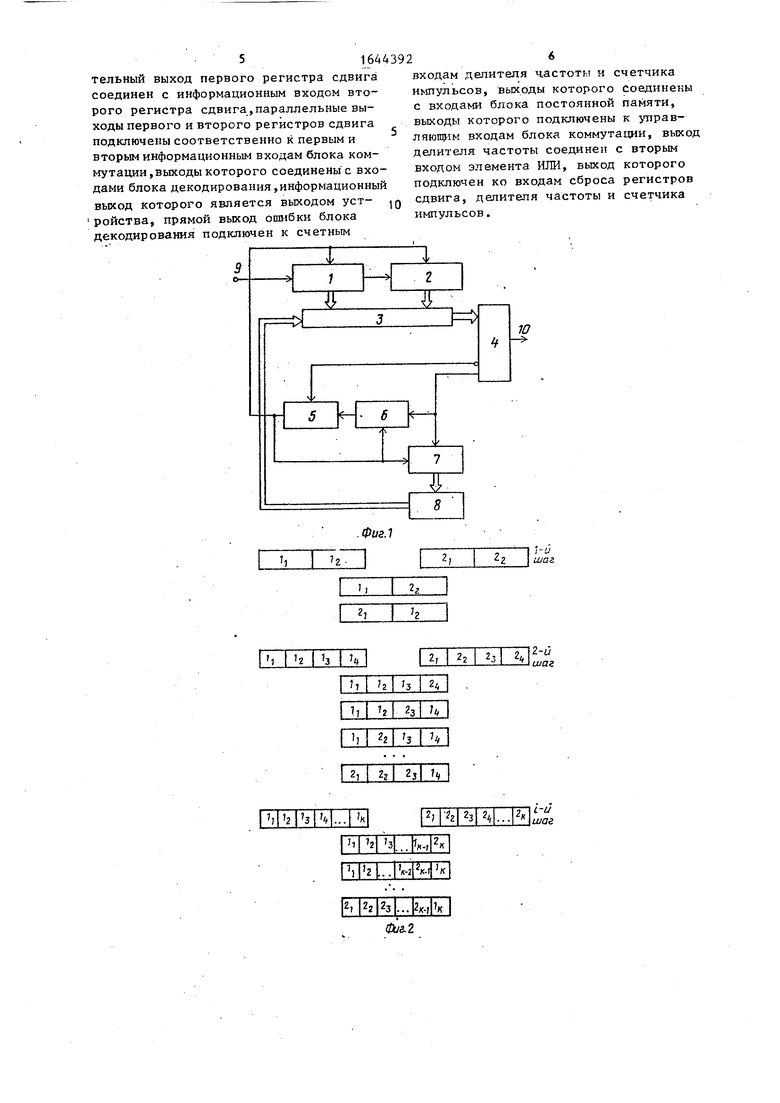

На фиг. 1 приведена функциональная схема устройства$ на фиг. 2 - принцип его работы.

Устройство защиты от ошибок содержит первый 1 и второй 2 регистры сдвига, блок 3 коммутации, блок 4 декодирования, элемент ИЛИ 5, делитель 6 частоты, счетчик 7 импульсов и блок 8 постоянной памяти. На фиг. 1 обозначены вход 9 и выход 10 ус-тройства-. Тактовые входы регистров 1, 2 и блока 4 (на фиг. 1 не показаны).

Блок 4 декодирования служит для декодирования используемого кода с обнаружением ошибок. Его прямой и инверсный выходы ошибки импульсные.

Делитель 6 частоты может быть реализован на счетчике.

Блок 3 коммутации может представлять собой п двухвходовых коммутаторов (п - длина кодового слова) каждый со своим управляющим входом.

Блок 8 постоянной памяти предназначен для хранения сигналов, управляющих работой блока 3 коммутации.

Устройство работает следующим образом.

В исходном состоянии устройства делитель 6 и счетчик 7 находятся в сброшенном состоянии. На управляющих входах блока 3 коммутации действуют управляющие сигналы, считываемые по первому адресу из блока 8 постоф

Јь Ј ОЭ СО N)

янной памяти, задаваемому нулевой комбинацией на выходах счетчика 7.

Первое и второе повторения кодовой комбинации, поступающей на вход 9, записываются в регистры 1 и 2.Блок 3 коммутации осуществляет коммутацию по управляющим сигналам, действующим на его управляющих входах из блока 8,своих вторых информационных входов (т.е. выходов второго регистра 2) с входами блока 4, где кодовая комбинация проверяется на наличие ошибок. Если в кодовой комбинации имеются ошибки, то блок 4 формирует га прямом выходе ошибки импупьсной сигнал, который занусгаег счегчик 7 я делитель 6, На выходе счетчика 7 появляется следующая комбинация, определяющая адрес считывания управляющих сигналов из блп а 8 постоянной памяти. Блок 3 коммутации по этим управляющим сигналам осуществляет коммутацию своих пер- вьгх информационных входов с входами блока 4, где (второе повторение) кодовая комбинация снова проверяет ,д на наличие ошибок. В случае наличия ошибок 1 л полном выходе ошибки блока 4 лотвляетсч управляющий сигнач, увеличивающий состояние счетчика 7 и делителя 6 ла единицу. По адресу, задаваемому счетчиком 7, из блока 8 постоянней памяти считываются следующие управляющие сигналы,, по которым блок 3 коммутации осуществляет коммутацию СБОИТ входов и выходов согласно схеме, представленной на фиг. 2. Кал видно из этой схемы, каждое повторение кодового слова делится на два сегмента (в нумерации на фиг. 2 индексы обозначают номера соответствующих сегментов в повороте) . После этого формируют две новые комбинации путем суперпозиций сегментов из разных повторений. При наличии в каждой из новых комбинаций ошибок их сегменты снова делятся на две части, и формируются четыре новых комбинации и т.д. На i-м шаге число,сегментов ,в каждом повторении К - 21.

Когда образованная в результате аких суперпозиций кодовая комбинаия не будет содержать ошибок, блок декодирования формирует на инверсном выходе ошибок управляющий сигнал, который поступает через элемент ИЛИ 5, сбрасывает делитель 6 и

0

5

0

счетчик 7 в исходное состояние и разрешает стирание информации из регист- .ров 1 и 2. Если же в случае перебора всех М возможных комбинаций суперпозиционных сегментов кодовых комбинаций для заданного числа ни одна из образованных кодовых комбинаций не удовлетворяет требованиям достоверности в блоке 4, то на выходе делителя 6, коэффициент деления которого равен М, появляется сигнал переполнения, который через элемент ИЛИ 5 сбрасывает в исходное состояние делитель 6, счетчик 7 и регистры 1 и 2, а на выход 10 кодовая комбинация не поступает (т.е. стирается).

Вероятность правильного декодирования кодовой комбинации с N-ro повтора определяется выражением i , ,Н

А

1 - (1 РПМ ) )

где Р„л, вероятность правильного

декодирования кодовой комбинации с 1-го повтора. Предельно достижимое значение Р, достигается при К п, т.е. когда длина каждого сегмента равна одному биту. При этом кодовая комбинация будет неправильно декодирована в случае, если хотя бы в одной одноименной позиции двух комбинаций будет ошибка. Отсюда вероятность правильного декодирования

П

Ч

- 1 - Р02 ,

0

5

0

5

где п Р

-длина кодовой комбинации,

-вероятность ошибки в дискретном канале.

Напрлмер, при РО 5 10 для получения Рпд 0,99 требуется шесть повторов кодовой комбинации вместо десяти у известных устройств.

Формула изобретения

Устройство защиты от ошибок, содержащее первый и второй регистры сдвига, блок постоянной памяти, блок декодирования, инверсный вход ошибки которого соединен с первым входом элемента ИЛИ, отличающее- с я тем, что, с целью повышения эффективности декодирования и быстродействия устройства, в него введены блок коммутации, счетчик импульсов и делитель частоты, информационный вход первого регистра сдвига является входом устройства, последова5164439

тельный выход первого регистра сдвига соединен с информационным входом второго регистра сдвига,параллельные выходы первого и второго регистров сдвига подключены соответственно к первым и вторым информационным входам блока коммутации, выходы которого соединены с входами блока декодирования,информационный выход которого является выходом уст- Q 1 ройства, прямой выход ошибки блока декодирования подключен к счетным

входам делителя частоты и счетчика импульсов, выходы которого соединены с входами блока постоянной памяти, выходы которого подключены к управляющим входам блока коммутации, выход делителя частоты соединен с вторым входом элемента ИЛИ, выход которого подключен ко входам сброса регистров сдвига, делителя частоты и счетчика импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

| Декодирующее устройство | 1988 |

|

SU1522415A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Устройство для мажоритарного декодирования при трехкратном повторении кодовой комбинации | 1985 |

|

SU1305876A1 |

| Устройство для обнаружения и исправления ошибок | 1989 |

|

SU1640814A1 |

| Декодирующее устройство | 1986 |

|

SU1381720A1 |

| Устройство для мажоритарного декодирования имитостойких циклических кодов при трехкратном повторении комбинации | 1990 |

|

SU1709538A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1990 |

|

RU2007866C1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

Изобретение относится к технике связи и вычислительной технике. Его использование в адаптивных системах передачи дискретной информации по каналам низкого качества позволяет повысить эффективность декодирования и быстродействие устройства. Устройство содержит регистры 1, 2 сдвига, блок 4 декодирования, элемент ИЛИ 5 и блок 8 постоянной памяти. Благодаря введению блока 3 коммутации, делителя 6 частоты и счетчика 7 импульсов в устройстве обеспечивается суперпозиция сегментов двух повторений кодового слова, что позволяет снизить общее число повторов. 2 ил.

| Устройство мажоритарного декодирования | 1982 |

|

SU1138947A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Декодирующее устройство @ -разрядного кода | 1985 |

|

SU1444963A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-04-23—Публикация

1989-04-11—Подача