Это изобретение связано с тестированием информации, записанной в память, которая объединена с микропроцессором.

Это может быть память, содержимое которой нельзя изменить (постоянное запоминающее устройство или ПЗУ (ROM)) или память, информацию в которой можно изменять, например электрически программируемое постоянное запоминающее устройство (ЭППЗУ (EPROM)) или оперативное запоминающее устройство (ОЗУ (RAM)).

Существует множество случаев, когда необходимо протестировать память, содержащую предварительно записанную информацию. Например, использование объединенных кредитных карт, известных также под названием интеллектуальных плат. Обычно память интеллектуальных плат тестируют, подсоединяя ее к читающему устройству, которое считывает содержимое памяти, проверяет на результат, возможно посредством проверки контрольной суммы или сравнением данных на выходе с данными, которые должны быть в действительности. Часто бывает, что память содержит конфиденциальную информацию и можно получить несанкционированный доступ к этой информации, просто задав тестирование памяти. Решение этой проблемы и является целью настоящего изобретения.

Заявка ЕР 0215464, опубликованная 25.03.87 кл. G 11 C 29/00, раскрывает интегральную схему, содержащую постоянное запоминающее устройство с запретом на вывод информации во внешний терминал, и схему сравнения для сравнения данных, считываемых из постоянного запоминающего устройства, с данными, подаваемыми во внешний терминал. Результат этого сравнения подается во внешний терминал.

В заявке ЕР 0267114, опубликованной 11.05.88 кл. G 11 C 29/00, описана интегральная схема, содержащая электрически программируемое запоминающее устройство. Данные из устройства ввода-вывода декодируются и сравниваются с выходным сигналом запоминающего устройства в компараторе.

В соответствии с первым объектом настоящего изобретения предлагается способ тестирования правильной работы изменяемой электрическим способом памяти, объединенной с интегральной схемой, согласно которому записывают данные тестирования в память, подают предварительно заданные данные на вход интегральной схемы, шифруют предварительно заданные данные, сравнивают данные, находящиеся внутри интегральной схемы, с данными тестирования, записанными в память, и выводят на выход интегральной схемы сигнал проверки, по которому можно проверить правильность работы функции записи и качество хранения в памяти.

Согласно способу по первому объекту настоящего изобретения шифрованные предварительны заданные данные пересылают на первый вход устройства сравнения, являющегося частью вышеупомянутой интегральной схемы, содержимое памяти пересылают на второй вход в вышеупомянутое устройство сравнения, и вышеупомянутым устройством сравнения сравнивают данные с двух входов и выдают на выход сигнал проверки, показывающий положительный или отрицательный результат сравнения.

При этом сигнал проверки могут выдавать на выход только с задержкой.

С помощью этого способа можно протестировать функцию записи и качество хранения в изменяемой электрическим способом памяти.

В соответствии со вторым объектом настоящего изобретения предлагается способ тестирования содержимого памяти, объединенной с микропроцессором в модуль, согласно которому подают предварительно заданные данные на вход этого модуля, шифруют предварительно заданные данные, сравнивают зашифрованные предварительно заданные данные внутри модуля с данными, хранящимися в памяти, и выводят на выход модуля сигнал проверки, показывающий положительный или отрицательный результат сравнения.

Согласно второму объекту изобретения шифрованные предварительно заданные данные подают на первый вход устройства сравнения, образующего часть вышеупомянутого модуля, содержимое памяти подают на второй вход вышеупомянутого устройства сравнения, а устройством сравнения сравнивают данные, поданные на его два входа и выдают сигнал проверки, показывающий положительный или отрицательный результат сравнения.

При этом вышеупомянутую память могут изменять электрическим способом и она имеет вход записи, на который подают вышеупомянутые данные тестирования и временно сохраняют в вышеупомянутой памяти перед передачей на второй вход вышеупомянутого устройства сравнения.

Сигнал проверки могут выдавать на выход только с задержкой.

В соответствии со вторым объектом настоящего изобретения данные, хранящиеся в памяти, могут быть данными, которые постоянно находятся в памяти или могут обновляться, как, например, данные программы и/или данные инициализации, или же это могут быть данные, записанные в память в качестве первой команды тестирования. Этим последним способом можно оттестировать функцию записи и качество хранения в памяти, изменяемой электрическим способом.

Модуль может быть интегральной схемой, включающей в себя память и микропроцессор, или может быть набором интегральных схем, физически соединенных герметиком или чем-либо подобным. Обычно модуль - это интегральная схема в интеллектуальной плате.

Использование описанного ранее способа внутреннего сравнения данных делает невозможным прямой доступ к содержимому памяти. Все, что есть на выходе - это сигнал проверки.

Возможно, что мошеннические попытки определить содержимое памяти могут быть осуществлены посредством автоматического последовательного ввода наборов данных тестирования, методично изменяющихся по содержанию до тех пор, пока сигнал на выходе не покажет, что данные памяти совпадают с данными, подаваемыми на вход. Существуют разные способы решения этой проблемы.

В соответствии с одним признаком настоящего изобретения микропроцессор запрограммирован таким образом, чтобы задерживать выход каждого сигнала подтверждения или неподтверждения. Задержка между следующими друг за другом сигналами может составлять несколько микросекунд или секунд. Тогда для методичной проверки потребуется очень большой промежуток времени.

Другой способ предотвращения мошеннических попыток тестирования памяти заключается в кодировании данных перед их сравнением, например, с помощью секретного алгоритма. И тогда данные на входе не будут иметь четкой взаимосвязи с содержимым памяти. Алгоритм или ключ может отличаться от проверки к проверке интеллектуальной платы.

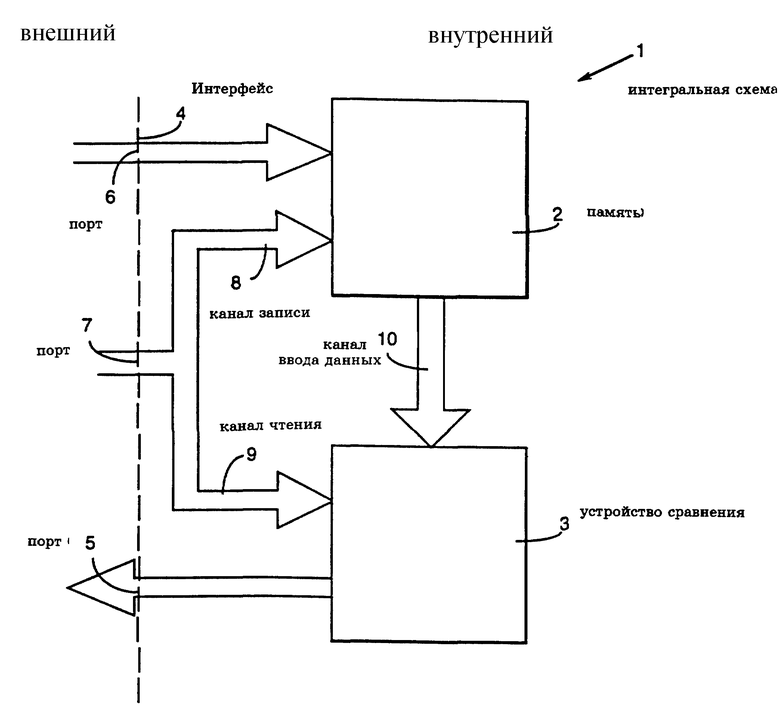

Настоящее изобретение будет далее описываться со ссылкой на сопровождающий его чертеж, являющийся блок-схемой, описывающей способ, в котором заключается настоящее изобретение.

На чертеже показаны интегральная схема 1 с памятью 2 ЭППЗУ (EPROM), которая содержит некоторые данные, и устройство сравнения 3, например микропроцессор, запрограммированный для сравнения данных. Интерфейс 4 связи с внешними устройствами показан пунктирной линией. Интерфейс 4 имеет три порта доступа 5, 6 и 7, через которые осуществляется передача сигналов в интегральную схему 1 и от нее. Внутренний канал доступа от порта 7 разделяется на два: канал записи 8, ведущий к памяти, и канал чтения 9, ведущий к устройству сравнения. Тестирование выполняется посредством ввода данных программы в интегральную схему и выполнением внутреннего сравнения с помощью устройства сравнения 3. Данные программы генерируются внешними устройствами (устройства не показаны) и передаются на устройство сравнения через порт ввода данных 10 и канал чтения 9. Тестируемые данные, записанные в память 2, передаются в устройство сравнения 3 через канал 10. В устройстве сравнения данные из двух каналов 9 и 10 сравниваются, а результат сравнения передается во внешнюю среду через порт 5 посредством сигнала проверки 3, показывающим результат сравнения. Этот способ не позволяет выводить информацию из интегральной схемы 1 и, таким образом, обеспечивает высокую степень защиты. Адрес чтения и сигналы управления могут генерироваться внешними устройствами (устройства не показаны), и их ввод можно осуществлять через адресный/управляющий порт 6 интерфейса 4. Адресные/управляющие сигналы передаются в память и управляют передачей данных из памяти 2 в устройство сравнения 3 стандартным способом.

В альтернативной реализации изобретения (не показано) порты 5 и 7 объединены в один мультиплексный порт чтения/записи, а порт 6 удален. Адресные и управляющие сигналы, которые ранее поступали через порт 6, передаются через мультиплексный порт 7 объединенного порта 5/7 и через канал доступа 8.

Данная схема также позволяет тестировать функцию записи в память, программируемую электрическим способом, тестируя данные, записанные в память 2 через порт ввода данных 7 интерфейса 4 и канал записи 8. Правильную запись можно затем проверить способом, описанным выше и опять же под управлением адресных/управляющих сигналов. В этом способе можно тестировать такие свойства как износостойкость, время хранения, надежность ячейки памяти.

Возможно получение несанкционированного доступа к содержимому памяти 2 посредством проведения тестирования всех возможных комбинаций памяти. Можно показать, что это усложняется при генерации нескольких сигналов ошибки. Например, если ошибка генерируется после чтения простого байта, состоящего из 8 битов, то для полного тестирования байта его нужно прочитать 256 раз. Если же сигнал ошибки генерируется только после 16-битового слова, то для тестирования слова потребуется его прочитать 65536 раз. Таким образом, для тестирования 32-битового слова его нужно прочитать 4294967296 раз. Применяя данную схему, исчерпывающее тестирование для получения содержимого памяти легко можно сделать невыполнимым.

Дополнительным средством для защиты является следующее средство - тестируемые слова должны превышать границы страницы памяти, возможно с помощью переменных значений.

Предлагаемый способ тестирования памяти, объединенной с микропроцессором, может найти применение, например, для использования в интеллектуальных платах. Способ включает сравнение выходной информации из памяти, подаваемой по каналу чтения, с сигналами шифрованных предварительно заданных данных, генерируемых извне и подаваемых через порт по каналу чтения. Сравнение осуществляют устройством сравнения, которое может быть, например, микропроцессором, запрограммированным для выполнения сравнения. На выходе устройства сравнения появляется простой сигнал проверки, который подают в порт. Сохраненные данные, записанные в памяти, могут постоянно храниться в памяти, например в постоянном запоминающем устройстве, или (если память изменяется электрическим способом) могут быть специально записаны в память для тестирования. 2 с. и 14 з.п. ф-лы, 1 ил.

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ГЛУБИНЫ ОБЪЕМНОЙ КАМЕРЫ ТАБЛЕТМАШИНЫ | 1965 |

|

SU215464A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКА ПОСТОЯННОЙ ПАМЯТИ | 0 |

|

SU235108A1 |

| ПРОЯВЛЯЮЩЕЕ (СТИРАЮЩЕЕ) УСТРОЙСТВО ДЛЯ АППАРАТУРЫ ТЕРМОПЛАСТИЧЕСКОЙ ЗАПИСИ | 0 |

|

SU267114A1 |

| Устройство для обнаружения ошибок в блоках памяти программ | 1988 |

|

SU1709395A1 |

| СПОСОБ ПОЛУЧЕНИЯ ЗАМЕЩЕННЫХ БИЦИКЛИЧЕСКИХ ЛАКТОН-ЛАКТАМНЫХ СОЕДИНЕНИЙ | 0 |

|

SU320489A1 |

Авторы

Даты

2000-09-10—Публикация

1995-07-12—Подача