Изобретение относится к цифровым системам, а более конкретно к способу определения состояния совместно используемого ресурса.

Во многих цифровых системах один системный ресурс должен быть совместно использован многими компонентами системы. Например, в цифровом вычислительном комплексе обычным является то, что центральный процессор совместно использует запоминающее устройство с подсистемой видеодисплея или даже с другим центральным процессором. Такая ситуация требует арбитражного алгоритма для того, чтобы решить, которому из потенциально многих запросов ресурса будет дано разрешение доступа к совместно используемому ресурсу. Кроме того, при использовании одного ресурса для передачи информации от одного компонента системы (записывающего "производителя") к другому (считывающему "потребителю") информация, сохраненная в ресурсе производителем, должна быть сохранена до тех пор, пока потребитель ею не воспользуется. Это особенно актуально, если другие производители конкурируют для записи информации в тот же ресурс. В соответствии с этим, как только производитель записал информацию в совместно используемый ресурс, другим производителям не должна быть разрешена запись в этот ресурс до тех пор, пока эта информация не будет считана потребителем.

Традиционная схема координации доступа к совместно используемому системному ресурсу включает в себя применение регистра состояния (или "семафора"), связанного с ресурсом, который представляется полным в одном (высоком) логическом состоянии и представляется пустым в другом (низком) логическом состоянии. Такой семафор, как правило, получают при использовании стандартного триггера. Например, семафор может быть использован для регулирования обмена информацией через совместно используемый ресурс, способный хранить данные. Такой семафор будет представлять, что ресурс полон, когда "установлен в состояние "1"" производителем, который только что записал данные в ресурс (показывая, что данные теперь могут быть считаны потребителем), и будет представлять что ресурс пуст, если потребителем, который только что считал данные из ресурса, "занесен "0"" (показывая, что производителем теперь могут быть записаны новые данные).

Алгоритм семафора удовлетворителен, пока все изготовители и потребители работают в одной тактовой области, что и семафор. При однородной тактовой области, производители и потребители могут проверять значение семафора, не интересуясь тем, что сигнал обновления данных еще не принят семафором, или тем, что значение семафора обновленных данных еще не передано всем производителям или потребителям. Иными словами, в однородной тактовой области нет трудности в гарантировании того, что значение семафора отражает истинное состояние совместно используемого ресурса.

Для синхронизации сигналов между подсистемами, работающими в однородной тактовой области, нет необходимости. Однако если подсистемы работают в разных тактовых областях, то сигналы от одной подсистемы к другой должны быть синхронизированы.

В соответствии с этим, если подсистемы совместно используют ресурс, но работают в разных тактовых областях, то возникают проблемы. Традиционные алгоритмы семафора должны преодолевать трудности, связанные с множеством тактовых областей, например, 1) которая тактовая область будет использовать семафор; 2) как сигналы установки в состояние "1" и занесения "0" формируются в различных тактовых областях; 3) отражает ли значение семафора действительное состояние совместно используемого ресурса, так что подсистема может проверить такое состояние; и 4) как соответствующая схемная логика проверяется для исправления на стадии проектирования.

В простой системе, содержащей один производитель и один потребитель, которые совместно используют ресурс, но работают в разных тактовых областях, традиционный алгоритм семафора позволяет три возможных выбора тактовой области для семафора. Во-первых, семафор может быть расположен в тактовой области производителя. В такой конфигурации производитель имеет немедленный синхронный доступ к семафору, отражающему состояние совместно используемого ресурса; таким образом, сигнал (производителя) установки в состояние "1" синхронен семафору. Однако сигнал (потребителя) занесения "0" не синхронен семафору. Следовательно, сигнал (потребителя) занесения "0" должен быть синхронизирован с тактовыми импульсами производителя для обновления семафора, а новое значение семафора должно быть обратно синхронизировано с тактовой областью потребителя, чтобы позволить потребителю проверить состояние ресурса.

Имеется задержка, связанная с синхронизацией сигнала (потребителя) занесения "0" с тактовой областью семафора (и производителя), и другая задержка, связанная с синхронизацией нового значения семафора обратно в тактовой области потребителя. Эти задержки создают окно времени, если значение семафора, проверенное потребителем, не является действительным (не отражающим действительного состояния ресурса). Если потребитель проверяет семафор в течение этого окна времени, потребитель обнаружит состояние установки в состояние "1", которое не является действительным. Чтобы помешать потребителю преждевременно проверять семафор, потребитель должен быть задержан на достаточно длительное время, чтобы позволить своему собственному сигналу обновления вернуть семафор в состояние "0", а также позволить новому, возвращенному в исходное состояние, значению семафора достичь потребителя.

При втором выборе тактовых областей для семафора необходимо использовать тактовую область потребителя. Выбор использования тактовой области потребителя предлагает обратный сценарий проблемы задержки: производитель должен быть задержан на достаточно длительное время, чтобы помешать ему преждевременно проверять семафор для предотвращения возможности обнаружения недействительного состояния занесения "0".

При третьем выборе тактовых областей для семафора необходимо использовать третью тактовую область, которая отличается от тактовой области производителя или потребителя. В этом случае производитель и потребитель должны быть задержаны для предотвращения преждевременной проверки семафора. Таким образом, не зависимо от выбора тактовой области для семафора, производитель или потребитель или оба должны быть замедлены задержкой, чтобы позволить синхронизацию.

Дополнительные трудности возникают, если для записи данных в совместно используемый ресурс необходимо более одного производителя для записи данных в совместно используемый ресурс или более одного потребителя для считывания данных из совместно используемого ресурса. Должен быть введен арбитр, который бы управлял записями, делаемыми производителями, и считываниями, осуществляемыми потребителями. Роль такого арбитра заключается в координации прав доступа среди производителей и потребителей для предотвращения режима соперничества, аналогичного режиму соперничества, возникающему вследствие того, что два или более производителей одновременно делают запись в один ресурс, или из-за того, что два или более потребителей одновременно осуществляют считывание из одного ресурса. Традиционный арбитр принимает множество запросов на ресурс и разрешает доступ только одному просителю, который затем становится текущим пользователем. Арбитр не удовлетворит другой запрос на ресурс до тех пор, пока его не освободит текущий пользователь.

В системе, имеющей множество производителей, арбитр необходим для регулирования доступа производителя для записи в совместно используемый ресурс. В системе, имеющей множество потребителей, арбитр необходим для регулирования доступа потребителя для считывания из совместно используемого ресурса. В системе, имеющей множество производителей и множество потребителей, необходимо два арбитра: один для регулирования доступа производителей, а другой для регулирования доступа потребителей.

В случае множества тактовых областей, требующем арбитража, проблема синхронизации становится более сложной. Когда арбитр, в конце концов, удовлетворяет запрос производителя или потребителя на доступ совместно используемого ресурса, производитель или потребитель должны гарантировать, что значение семафора отражает действительное состояние ресурса.

Для более подробного рассмотрения этой проблемы допустим, что один производитель заканчивает запись данных в совместно используемый ресурс, посылает сигнал обновления для установки семафора в состояние "1" и дает права доступа к совместно используемому ресурсу. Допустим также, что после этого арбитр обнаруживает освобождение ресурса и удовлетворяет требование второго производителя на доступ. Между тем, сигнал обновления (первого производителя), который должен быть синхронизирован с тактовой областью семафора, установит семафор в состояние "1". Значение семафора должно быть, в конечном счете, синхронизировано с тактовыми импульсами второго производителя, чтобы позволить второму производителю достоверно проверить состояние ресурса. В то время когда арбитр удовлетворил запрос второго производителя на ресурс, значение семафора, проверенное вторым производителем, не может отражать действительного состояния совместно используемого ресурса, если для того, чтобы значение семафора было синхронизировано в тактовой области второго производителя, не прошло достаточно времени. И в этом случае традиционное решение этой проблемы должно вводить задержку.

Проблема синхронизации была решена путем введения задержки в арбитражную логику для гарантии того, что время между освобождением доступа одним производителем и обнаружением разрешения, данное арбитром, другим производителем по меньшей мере равно времени между выдачей одним производителем сигнала обновления семафору и конечной синхронизацией вновь обновленного значения семафора в тактовой области другого производителя. В системах, имеющих более двух производителей или более двух потребителей, требуемая арбитражная задержка должна быть сделана, принимая во внимание самую медленную тактовую область, для гарантии того, чтобы самый медленный производитель или потребитель преждевременно не проверял состояние совместно используемого ресурса.

Одним недостатком традиционного алгоритма семафора с арбитражной логикой является то, что производительность системы ухудшается требуемой задержкой. При ее увеличении и необходимости быстродействующих вычислительных систем любое ухудшение быстродействия системы является большим недостатком.

Были сделаны попытки оптимизировать вводимые задержки, но такие попытки, даже если и были успешными, были необычайно сложными и трудными для осуществления. Таким образом, другим недостатком известных алгоритмов семафора с арбитражной логикой является то, что оптимизация требуемых задержек трудна для исполнения.

Еще одним недостатком алгоритма семафора с арбитражной логикой является то, что на стадии проектирования необходим сложный анализ для определения наименьшего времени возможной задержки, необходимого для преодоления наихудшего сценария. Сложность требуемого анализа экспоненциально растет с увеличением числа производителей или потребителей, работающих в разных тактовых областях, и дополнительно усложняется, если дополнительные разные тактовые области содержат семафор или арбитр или семафор и арбитр.

Однако важнейшим является недостаток, который заключается в том, что алгоритмы семафора с арбитражной логикой трудны для подтверждения правильности на стадии проектирования. Эта проблема ощутимее всего в тех случаях, где соответствующая логика представляет собой один небольшой элемент большой интегральной схемы. Вследствие большой стоимости, связанной с производством больших интегральных схем, для предотвращения очень дорогих ошибок большое внимание на стадии проектирования уделяется верификации правильности всей логики.

Указанные недостатки преодолены в нижеприведенных способах, реализуемых с использованием нижеприведенных устройств.

Способ определения состояния ресурса цифровой системы, в которой первая подсистема, работающая синхронно с первыми тактовыми импульсами, записывает данные в указанный ресурс, вторая подсистема, работающая синхронно со вторыми тактовыми импульсами, считывает данные из указанного ресурса, причем указанные вторые тактовые импульсы асинхронны указанным первым тактовым импульсам и указанный ресурс не доступен для записи дополнительных данных из указанной первой подсистемы до тех пор, пока записанные прежде данные не будут считаны из указанного ресурса указанной второй подсистемой, причем формируют первый количественный параметр, представляющий число доступов записи в указанный ресурс, сделанных указанной первой подсистемой, причем указанный первый количественный параметр формируют синхронно с указанными первыми тактовыми импульсами, формируют второй количественный параметр, представляющий число доступов считывания из указанного ресурса, сделанных указанной второй подсистемой, причем указанный второй количественный параметр формируют синхронно с указанными вторыми тактовыми импульсами, синхронизируют указанный первый количественный параметр с указанными вторыми тактовыми импульсами для формирования третьего количественного параметра, синхронизируют указанный второй количественный параметр с указанными первыми тактовыми импульсами для формирования четвертого количественного параметра, сравнивают указанный первый количественный параметр с указанным четвертым количественным параметром для формирования первого сигнала доступности ресурса для указанной первой подсистемы, причем указанный первый сигнал доступности ресурса активен, если указанный первый количественный параметр равен указанному четвертому количественному параметру, при этом указанный первый сигнал доступности ресурса формируют синхронно с указанными первыми тактовыми импульсами и сравнивают указанный второй количественный параметр и указанный третий количественный параметр для формирования второго сигнала доступности ресурса для указанной второй подсистемы, причем указанный второй сигнал доступности ресурса активен, если указанный второй количественный параметр отличается от указанного третьего количественного параметра, при этом указанный второй сигнал доступности ресурса формируют синхронно с указанными вторыми тактовыми импульсами. Предпочтительно, указанный первый количественный параметр, указанный второй количественный параметр, указанный третий количественный параметр и указанный четвертый количественный параметр представляют значение нуля или единицы, причем указанное значение изменяется от единицы к нулю или от нуля к единице при наличии приращения, указанный первый сигнал доступности ресурса формируют в результате операции исключающее ИЛИ, которой подвергают указанный первый количественный параметр и указанный четвертый количественный параметр, а указанный второй сигнал доступности ресурса формируют в результате операции исключающее ИЛИ, которой подвергают указанный второй количественный параметр и указанный третий количественный параметр.

Способ определения состояния ресурса цифровой системы, в которой первая подсистема, работающая синхронно с первыми тактовыми импульсами, записывает данные в указанный ресурс, вторая подсистема, работающая синхронно со вторыми тактовыми импульсами, считывает данные из указанного ресурса, причем указанные вторые тактовые импульсы асинхронны указанным первым тактовым импульсам и указанный ресурс не доступен для записи дополнительных данных из указанной первой подсистемы до тех пор, пока записанные прежде данные не будут считаны из указанного ресурса указанной второй подсистемой, в которой третья подсистема указанной цифровой системы работает синхронно с третьими тактовыми импульсами, причем указанные третьи тактовые импульсы асинхронны указанным первым тактовым импульсам и указанным вторым тактовым импульсам, указанная третья подсистема записывает данные в указанный ресурс, причем указанный ресурс не доступен для записи дополнительных данных из указанной третьей подсистемы до тех пор, пока записанные прежде данные не будут считаны из указанного ресурса указанной второй подсистемой, при этом формируют первый количественный параметр, представляющий число доступов записи в указанный ресурс, сделанных указанной первой подсистемой, причем указанный первый количественный параметр формируют синхронно с указанными первыми тактовыми импульсами, формируют второй количественный параметр, представляющий число доступов считывания из указанного ресурса, сделанных указанной второй подсистемой, причем указанный второй количественный параметр формируют синхронно с указанными вторыми тактовыми импульсами, синхронизируют указанный первый количественный параметр с указанными вторыми тактовыми импульсами для формирования третьего количественного параметра, синхронизируют указанный второй количественный параметр с указанными первыми тактовыми импульсами для формирования четвертого количественного параметра, формируют пятый количественный параметр, представляющий число доступов записи в указанный ресурс, сделанных указанной третьей подсистемой, причем указанный пятый количественный параметр формируют синхронно с указанными третьими тактовыми импульсами, синхронизируют указанный первый количественный параметр с указанными третьими тактовыми импульсами для формирования шестого количественного параметра, синхронизируют указанный второй количественный параметр с указанными третьими тактовыми импульсами для формирования седьмого количественного параметра, синхронизируют указанный пятый количественный параметр с указанными первыми тактовыми импульсами для формирования восьмого количественного параметра, синхронизируют указанный пятый количественный параметр с указанными вторыми тактовыми импульсами для формирования девятого количественного параметра, формируют первый сигнал доступности ресурса посредством сравнения суммы указанного первого количественного параметра и указанного восьмого количественного параметра с указанным четвертым количественным параметром, причем указанный первый сигнал доступности ресурса активен, если указанная сумма указанного первого количественного параметра и указанного восьмого количественного параметра равна указанному четвертому количественному параметру, при этом указанный первый сигнал доступности ресурса формируют синхронно с указанными первыми тактовыми импульсами, формируют второй сигнал доступности ресурса посредством сравнения суммы указанного третьего количественного параметра и указанного девятого количественного параметра с указанным вторым количественным параметром, причем указанный второй сигнал доступности ресурса активен, если указанная сумма указанного третьего количественного параметра и указанного девятого количественного параметра отличается от указанного второго количественного параметра, при этом указанный второй сигнал доступности ресурса формируют синхронно с указанными вторыми тактовыми импульсами и формируют третий сигнал доступности ресурса посредством сравнения суммы указанного пятого количественного параметра и указанного шестого количественного параметра с указанным седьмым количественным параметром, причем указанный третий сигнал доступности ресурса активен, если указанная сумма указанного пятого количественного параметра и указанного шестого количественного параметра равна указанному седьмому количественному параметру, при этом указанный третий сигнал доступности ресурса формируют синхронно с указанными первыми тактовыми импульсами.

Способ определения состояния ресурса цифровой системы, в которой первая подсистема, работающая синхронно с первыми тактовыми импульсами, записывает данные в указанный ресурс, вторая подсистема, работающая синхронно со вторыми тактовыми импульсами, считывает данные из указанного ресурса, причем указанные вторые тактовые импульсы асинхронны указанным первым тактовым импульсам, третья подсистема указанной цифровой системы работает синхронно с третьими тактовыми импульсами, а указанные третьи тактовые импульсы асинхронны указанным первым тактовым импульсам и указанным вторым тактовым импульсам, указанная третья подсистема записывает данные в указанный ресурс, четвертая подсистема указанной цифровой системы работает синхронно с указанными четвертыми тактовыми импульсами, при этом указанные четвертые тактовые импульсы асинхронны указанным первым тактовым импульсам, указанным вторым тактовым импульсам и указанным третьим тактовым импульсам, указанная четвертая подсистема считывает данные из указанного ресурса, указанный ресурс не доступен для записи дополнительных данных из указанной первой подсистемы или из указанной третьей подсистемы до тех пор, пока записанные прежде данные не будут считаны из указанного ресурса указанной второй подсистемой или указанной четвертой подсистемой, при этом формируют первый количественный параметр, представляющий число доступов записи в указанный ресурс, сделанных указанной первой подсистемой, причем указанный первый количественный параметр формируют синхронно с указанными первыми тактовыми импульсами, формируют второй количественный параметр, представляющий число доступов считывания из указанного ресурса, сделанных указанной второй подсистемой, причем указанный второй количественный параметр формируют синхронно с указанными вторыми тактовыми импульсами, синхронизируют указанный первый количественный параметр с указанными вторыми тактовыми импульсами для формирования третьего количественного параметра, синхронизируют указанный второй количественный параметр с указанными первыми тактовыми импульсами для формирования четвертого количественного параметра, формируют пятый количественный параметр, представляющий число доступов записи в указанный ресурс, сделанных указанной третьей подсистемой, причем указанный пятый количественный параметр формируют синхронно с указанными третьими тактовыми импульсами, синхронизируют указанный первый количественный параметр с указанными третьими тактовыми импульсами для формирования шестого количественного параметра, синхронизируют указанный второй количественный параметр с указанными третьими тактовыми импульсами для формирования седьмого количественного параметра, синхронизируют указанный пятый количественный параметр с указанными первыми тактовыми импульсами для формирования восьмого количественного параметра, синхронизируют указанный пятый количественный параметр с указанными вторыми тактовыми импульсами для формирования девятого количественного параметра, формируют десятый количественный параметр, представляющий число доступов считывания из указанного ресурса, сделанных указанной четвертой подсистемой, причем указанный десятый количественный параметр формируют синхронно с указанными четвертыми тактовыми импульсами, синхронизируют указанный первый количественный параметр с указанными четвертыми тактовыми импульсами для формирования одиннадцатого количественного параметра, синхронизируют указанный второй количественный параметр с указанными четвертыми тактовыми импульсами для формирования двенадцатого количественного параметра, синхронизируют указанный пятый количественный параметр с указанными четвертыми тактовыми импульсами для формирования тринадцатого количественного параметра, синхронизируют указанный десятый количественный параметр с указанными первыми тактовыми импульсами для формирования четырнадцатого количественного параметра, синхронизируют указанный десятый количественный параметр с указанными вторыми тактовыми импульсами для формирования пятнадцатого количественного параметра, синхронизируют указанный десятый количественный параметр с указанными третьими тактовыми импульсами для формирования шестнадцатого количественного параметра, формируют первый сигнал доступности ресурса посредством сравнения суммы указанного первого количественного параметра и указанного восьмого количественного параметра с суммой указанного четвертого количественного параметра и указанного четырнадцатого количественного параметра, причем указанный первый сигнал доступности ресурса активен, если указанная сумма указанного первого количественного параметра и указанного восьмого количественного параметра равна указанной сумме указанного четвертого количественного параметра и указанного четырнадцатого количественного параметра, при этом указанный первый сигнал доступности ресурса формируют синхронно с указанными первыми тактовыми импульсами, формируют второй сигнал доступности ресурса посредством сравнения суммы указанного третьего количественного параметра и указанного девятого количественного параметра с суммой указанного второго количественного параметра и указанного пятнадцатого количественного параметра, причем указанный второй сигнал доступности ресурса активен, если указанная сумма указанного третьего количественного параметра и указанного девятого количественного параметра отличается от указанной суммы указанного второго количественного параметра и указанного пятнадцатого количественного параметра, при этом указанный второй сигнал доступности ресурса формируют синхронно с указанными вторыми тактовыми импульсами, формируют третий сигнал доступности ресурса посредством сравнения суммы указанного пятого количественного параметра и указанного шестого количественного параметра с суммой указанного седьмого количественного параметра и указанного шестнадцатого количественного параметра, причем указанный третий сигнал доступности ресурса активен, если указанная сумма указанного пятого количественного параметра и указанного шестого количественного параметра равна указанной сумме указанного седьмого количественного параметра и указанного шестнадцатого количественного параметра, при этом указанный третий сигнал доступности ресурса формируют синхронно с указанными третьими тактовыми импульсами и формируют четвертый сигнал доступности ресурса посредством сравнения суммы указанного одиннадцатого количественного параметра и указанного тринадцатого количественного параметра с суммой указанного десятого количественного параметра и указанного двенадцатого количественного параметра, причем указанный четвертый сигнал доступности ресурса активен, если указанная сумма указанного одиннадцатого количественного параметра и указанного тринадцатого количественного параметра равна указанной сумме указанного десятого количественного параметра и указанного двенадцатого количественного параметра, при этом указанный четвертый сигнал доступности ресурса формируют синхронно с указанными четвертыми тактовыми импульсами.

Способ определения состояния ресурса цифровой системы, в которой первая подсистема, работающая синхронно с первыми тактовыми импульсами, записывает данные в указанный ресурс, вторая подсистема, работающая синхронно со вторыми тактовыми импульсами, считывает данные из указанного ресурса, причем указанные вторые тактовые импульсы асинхронны указанным первым тактовым импульсам, третья подсистема указанной цифровой системы работает синхронно с третьими тактовыми импульсами, при этом указанные третьи тактовые импульсы асинхронны указанным первым тактовым импульсам и указанным вторым тактовым импульсам, указанная третья подсистема считывает данные из указанного ресурса, указанный ресурс не доступен для записи дополнительных данных из указанной первой подсистемы до тех пор, пока записанные прежде данные не будут считаны из указанного ресурса указанной второй подсистемой или указанной третьей подсистемой, при этом формируют первый количественный параметр, представляющий число доступов записи в указанный ресурс, сделанных указанной первой подсистемой, причем указанный первый количественный параметр формируют синхронно с указанными первыми тактовыми импульсами, формируют второй количественный параметр, представляющий число доступов считывания из указанного ресурса, сделанных указанной второй подсистемой, причем указанный второй количественный параметр формируют синхронно с указанными вторыми тактовыми импульсами, синхронизируют указанный первый количественный параметр с указанными вторыми тактовыми импульсами для формирования третьего количественного параметра, синхронизируют указанный второй количественный параметр с указанными первыми тактовыми импульсами для формирования четвертого количественного параметра, формируют пятый количественный параметр, представляющий число доступов считывания из указанного ресурса, сделанных указанной третьей подсистемой, причем указанный пятый количественный параметр формируют синхронно с указанными третьими тактовыми импульсами, синхронизируют указанный первый количественный параметр с указанными третьими тактовыми импульсами для формирования шестого количественного параметра, синхронизируют указанный второй количественный параметр с указанными третьими тактовыми импульсами для формирования седьмого количественного параметра, синхронизируют указанный пятый количественный параметр с указанными первыми тактовыми импульсами для формирования восьмого количественного параметра, синхронизируют указанный пятый количественный параметр с указанными вторыми тактовыми импульсами для формирования девятого количественного параметра, формируют первый сигнал доступности ресурса посредством сравнения указанного первого количественного параметра с суммой указанного четвертого количественного параметра и указанного восьмого количественного параметра, причем указанный первый сигнал доступности ресурса активен, если указанный первый количественный параметр равен указанной сумме указанного четвертого количественного параметра и указанного восьмого количественного параметра, при этом указанный первый сигнал доступности ресурса формируют синхронно с указанными первыми тактовыми импульсами, формируют второй сигнал доступности ресурса посредством сравнения указанного третьего количественного параметра с суммой указанного второго количественного параметра и указанного девятого количественного параметра, причем указанный второй сигнал доступности ресурса активен, если указанный третий количественный параметр отличается от указанной суммы указанного второго количественного параметра и указанного девятого количественного параметра, при этом указанный второй сигнал доступности ресурса формируют синхронно с указанными вторыми тактовыми импульсами и формируют третий сигнал доступности ресурса посредством сравнения указанного пятого количественного параметра с суммой указанного седьмого количественного параметра и указанного шестого количественного параметра, причем указанный третий сигнал доступности ресурса активен, если указанный пятый количественный параметр равен указанной сумме указанного седьмого количественного параметра и указанного шестого количественного параметра, при этом указанный третий сигнал доступности ресурса формируют синхронно с указанными третьими тактовыми импульсами.

Способ определения состояния ресурса цифровой системы, в которой по меньшей мере одна записывающая подсистема записывает данные в ресурс, а по меньшей мере одна считывающая подсистема считывает данные из ресурса, причем указанный ресурс не доступен для записи дополнительных данных из указанных записывающих подсистем до тех пор, пока записанные прежде данные не будут считаны из указанного ресурса одной из указанных считывающих подсистем, причем каждая записывающая подсистема и каждая считывающая подсистема работают синхронно с соответствующими тактовыми импульсами, по меньшей мере одна записывающая подсистема работает синхронно с первыми тактовыми импульсами, а по меньшей мере одна считывающая подсистема работает синхронно со вторыми тактовыми импульсами, вторые тактовые импульсы асинхронны указанным первым тактовым импульсам, при этом формируют один количественный параметр записи для каждой указанной записывающей подсистемы, причем каждый указанный количественный параметр записи представляет число доступов записи в указанный ресурс, сделанных соответствующей указанной записывающей подсистемой, при этом каждый указанный количественный параметр записи для каждой указанной записывающей подсистемы формируют синхронно с указанными соответствующими тактовыми импульсами указанной записывающей подсистемы, формируют один количественный параметр считывания для каждой указанной считывающей подсистемы, причем каждый указанный количественный параметр считывания представляет число доступов считывания из указанного ресурса, сделанных соответствующей указанной считывающей подсистемой, при этом каждый указанный количественный параметр считывания для каждой указанной считывающей подсистемы формируют синхронно с указанными соответствующими тактовыми импульсами указанной считывающей подсистемы, синхронизируют каждый количественный параметр записи с указанными тактовыми импульсами записывающих подсистем и указанными тактовыми импульсами считывающих подсистем, синхронизируют каждый количественный параметр с указанными тактовыми импульсами записывающих подсистем и указанными тактовыми импульсами считывающих подсистем, суммируют указанные количественные параметры записи для формирования общего количественного параметра считывания, причем указанное суммирование осуществляют независимо каждой указанной записывающей подсистемой и каждой указанной считывающей подсистемой, суммируют указанные количественные параметры считывания для формирования общего количественного параметра считывания, причем указанное суммирование осуществляют независимо каждой указанной записывающей подсистемой и каждой указанной считывающей подсистемой, сравнивают указанный общий количественный параметр записи и указанный общий количественный параметр считывания для формирования сигнала доступности ресурса для записи, причем указанный сигнал доступности ресурса для записи активен, если указанный общий количественный параметр записи равен указанному общему количественному параметру считывания, при этом указанное сравнение выполняется независимо каждой указанной записывающей подсистемой для формирования соответствующих сигналов доступности ресурса для записи, и сравнивают указанный общий количественный параметр записи и указанного общего количественного параметра считывания для формирования сигнала доступности ресурса для считывания, причем указанный сигнал доступности ресурса для считывания активен, если указанный общий количественный параметр записи отличается от указанного общего количественного параметра считывания, при этом указанное сравнение выполняется независимо каждой указанной считывающей системой для формирования соответствующих сигналов доступности ресурса для считывания.

Предпочтительно указанные количественные параметры записи и указанные количественные параметры считывания представляют значение либо нуля, либо единицы, причем указанное значение меняется от единицы к нулю или от нуля к единице при приращении, в котором указанный общий количественный параметр записи формируют посредством операции исключающее ИЛИ, которой подвергают указанные количественные параметры записи, причем указанный общий количественный параметр считывания формируют посредством операции исключающее ИЛИ, которой подвергают указанные количественные параметры считывания, причем указанный сигнал доступности ресурса для записи формируют посредством операции исключающее ИЛИ, которой подвергают указанный общий количественный параметр записи и указанный общий количественный параметр считывания, при этом указанный сигнал доступности ресурса для записи формируют независимо каждой указанной записывающей подсистемой, указанный сигнал доступности ресурса для считывания формируют посредством операции исключающее ИЛИ, которой подвергают указанный общий количественный параметр считывания и указанный общий количественный параметр записи, а указанный сигнал доступности ресурса для считывания формируют независимо каждой указанной считывающей подсистемой.

Способ определения состояния ресурса цифровой системы, в которой первая подсистема, работающая синхронно с первыми тактовыми импульсами, делает первичные доступы к ресурсу, вторая подсистема, работающая синхронно со вторыми тактовыми импульсами, делает вторичные доступы к ресурсу, указанные вторые тактовые импульсы асинхронны указанным первым тактовым импульсам, указанный ресурс не доступен для дополнительных указанных первичных доступов до тех пор, пока не будет иметь место указанный вторичный доступ, а указанный ресурс не доступен для указанных вторичных доступов до тех пор, пока не будет иметь места указанный первичный доступ, указанные первичные доступы чередуются по времени с указанными вторичными доступами, при этом формируют первый количественный параметр, представляющий число указанных первичных доступов к указанному ресурсу, сделанных указанной первой подсистемой, причем указанный первый количественный параметр формируют синхронно с указанными первыми тактовыми импульсами, формируют второй количественный параметр, представляющий число указанных вторичных доступов к указанному ресурсу, сделанных указанной второй подсистемой, причем указанный второй количественный параметр формируют синхронно с указанными вторыми тактовыми импульсами, синхронизируют указанный первый количественный параметр с указанными вторыми тактовыми импульсами для формирования третьего количественного параметра, синхронизируют указанный второй количественный параметр с указанными первыми тактовыми импульсами для формирования четвертого количественного параметра, сравнивают указанный первый количественный параметр с указанным четвертым количественным параметром для формирования первого сигнала доступности ресурса для указанной первой подсистемы, причем указанный первый сигнал доступности ресурса активен, если указанный первый количественный параметр равен указанному четвертому количественному параметру, при этом указанный первый сигнал доступности ресурса формируют синхронно с указанными первыми тактовыми импульсами, и сравнивают указанный второй количественный параметр с указанным третьим количественным параметром для формирования второго сигнала доступности ресурса для указанной второй подсистемы, причем указанный второй сигнал доступности ресурса активен, если указанный второй количественный параметр отличается от указанного третьего количественного параметра, при этом указанный второй сигнал доступности ресурса генерируется синхронно с указанными вторыми тактовыми импульсами.

Устройство для определения состояния ресурса в цифровой системе, в которой записывающая подсистема посылает сигнал записи в указанный ресурс, считывающая подсистема посылает сигнал считывания из указанного ресурса, указанная записывающая подсистема работает синхронно с первыми тактовыми импульсами, указанная считывающая подсистема работает синхронно со вторыми тактовыми импульсами, причем указанные вторые тактовые импульсы асинхронны указанным первым тактовым импульсам, причем оно содержит первый семафор, который формирует первый сигнал обновления, который может быть в первом логическом состоянии или втором логическом состоянии, причем указанный первый семафор реагирует на указанный сигнал записи, изменяя логическое состояние указанного первого сигнала обновления синхронно с указанными первыми тактовыми импульсами каждый раз, когда указанная записывающая подсистема записывает данные в указанный ресурс, второй семафор, который формирует второй сигнал обновления, который может быть в первом логическом состоянии и во втором логическом состоянии, причем указанный второй семафор реагирует на указанный сигнал считывания, изменяя логическое состояние указанного второго сигнала обновления синхронно с указанными вторыми тактовыми импульсами каждый раз, когда указанная считывающая подсистема считывает данные из указанного ресурса, первый синхронизирующий элемент, который синхронизирует указанный первый сигнал обновления с указанными вторыми тактовыми импульсами для формирования первого синхронизированного сигнала обновления, второй синхронизирующий элемент, который синхронизирует указанный второй сигнал обновления с указанными первыми тактовыми импульсами для формирования второго синхронизированного сигнала обновления, первый проверочный элемент, который формирует первый проверочный выходной сигнал, который может быть в первом логическом состоянии и во втором логическом состоянии, причем указанный первый проверочный элемент формирует указанный первый проверочный выходной сигнал в указанном первом логическом состоянии, если указанный первый сигнал обновления равен указанному второму синхронизированному сигналу обновления, указанный первый проверочный элемент формирует указанный первый проверочный выходной сигнал в указанном втором логическом состоянии, если указанный первый сигнал обновления отличается от указанного второго синхронизированного сигнала обновления, и второй проверочный элемент, который формирует второй проверочный выходной сигнал, который может быть в первом логическом состоянии и во втором логическом состоянии, причем указанный второй проверочный элемент формирует указанный второй проверочный выходной сигнал в указанном первом логическом состоянии, если указанный первый синхронизированный сигнал обновления равен указанному второму сигналу обновления, указанный второй проверочный элемент формирует указанный второй проверочный выходной сигнал в указанном втором логическом состоянии, если указанный первый синхронизированный сигнал обновления отличается от указанного второго сигнала обновления. Обычно указанный первый семафор содержит первый логический элемент исключающее ИЛИ и первый триггер задержки, причем указанный первый логический элемент исключающее ИЛИ имеет первый выход, указанный первый выход соединен со входом указанного триггера задержки, указанный первый триггер задержки имеет второй выход, указанный второй выход соединен со входом указанного первого логического элемента исключающее ИЛИ, и указанный второй семафор содержит второй логический элемент исключающее ИЛИ и второй триггер задержки, причем указанный второй логический элемент исключающее ИЛИ имеет третий выход, соединенный с указанным третьим выходом указанного второго триггера задержки, указанный второй триггер задержки имеет четвертый выход, указанный четвертый выход соединен со входом указанного второго логического элемента исключающее ИЛИ.

Преимущественно указанный первый синхронизирующий элемент содержит два триггера задержки с фиксацией состояния, при этом указанный второй синхронизирующий элемент содержит два триггера задержки с фиксацией состояния. Предпочтительно указанный первый проверочный элемент содержит логический элемент исключающее ИЛИ, при этом указанный второй проверочный элемент содержит логический элемент исключающее ИЛИ.

Устройство для определения состояния ресурса цифровой системы, в которой первая подсистема, работающая синхронно с первыми тактовыми импульсами, записывает данные в указанный ресурс, вторая подсистема, работающая синхронно со вторыми тактовыми импульсами, считывает данные из указанного ресурса, причем указанные вторые тактовые импульсы асинхронны указанным первым тактовым импульсам, указанный ресурс не доступен для записи дополнительных данных из указанной первой подсистемы до тех пор, пока записанные прежде данные не будут считаны из указанного ресурса указанной второй подсистемой, причем оно содержит средство для формирования первого количественного параметра, представляющего число доступов записи в указанный ресурс, сделанных указанной первой подсистемой, причем указанный первый количественный параметр формируют синхронно с указанными первыми тактовыми импульсами, средство для формирования второго количественного параметра, представляющего число доступов считывания из указанного ресурса, сделанных указанной второй подсистемой, причем указанный второй количественный параметр формируют синхронно указанным вторым тактовым импульсам, средство для синхронизации указанного первого количественного параметра с указанными вторыми тактовыми импульсами для формирования третьего количественного параметра, средство для синхронизации указанного второго количественного параметра с указанными первыми тактовыми импульсами для формирования четвертого количественного параметра, средство для сравнения указанного первого количественного параметра с указанным четвертым количественным параметром для формирования первого сигнала доступности ресурса для указанной первой подсистемы, причем указанный первый сигнал доступности ресурса активен, если указанный первый количественный параметр равен указанному четвертому количественному параметру, при этом указанный первый сигнал доступности ресурса формируют синхронно указанным первым тактовым импульсам, и средство для сравнения указанного второго количественного параметра с указанным третьим количественным параметром для формирования второго сигнала доступности ресурса для указанной второй подсистемы, причем указанный второй сигнал доступности ресурса активен, если указанный второй количественный параметр отличается от указанного третьего количественного параметра, при этом указанный второй сигнал доступности ресурса формируют синхронно указанным вторым тактовым импульсам.

Краткое описание чертежей.

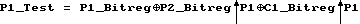

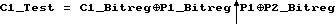

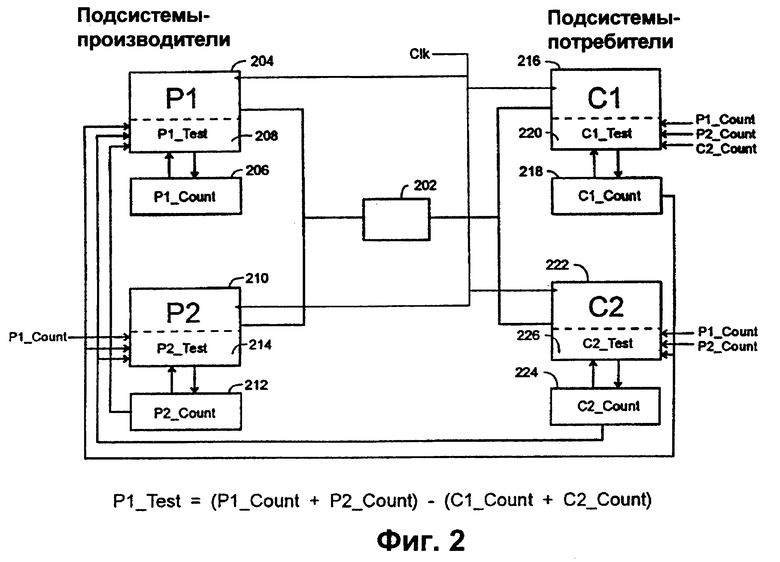

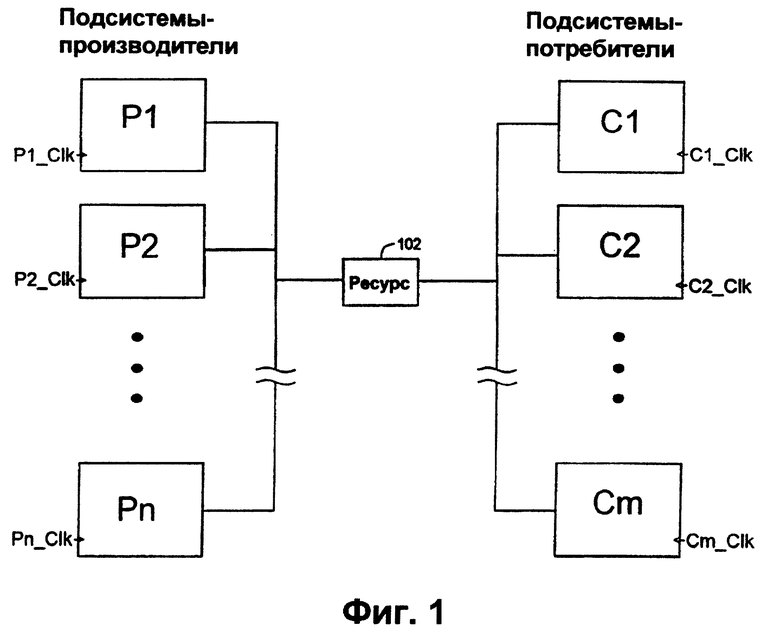

Фиг. 1 - блок-схема, иллюстрирующая часть цифровой системы, имеющей множество подсистем-производителей и множество подсистем-потребителей, причем все подсистемы работают в разных тактовых областях, совместно используя общий ресурс.

Фиг. 2 - блок-схема, иллюстрирующая две подсистемы, являющиеся производителями, и две подсистемы, являющиеся потребителями, причем каждый производитель и потребитель содержит счетчик и совместно использует один ресурс в вычислительной среде, в которой каждый производитель и потребитель работает в одной тактовой области.

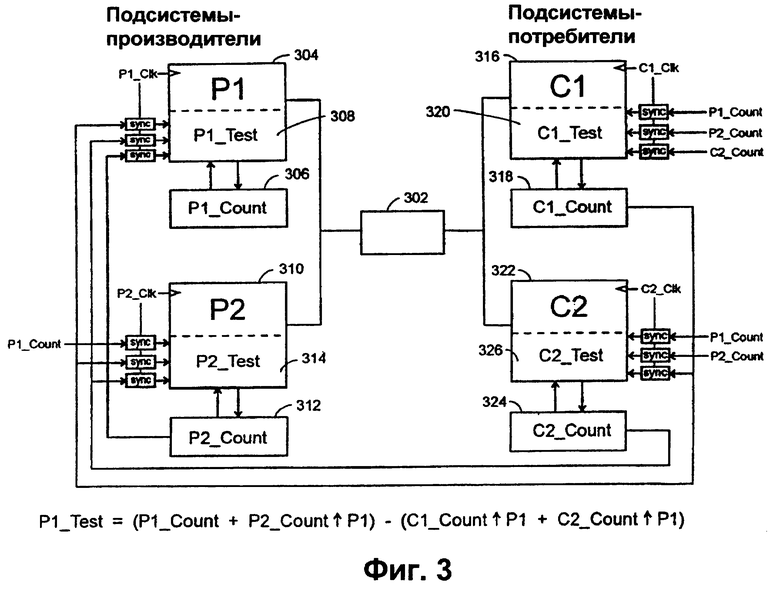

Фиг. 3 - блок-схема, иллюстрирующая две подсистемы, являющиеся производителями, и две подсистемы, являющиеся потребителями, причем каждая подсистема содержит счетчик, каждая подсистема совместно использует ресурс, каждый производитель и потребитель работает в другой тактовой области.

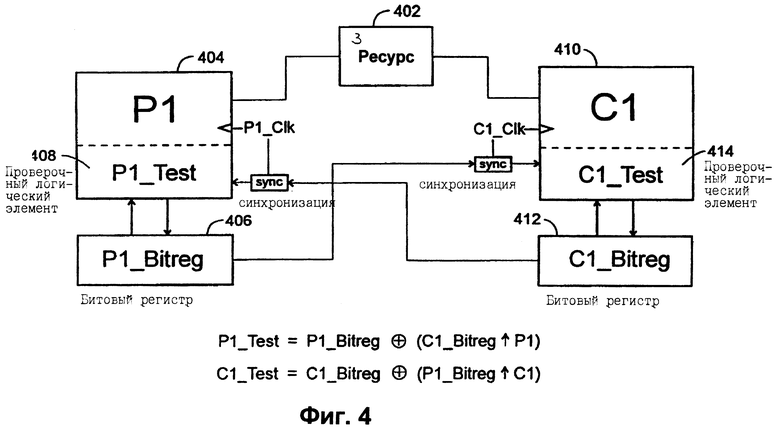

Фиг. 4 - блок-схема части цифровой системы, содержащей одного производителя и одного потребителя, совместно использующих один ресурс, каждый содержит битовый регистр и каждый работает в другой тактовой области.

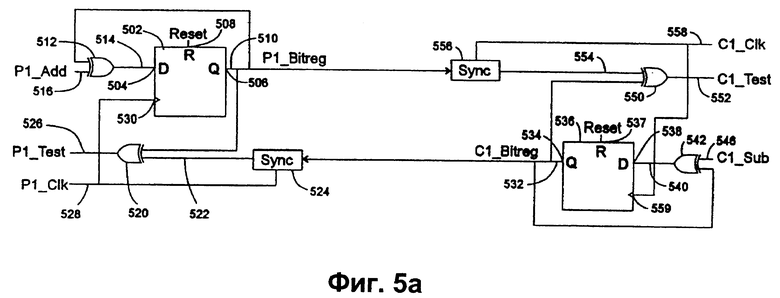

Фиг. 5а - логическая блок-схема, иллюстрирующая соответствующие компоненты битового регистра и компоненты проверки ресурса для одной подсистемы-производителя и одной подсистемы-потребителя, причем каждая подсистема работает в другой тактовой области.

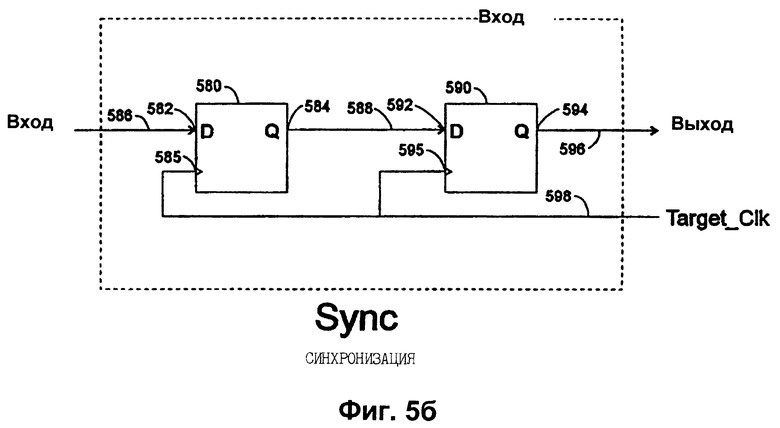

Фиг.5b - логическая блок-схема, иллюстрирующая синхронизирующий элемент, содержащий два триггера задержки, тактируемых посредством общих тактовых импульсов

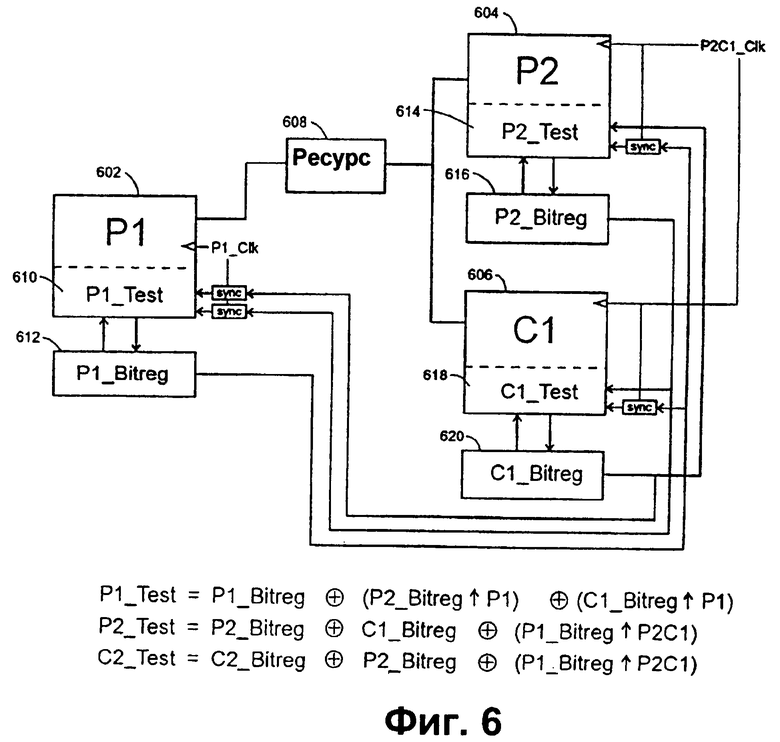

Фиг.6 - блок-схема, представляющая часть цифровой системы содержащей две тактовые области, причем первая тактовая область содержит одну подсистему-производитель, вторая тактовая область содержит одну подсистему-производитель и одну подсистему-потребитель, каждая подсистема содержит битовый регистр и каждая подсистема совместно использует ресурс.

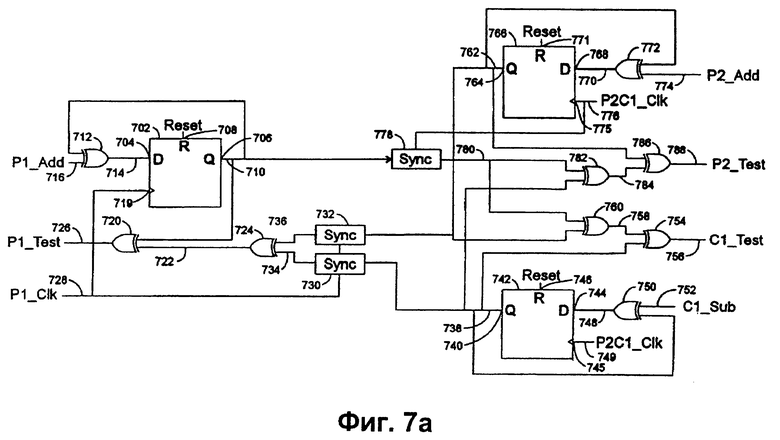

Фиг.7а - логическая блок-схема, иллюстрирующая соответствующие компоненты битового регистра и компоненты проверки ресурса для одной подсистемы-производителя, работающей в одной тактовой области, и для одной подсистемы-производителя и одной подсистемы-потребителя, работающих в другой тактовой области.

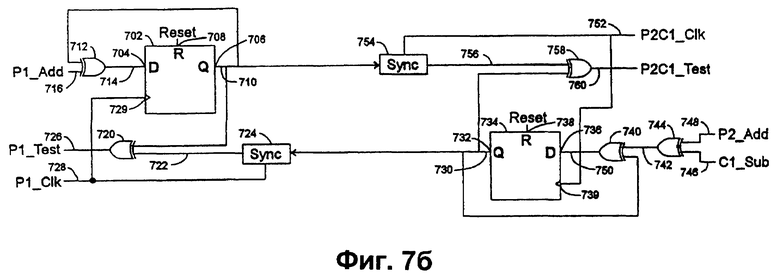

Фиг. 7b - логическая блок-схема, иллюстрирующая компонент битового регистра и компонент проверки ресурса для одной подсистемы-производителя, работающей в одной тактовой области, причем компонент битового регистра и компонент проверки ресурса совместно используются одной системой-производителем и одной подсистемой-потребителем, работающих в другой тактовой области.

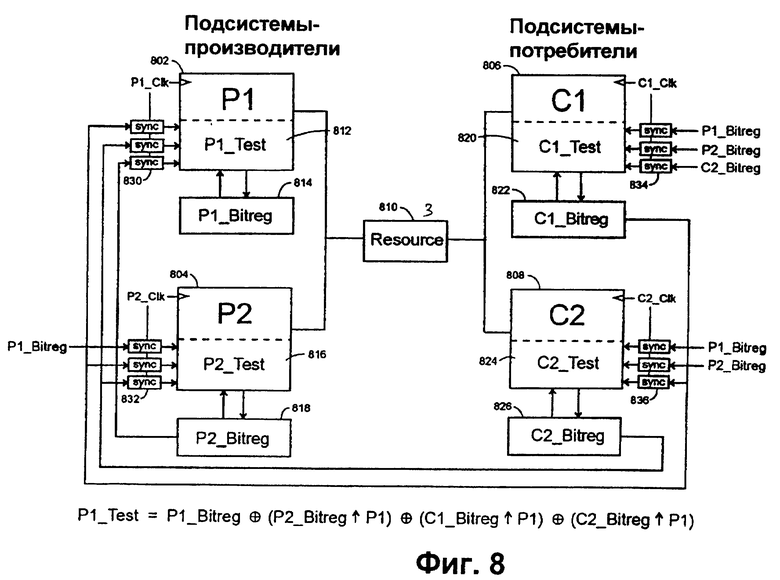

Фиг. 8 - блок-схема, иллюстрирующая часть цифровой системы, содержащей две подсистемы, являющиеся производителями, и две подсистемы, являющиеся потребителями, причем каждая подсистема содержит битовый регистр, каждая совместно использует общий ресурс, каждая работает в другой тактовой области.

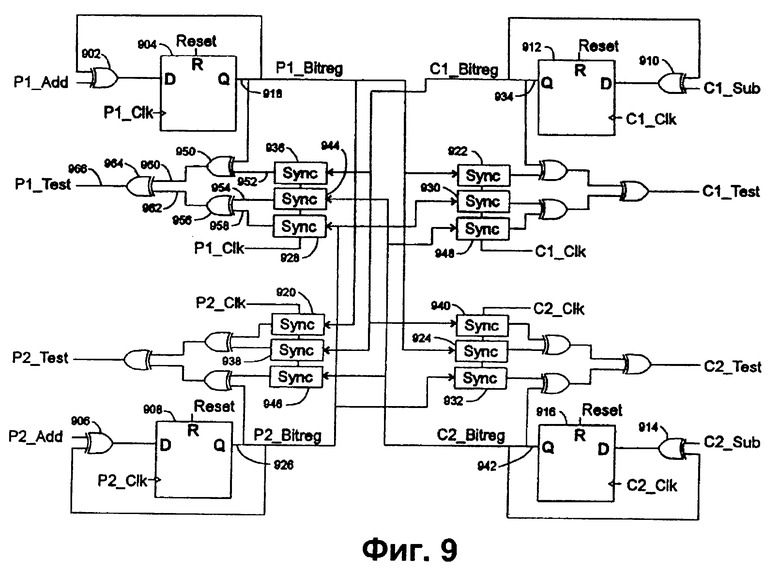

Фиг. 9 - логическая блок-схема, представляющая часть цифровой системы, содержащей соответствующие компоненты битового регистра и компоненты проверки ресурса для двух подсистем-производителей и для двух подсистем-потребителей, причем все подсистемы работают в автономных тактовых областях

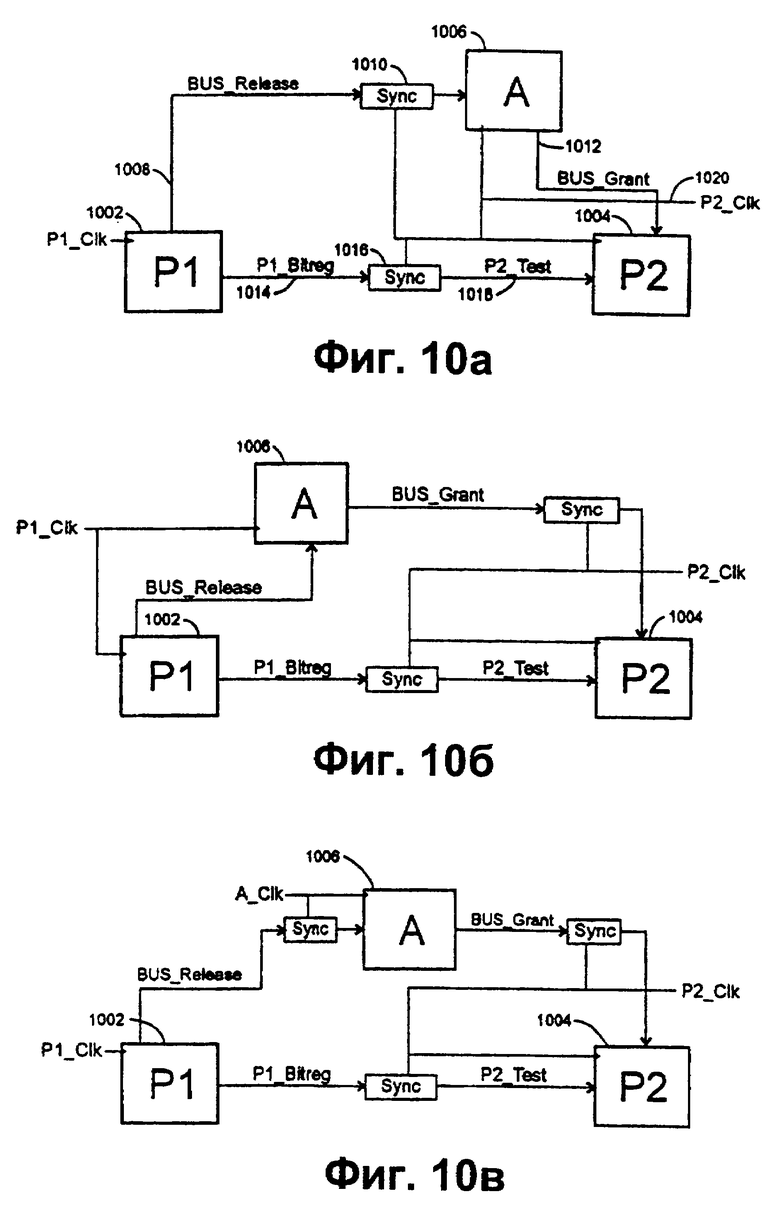

Фиг. 10а - блок-схема, представляющая двух производителей, причем каждый работает в другой тактовой области и регулируется арбитром, работающим в тактовой области второго производителя.

Фиг. 10b - блок-схема, представляющая двух производителей, причем каждый работает в другой тактовой области и регулируется арбитром, работающим в тактовой области первого производителя.

Фиг. 10b - блок-схема, представляющая двух производителей, причем каждый работает в другой тактовой области и регулируется арбитром, работающим в еще одной тактовой области.

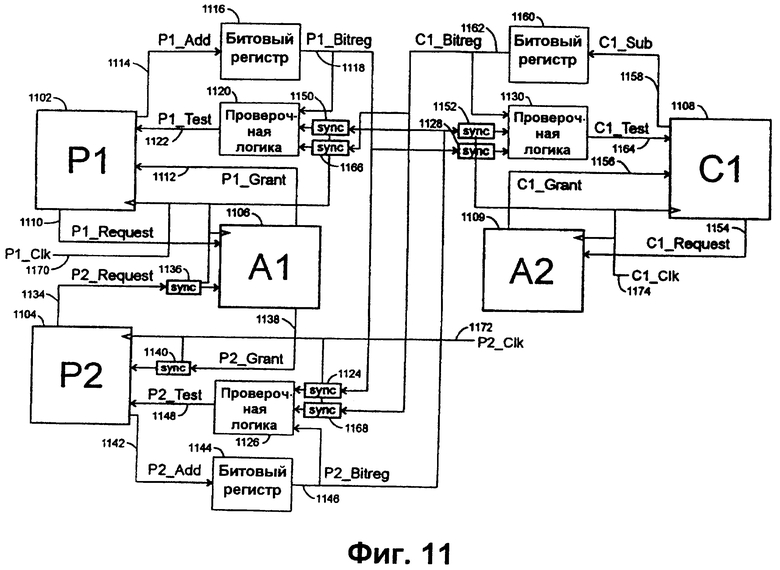

Фиг. 11 - блок-схема, представляющая двух производителей, работающих в разных тактовых областях, регулируемых арбитром, работающим в третьей тактовой области, где сигналы от каждого производителя к арбитру и от арбитра к каждому производителю синхронизируются в тактовой области другого производителя.

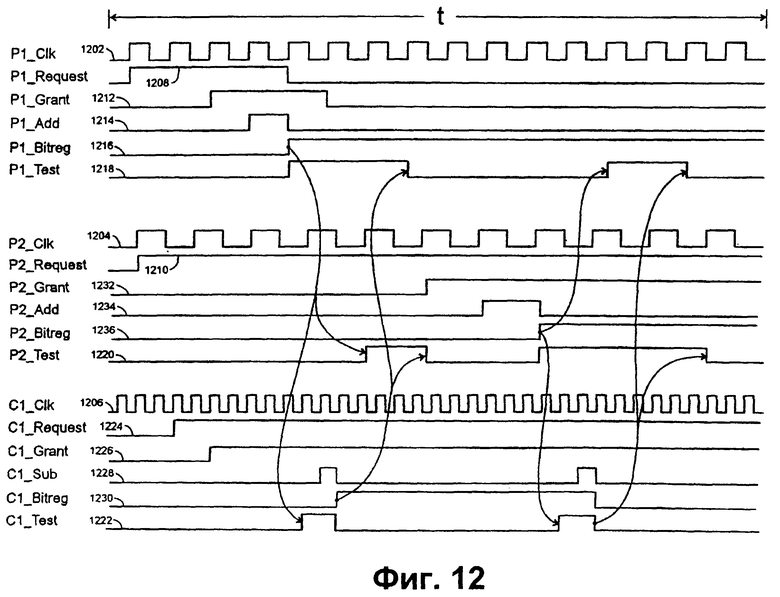

Фиг. 12 - диаграмма согласования формы сигнала, представляющая соответствующие запросы доступа и разрешения доступа ресурса для первого производителя, второго производителя и потребителя.

Ниже приведено подробное описание предпочтительного варианта осуществления настоящего изобретения.

На фиг. 1 показана упрощенная блок-схема, представляющая множество подсистем вычислительного комплекса, в котором все подсистемы могут иметь допуск к одному совместно используемому ресурсу 102. Подсистемы являются "производителями" и "потребителями", причем каждый такой производитель способен записывать данные в ресурс 102, а каждый такой потребитель способен считывать данные из этого ресурса. Как следует из фиг.1, подсистемы-производители могут обеспечивать информацию для подсистем-потребителей посредством записи данных в совместно используемый ресурс 102, которые затем могут быть считаны потребителем. Совместно используемый ресурс 102 способен удерживать один элемент данных.

Каждая подсистема-производитель и подсистема-потребитель, иллюстрируемая на фиг.1, работает в другой тактовой области. Очевидно, что тактовая область содержит один или более тактовых генераторов, работающих с одной частотой и в одной фазе. Очевидно также, что каждая из систем, описываемых в этой заявке, сначала возвращается к известной установке состояний. Возврат в исходное состояние не показан на каждой блок-схеме, однако квалифицированному в этой области техники специалисту будет очевидно, что механизм возврата в исходное состояние обеспечен для каждой системы.

Настоящее изобретение направлено на определение доступности совместно используемого ресурса. При использовании настоящего изобретения любое число подсистем-производителей или подсистем-потребителей, причем все подсистемы работают в одной тактовой области, в разных тактовых областях или в любой комбинации, могут определить доступность для них совместно используемого ресурса.

На фиг. 2 показана упрощенная блок-схема части цифровой системы, содержащей две подсистемы, названные производителями ("Р1" и "Р2"), и две подсистемы, названные потребителями ("С1" и "С2"), совместно использующие ресурс 202, который способен удерживать один элемент данных. Каждый производитель и потребитель имеет соответствующий счетный элемент ("P1_Count", "P2_ Count". "C1_Count", "C2_Count"). Каждый счетный элемент способен удерживать целые значения, начиная от нуля, причем такие значения способны приращиваться на единицу.

Первый производитель 204 содержит счетчик 206 и проверочный логический элемент 208. Первый производитель 204 дает приращение счетчика 206 каждый раз на единицу, когда первый производитель 204 записывает данные в совместно используемый ресурс 202. Второй производитель 210 аналогичным образом содержит счетчик 212 и проверочный логический элемент 214. Второй производитель 210 дает приращения счетчика 212 каждый раз на единицу, когда второй производитель 210 записывает данные в совместно используемый ресурс 202.

Первый потребитель 216 содержит счетчик 218 и проверочный логический элемент 220. Первый потребитель 216 дает приращение счетчика 218 каждый раз на единицу, когда первый потребитель 216 считывает данные из совместно используемого ресурса 202. Аналогичным образом второй потребитель 222 содержит счетчик 224 и проверочный логический элемент 226. Второй потребитель 222 дает приращение счетчика 224 каждый раз на единицу, когда второй потребитель считывает данные из совместно используемого ресурса 202.

Оба производителя и оба потребителя могут читать значение четырех счетчиков. Таким образом, например, значение счетчика 206 первого производителя 204 не может быть только прочитано первым производителем 204, но может быть также прочитано вторым производителем 210, а также первым потребителем 216 и вторым потребителем 222.

Для предотвращения записи данных в совместно используемый ресурс 202 прежде, чем предварительно записанные данные были прочитаны, производитель должен быть способным выяснить, позволено ли ему записывать данные в совместно используемый ресурс. Для выяснения, позволено ли ему записать данные в совместно используемый ресурс, производитель должен проверить состояние ресурса, если ресурс содержит данные, которые еще не были прочитаны потребителем (то есть "свежие" данные), производитель не может записать новые данные в ресурс, не разрушив предполагаемой выше связи.

Потребитель должен также проверить состояние ресурса для определения, являются ли данные в ресурсе старыми данными, которые уже были прочитаны потребителем (то есть "устаревшими" данными), или являются новыми данными, готовыми для считывания. Потребитель должен избегать считывания устаревших данных и должен быть уверен, что любые считываемые данные являются свежими.

При однородном тактировании, иллюстрируемом на фиг.2, первый производитель 204 может выяснить, когда он может безопасно записать данные в совместно используемый ресурс 202 (то есть, когда ресурс содержит устаревшие данные), путем считывания значений всех счетчиков всех производителей и потребителей в системе. Проверочный логический элемент 208 первого производителя 204 суммирует значение своего собственного счетчика 206 и значение счетчика 212 второго производителя для получения всего числа записей в совместно используемый ресурс 202. Проверочный логический элемент 208 первого производителя 204 суммирует также значение счетчика 218 первого потребителя и значение счетчика 224 второго потребителя для получения общего числа считываний из совместно используемого ресурса 202. После этого проверочный логический элемент 208 вычитает общее число считываний из общего числа записей. Нулевой результат показывает первому производителю 204, что он может безопасно записать данные в совместно используемый ресурс 202. Нулевой результат показывает, что каждое требование производителя записать данные в совместно используемый ресурс сопровождается согласующимся требованием потребителя считывать данные из ресурса. Аналогичным образом, если результат такого вычитание не равен нулю, то первый производитель 204 способен различить, что записывать данные в совместно используемый ресурс 202 не безопасно (то есть, что в ресурсе находятся свежие данные, которые еще не были прочитаны).

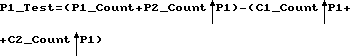

Логика проверки, требуемая для первого изготовителя 204 для проверки состояния совместно используемого ресурса 202, может быть представлена в виде уравнения

P1_Test=(P1_Count+P2_Count)-(C1_Count+C2_Count).

Если результат уравнения P1_Test равен нулю, то в совместно используемом ресурсе 202 находятся устаревшие данные и первый производитель 204 может безопасно записать в совместно используемый ресурс 202 новые данные. Если результат уравнения P1_Test не равен нулю, то в совместно используемом ресурсе 202 находятся свежие данные и первый производитель 204 не может записать в совместно используемый ресурс 202 новые данные.

Аналогичная логика проверки позволяет потребителю выяснить, когда совместно используемый ресурс доступен для считывания. Проверочный логический элемент 220 первого потребителя 216 будет независимо осуществлять аналогичные вычисления, что и проверочный логический элемент 208 первого производителя 204, описанные выше. Если результат вычислений не равен нулю, то в ресурсе 202 находятся свежие данные и первый потребитель 216 может считывать данные из совместно используемого ресурса 202. Если результат равен нулю, то в ресурсе 202 находятся устаревшие данные и первый потребитель 216 не может считывать данные.

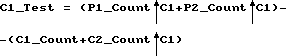

Логика проверки, требуемая для потребителя 216 для проверки состояния совместно используемого ресурса 202, аналогична логике проверки, требуемой для производителя 204 и может быть представлена в виде уравнения

С1_Test=(Р1_Count+P2_Count)-(С1_Count+C2_Count).

Если результат уравнения C1_Test не равен нулю, то в совместно используемом ресурсе 202 находятся свежие данные и первый потребитель 216 может безопасно считывать данные из совместно используемого ресурса 202. Если результат уравнения C1_ Test равен нулю, то в совместно используемом ресурсе 202 находятся устаревшие данные и первый потребитель 216 не может считывать данные.

Очевидно, что блок-схема, приведенная на фиг.2, предлагается только для теоретических целей. На практике нет счетчика целых чисел, который был бы способен обеспечивать бесконечный счет. Как правило, такие счетчики обнуляются, когда переполняются сверх допустимого диапазона чисел. Уравнения логики проверки, описанные выше со ссылкой на фиг.2, не станут справедливыми, как только один из счетчиков внезапно от очень высокого числа перейдет к нулевому значению. Однако блок-схема, показанная на фиг.2, полезна для пояснения теоретических принципов настоящего изобретения, заключающихся в том, что состояние совместно используемого ресурса может быть определено, заставляя каждую подсистему представлять свою собственную историю доступа ресурса и, путем последующего исследования всех таких историй, доступа всех подсистем.

На фиг. 3 приведена упрощенная блок-схема, представляющая двух производителей ("P1" и "Р2") и двух потребителей ("С1" и "С2"). Все эти четыре подсистемы имеют доступ к совместно используемому ресурсу 302, способному удерживать один элемент данных. Кроме того, каждый производитель и каждый потребитель в системе, иллюстрируемой на фиг.3, работает в другой тактовой области. Другими словами, на фиг.3 иллюстрируются четыре разные тактовые области, по одной для каждой подсистемы.

На фиг. 3 показан первый производитель 304 содержащий счетчик 306 и проверочный логический элемент 308, работающий синхронно с первыми тактовыми импульсами (P1_ Clk). Первый производитель 304 дает приращение счетчика 306 каждый раз на единицу, когда производитель 304 записывает данные в совместно используемый ресурс 302. Второй производитель 310 аналогичным образом содержит счетчик 312 и проверочный логический элемент 314 и работает синхронно со вторыми тактовыми импульсами (Р2_Сlk). Второй производитель 310 дает приращение счетчика 312 каждый раз на единицу, когда второй производитель 310 записывает данные в совместно используемый ресурс 302.

Первый потребитель 316 содержит счетчик 318 и проверочный логический элемент 320 и работает синхронно с третьими тактовыми импульсами (C1__Clk). Первый потребитель 316 дает приращение счетчика 318 каждый раз на единицу, когда первый потребитель 316 считывает данные из совместно используемого ресурса 302. Аналогичным образом второй потребитель 322 содержит счетчик 324 и проверочный логический элемент 326 и работает синхронно с четвертыми тактовыми импульсами (C2_Clk). Второй потребитель 322 дает приращение счетчика 324 каждый раз на единицу, когда второй потребитель считывает данные из совместно используемого ресурса 302.

Как было справедливо для системы, описанной со ссылкой на фиг.2, проверочный логический элемент дает возможность каждому производителю определить, может ли он безопасно записать данные в совместно используемый ресурс (установить, являются ли данные "устаревшими") и дает возможность каждому потребителю определить, может ли он безопасно считывать данные из совместно используемого ресурса (установить, являются ли данные "свежими"). Однако подсистемы, показанные на фиг.3, работают в разных тактовых областях; таким образом, прежде, чем проверочный логический элемент производителя или потребителя может использовать значения счетчиков, связанных с другими подсистемами, квалифицированному специалисту в этой области техники будет очевидно, что такие значения должны быть синхронизированы с тактовыми импульсами проверочного логического элемента.

В соответствии с этим, поскольку счетчик 306 работает в такой же тактовой области, что и первый производитель 304, первый производитель 304 имеет немедленный синхронный доступ к значению счетчика 306. Однако первый производитель 304 не имеет синхронного доступа к значению счетчика 312 второго производителя 310, к значению счетчика 318 первого потребителя 316 или к счетчику 324 второго потребителя 322. Будет очевидно, что для разрешения первому производителю 304 считывать значения счетчиков 312, 318 и 324 значение каждого счетчика должно быть синхронизировано с тактовыми импульсами P1_Clk первого производителя.

На фиг.3 иллюстрируется синхронизация значений счетчиков 312, 318 и 324 с тактовыми импульсами P1_Clk. Таким образом, значение счетчика 312 второго производителя 310 является входом в синхронизирующий элемент, тактируемый посредством тактовых импульсов P1__Clk. Синхронизированное значение счетчика 312 затем передается к проверочному логическому элементу 308 первого производителя 304. Аналогичным образом значение счетчика 318 первого потребителя 316 является также входом в синхронизирующий элемент, тактируемый посредством тактовых импульсов P1_Clk. После этого синхронизированное значение счетчика 318 передается к проверочному логическому элементу 308 первого производителя 304. Значение счетчика 324 второго потребителя 322 также является входом в синхронизирующий элемент, тактируемый посредством тактовых импульсов P1_Clk. Синхронизированное значение счетчика 324 затем передается к проверочному логическому элементу 308 первого производителя 304.

Как только значения счетчика синхронизированы с тактовой областью производителя или потребителя, производитель или потребитель может проверить состояние совместно используемого ресурса 302. Как описано со ссылкой на фиг. 2, первый производитель 304 может проверять состояние совместно используемого ресурса 302 путем вычитания суммы значений счетчиков 310, 312 потребителей из суммы значений счетчиков 304, 308 производителей. Логика проверки, используемая первым производителем 304 для проверки состояния совместно используемого ресурса 302, может быть представлена следующим уравнением

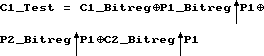

Следует отметить, что синхронизация P2_ Count, C1_Count и C2_Count с тактовыми импульсами P1_ Clk производителя 304 показана в уравнении посредством операционного суффикса  Как описано со ссылкой на фиг.2, нулевой результат уравнения P1_Test указывает на то, что в ресурсе 302 находятся устаревшие данные и первый производитель 304 может записать новые данные в ресурс 302. С другой стороны, ненулевое значение указывает на то, что в ресурсе 302 находятся свежие данные и производитель 304 не может записать новые данные в ресурс 302.

Как описано со ссылкой на фиг.2, нулевой результат уравнения P1_Test указывает на то, что в ресурсе 302 находятся устаревшие данные и первый производитель 304 может записать новые данные в ресурс 302. С другой стороны, ненулевое значение указывает на то, что в ресурсе 302 находятся свежие данные и производитель 304 не может записать новые данные в ресурс 302.

Логика проверки, используемая первым потребителем 316, совершенно аналогична и может быть представлена аналогичным уравнением. Например, уравнение логики проверки для первого потребителя имеет вид

Следует отметить, что P1_Count, P2_Count и C2_Count все синхронизированы с тактовыми импульсами C1_ Clk первого потребителя 316. Если результат уравнения C1_ Test не равен нулю, то это указывает на то, что первый потребитель 316 может безопасно считывать данные из совместно используемого ресурса 302. Если результат уравнения C1_Test равен нулю, то первый потребитель 316 не может безопасно считывать данные из совместно используемого ресурса 302.

Как было показано со ссылкой на фиг.2, данные, приведенные со ссылкой на фиг. 3, полезны только для теории. Поскольку счетчики на практике не могут считать бесконечно большие значения, логика проверки, описанная со ссылкой на фиг.3, не может иметь практического значения.

На фиг.4 приведена упрощенная блок-схема, представляющая часть цифровой системы, содержащей одну подсистему-производитель ("Р1") и одну подсистему-потребитель ("С1"), работающие в разных тактовых областях. Производитель и потребитель совместно используют ресурс 402, способный удерживать один элемент данных.

Как показано на фиг. 4, подсистема-производитель 404 содержит битовый регистр 406 и проверочный логический элемент 408 и работает синхронно с первыми тактовыми импульсами P1_Clk. Подсистема-потребитель 410 содержит битовый регистр 412 и проверочный логический элемент 414 и работает синхронно со вторыми тактовыми импульсами C1_Clk. Каждый битовый регистр 406, 412 способен представлять значение нуля или единицы.

Производитель 404 может считывать значение битового регистра 412 потребителя 410, а потребитель 410 может считывать значение битового регистра 406 производителя 404. Однако производитель 404 и потребитель 410 работают в асинхронных тактовых областях. По этой причине значение битового регистра 412 должно быть синхронизировано с тактовыми импульсами P1_Clk производителя 404, а значение битового регистра 406 должно быть синхронизировано с тактовыми импульсами C1_ Clk потребителя 410. В соответствии с этим на фиг.4 показано, что значение битового регистра 412 подается как вход в синхронизирующий элемент, тактируемый посредством тактовых импульсов C1_Clk. Синхронизированное значение битового регистра 406 затем подается к проверочному логическому элементу 414 потребителя 410.

Настоящее изобретение обеспечивает сравнение числа раз, когда производитель записал данные в совместно используемый ресурс (числа "записей"), с числом раз, когда потребитель считал данные из совместно используемого ресурса (с числом "считываний"). Для целей настоящего изобретения состояние совместно используемого ресурса может быть проверено путем выяснения равно ли число записей числу считываний или отличается ли число записей от числа считываний, то есть для проверки состояния совместно используемого ресурса не требуется вычисления действительного числа записей или считываний.

По этой причине может быть упрощена логика проверки, описанная выше в связи с фиг.2 и фиг.3. Поскольку совместно используемый ресурс 402 способен удерживать только один элемент данных и поскольку для представления состояния совместно используемого ресурса требуется только нулевой или ненулевой результат, квалифицированному в этой области техники специалисту будет очевидно, что описанные выше со ссылкой на фиг.2 и фиг.3 счетчики могут быть заменены битовыми регистрами. Кроме того, квалифицированному в этой области техники специалисту также будет очевидно, что по некоторым причинам операция исключающее ИЛИ алгебры логики может заменить сложение и вычитание, описанные выше со ссылкой на фиг.2 и фиг.3.

Операция исключающее ИЛИ хорошо известна в этой области техники. Оператор исключающее ИЛИ, используемый с двумя двоичными операндами, даст в результате выход высокого состояния, если один двоичный операнд находится в высоком состоянии, а другой - в низком состоянии. Операция исключающее ИЛИ даст в результате выход низкого состояния, если оба двоичных операнда находятся в высоком состоянии или если оба двоичных операнда находятся в низком состоянии.

Вполне очевидно, что операция исключающее ИЛИ идеально пригодна для сравнения числа записей с числом считываний (при этом каждая запись или каждое считывание указывается производителем или потребителем, изменяющим значение своего соответствующего битового регистра) для определения, согласуется или не согласуется число записей с числом считываний. Настоящее изобретение относится к строго осуществляемой стратегии доступа запись-считывание-запись-считывание и абсолютно препятствует двум или более записям без промежуточного считывания, а также двум или более считываниям без промежуточной записи. В контексте системы, использующей такую стратегию доступа, операция исключающее ИЛИ, использованная для каждого битового регистра как двоичный операнд, даст ноль, если число записей согласуется с числом считываний, и даст единицу, если эти числа отличаются.

Таким образом, производитель 404 и потребитель 410 содержат битовые регистры 406, 412 вместо целочисленных счетчиков, описанных со ссылкой на фиг.2 и фиг. 3. Производитель 404 может определить, находятся ли в совместно используемом ресурсе 402 устаревшие данные, в результате операции исключающее ИЛИ, которой подвергается значение своего собственного битового регистра 406 и значение битового регистра 412 потребителя 410. Такую операцию исключающее ИЛИ осуществляют в проверочном логическом элементе 408 производителя 404. Если полученный результат операции исключающее ИЛИ со значением обоих битовых регистров 406, 412 равен нулю, то данные, находящиеся в совместно используемом ресурсе 402, являются устаревшими и производитель 404 может записать данные в совместно используемый ресурс 402. Однако если полученным результатом является единица, то в совместно используемом ресурсе 402 находятся свежие данные и производитель 404 не может записать новые данные в совместно используемый ресурс 402.

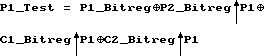

Для иллюстрации требуемой логики проверки производитель 404 может определить состояние совместно используемого ресурса 402 в соответствии со следующим уравнением:

Следует отметить, что операция исключающее ИЛИ указана в приведенном выше уравнении посредством оператора "⊕". Если результатом уравнения P1_Test является ноль, то данные в совместно используемом ресурсе 402 уже были считаны потребителем 410 (данные являются устаревшими) и производитель 404 может записать новые данные в совместно используемый ресурс 402. Однако если результатом уравнения P1_Test является единица, то в совместно используемом ресурсе 402 находятся свежие данные и производитель 404 не может записать в совместно используемый ресурс 402 новые данные.

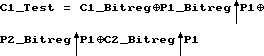

Аналогичная логика проверки используется потребителем 410. Например, потребитель 410 может определить состояние совместно используемого ресурса 402 в соответствии со следующим уравнением:

Если результатом уравнения C1_ Test является единица, то в совместно используемом ресурсе 402 находятся свежие данные и эти данные могут быть немедленно считаны потребителем 410. С другой стороны, если результатом уравнения C1_ Test является ноль, то в совместно используемом ресурсе 402 находятся устаревшие данные и потребитель 410 не может считывать эти данные.

На фиг.5 приведена логическая блок-схема, представляющая логику, которая позволяет одному производителю и одному потребителю независимо проверять состояние совместно используемого ресурса. Совместно используемый ресурс на фиг. 5 не показан. На фиг.5 полностью не показаны также подсистемы производителя и потребителя, а показаны только компоненты, которые облегчают работу битового регистра, и проверочные логические элементы, описанные в общем со ссылкой на фиг.4. Функция битового регистра позволяет производителю показывать, что он записал данные в совместно используемый ресурс, и позволяет потребителю показывать, что он считал данные из совместно используемого ресурса. Проверочный логический элемент позволяет потребителю или производителю проверять состояние совместно используемого ресурса.

Как показано на фиг.5а, первый триггер 502 сдвига имеет D-вход 504, Q-выход 504 и R-вход (вход занесения "0") 508. Q-выход 506 соединен линией 510 связи с первым входом логического элемента 512 исключающее ИЛИ. Логический элемент 512 исключающее ИЛИ имеет выход, соединенный посредством линии 514 с D-входом 504. Второй вход в логический элемент 512 исключающее ИЛИ соединен посредством линии 516 связи с сигналом P1_Add, формируемым подсистемой-производителем 404 (фиг.4). Q-выход 506 соединен посредством линии 510 связи с первым входом второго логического элемента 520 логическое ИЛИ. Второй вход в логический элемент 520 исключающее ИЛИ соединен посредством линии 522 связи с выходом элемента 524 синхронизации. Выход логического элемента 520 исключающее ИЛИ соединен посредством линии 526 связи как вход P1_Test к производителю 404. Элемент 524 синхронизации соединен посредством линии 528 связи с первыми тактовыми импульсами (P1_Clk). Тактовые импульсы P1_Clk соединены также посредством линии 528 связи с тактируемым входом 530 триггера 502 задержки.

Вход в синхронизирующий элемент 524 соединен посредством линии 532 связи с Q-выходом 534 второго триггера 536 задержки. Триггер 536 задержки имеет R-вход (вход занесения "0") 537 и D-вход 538. D-вход 538 триггера 536 задержки соединен посредством линии 540 связи с выходом третьего логического элемента 542 исключающее ИЛИ. Q-выход 534 триггера 536 задержки соединен посредством линии 532 связи как первый вход в логический элемент 542 исключающее ИЛИ. Второй вход логического элемента 542 исключающее ИЛИ соединен посредством линии 546 связи для приема сигнала C1_Sub от подсистемы-потребителя 406 (фиг. 4). Q-выход 534 триггера 536 задержки соединен посредством линии 532 связи как первый вход в четвертый логический элемент 550 исключающее ИЛИ. Выход логического элемента 550 исключающее ИЛИ соединен посредством линии 552 связи как сигнал C1_Test к подсистеме-потребителю 406. Второй вход в логический элемент 550 исключающее ИЛИ соединен посредством линии 554 связи с выходом элемента 556 синхронизации. Элемент 556 синхронизации соединен посредством линии 558 связи со вторыми тактовыми импульсами (C1_Clk). Тактовые импульсы C1_Clk соединены также посредством линии 558 связи с тактируемым входом 559 триггера 536 задержки. Вход элемента 556 синхронизации соединен посредством линии 510 связи с Q-выходом 506 триггера 502 задержки. R-входы (входы занесения "0") 508, 537 соединены с линией возврата системы в исходное состояние.

Работа триггеров задержки хорошо известна квалифицированным специалистам в этой области техники и по этой причине не будет подробно описываться в этой заявке. Триггер задержки по существу имеет только один двоичный входной сигнал и один двоичный выходной сигнал. Работа триггера задержки синхронизирована с входным тактовым сигналом. Двоичный выходной сигнал триггера задержки будет допускать состояние (высокое или низкое) двоичного входного сигнала при наличии характерной передачи тактового импульса.

Как описано со ссылкой на фиг.4, производитель может показать запись данных в совместно используемый ресурс путем изменения значения соответствующего, связанного с ним, битового регистра. Аналогичным образом потребитель может показать считывание из совместно используемого ресурса путем изменения значения соответствующего, связанного с ним, битового регистра. Такой битовый регистр непрерывно представляет высокое или низкое состояние и изменяет представляемое им состояние (то есть от низкого к высокому или от высокого к низкому) каждый раз, когда обнаруживает определенный сигнал. Один такой битовый регистр иллюстрируется на фиг.5 как содержащий логический элемент 512 исключающее ИЛИ и триггер 502 задержки.

Логическое состояние Q-выхода 506 триггера 502 задержки сначала является низким, как и сигнал на линии 516, формируемый производителем; таким образом, логическое состояние выхода логического элемента 512 исключающее ИЛИ сначала является низким. Когда производитель записывает новые данные в совместно используемый ресурс, производитель инициирует операцию записи посредством формирования импульсного сигнала (P1_Add) высокого состояния, передаваемого по линии 716 связи. Выход логического элемента 512 исключающее ИЛИ принимает высокое логическое состояние в течение длительности сигнала P1_Add и высокое логическое состояние передается по линии 514 связи к D-входу 504 триггера 502 задержки. При поступлении следующего граничного перехода, формируемого тактовыми импульсами P1_Clk подсистемы-производителя, Q-выход 506 триггера 502 задержки принимает высокое логическое состояние. Квалифицированному в этой области техники специалисту будет очевидно, что длительность сигнала P1_Add равна приблизительно одному периоду тактовых импульсов Р1_Сlк производителя, обеспечивая достаточное время вхождения в режим и промежуточного хранения для формирования правильного сигнала на D-входе 504 триггера 502 задержки.

После этого логическое состояние Q-выхода 506 триггера 502 задержки передается по линии 510 как вход в логический элемент 512 исключающее ИЛИ. Если сигнал P1_Add еще имеет высокое состояние, когда сигнал Q-выхода 506 поступает в логический элемент 512 исключающее ИЛИ, то выход логического элемента 512 исключающее ИЛИ принимает низкое логическое состояние. Однако очевидно, что за время поступления следующего позитивного граничного перехода, формируемого посредством тактовых импульсов Р1_С1к, сигнал P1_Add уменьшится до низкого уровня и выход логического элемента 512 исключающее ИЛИ таким образом примет высокое логическое состояние. Таким образом, поскольку высокое логическое состояние обеспечено на D-входе 504 посредством линии 514 связи, логическое состояние Q-выхода 506 триггера 502 задержки, следовательно, остается высоким.

Когда подсистема-производитель затем записывает данные в совместно используемый ресурс, производитель формирует другой активный сигнал P1_Add на линии 516 связи как вход в логический элемент 512 исключающее ИЛИ. Однако линия 510 связи еще имеет высокое логическое состояние, которое представляет второй вход в логический элемент 512 исключающее ИЛИ. Таким образом, поскольку оба его входа имеют высокое логическое состояние, выход логического элемента 512 исключающее ИЛИ принимает низкое логическое состояние. Следовательно, линия 514 связи воспроизводит низкое логическое состояние на D-входе 504 триггера 502 задержки. Очевидно, что при поступлении следующего позитивного перехода, формируемого тактовыми импульсами P1_Clk, Q-выход 506 принимает низкое логическое состояние D-входа 504. Как описано выше, линия 510 связи передает низкое логическое состояние Q-выхода 506 как вход в логический элемент 512 исключающее ИЛИ. Когда сигнал P1_Add падает до низкого логического состояния во время или перед следующим тактом, оба входа в логический элемент 512 исключающее ИЛИ представляют низкое логическое состояние, вынуждая выход логического элемента 512 исключающее ИЛИ иметь низкое логическое состояние. Таким образом, линия 514 связи воспроизводит низкое логическое состояние на D-входе 504 триггера 502 задержки. При поступлении следующего позитивного перехода, формируемого тактовыми импульсами производителя, Q-выход 506 триггера 502 задержки принимает логическое состояние D-входа 504 и по этой причине остается имеющим низкое логическое состояние.

В описанном выше случае логический элемент 512 исключающее ИЛИ и триггер 502 задержки работают вместе как битовый регистр (или одноразрядный счетчик), который изменяет логические состояния от высокого к низкому или от низкого к высокому (то есть переключает) каждый раз, когда производитель формирует активный сигнал P1_Add на линии 516 связи. Битовый регистр поддерживает непрерывное логическое состояние (P1_Bitreg) на линии 510 связи между такими импульсами.