Изобретение относится к рычислигель- ной технике, о частности, к системам ппо- граммного управления .ибких производственных модулей АСУ ТП и может быть использовано для быстрой модификации производств в условиях невысокой квалификации персонала.

Цель изобретения - упрощение моди- цичации системы пользователю с низкой квалификацией,

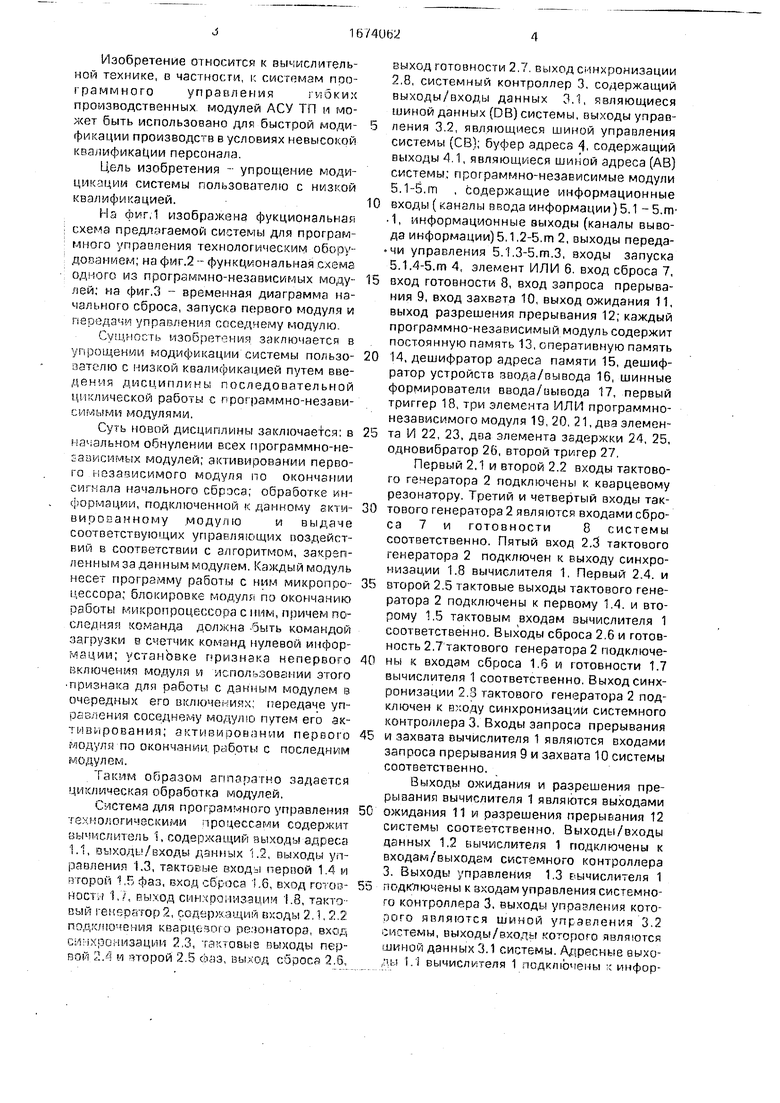

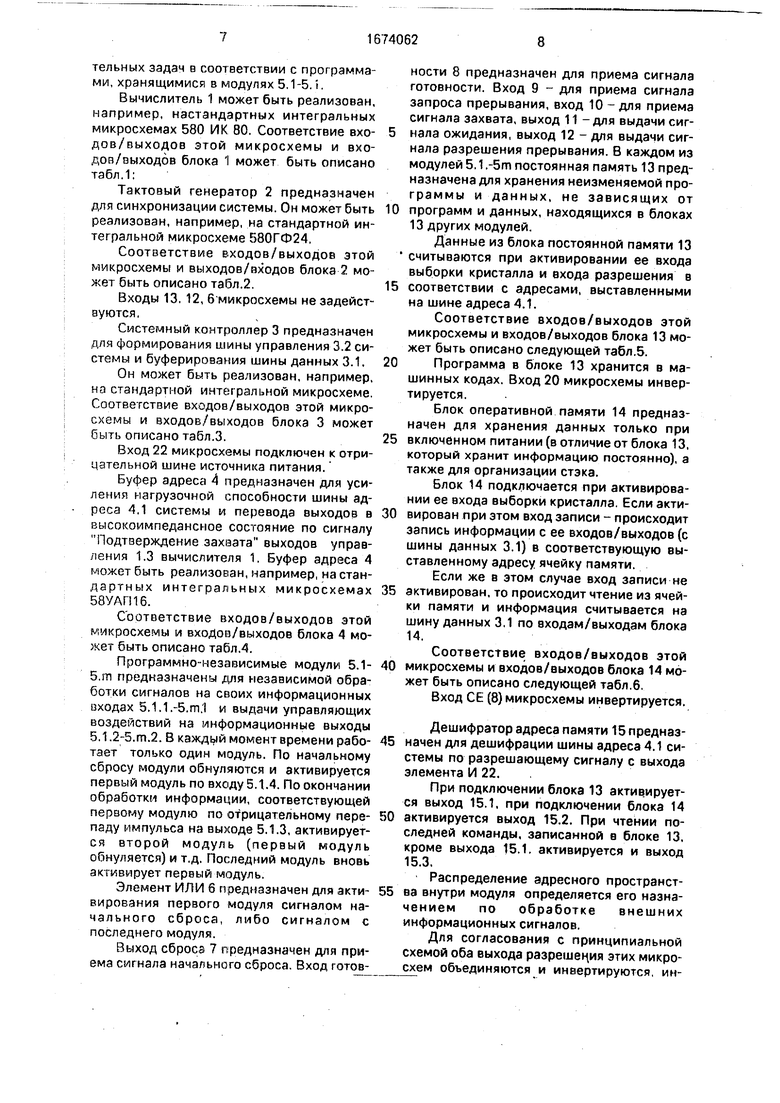

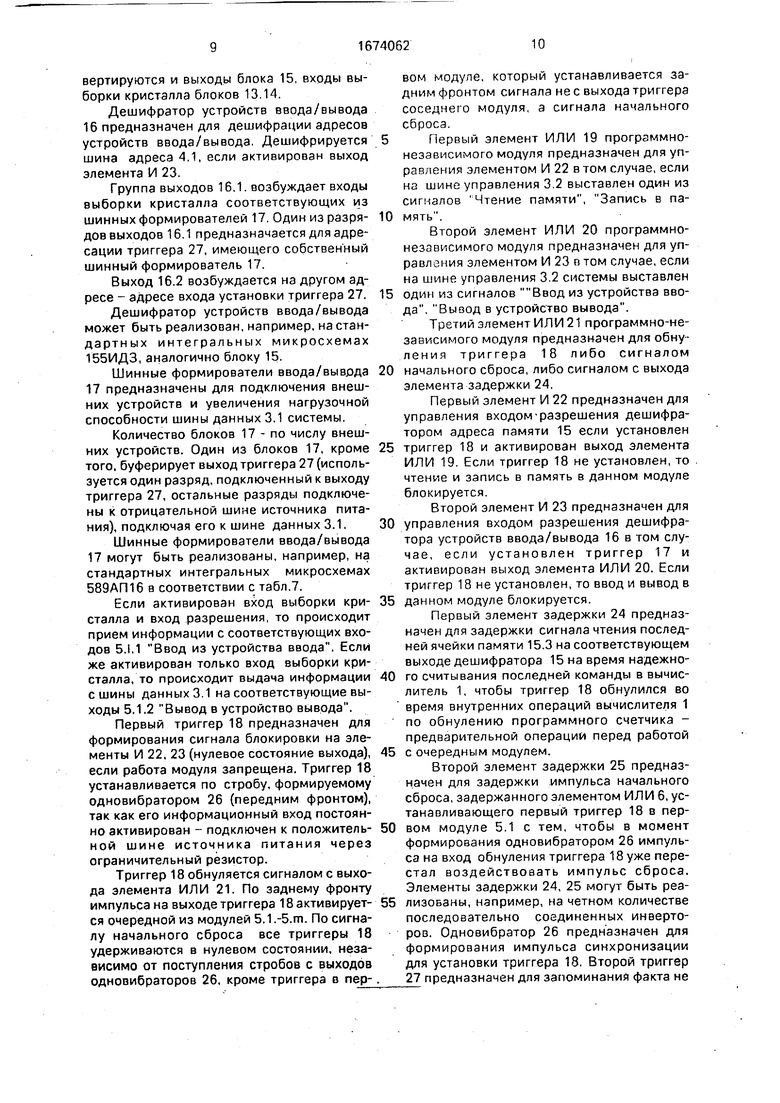

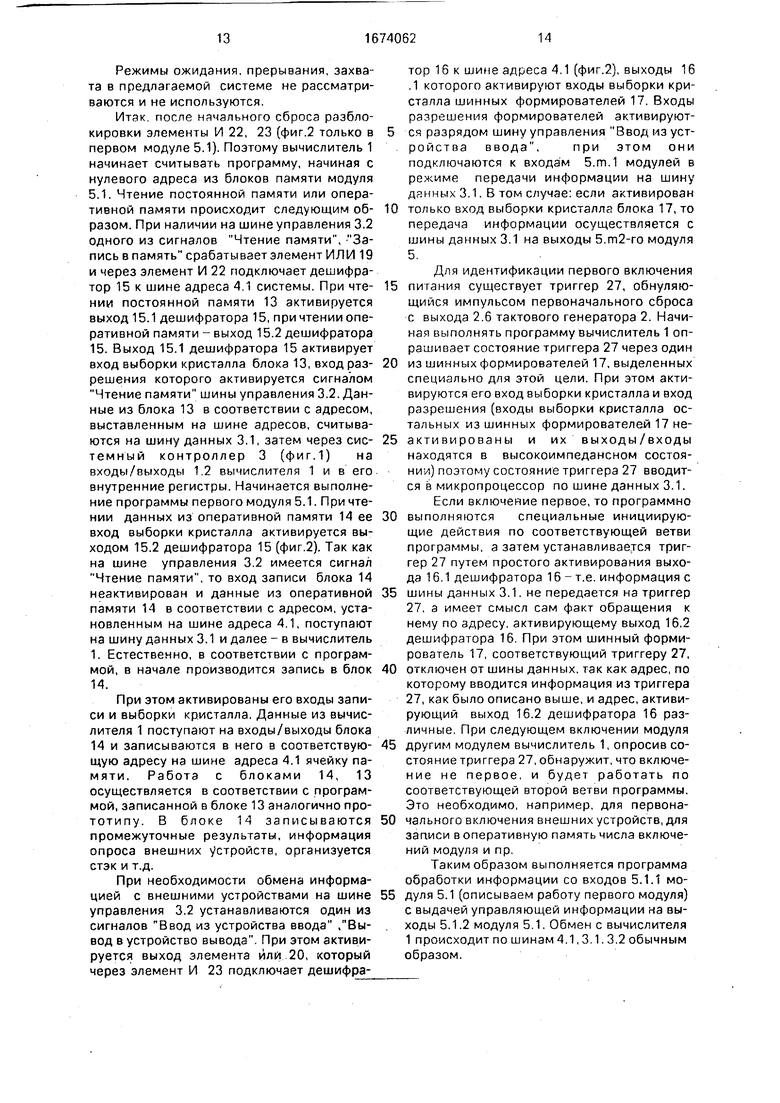

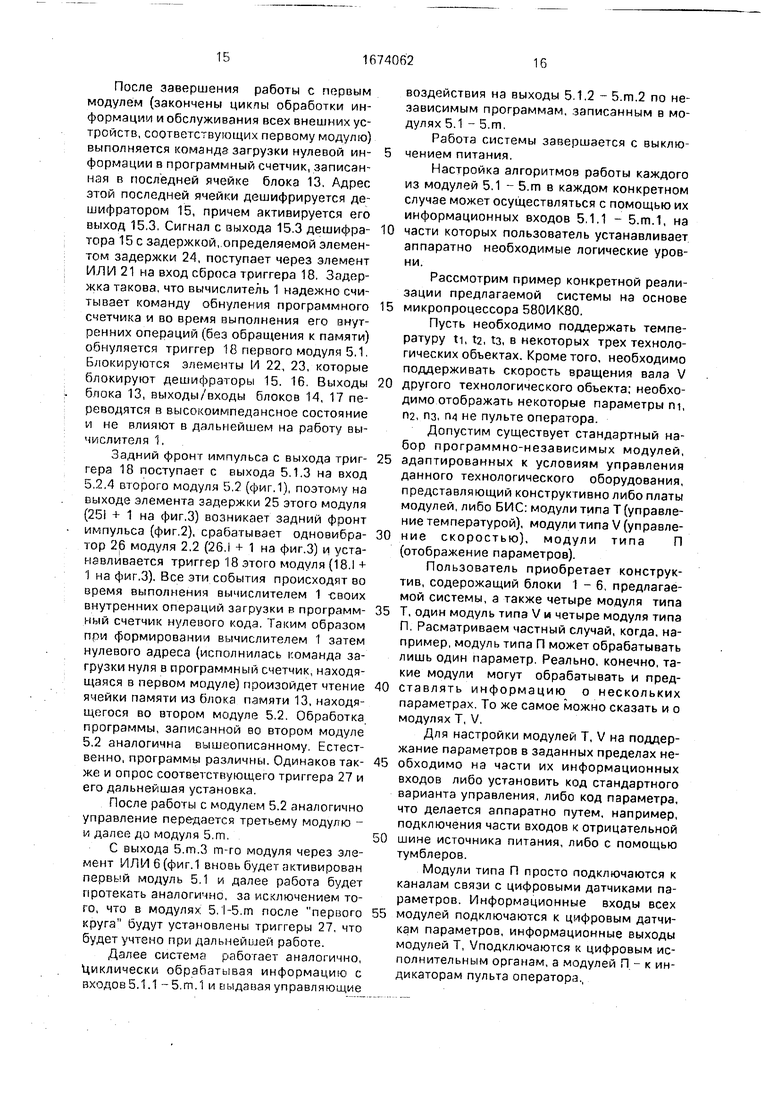

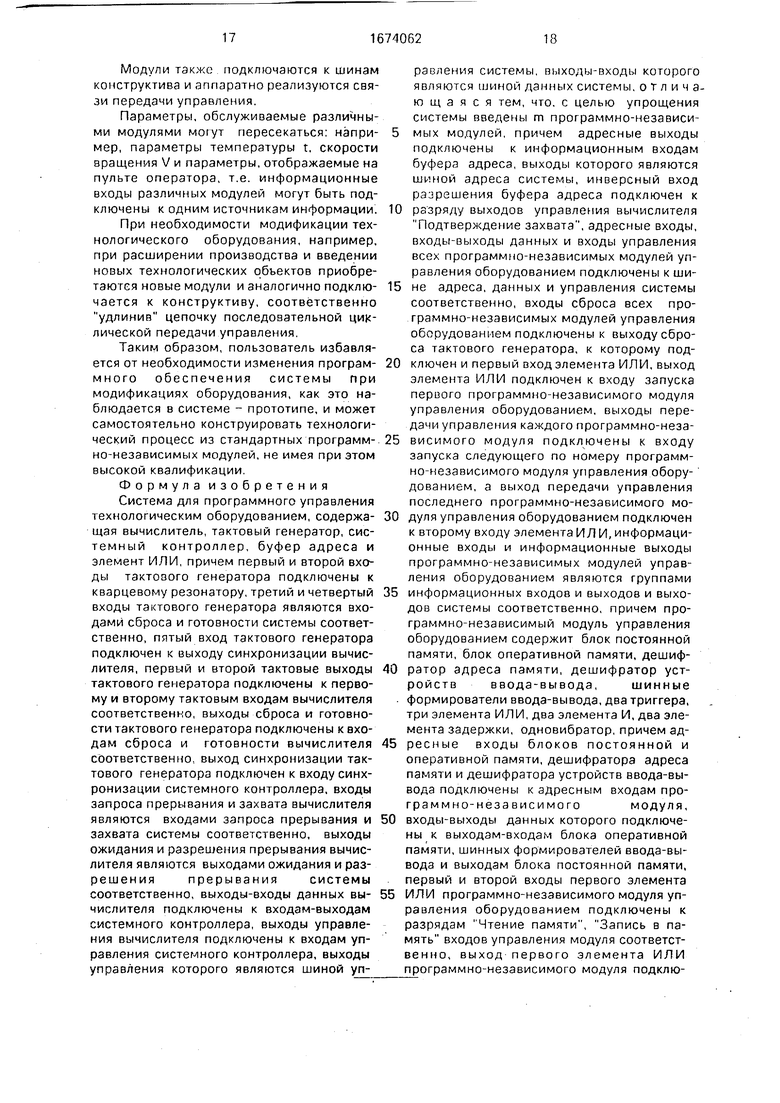

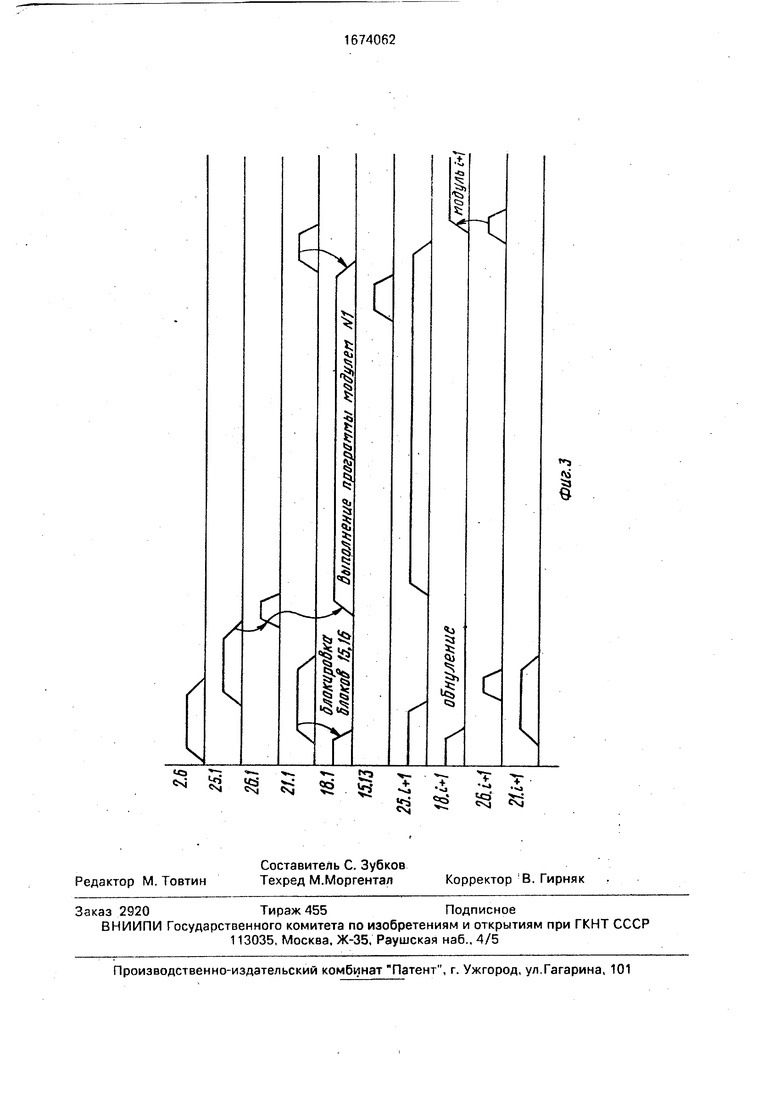

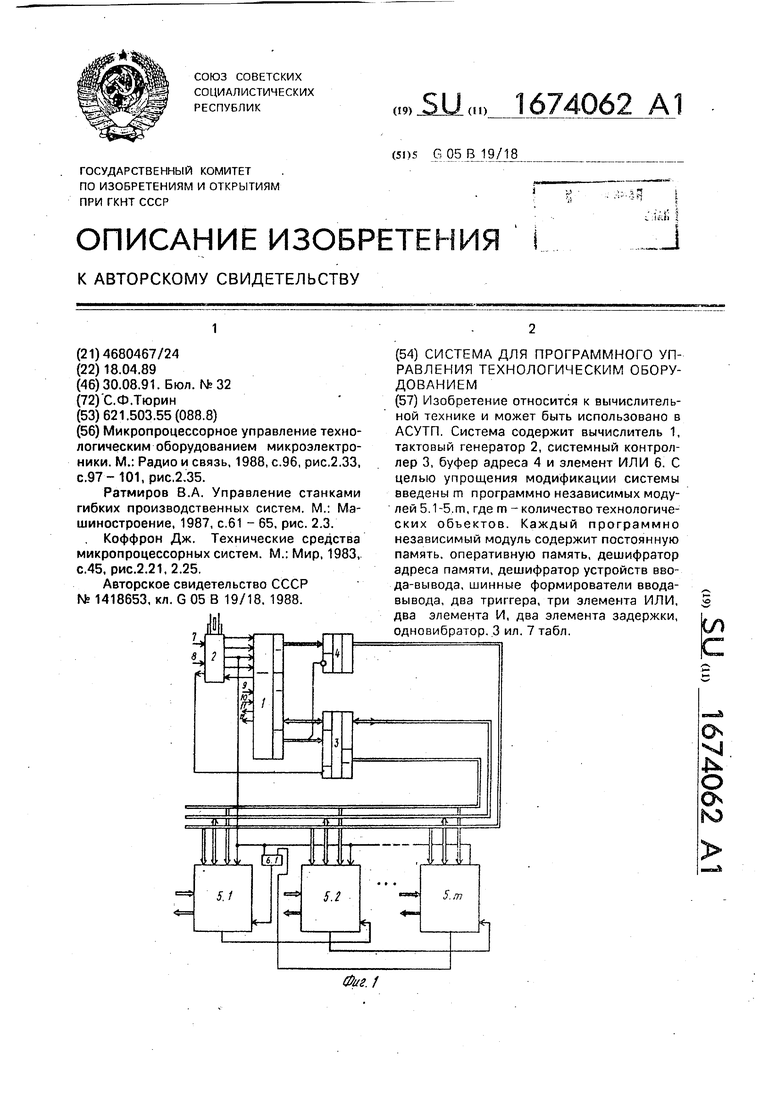

На Фиг,1 изображена фукциональная схема предлагаемой системы для программного управления технологическим оборудованием, на фиг.2 - функциональная схема одного из программно-независимых модулей; на фиг.З - временная диаграмма начального сброса, запуска первого модуля и пепедэмч упрапленич соседнему модулю

Оуцнг; гь изобрет°нич заключается в упрощении модификации системы пользо- тателю с низкой квалификацией путем введения дисциплины последовательной циклической рабпты с программно-незави- ,р-иыми модулями.

Суть попой дисциплины заключается: в i,i эльчом обнулении всех npoi раммно-не- саьисимнх модулей; активировании перво- 10 независимого модуля по окончании сигнала начального сброса, обработке ин- i; ормации, подключенной к данному активированному модулюи выдаче соответствующих управляющих воздействий в соответствии с алгоритмом, закрепленным за данным модулем. Каждый модуль несет программу работы с ним микропроцессора; блокировке модуля по окончанию работы микропроцессора с ним, причем последняя команда должна быть командой загрузки е счетчик команд нулевой инфор- мзции; установке признака непервого включения модуля и использовании этого признака для работы с данным модулем в очередных его включениях; передаче уп- ргв-ения соседнему модулю путем его активирования; активировании первого модуля по окончании работы с последним модулем.

Таким образом аппарагно задается циклическая обработка модулей.

Система для программного управления гс -мологичоскими процессами содержит вычислитель 1, содержащий выходы адреса 1.1, выходи/входы данных 1 2, выходы управления 1.3, тактовые входч нерпой 1.4 и пгорой 1 Г фаз, вход сброса 1 б, РХОД готовности 1.- , синхргмнзацим 1 8, такто вый iei;r,p 4iop 1, содержащий и/ пды 1 2 2 почкпючечия кварцевого резонатор вход си N pi. шэации 3, тактовые выходы первой 7. 4 и второй 2 5 фаз, вы;од сброса 2 6,

выход i отовности 2 , выход синхронизации 2 8, системный контроллер 3, содержащий выходы/входы данных 3 1, являющиеся шиной данных (DB) системы, выходы управлеиия 3 2, являющиеся шиной управления системы (СВ), буфер адреса 4,. содержащий выходы 4 1, являющиеся шиной адреса (АВ) системы, программно-независимые модули 5.1-Б.гл . содержащие информационные

0 входы (каналы ввода информации)5.1 - 5.пт

1, информационные выходы (каналы вывода информации)5.1,2-5.m 2, выходы передачи управления 5.1.3-5.т.3, входы запуска 5.1.4-5.т 4, элемент ИЛИ 6, вход сброса 7,

5 вход готовности 8, вход запроса прерывания 9, вход захвата 10, выход ожидания 11, выход разрешения прерывания 12, каждый программно-независимый модуль содержит постоянную память 13, оперативную память

0 14, дешифратор адреса памяти 15. дешифратор устройств ооояя/яывода 16, шинные формирователи ввода/иывода 17, первый триггер 18, три элемента ИЛИ программно- независимого модуля 19,20.21, два элемен5 та И 22, 23, два элемента задержки 24, 25, одновибрагор 26, второй тригер 27

Первый 2,1 и второй 2 2 входы тактового генератора 2 подключены к кварцевому резонатору, Третий и четвертый входы так0 тового генератора 2 являются входами сброса 7 и готовности 8 системы соответственно. Пятый вход 2 3 тактового генератора 2 подключен к выходу синхронизации 1.8 вычислителя 1. Первый 2 4. и

5 второй 2 5 тактовые выходы тактового генератора 2 подключены к первому 1.4. и второму 1 5 тактовым входам вычислителя 1 соответственно. Выходы сброса 2 6 и готовность 2.7 тактового генератора 2 подключе0 ны к входам сброса 1 6 и готовности 1.7 вычислителя 1 соответственно. Выход синхронизации 2 3 тактового генератора 2 подключен к FT.оду синхронизации системного контроллера 3. Входы запроса прерывания

5 и захвата вычислителя 1 являются входами запроса прерывания 9 и захвата 10 системы соответственно.

Выходы ожидания и разрешения прерывания вычислителя 1 являются выходами

0 ожидания 11 и разрешения прерывания 12 системы соответственно. Выходы/входы данных 1.2 вычислителя 1 подключены к входам/выходам системного контроллера 3 Выходы управления 1.3 вычислителя 1

5 подключены к входам управления сис емно- го контроллера 3, выходы управления кото рого являются шиной упрагления 3 2 сигтемы, выходы/вхолн которого являются шиной данных 3.1 системы. Адресные выхи- лн i 1 вычислителя 1 .юдключпны инфор

мационным входам буфера адреса 4, выходы которого являются шиной адреса 4 1 системы. Инверсный вход разрешения буфера адреса 4 подключен к разряду выходов управления 1.3 вычислителя 1 Подтверждение захвата. Адресные входы, входы/выходы данных и входы управления всех программно-независимых модулей 5.1- 5.т подключены к шине адреса 4.1 данных 3.1и управления 3.2 системы соответственно. Входы сброса всех программно-незави симых модулей 5.1-5.т подключены к выходу сброса 2.6 тактового генератора 2, к которому подключен и первый вход элемента ИЛИ 6. Выход элемента ИЛИ подключен к входу запуска 5.1.4 первого программно-независимого модуля 5.1. Выходы передачи управления 5.1.3-5.т-1.3 каждого программно-независимого модуля 5.1-5.т-1 подключены к входу запуска 5.2.4- 5.т.4 следующего по номеру программно- независимого модуля 5.1-5.ГП-1. Выход передачи управления 5.т 3 последнего программно-независимого модуля 5 подключен к второму входу элемента ИЛИ 6. Информационные входы 5.1.1-5.гл.1 и информационные выходы 5.1.2-5.т.2 программно-независимых модулей являются группами информационных входов и выходов системы соответственно.

В каждом программно-независимом модуле 5.1-5.ГП адресные входы постоянной 13 и оперативной 14 памяти, дешифратора адреса памяти 15 и дешифратора устройств ввода/вывода 16 подключены к адресным входам 4.1 программно-независимого модуля. Входы/выходы 3.1 данных модуля подключены к выходам/входам оперативной памяти 14, шинных формирователей ввода/вывода 17 и выходам постоянной памяти 13. Первый и второй входы первого элемента ИЛИ программно-независимого модуля 19 подключены к разрядам Чтение памяти. Запись в память входов управления 3.2 модуля соответственно. Выход первого элемента ИЛИ программно-независимого модуля 19 подключен к первому входу первого элемента И 22, второй вход которого подключен к выходу первого триггера 18 и к второму входу второго элемента И 23. Выход первого элемента И 22 подключен к входу выборки кристалла дешифратора адреса памяти 15. Вход разрешения постоянной памяти 13 подключен к разряду Чтение памяти входов управления 3.2 программно-независимого модуля. Вход выборки кристаллов блока постоянной памяти 13 подключен к первому выходу 15.1 дешифратора адреса памяти 15, второй выход 15.2 которого подключен к входу выборки кристалла блока оперативной памяти 14. вход записи которой подключен к разряду Запись в память входов управления 3.2 программно-независимого модуля. Третий 5 выход 15.3 дешифратора адреса памяти 15 подключен к входу первого элемента задержки 24. Первый и второй входы FSTOporo элемента ИЛИ 20 программно-независимо го модуля подключены к разрядам Ввод из

0 устройства ввода, Вывод в устройство вывода входов управления 3.2 программно- независимого модуля. Выход которого элемента ИЛИ 20 программно-независимого модуля подключен к первому входу вто5 рого элемента И 23, выход которого подключен к входу выборки кристалла дешифратора устройств ввода/выподэ 16. Группа выходов 16.1 дешифратора устройств ввода/вывода 16 подключена к вхо0,дам выборки кристалла шинных формирователей устройств ввода/вывода 17, входы разрешения которых подключены к разряду Ввод из устройства ввода входов управления 3.2 программно-независи5 мого модуля. Второй выход 16.2 дешифратора устройств ввода/вывода 16 подключен к входу установки второго триггера 27. Входы шинных формирователей устройств ввода/вывода 17 являются

0 информационными входами 5.т. 1-го программно-независимого модуля 5.I. Выходы шинных формирователей устройств вво- да/выьода 17 являются информационными выходами 5.i2l-ro программно-независимо5 го модуля 5.i. Выход второго триггера 27 подключен к входу одного из шинных формирователей ввода/вывода 17.

Выход первого триггера 18 является выходом передачи управления 5.i.3i-ro про0 граммно-независимого модуля 5.I, вход сброса 2.6 которого подключен к первому входу третьего элемента ИЛИ 2.1 программно-независимого модуля и к входу сброса второго триггера 27. Выход первого эле5 мента задержки 24 подключен к второму входу третьего элемента ИЛИ 21 программно-независимого модуля, выход которого подключен к входу сброса третьего триггера 18. Вход синхронизации первого тригге0 ра 18 подключен к выходу одновибратора 26, вход которого подключен к выходу второго элемента задержки 25, вход которого является входом запуска 5.i 41-го программно-независимого модуля 5.I. Информацион5 ный вход первого триггера 18 подключен через ограничительный резистор к положительной шине источника питания и постоянно активирован.

Вычислитель 1 предназначен для управления шинами системы и решения вычислительных задач в соответствии с программами, хранящимися в модулях 5.1-5.1.

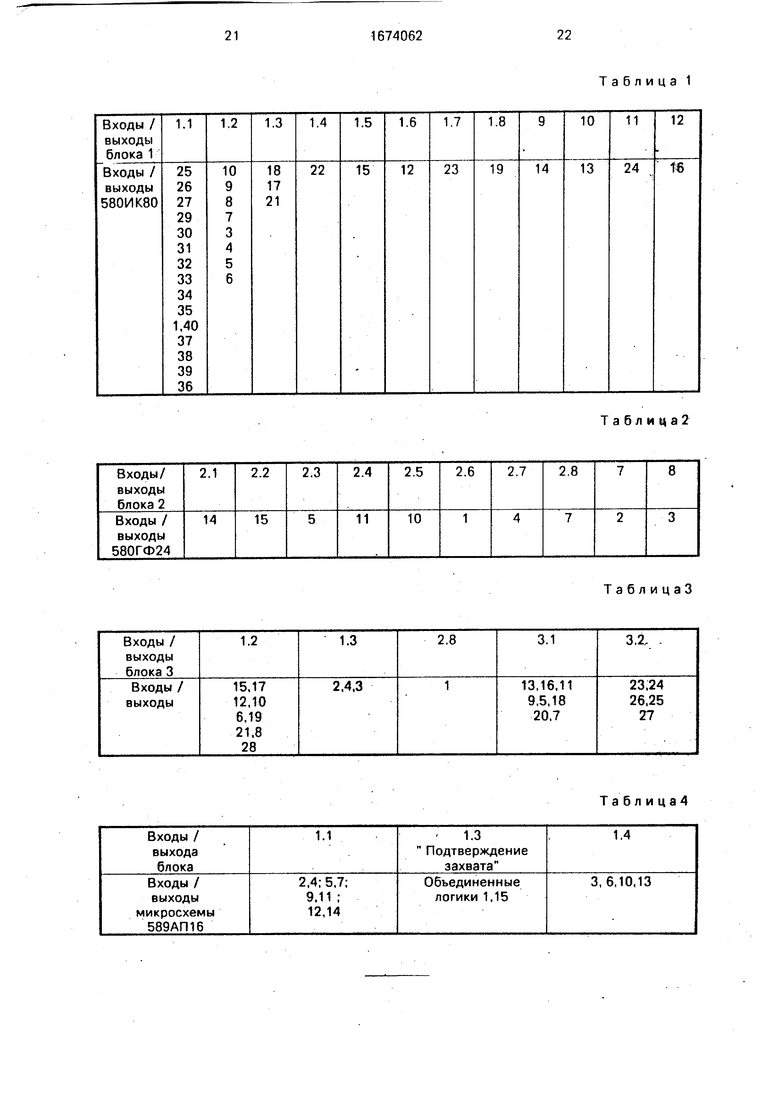

Вычислитель 1 может быть реализован, например, нестандартных интегральных микросхемах 580 ИК 80. Соответствие входов/выходов этой микросхемы и входов/выходов блока 1 может быть описано табл.1:

Тактовый генератор 2 предназначен для синхронизации системы. Он может быть реализован, например, на стандартной интегральной микросхеме 580ГФ24.

Соответствие входов/выходов этой микросхемы и выходов/входов блока 2 может быть описано табл.2.

Входы 13. 12,6 микросхемы не задейст- вуются,

Системный контроллер 3 предназначен для формирования шины управления 3.2 системы и буферирования шины данных 3.1.

Он может быть реализован, например, на стандартной интегральной микросхеме. Соответствие входов/выходов этой микросхемы и входов/выходов блока 3 может быть описано табл.3.

Вход 22 микросхемы подключен к отрицательной шине источника питания.

Буфер адреса 4 предназначен для усиления нагрузочной способности шины адреса 4.1 системы и перевода выходов в высокоимпедансное состояние по сигналу Подтверждение захвата выходов управления 1.3 вычислителя 1, Буфер адреса 4 может быть реализован, например, на стан- дартных интегральных микросхемах 58УАП16.

Соответствие входов/выходов этой микросхемы и входов/выходов блока 4 может быть описано табл.4.

Программно-независимые модули 5.1- 5.т предназначены для независимой обработки сигналов на своих информационных входах 5.1.1.-5.т.1 и выдачи управляющих воздействий на информационные выходы 5.1.2-5.т.2. В каждый момент времени работает только один модуль. По начальному сбросу модули обнуляются и активируется первый модуль по входу 5Л .4. По окончании обработки информации, соответствующей первому модулю по отрицательному перепаду импульса на выходе 5.1.3, активируется второй модуль (первый модуль обнуляется) и т.д. Последний модуль вновь активирует первый модуль.

Элемент ИЛИ 6 предназначен для активирования первого модуля сигналом начального сброса, либо сигналом с последнего модуля.

Выход сброса 7 предназначен для приема сигнала начального сброса. Вход готовности 8 предназначен для приема сигнала готовности. Вход 9 - для приема сигнала запроса прерывания, вход 10 - для приема сигнала захвата, выход 11 -для выдачи сигнала ожидания, выход 12 - для выдачи сигнала разрешения прерывания. В каждом из модулей 5.1 .-5т постоянная память 13 предназначена для хранения неизменяемой про- граммы и данных, не зависящих от

0 программ и данных, находящихся в блоках 13 других модулей.

Данные из блока постоянной памяти 13

считываются при активировании ее входа

выборки кристалла и входа разрешения в

5 соответствии с адресами, выставленными на шине адреса 4.1.

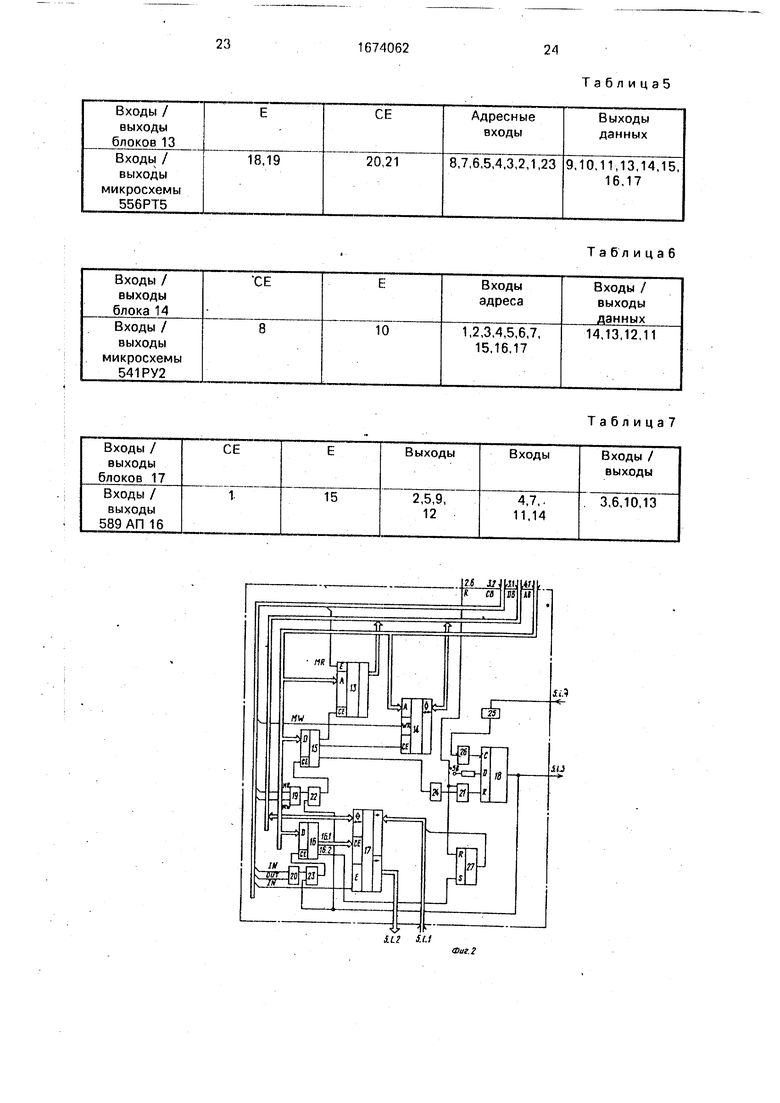

Соответствие входов/выходов этой микросхемы и входов/выходов блока 13 может быть описано следующей табл.5.

0 Программа в блоке 13 хранится в машинных кодах. Вход 20 микросхемы инвертируется.

Блок оперативной памяти 14 предназначен для хранения данных только при

5 включенном питании (в отличие от блока 13. который хранит информацию постоянно), а также для организации стэка.

Блок 14 подключается при активировании ее входа выборки кристалла. Если акти0 вирован при этом вход записи - происходит запись информации с ее входов/выходов (с шины данных 3.1) в соответствующую выставленному адресу ячейку памяти.

Если же в этом случае вход записи не

5 активирован, то происходит чтение из ячейки памяти и информация считывается на шину данных 3.1 по входам/вы ходам блока 14.

Соответствие входов/выходов этой

0 микросхемы и входов/выходов блока 14 может быть описано следующей табл.6.

Вход СЕ (8) микросхемы инвертируется.

Дешифратор адреса памяти 15 преднаэ- 5 начен для дешифрации шины адреса 4.1 системы по разрешающему сигналу с выхода элемента И 22.

При подключении блока 13 активируется выход 15.1, при подключении блока 14 0 активируется выход 15.2. При чтении последней команды, записанной в блоке 13. кроме выхода 15.1. активируется и выход 15.3,

Распределение адресного пространст- 5 ва внутри модуля определяется его назначением по обработке внешних информационных сигналов.

Для согласования с принципиальной схемой оба выхода разрешения этих микросхем объединяются и инвертируются, инвертируются и выходы блока 15. входы выборки кристалла блоков 13.14.

Дешифратор устройств ввода/вывода

16предназначен для дешифрации адресов устройств ввода/вывода. Дешифрируется шина адреса 4.1, если активирован выход элемента И 23.

Группа выходов 16.1. возбуждает входы выборки кристалла соответствующих из шинных формирователей 17. Один из разрядов выходов 16.1 предназначается для адресации триггера 27, имеющего собственный шинный формирователь 17.

Выход 16.2 возбуждается на другом адресе - адресе входа установки триггера 27.

Дешифратор устройств ввода/вывода может быть реализован, например, на стандартных интегральных микросхемах 155ИДЗ, аналогично блоку 15.

Шинные формирователи ввода/вывддэ

17предназначены для подключения внешних устройств и увеличения нагрузочной способности шины данных 3.1 системы.

Количество блоков 17 - по числу внешних устройств. Один из блоков 17, кроме того, буферирует выход триггера 27 (используется один разряд, подключенный к выходу триггера 27, остальные разряды подключены к отрицательной шине источника питания), подключая его к шине данных 3.1.

Шинные формирователи ввода/вывода 17 могут быть реализованы, например, на стандартных интегральных микросхемах 589АП16 в соответствии с табл.7.

Если активирован вход выборки кристалла и вход разрешения, то происходит прием информации с соответствующих входов 5.1.1 Ввод из устройства ввода. Если же активирован только вход выборки кристалла, то происходит выдача информации с шины данных 3.1 на соответствующие выходы 5.1.2 Вывод в устройство вывода.

Первый триггер 18 предназначен для формирования сигнала блокировки на элементы И 22, 23 (нулевое состояние выхода), если работа модуля запрещена. Триггер 18 устанавливается по стробу, формируемому одновибратором 26 (передним фронтом), так как его информационный вход постоянно активирован - подключен к положительной шине источника питания через ограничительный резистор.

Триггер 18 обнуляется сигналом с выхода элемента ИЛИ 21. По заднему фронту импульса на выходе триггера 18 активируется очередной из модулей 5.1.-5.т. По сигналу начального сброса все триггеры 18 удерживаются в нулевом состоянии, независимо от поступления стробов с выходов однопибраторов 26. кроме триггера о пер- .

вом модуле, который устанавливается задним фронтом сигналя не с выхода триггера соседнего модуля, а сигнала начального сброса.

5Первый элемент ИЛИ 19 программнонезависимого модуля предназначен для уп- рпчления элементом И 22 в том случае, если и;; шине управления 3.2 выставлен один из CHI налов Чтение памяти, Запись в па- 0 мять.

Второй элемент ИЛИ 20 программно- незовпсимого модуля предназначен для уп- раолзния элементом И 23 п том случае, если на шине управления 3.2 системы выставлен

5 один из сигналов Ввод из устройства ввода, Выоод в устройство вывода,

Третий элемент ИЛИ 21 программно-независимого модуля предназначен для обнуления триггера 18 либо сигналом

0 начального сброса, либо сигналом с выхода элемента задержки 24.

Первый элемент И 22 предназначен для управления входом-разрешения дешифратором адреса памяти 15 если установлен

5 триггер 18 и активирован выход элемента ИЛИ 19. Если триггер 18 не установлен, то чтение и запись в память в данном модуле блокируется.

Второй элемент И 23 предназначен для

0 управления входом разрешения дешифратора устройств ввода/вывода 16 в том случае, если установлен триггер 17 и активирован выход элемента ИЛИ 20. Если триггер 18 не установлен, то ввод и вывод в

5 данном модуле блокируется.

Первый элемент задержки 24 предназначен для задержки сигнала чтения последней ячейки памяти 15.3 на соответствующем выходе дешифратора 15 на время надежно0 го считывания последней команды в вычислитель 1, чтобы триггер 18 обнулился во время внутренних операций вычислителя 1 по обнулению программного счетчика - предварительной операции перед работой

5 с очередным модулем.

Второй элемент задержки 25 предназначен для задержки импульса начального сброса, задержанного элементом ИЛИ 6, устанавливающего первый триггер 18 в пер0 вом модуле 5.1 с тем. чтобы в момент формирования одновибратором 26 импульса на вход обнуления триггера 18 уже перестал воздействовать импульс сброса. Элементы задержки 24. 25 могут быть реа5 лизованы, например, на четном количестве последовательно соединенных инверторов. Одновибратор 26 предназначен для формирования импульса синхронизации для установки триггера 18. Второй триггер 27 предназначен для запоминания факта не

первого включения модуля Трш тр 27 обнуляется сигналом начального сброса Вычислитель 1 программно- проверяет состояние пыходз этого триггера, подключая соответствующий ему на шинных формирователей 17. После первого включения модуля триггер 27 устанавливается при возбуждении выхода 16.2 дешифратора 16. Второй тригг- грр 27 может быть реализован, например, на сгандэртной интегральной микросхеме 1Ь5ТМ2.

Система работает следующим образом.

После включения питания на вход 7 по- дрется импульс сброса, который с выхода 2.6 тактового генератора 2 поступает на вход 1 G вычислителя 1 и на входы сброса гтех кю/н лей 5.1 5 m (фиг.1). В микропроцессоре обнуляется программный счетчик и нпциируетгя работа управляющего авто- г л1 а

HMIIWU-C сброса с выхода 2.6 генератора 2 (фиг.2 3) в каждом модуле 5.1-5.гл через цемент ИПИ 21 поступает на вход сброса тренера 10 который обнуляется, если он был установлен, или подтверждается его ну- свое состояние. Через элемент ИЛИ 6 (фш 1) импульс сброса поступает на вход 5 1 / т тянопки первого модуля 5.1. Поэтому (Фпг.2.3) импульс сброса 2.6 задержанный на элементе задержки 25 поступает на од- нопибратор 26 Задний фронт импульса на мходп элемента задержки 25 возникает в норном модуле 5 1 в тот момент, когда уже закончилось действие импульса сброса на пиходе элемента ИЛИ 21. Затем срабатывает однзвиПратор 26, по переднему фронту ичпутьсз которого устанавлиьается триг- iep 18 в первом модуле 5.1 (18.1 на фиг.З). В и-код триггера 10 разблокирует элементы 11 22, 23 (фиг.2). Следует отметить тот факт, при обнулении триггеров 18 в модулях F, I.5.IT) при переходе триггера 18.1 в модуле 5. (сосед слева) в модуле 5. + 1 на пыхоцо элемента задержки 25.i + 1 может наблюдаться задний фронт импульса обну- пения триггера 18 (фиг.З). При эюм возможно срабатывание однооибратора 26.i + 1 в этом модуле. Однако, это не приведет к установке триггера 18.1+ 1, так как длительнее ь гмпульса первоначального сброса 2.G, поступающего через элемент ИЛИ 21.1 i 1, Оольи времени задержки импульса с РЫХСДЯ триггера 1C.) предыдущего модуля па ломенте 25 I и срабатывания одновиб- рагорэ Г.О. Триггеры 18 всех модулей представляютсобойD-григгеры, информационные входы которых подклю- че пь чер°з ограничительный резистор к по- пожитсльнои шине источника питания.

Поэтому при действии сигнала сброса триггер 18 не установится по своему синх- ровходу На фиг 3 показано, что сработал одновибратор 26 И 1, но так как действует

сигнал сброса 21.1 + 1, то триггер 181 + 1 остается обнуленным. Таким образом, после начального сброса триггеры 18 обнулены во всех модулях 5.1-5.т, кроме первого, установленного импульсом сброса через

0 элемент ИЛИ 6 по входу 5 1.4(фиг.1) «этому времени начинает функционировать управляющий автомат вычислителя 1 под воздействием тактовых сигналов 1.4, 1.5, формируемых на выходах 2.4, 2.5 тактового

5 генератора 2. Стабильность тактовой часто ты обеспечивается кварцевым резонатором, подключенным к входам 2 1, 2.2 генератора 2.

Вычислитель генерирует сигналы адре0 са на выходах 1.1 и управления 1 3, а по выходам/входам данных 1.2 в первом такте каждого машинного цикла выдает слово состояния При этом на выходе 1.8 формируется сигнал синхронизации, поступающий

5 на вход 2.3 тактового генератора 2, строби- руя там и с его выхода 2 8 поступает на вход синхронизации системного контроллера 3, в который записывается слово состояния вычислителя 1. По слову состояния и сигна0 лам упранления 1.3 системный контроллер 3 формирует шину управления (СВ) системы Кроме того, системный контроллер 3 увеличивает нагрузочную способность выходов/входов 1.2 вычислителя 1 и формиру5 ет шину данных 3.1 системы.

Буфер адреса 4 увеличивает нагрузочную способность шины адреса и формирует шину адреса 4.1 системы.

Система может быть переведена в ре0 жим ожидания путем обнуления входа готовности 3 системы, при этом обнуляется вход готовности 1.7 вычислителя 1 сигналом с выхода 2.7 генератора 2 и на выходе 11 системы устанавливается сигнал 1,сигна5 лизирующий о переходе системы в режим ожидания. Система может быть переведена в режим прерывания путем подачи сигнала запроса на вход 9, после перехода в режим прерывания, если они не запрещены про0 граммно, обнуляется выход 12 разрешения прерывания. Система может быть переведена и режим захвата путем подачи сигнала захвата на вход 10, при этом на выходах управления 1.3 формируется сигнал под5 тверждения захвата, который переводит выходы 4.1 буфера адреса 4 в состояние высокого импеданса (по его входу разрешения) Также переводятся в состояние высокого импенданса шина управления 3 2 и ши о данных 3.1 системы.

Режимы ожидания, прерывания захва та в предлагаемой системе не рассматриваются и не используются

Итак послг начального сброса кировки элементы И 22, 23 (фиг.2 только в первом модуле 5 1) Поэтому вычислитель 1 начинает считывать программу, начиная с нулевого адреса из блоков памяти модуля 5 1 Чтение постоянной памяти или оперативной памяти происходит следующим образом. При наличии на шине управления 3 2 одного из сигналов Чтение памяти Запись в память срабатывает элемент ИЛ И 19 и через элемент И 22 подключает дешифра тор 15 к шине адреса 4 1 системы При чтении постоянной памяти 13 активируется выход 15 1 дешифратора 15, при чтении оперативной памяти - выход 15 2 дешифратора 15. Выход 15.1 дешифратора 15 активирует вход выборки кристалла блока 13, вход разрешения которого активируется сигналом Чтение памяти шины управления 3 2 Данные из блока 13 в соответствии с адресом выставленным на шине адресов, считываются на шину данных 3 1, затем через системный контроллер 3 (фиг 1) на входы/выходы 1 2 вычислителя 1 и в его внутренние регистры Начинается выполнение программы первого модуля 5 1 Причте- нии данных из оперативной памяти 14 ее вход выборки кристалла активируется выходом 15.2 дешифратора 15 (фиг 2) Так как на шине управления 3 2 имеется сигнал Чтение памяти то вход записи блока 14 неактивирован и данные из оперативной памяти 11 в соответствии с адресом, установленным на шине адреса 4 1, поступают на шину данных 3 1 и далее - в вычислитель 1 Естественно, в соответствии с программой, в начале производится запись в блок 14.

При этом активированы его входы записи и выборки кристалла. Данные из вычислителя 1 поступают на входы/выходы блока 14 и записываются в него в соответствующую адресу на шине адреса 4 1 ячейку памяти. Работа с блоками 14, 13 осуществляется в соответствии с программой, записанной в блоке 13 аналогично прототипу В блоке 14 записываются промежуточные результаты, информация опроса внешних устройств организуется стэк и т.д

При необходимости обмена информацией с внешними устройствами на шине управления 3 2 устанавливаются один из сигналов Ввод из устройства ввода .Вывод в устройство вывода При этом активируется выход элемента или 20. который через элемент И 23 подключает дешифратор 16 к шине адреса 4 1 (фиг 2) выходы 16 1 которого активируют входы выборки кристалла шинных формирователей 17 Входы разрешения формирователей активируют- 5 сч разрядом шину управления Ввод из устройства ввода,при этом они подключаются к входам 5 m 1 модулей в режиме передачи информации на шину данных 3 1 В том случае если активирован 0 только вход выборки кристалл блока 17, то передача информации осуществляется с шины данных 3 1 на выходы 5 т2-го модуля 5

Для идентификации первого включения 5 питания существует триггер 27, обнуляющийся импульсом первоначального сброса г. выхода 2 6 тактового генератора 2 Начиная выполнять программу вычислитель 1 опрашивает состояние триггера 27 через один

0 из шинных формирователей 17, выделенных специально для этой цели При этом активируются его вход выборки кристалла и вход разрешения (входы выборки кристалла остальных из шинных формирователей 17 не5 активированы и их выходы/входы находятся в высокоимпедэнсном состоянии) поэтому состояние триггера 27 вводится в микропроцессор по шине данных 3 1. Если включение первое, то программно

0 выполняются специальные инициирующие действия по соответствующей ветви программы а затем устанавливается триггер 27 путем простого активирования выхода 16 1 дешифратора 16 те информация с

5 шины данных 3 1 не передается на триггер 27 а имеет смысл сам факт обращения к нему по адресу активирующему выход 16 2 дешифратора 16 При этом шинный формирователь 17, соответствующий триггеру 27

0 отключен от шины данных так как адрес, по которому вводится информация из триггера 27, как было описано выше и адрес, активирующий выход 162 дешифратора 16 различные При следующем включении модуля

5 другим модулем вычислитель 1, опросив состояние триггера 27 обнаружит что включение не первое и будет работать по соответствующей второй ветви программы Это необходимо, например для первона0 чального включения внешних устройств, для записи в оперативную память числа включений модуля и пр

Таким образом выполняется программа обработки информации со входов 5.1 1 мо5 дуля 5.1 (описываем работу первого модуля) с выдачей управляющей информации на выходы 5 1.2 модуля 5 1 Обмен с вычислителя 1 происходит по шинам 4 1 3 1 32 обычным образом.

После завершения работы с первым модулем (закончены циклы обработки информации и обслуживания всех внешних устройств, соответствующих первому модулю) выполняется команда загрузки нулевой информации в программный счетчик, записанная в последней ячейке блока 13. Адрес этой последней ячейки дешифрируется дешифратором 15, причем активируется его выход 15.3. Сигнал с выхода 15.3 дешифратора 15 с задержкой, определяемой элементом задержки 24, поступает через элемент ИЛИ 21 на вход сброса триггера 18. Задержка такова, что вычислитель 1 надежно считывает команду обнуления программного счетчика и во время выполнения его внутренних операций (без обращения к памяти) обнуляется триггер 18 первого модуля 5.1. Блокируются элементы И 22, 23. которые блокируют дешифраторы 15. 16. Выходы бпока 13, выходы/входы блоков 14, 17 переводятся в высокоимпедансное состояние и не влияют в дальнейшем на работу вычислителя 1.

Задний фронт импульса с выхода триггера 18 поступает с выхода 5.1.3 на вход 5.2.4 второго модуля 5.2 (фиг.1), поэтому на выходе элемента задержки 25 этого модуля (25 + 1 на фиг.З) возникает задний фронт импульса (фиг.2), срабатывает одновибра- тор 26 модуля 2.2 (26.) + 1 на фиг.З) и устанавливается триггер 18 этого модуля (18.1 + 1 на фиг.З). Все эти события происходят во время выполнения вычислителем 1 своих внутренних операций загрузки в программный счетчик нулевого кода. Таким образом при формировании вычислителем 1 затем нулевого адреса (исполнилась команда загрузки нуля в программный счетчик, находящаяся в первом модуле) произойдет чтение ячейки памяти из блока памяти 13, находящегося во втором модуле 5.2. Обработка программы, записанной во втором модуле 5.2 аналогична вышеописанному. Естественно, программы различны. Одинаков также и опрос соответствующего триггера 27 и его дальнейшая установка.

После работы с модулем 5.2 аналогично управление передается третьему модулю - и далее до модуля 5.т.

С выхода 5.т.3 т-го модуля через элемент ИЛИ 6 (фиг.1 вновь будет активирован первый модуль 5.1 и далее работа будет протекать аналогично, за исключением того, что в модулях 5.1-5.т после первого круга будут установлены триггеры 27, что будет учтено при дальнейшей работе.

Далее система работает аналогично, Циклически обрабатывая информацию с входов 5.1.1 -5.ГП.1 и выдавая управляющие

воздействия на выходы 5.1.2 - 5.гл.2 по независимым программам, записанным в модулях 5.1 - 5.т

Работа системы завершается с выключением питания.

Настройка алгоритмов работы каждого из модулей 5,1 -- 5.т в каждом конкретном случае может осуществляться с помощью их информационных входов 5.1.1 - 5.т.1, на

0 части которых пользователь устанавливает аппаратно необходимые логические уровни.

Рассмотрим пример конкретной реализации предлагаемой системы на основе

5 микропроцессора 580ИК80.

Пусть необходимо поддержать температуру ti, t2, 13, в некоторых трех технологических объектах. Кроме того, необходимо поддерживать скорость вращения вала V

0 другого технологического объекта; необходимо отображать некоторые параметры гм, П2, пз, П4 не пульте оператора.

Допустим существует стандартный набор программно-независимых модулей,

5 адаптированных к условиям управления данного технологического оборудования, представляющий конструктивно либо платы модулей, либо БИС: модули типа Т (управление температурой), модули типа V (управле0 ние скоростью), модули типа П (отображение параметров).

Пользователь приобретает конструктив, содерожащий блоки 1 - 6, предлагаемой системы, а также четыре модуля типа

5 Т, один модуль типа V и четыре модуля типа П. Расматриваем частный случай, когда, например, модуль типа П может обрабатывать лишь один параметр. Реально, конечно, такие модули могут обрабатывать и пред0 ставлять информацию о нескольких параметрах. То же самое можно сказать и о модулях Т, V.

Для настройки модулей Т, V на поддержание параметров в заданных пределах не5 обходимо на части их информационных входов либо установить код стандартного варианта управления, либо код параметра, что делается аппаратно путем, например, подключения части входов к отрицательной

0 шине источника питания, либо с помощью тумблеров.

Модули типа П просто подключаются к каналам связи с цифровыми датчиками параметров. Информационные входы всех

5 модулей подключаются к цифровым датчикам параметров, информационные выходы модулей Т, Уподключаются к цифровым исполнительным органам, а модулей П - к индикаторам пульта оператора.,

МОДУЛИ также подключаются к тинам юиструкгива и аппарате реализуются связи передачи управления.

Параметры, обслуживаемые различными модулями Moiyi пересекаться: например, параметры температуры t. скорости аращения V и параметры, отображаемые на пульте оператора, т.е. информационные входы различных модулей могут быть подключены к одним источникам информации.

При необходимости модификации технологического оборудования, например, при расширении производства и введении новых технологических объектов приобретаются новые модули и аналогично подключается к конструктиву, соответственно удлинив цепочку последовательной циклической передачи управления.

Таким образом, пользователь избавляется от необходимости изменения програм- много обеспечения системы при модификациях оборудования, как это наблюдается в системе - прототипе, и может самостоятельно конструировать технологический процесс из стандартных программно-независимых модулей, не имея при этом высокой квалификации.

Формула изобретения

Система для программного управления (ехнологическим оборудованием, содержащая вычислитель, тактовый генератор, системный контроллер, буфер адреса и элемент ИЛИ, причем первый и второй входы тактозого генератора подключены к кварцевому резонатору, третий и четвертый входы тактового генератора являются входами сброса и готовности системы соответственно, пятый вход тактового генератора подключен к выходу синхронизации вычислителя, первый и второй тактовые выходы тактового генератора подключены к первому и второму тактовым входам вычислителя соответственно, выходы сброса и готовности тактового генератора подключены к входам сброса и готовности вычислителя соответственно, выход синхронизации тактового генератора подключен к входу синхронизации системного контроллера, входы запроса прерывания и захвата вычислителя являются входами запроса прерывания и захвата системы соответственно, выходы ожидания и разрешения прерывания вычислителя являются выходами ожидания и разрешения прерывания системы соответственно, выходы-входы данных вычислителя подключены к входам-выходам системного контроллера, выходы управления вычислителя подключены к входам управления системного контроллера, выходы управления которого являются шиной упропления системы выходы-входы которого являются шиной данных системы, отличающаяся тем. что, с целью упрощения системы введены m программно-независи- 5 мых модулей, причем адресные выходы подключены к информационным входам буфера адреса, выходы которого являются шиной адреса системы, инверсный вход ртрзшения буфера адреса подключен к 10 разряду выходов управления вычислителя Подтверждение захвата, адресные входы, входы-выходы данных и входы управления всех программно-независимых модулей управления оборудованием подключены к ши- 5 не адреса, данных и управления системы соответственно, входы сброса всех программно-независимых модулей управления оборудованием подключены к выходу сброса тактового генератора, к которому под- 0 ключен и первый вход элемента ИЛИ. выход элемента ИЛИ подключен к входу запуска первого программно-независимого модуля управления оборудованием, выходы передачи управления каждого программно-неза- 5 висимого модуля подключены к входу запуска следующего по номеру программно-независимого модуля управления оборудованием, а выход передачи управления последнего программно-независимого мо- 0 дуля управления оборудованием подключен к второму входу элемента И Л1/1, информационные входы и информационные выходы программно-независимых модулей управления оборудованием являются группами 5 информационных входов и выходов и выходов системы соответственно, причем программно-независимый модуль управления оборудованием содержит блок постоянной памяти, блок оперативной памяти, дешиф- 0 ратор адреса памяти, дешифратор устройствввода-вывода,шинные формирователи ввода-вывода, два триггера, три элемента ИЛИ. два элемента И, два элемента задержки, одновибратор. причем ад- 5 ресные входы блоков постоянной и оперативной памяти, дешифратора адреса памяти и дешифратора устройств ввода-вывода подключены к адресным входам программно-независимого модуля, 0 входы-выходы данных которого подключены к выходам-входам блока оперативной памяти, шинных формирователей ввода-вывода и выходам блока постоянной памяти, первый и второй входы первого элемента 5 ИЛИ программно-независимого модуля управления оборудованием подключены к разрядам Чтение памяти, Запись в память входов управления модуля соответственно, выход первого элемента ИЛИ программно-независимого модуля подключем к первому входу первого элемента И, второй вход которого подключен к выходу первого триггера и к второму входу второго элемента И. выход первого элемента И подключен к входу выборки кристалла дешифратора адреса памяти, вход разрешения блока постоянной памяти подключен к разряду Чтение памяти входов управления программно-независимого модуля управления оборудованием, вход выборки кристалла блока постоянной памяти подключен к первому выходу дешифратора адреса памяти, второй выход которого подключен к входу выборки кристалла блока оперативной памяти, вход записи подключен к разряду Запись в память входов управления программно-независимого модуля управления оборудованием, третий выход дешифратора адреса памяти подключен к входу первого элемента задержки, первый и второй входы второго элемента ИЛИ программно-независимого модуля управления оборудованием подключены к разрядам Ввод из устройства ввода, Вывод в устройство вывода входов управления программно-независимогомодуляуправления оборудованием, выход второго элемента ИЛИ программно-независимого модуля управления оборудованием подключен к первому входу второго элемента И, выход которого подключен к входу выборки кристалла дешифратора устройств ввода-вывода, группа выходов дешифратора устройств ввода-вывода подключена к входам выборки кристалла шинных формирователей устройств ввода- вывода, входы разрешения которых подключены к разряду Ввод из устройства ввода входов управления программно-независимого модуля управления оборудованием, второй выход дешифратора

устройств ввода-вывода подключен к входу установки второго триггера, входы шинных формирователей устройств ввода-вывода являются информационными входами программно-независимого модуля, выходы

шинных формирователей устройств ввода- вывода являются информационными выходами программно-независимого модуля управления оборудованием, выход второго триггера подключен к входу шинного формирователя ввода-вывода, выход первого триггера является выходом передачи управления программно-независимого модуля управления оборудованием, вход сброса которого подключен к первому входу третьего

элемента ИЛИ программно-независимого модуля управления оборудованием и к входу сброса второго триггера, выход первого элемента задержки подключен к второму входу третьего элемента ИЛИ программнонезависимого модуля управления оборудованием, выход которого подключен к входу сброса первого триггера, вход синхронизации первого триггера подключен к выходу одновибратора. вход которого подключей к выходу второго элемента задержки, вход которого является входом запуска программно-независимого модуля управления оборудованием, информационный вход первого триггера

подключен через ограничительный резистор к положительной шине источника питания и постоянно активирован.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| Микропроцессорная система для программного управления технологическим оборудованием | 1988 |

|

SU1525678A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1751772A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Микропроцессорная система для программного управления технологическими процессами | 1987 |

|

SU1418653A1 |

Изобретение относится к вычислительной технике и может быть использовано в АСУТП. Система содержит вычислитель 1, тактовый генератор 2, системный контроллер 3, буфер адреса 4 и элемент ИЛИ 6. С целью упрощения модификации системы введены M программно независимых модулей 5.1 - 5.M, где M - количество технологических объектов. Каждый программно независимый модуль содержит постоянную память, оперативную память, дешифратор адреса памяти, дешифратор устройств ввода-вывода, шинные формирователи ввода-вывода, два триггера, три элемента ИЛИ, два элемента И, два элемента задержки, одновибратор. 3 ил.

Таблица2

ТаблицаЗ

Таблица

Тэблицэб

Таблицаб

Таблица

иг it.t

Фаг. 2

| Микропроцессорное управление технологическим оборудованием микроэлектроники | |||

| М.: Радио и связь, 1988, с.96, рис,2 33, с.97- 101, рис.2.35 | |||

| Ратмиров В.А | |||

| Управление станками гибких производственных систем | |||

| М/ Машиностроение, 1987, с.61 - 65, рис | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Коффрон Дж | |||

| Технические средства микропроцессорных систем | |||

| М.: Мир, 1983, с.45, рис.2.21,2.25 | |||

| Микропроцессорная система для программного управления технологическими процессами | 1987 |

|

SU1418653A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1991-08-30—Публикация

1989-04-18—Подача