Изобретение относится к микропроцессорной технике и может быть использовано в автоматизированных системах для программного управления

технологическими процессами, например, в системах числового программного управления производственных комплексов,роботов-манипуляторов и т.д.

Цель изобретения - позззпиекие производительности микропроцессорной системы путем введения режима адаптивной выборки данных.

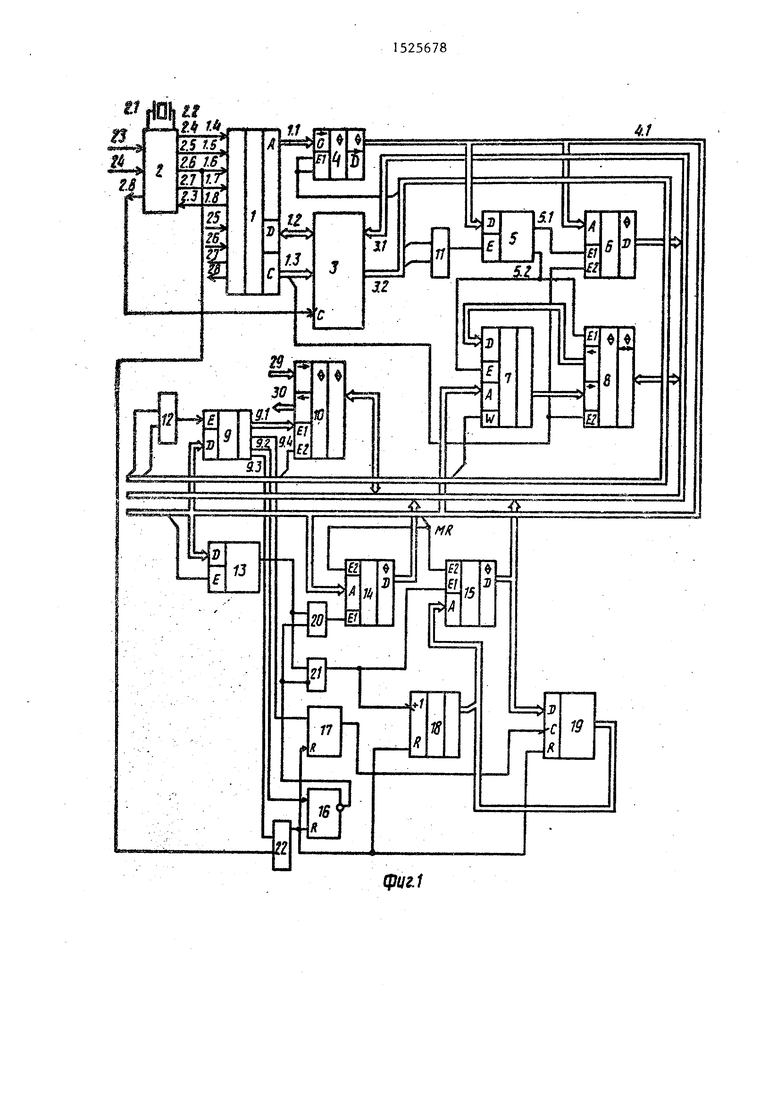

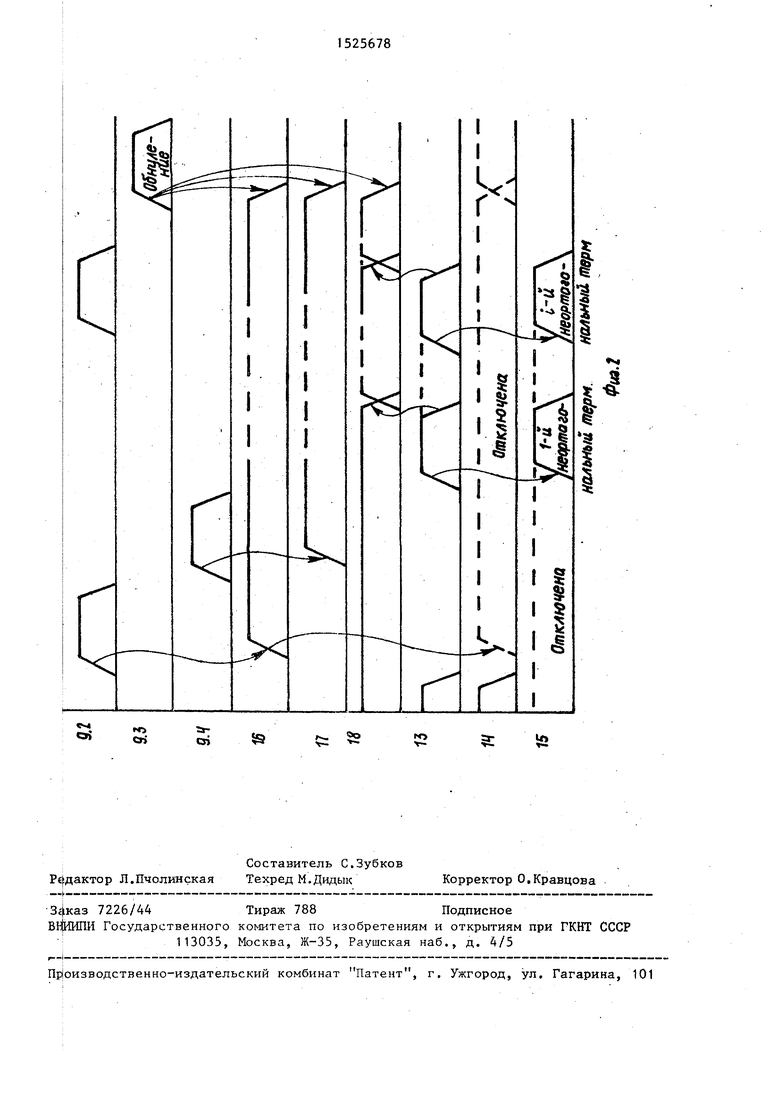

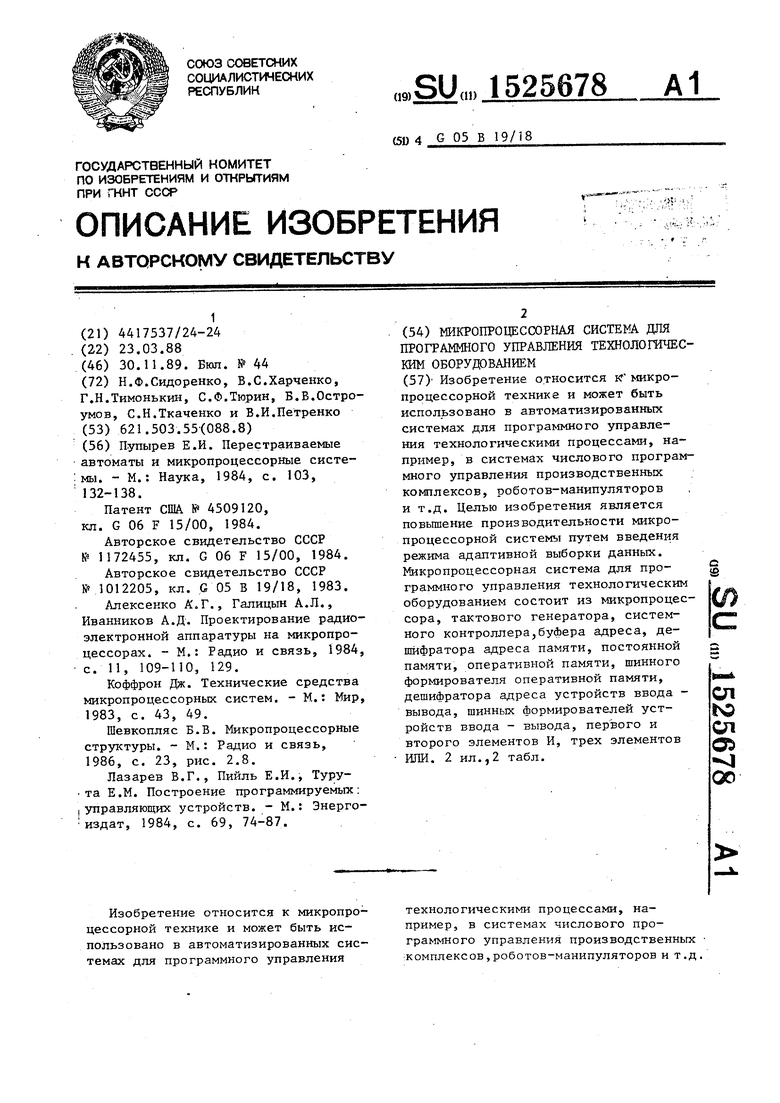

На фиг. 1 изображена функциональная схема микропроцессорной системы; на фиг. 2 - временная диаграм)у1а pci6o ты микропроцессорной системы в режиме адаптивной выборки данных,

Микропроцессорная система для программного управления технологическим оборудованием содержит ш кропроцес- сор 1 с адресными выходами 1 И, входами-выходами 1,2 данных, выхода ж 1«3 управления а тактовым входагчи 1.4 и 1,5 первой и второй фаз входо 1.6 сброса, входом 1,7 готовностк и выходом 1.8 синхронизации5 тактовьш генератор 2 . с входами 2,1 и 2,2 подключения кварцевого резонатора, входом 2,3 синхронизации, тактовыми выходами 2,4 и 2,5 первой и второй фаз, выходом 2 об сброса выходом 2„7 готовности и выходом 2„8 синхро- низации, системный контроллер 3 с выходами-входами 3,3 данныхj являющимися шиной данных микропроцессорной системы и выходами 3,2 управления; являгощи1 ШСя шиной управления: микропроцессорной систег-м, буфер 4 а цреса с выходами 4, 1 s являющимися нвшой адргса микропроцессорной сие™ тег-Ыд дешифратор 5 адреса памяти с выходом 5.1 подключения постоянной памяти и выходом 5,2 подключения оперативной паг-етти, постоянн то память б, оперативную память 7,, шиыньш формирователь 8 оперативной памяти, дешифратор 9 адреса устройств вводавывода с вькодами 9.1 подк.шочения усройств ввода-вывода и вьпсодг ш 9 -. 2- 9,4s шинный формирователь 10 устройств ввода-вывода5 первьй 11 и второй 12 элементы ИЛИ, дешифратор

13постоянной памяти данных,,, первую

14и вторую 15 постоянную память данныхg первьй 16 и второй 17 триггеры, счетчик 18, регистр 19s первый

20 и второй 21 элементы И 5, третий эле- мент ИЛИ 22; вход 23, являющейся входом сброса микропроцессорно системы, вход 24, являющийся входом готовности шкропроцессорной системь 5 вход 25, являющийся входом захвата микропроцессорной системы, вход 26, являющийся входом запроса прерывания /микропроцессорной системы,, выход 27 являющийся выходом ожидания м кро11роессорной системы, ВЬЕКОД 28, являю- ;ийся выходом разрешения прерывания 1икропроцессорной системьц входы 9, являющиеся информационными вхоами микропроцессорной системы, и ыходы 30, являющиеся информационны- м вь хода-ми микропроцессорной сисемы,

Первьй 2.1 и второй 2.2 входы тактового генератора подключены к кварцевому резонатору. Пятьш вход 2,3 тактового генератора 2 подключен к выходу синхронизации 1,8 микропроцессора 1. Первьй 2.4 и второй 2.5 выходы тактового генератора 2 под- к,гючены к первому 1„4 и второму 1,5 тактовым входам гжцсропроцессора 1 соответственно„ Третий 2„6 и четвертый 2.7 выходы тактового генератора , 2 подюш чень к входам сброса 1 ,6 и готовностк 1.7 кропроцессора 1 со- ответственно Пятый выход 2,8 тактового генератора 2 подключен к входу синхронизации системв:ого контроллера 3, Адресные выходь 1,, f iKponDO- цессора подк.тпсчень к кнформацион- кьы входам буфера 4 адресги Входы- выходы , 2 данных. Шакропроцессора 1 подключены к входам-ЕТэГгсодам данных системного KOHTpojixiepa Зо Выходы уп- равлеыия 1„3 г-шкропроцессора 1 под ключены к входам управления системного контроллера 3„ Первьй и второй входы разрешения буфера 4 ,адр9са подкл(очень к разряду шины З 2 управления ьшкропроцессорной системы Под- тяерж,Етение захвата, Икформациошше входы дешифраторов 5 и 9 адреса памяти .I адреса устройств ввода-вывода подключены к шине 4 с 1 адреса ропроцессорной системьь Вход разрешения дешифратора 5 а.дреса памяти подгслзочен к выходу первого элемента RTffi nepBbtti и второй входы которого подключены к разрядам ЕШНЫ 3,2 У71равления микропроцессорной систе2 Ы Чтение памяти, Запксь в память, соответственно Первьй выход дешифратора 5 адреса naiviHTi i подключен к nepjBOMy входу разрешения постоянной па,У1яти 6. Второй выход 5.2 дешифратора 5 адреса памяти подвлючен к входу разрешения оперативной 7 и к первому входу разрешения шинного формирователя В оперативной памяти. Второй вход разрешения иост янной памяти 6 подключен к разрйду

выходов 1.3 управления микропроцессора 1 Прием, та1сже подключенному к второму входу разрешения шинного формирователя 8 оперативной памяти. Вход записи оперативной памяти 7 подключен к разряду шины 3.2 управления микропроцессорной системы Запись в память. Адресные входы постоянной 6 и оперативной 7 памяти подключены к шине 4.1 адреса микропроцессорной системы. Информационные выходы постоянной памяти 6, входы-выходы шинных формирователей 8 и 10 оперативной памяти устройств ввода-вывода подключены к шине данных 3,1 микропроцессорной системы. Выходы .шинного формирователя 8 оперативной памяти подключены к входам данных оперативной памяти 7, выходы данных которой подключены к входам шинного формирователя 8 памяти. Вход разрешения дешифратора 9 адреса устройств ввода-вывода подключен к выходу второго элемента ИЛИ 12, первый и второй входы которого подключены к разрядам шины 3.2 управления микропроцессорной системы Ввод из устройства ввода, Вывод в устройство вывода соответственно. Группа информационных выходов 9.1 дешифратора адреса устройств ввода-вывода 9 подключена к первым входам разрешения соответствующих шинных формирователей 10 устройств ввода-вывода, вторые входы разрешения которых подключены к разряду шины 3.2 управления микропроцессорной системы Ввод из устройства ввода. Выходы шинных формирователей 10 ввода-вывода являются и информационными выходами 30 микропроцессорной системы, а их входы являются информационными входами 29 микропроцессорной системы. Информационные входы дешифратора 13 постоянной памяти данных подключены к шине 4.1 адреса микропроцессорной системы, а его вход разрешения подключен к разряду шины 3.2 управления микропроцессорной системы Чтение памяти. Выход дешифратора 13 постоянной памяти данных подключен к первым входам первого 20 и второго 21 элементов И. Второй выход 9.2 дешифратора адреса устройств ввода-вывода подключен к входу установки первого триггера 16. Третий выход 9.3 дешифратора адреса устройств ввода-вывода подключен к.первоьгу входу третьего элемента ИЛИ 22, второй вход которого подключен к третье г - выходу 2.6 тактового генератора 2. Четвертый 9.4 выход дешифратора адреса памяти 9 подключен к входу установки второго триггера 17. Выход третьего элемента ИЛИ 22 подключен к входам сброса первого 16 и второго 17-триггеров, счетчика 18 и регистра 19. Выход первого триггера 16 подключен к вторым входам первого 20 и второго 21 элементов И. Выход второго -триггера 17 подключен ко входу синхронизации регистра 19,

Выход первого элемента И 20 подключен к первому входу разрешения первой постоянной памяти 14 данных, второй вход разрешения которой .подключен к разряду шины 3.2 управления микропроцессорной системы Чтение памяти, подключенному также к второму входу разрешения второй постоянной памяти 15 данных. Выход второго элемента И 21 подключен к первому входу

разрешения второй постоянной памяти 15 данных, а также к сч 1гтному входу счетчика 18. Выходы счетчика 18 подключены к первой части адресных входов второй постоянной памяти I5 данных, к второй части которых подключены выходы регистра 9. Выходы первой 14 и второй 15 постоянной памяти данных, а также входы регистра 19 подключены к шине данных 3.1 микропроцессорной системы. Адресные входы первой постоянной памяти 14 данных подключены к шине адреса 4.1 микропроцессорной системы.

Микропроцессорная система для прогpaм iнoгo управления технологическим оборудованием работает следующим образом.

Обычньш режим работы.

В этом режиме тактовьй генератор

2 (фиг. 1) форьшрует две неперекрывающиеся тактовые последовательности, которые с его выходов 2.4 и 2.5 поступают на тактовые входы первой 1.4 и второй 1,5 фаз микропроцессора 1,

Стабильность тактовой частоты обеспечивается кварцевым резонатором, подключенным к входам 2.1 и 2.2 тактового генератора 2.

Микропроцессор 1 генерирует сигналы адреса, данных и управления после подачи сигнала сброса на соответствующий его вход 1.6, причем внешний сигнал сброса с входа 23 микропроцессорной систеьп 1 стробируется в

актовом генераторе 2 и поступает на его выкод 2,6, после установления уровня 1 на входе 24 готовности микропроцессорной системы, причем сигнал готовности стробируется в тактовом генераторе 2 и с его выхода

2.7поступает на вход 1„7 готовности микропроцессора 1, Если же на входе 24 микропроцессорной системы установлен сигнал О, то на выходе 27 микропроцессорной системы устанавливается сигнал 1, свидетельствующий

о том, что микропроцессор 1 находится в режиме ожидания готовности.

Микропроцессор 1 выдает слово сос тояния на шину 1 „ 2 данных, по синхросигналу на соответствующем выходе 1.8, поступающему на вход 2,3 тактового генератора 2 в первом такте каждого машинного цикла, а стробиро- ванный по первой фазе сигнал синхронизации (системный строб) с выхода

2.8тактового генератора 2 поступает на вход синхронизации системного

контроллера 3, в который записывается слово состояния микропроцессора с входов выходов 1.2 данных ь/шкро- процессора 1 „ Системкьй :контро.п:аер 3 по слову состояния и сигналам на выходах 1,3 управления микропроцессора 1 формирует шину управления 3,2 микропроцессорной системь,, а также шинз данных 3, 1 микропроцессорной сие- темы, обеспечивая ее требуем 5гю нагру- зочную способность и двунаправлен- ность передачи данных на входах-выходах 1.2 данных ми.кропроцессора 1,

Буфер 4 адреса формирует по адресным сигналам на соответствующих выходах 1,1 микропроцессора 1 шину 4.1 адреса микропроцессорной систег Шд обеспечивая ее. требуемую нагрузочную способность„

Микропроцессорную систему можно перевести в режим прерывания и захвата подачей соответствующих сигналов на входы 25 и 26. При переходе в ре-жим прерывания с выхода 28 снимается сигнал разрешения прерывания„ При переходе микропроцессорной систег Ы в режим захвата на соответствующем разряде выходов 1 .3 управления микропро-- цессора 1 так же, как и на шине 3,2 управления микропроцессорной системы, устанавливается сигнал подтвер5кдения захвата, который по первому и второму входам управления переводит выходы: буфера адреса 4 в высокоимпедансное

состояние. По этому сигналу выходы ciicTeNffloro контроллера 3, выходы 1,1 адреса, входы-выходы 1.2 данных микропроцессора 1 переводятся в высоко- импедансное состояние. РежШ Ы захва- va и прерывания в предлагаемой микропроцессорной системе не используются.

Микропроцессор 1 считывает и выпел- няет программу, записанную в постоянной памяти 6 либо в оперативной памяти 7. При этом дешифратор 5 адреса памяти дешифрирует адрес, выставленный на шине 4,1 адреса микропроцессорной системы, если на шине 3.2 управления выставлен один из сигналов Чтение , Запись в память, при этом активизируется выход первого элемента ИЛИ 11 и вход управления дешифратора 5, Если на шине 4.1 адреса микропроцессорной системы выставлен адрес постоянной памяти 6, то активизируется выход 5.1 дешифратора 5 и первьш вход управления постоянной па- 6,

Если на шине адреса 4,1 микропроцессорной системы выставлен адрес оперативной памяти 7 то активизиру- гтся выход 5о2 дешифратора З,, вход управления оперативной памяти 7 и

первый вход управления пшнного формирователя 8 оперативной памяти.

Выходы постоянной памяти б подключаются к шине данных 1Ф Кропроцес - сорной систетф, если активизирован jкрона первого входа управления, второй вход управления сигналом При™ ем с соответствующего разряда выхо- . дов 1,3 управления микропроцессора 1, Данные считываются из ячеек постоянной памяти б в микропроцессор 1 по шине 3„2 данных г-шкропроцессорной системы через входы-выхо.ды данных системного контроллера на входы-выхо- ды К 2 данных Г шкропроцессора 1 в

соответствии с адресами, поступающим на адресные входы с шины 4.1 адреса микропроцессорной системы.

Для считывания данных из оператив- ной памяти 7, кроме активизирования ее входа управления, на ее вход записи подается сигнал О с соответствующего разряда шины 3,2 управления микропроцессорной системы Запись Б память, а второй вход управления шинного формирователя 8 оперативной памяти активизируется разрядом выходов 1.3 управления микропроцессору 1 Прием. Это переводит шинный формк -

рователь .8 памяти в режим приема, т.е. организуется передача данных с выходов оперативной памяти 7 на шину 3.1 данных микропроцессорной системы. Данные считываются из ячеек оперативной памяти 7 в микропроцессор 1 по шине 3,1 данных микропроцессорной системы в соответствии с адресами, , поступаклцими на ее адресные входы с шины 4.1 ад.реса микропроцессорной системы.

teiKponpoueccop 1 может записывать данные в оперативную память 7, при зтом шинньй формирователь 8 оператив ной памяти по второму входу управления, с которого снимается активный- уровень сигнала соответствующим разрядом выходов 1.3 управления микропроцессора 1, переводится в режим ввода данных с шины 3.1 данных микропроцессорной системы.

Оперативная память 7 по входу записи, которьй активизируется соответствующим разрядом Запись в память гаины 3.2 управления микропроцессорной системы, переводится в режим записи. Данные с шины данных 3.1 микропроцессорной системы записываются в ячейки оперативной памяти 7 в соот- ветствии с адресными сигналами, поступающими на адресные входы с шины 4.1 адреса микропроцессорной системы При отсутствии активных уровней управляющих сигналов выходы постоянной памяти 6 и выхЬды-входы шинного формирователя 8 оперативной памяти находятся в высокоиютедансном состоянии и отключены от шины 3.1 данных микропроцессорной системы.

Микропроцессорная система вводит данные со своих информационных входов 29 или выводит данные на свои информационные выходы 30. Дешифратор 9 адреса устройств ввода-вывода де- шифрирует адрес,, выставленный на шине 4.1 адреса микропроцессорной системы, если активизирован его вход управления выходом второго элемента ИЛИ 12 при активизировании его входов од шм из сигналов Ввод из устройства ввода, Вывод в устройство вывода на соответствующих разрядах шины 3.2 управления микропроцессорной системы.Выходы дешифратора 9 адреса управления ввода-вывода активизируют второй вход разрешения одного из шинных формирователей ввода-вывода, соответствующего адресу, пocтyпaюI e y на а,а,ресные входы деишуратора 9 адреса устройств ввода-вывода.

Режим работы (ввод или вывод) шин .ных формирователей устройства ввода- вывода определяется сигналом на вторых входах разрешения, т.е. соответ- ств пощим разрядом Ввод из. устройства ввода шины 32 управления микропроцессорной ст стемы. В режиме ввода данные с информационных входов 29 микропроцессорной системы поступают на входы соответствующего шинного формирователя устройства ввода-вывод а с его входов-вьжодов на шину 3.1 данных микропроцессоров системы через системньй контроллер 3 в шкро- процессор I по его входам-выходам данных,

В режиме вывода данные из MiKpo- процессора 1 по входам-вьтходам 1.2 данных, через системньш контроллер 3, по шкне 3,1 данных микропроцессорной системы поступают на входы-выходы соответствующего шинного формирователя устройства ввода-вывода, а с его выходов - на информационные входы микропроцессорной системы.

При OTcyTCTBiiH активных уровней сигналов управления шинные формирователи устройства ввода-вывода отключены от шины данных (находятся в высо- коимпедансном состоянии).

Микропроцессорная система реализует алгоритм моделирования программируемой логической матрицы, являю- ищйся стандартным для вычисления систем булевых функций, описывающих закон управления технологическим оборудованием. Такой алгоритм оформлен в виде процедуры PLA на языке высокого уровня для микропроцессоров PL/M. При этом входной вектор состояния технологического оборудования вводится с порта (портов) ввода, а выходной вектор управляющих сигналов выводится на порт (порты) вывода аналогично , описанному.

Обработка конъюнктивных термов

системы булевых функщш заключается в вычислении значений каждого -терма независимо от их значений на различных наборах входных векторов.

Режим реализац; и адаптивной выборки данных.

В этом режиме микропроцессорная система работает аналогично обычному ражиму, выполняя программу моделиро;вания программируемой логической |Матрицы. Обнаружив, что конъюнктив- |ньй терм системы булевых функций, |которые описывают закон управления технологическим оборудованием, равен 11, микропроцессор 1 выполняет команду вывода по адресу триггера 16. При этом выводимая информация, т.е. содержимое аккумулятора, не имеет зна- чения, важен факт возбуждения выхода 9.2 -дешифратора 9 адреса устройств ввода-вывода. Поэтому устанавливается триггер 17, обнуленный в начале работ системным сбросом. На выходе тригге- ра 16 (инверсном) устанавливается напряжение О, поэтому по второму входу элемент И 20 блокируется, а элемент И 21 подготавливается к работе. Далее микропроцессор 1 выводит по адресу триггера 17 адрес следующего конъюнктивного терма. При этом активизируется выход 9.4 дешифратора 9 адреса устройств ввода-вывода и устанавливается второй триггер 17, обну- ленный в начале работы системным сбросом с выхода третьего элемента ИЛИ 22. Вследствие этого в регистр 19 по информационным входам с шины 3 Л . данных микропроцессорной системы пе- редним фронтом сигнала на выходе второго триггера 17 записывается ад- i pec следующего конъюнктивного тер- I ма„

I Так как установлен первый, триг- гер 16 И блокирован по второму входу элемент И 20, то постоянная память I 14 отключается от шины данных, т.е. I ее выходы переводятся в высокоимпе-- i дансное состояние. Далее Микропроцес- : сорная система продолжает реализовать программу моделирования программируемой логической матрицы, которая за исключением команд вывода по адресу триггера 16 и вывода адреса следу- ющего конъюнктивного терма по адресу регистра 19 и сброса в том случае, если очередной вычисленный конъюнктив ньш терм равен 1, соответствует стандартной. Микропроцессор выставляет на шине 4.1 адрес очередной ячейки памяти данных, т.е. очередного конъюнктивного терма, при этом активизируется выход дешифратора 13 постоянной памяти данных. Однако, так как установлен триггер 16, не активизируется первый вход разрешения первой постоянной па- , мяти 14 данных, а активизируется пер- вый вход разрешения второй постоянной

памяти 15 данных, второй вход разрешения которой активизируется соответствующим сигналом Чтение памяти шины управления. Во второй постоянной памяти 15 данных по адресу, установленному на выходах счетчика 18 и регистра 19jзаписаны данные о конъюнктивных термах, не ортогональных вычисленному. Изменение состояния счетчика 18 происходит по заднему фронту сигнала на выходе дешифратора 13. Следовательно, после обнаружения единичного конъюнктивного терма выборка данных осуществляется из второй постоянной памяти 15 данньгх по адресам формируемым счетчиком 18 со смещением, обеспечиваемым регистром 19. В этом случае микропроцессорная система обрабатывает подмножество данных меньшей мощности, а именно подмножество конъюнктивных термов, неортогональных вычисленному первому единичному. При обнаружении в этом подмножестве нового единичного терма микропроцессорная система обрабатьшает то же подмножество данньгх, так как пер- вьй 16 и второй 17 триггеры уже установлены и очередные команды вывода по их адресам не изменяют, их состояния .

Обработка данных заканчивается при обнаружении маркера окончания вычислений, который завершает каждое и подмножеств данных, записанных во второй постоянной памяти 15. Обнуление первого 16 и второго 17 триггеров, регистра 19 и счетчика 18 обес- печивается командой вывода при возбуждении выхода 9.3 дешифратора 9 адреса устройств ввода-вывода.

В том случае, если ни один из конъюнктивных термов не равен 1, .м микропроцессорная система продолжает обрабатывать данные, расположенные в первой постоянной памяти 14 данных до обнаружения маркера окончания вычислений, который завершает полньй массив данных.

Таким образом, сокращается средне время обработки массива данных, кодирующего конъюнктивные термы системы булевых функций, описывающей зако управления технологическим оборудованием, на потоке входных векторов состояния технологического оборудования

Рассмотрим пример конкретной реализации ьгакропроцессорной системы для программного управления технологическим оборудованием, реализующей закон управления, который описывается следующей системой булевых функций:

,х„ухзХ2, ;5

Zi X3X,vx3X2 /X3X2X,vx,,XoVXjX.,x,Xo;

jZ,, 4i3X2VX3X,,VX3X.jX,X,VX3Xo; J X XiXoV/X XjVXjXoVXjX-jX X..

Вьтишем неповторяющиеся конъюнк- g тинные термы:

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорная система для программного управления технологическими процессами | 1987 |

|

SU1418653A1 |

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Устройство для сопряжения абонента с магистралью в микропроцессорной системе | 1987 |

|

SU1538173A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1751772A1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1476434A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1608679A1 |

Изобретение относится к микропроцессорной технике и может быть использовано в автоматизированных системах для программного управления технологическими процессами, например, в системах числового программного управления производственных комплексов, роботов-манипуляторов и т.д. Целью изобретения является повышение производительности микропроцессорной системы путем введения режима адаптивной выборки данных. Микропроцессорная система для программного управления технологическим оборудованием состоит из микропроцессора, тактового генератора, системного контроллера буфера адреса, дешифратора адреса памяти, постоянной памяти, оперативной памяти, шинного формирователя оперативной памяти, дешифратора адреса устройств ввода/вывода, шинных формирователей устройств ввода/вывода, первого и второго элементов И, трех элементов ИЛИ. 2 ил.

, XjX,

XjX

XjX,jX,

XjX,

,

XiX,

; Присвоим им порядковые номера 1-11 и составим матрицу неортого- напьности с учетом порядкового номера, т.е. учитывается неортогональность по отношению только к последующим по номеру термам:

23456789 1011 11 1

21

3II 1

4 Г

61

81 9

10 1

Матрица неортлгональнбсти покаэы- .вает, какие конъюнктивные термы необходимо вычислять, если терм, номер которого соответствует номеру строки, равен 1. Остальные терМы не подлежат вычислению, так как они ортогональны данному терму и, соответственно, равны О.

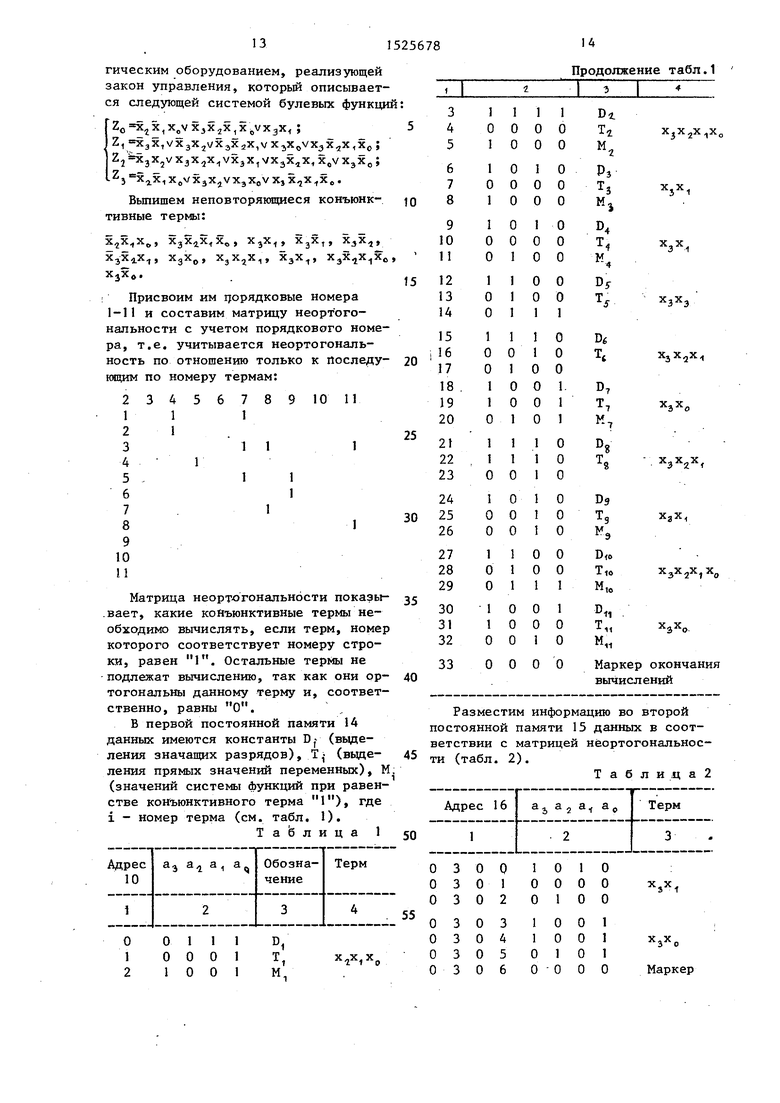

В первой постоянной памяти 14 данных имеются константы D (вьще- ления значащих разрядов). Т,- (вьще- ления прямых значений переменных), М (значений системы функций при равенстве конъюнктивного терма 1), где i - номер терма (см. табл. 1).

Т а Ь л и ц а 1

1001

М.

15

20

25

30

35

40

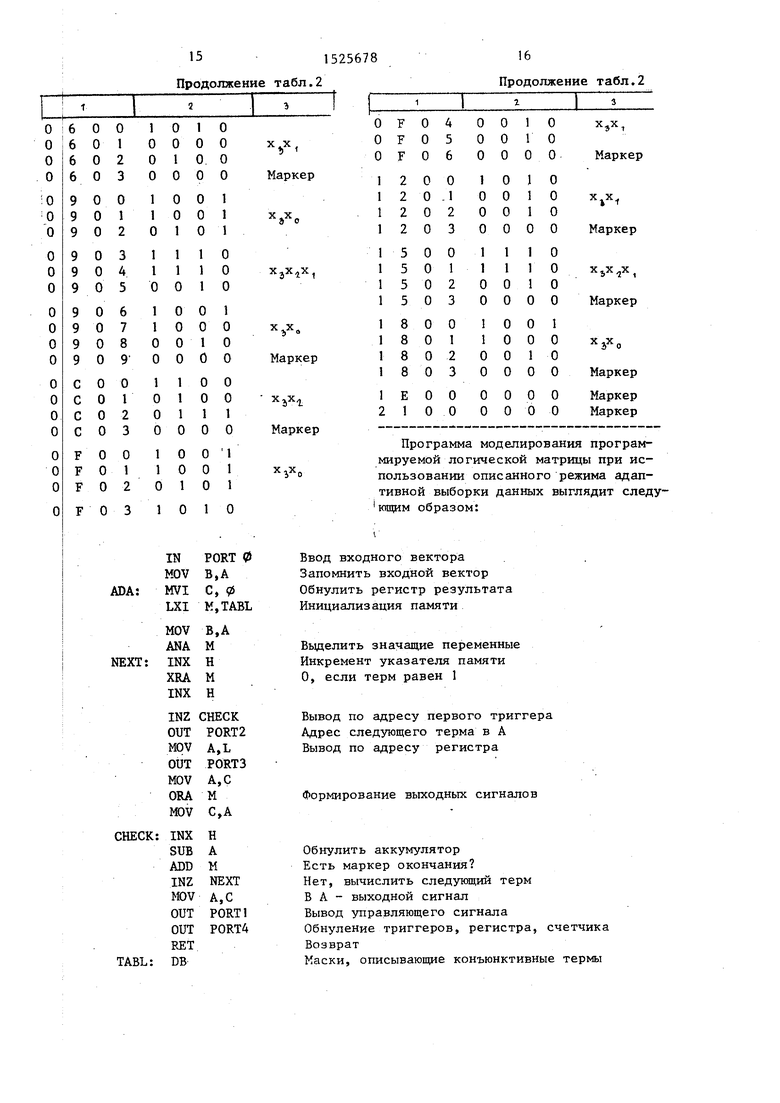

Разместим информацию во второй постоянной памяти 15 данных в соответствии с матрицей нёортогональнос- ти (табл. 2).

Таблица2

50

Маркер

15

1525678

Продолже ние т абл.2

INPORT 0

MOVВ,А

ADA: MVIС, 0

LXIM.TABL

MOVВ,A

ANAM

NEXT: INXH

XRAM

INXH

INZ CHECK

OUTPORT2

MOVA,L

OUTPORT3

MOVA, С

ORAM

MOVC,A

CHECK: INXH

SUBA

ADDM

INZNEXT

MOVA,С

OUTPORT 1

OUTPORT4 RET

TABL: DB

Ввод входного вектора Запомнить входной вектор Обнулить регистр результата Инициализация памяти

Выделить значащие переменные Инкремент указателя памяти О, если терм равен 1

Вывод по адресу первого триггера Адрес следующего терма в А Вывод по адресу регистра

Формирование выходных сигналов

Обнулить аккумулятор

Есть маркер окончания

Нет, вычислить следунндий терм

В А - выходной сигнал

Вывод управляющего сигнала

Обнуление триггеров, регистра, счетчика

Возврат

Маски, описывающие конъюнктивные термы

Продолжение табл.2

Следовательно, за исключением че- тьфех команд OUTPORT 2, MOVA, L, OUT PORT 3,4 программа соответствует известной..

Таким образом, микропроцессорная система обеспечивает сокращение временных затрат на вычисление закона управления технологическим оборудованием, заданным системой булевых функций,более чем в 1,6 раза.

Формула изобретения

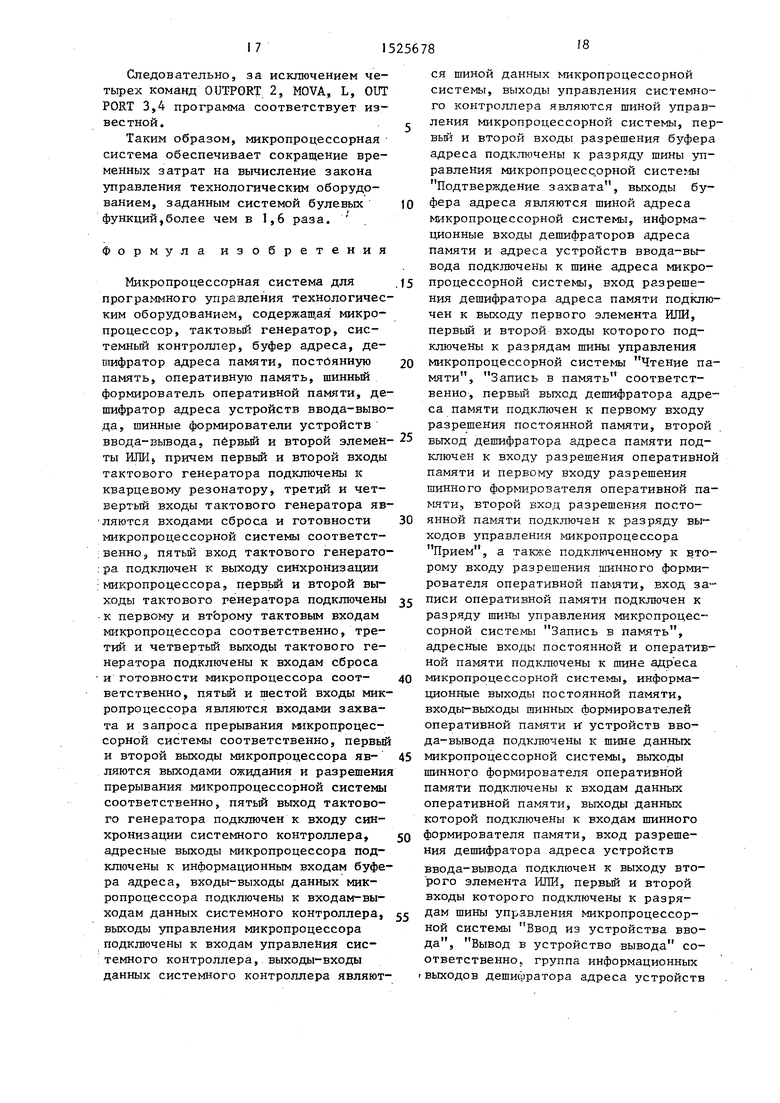

Микропроцессорная система для программного управления технологическим оборудованием, содержащая микропроцессор, тактовый генератор, системный контроллер, буфер адреса, дешифратор адреса памяти, постбянизгю память, оперативную память, шинный формирователь оперативной памяти, де- пшфратор адреса устройств ввода-вывода, шинные формирователи устройств ввода-вывода5 пёрвьй и второй элемен- ты ИЛИ5 причем пёрвьй и второй входы тактового генератора подключены к кварцевому резонатору, третий и четвертый входы тактового генератора яв- ляются входами сброса и готовности микропроцессорной системы соответст- ;Венно5 пятьй вход тактового генерато- :ра подключен к выходу синхронизации :микропроцессора, пёрвьй и второй выходы тактового генератора подключены

к первому и втЬрому тактовым входам микропроцессора соответственно, третий и четвертьй выходы тактового генератора подключены к входам сброса

и готовности микропроцессора соот- ветственно, пятьй и шестой входы микропроцессора являются входами захвата и запроса прерывания микропроцессорной системы соответственно, пёрвьй

и второй выходы микропроцессора яв- ляются выходами ожидания и разрешения прерывания микропроцессорной системы соответственно, пятьй выход тактового генератора подключен к входу синхронизации системного контроллера, адресные выходы микропроцессора подключены к информационным входам буфера адреса, входы-выходы данных микропроцессора подключены к входам-выходам данных системного контроллера, выходы управления микропроцессора подключены к входам управления сис- :темного контроллера, выходы-входы данных системного контроллера являются шиной данных микропроцессорной системы, выходы управления системного контроллера являются шиной управления микропроцессорной системы, пер вьй и второй входы разрешения буфера адреса подключены к разряду шины управления микропроцессорной системы Подтверждение захвата, выходы буфера адреса являются шиной адреса микропроцессорной системы, информационные входы дешифраторов адреса памяти и адреса устройств ввода-вывода подключены к шине адреса микропроцессорной системы, вход разрешения дешифратора адреса памяти подключен к выходу первого элемента ИЛИ, пёрвьй и второй входы которого подключены к разрядам шины управления микропроцессорной системы Чтение памяти, Запись в память соответственно, первьш выход дешифратора адреса памяти подключен к первому входу разрешения постоянной памяти, второй выход депшфратора адреса памяти подключен к входу разрешения оперативно памяти и первому входу разрешения шинного формирователя оперативной па мчти, второй вход разрешения постоянной памяти подключен к разряду вы ходов управления микропроцессора Прием, а также подключенному к второму входу разрешения шинного формирователя оперативной памяти, вход записи оперативной памяти подключен к разряду шины управления микропроцессорной системы Запись в память, адресные входы постоянной и оперативной памяти подключены к шине адреса микропроцессорной системы, информа- ционцые выходы постоянной памяти, входы-выходы шинных формирователей оперативной памяти и устройств ввода-вывода подключены к шине данных микропроцессорной системы, выходы Ш1шного формирователя оперативной памяти подключены к входам данных оперативной памяти, выходы данных которой подключены к входам шинного формирователя памяти, вход разрешения дешифратора адреса устройств ввода-вывода подключен к выходу второго элемента ШШ, пёрвьй и второй входы которого подключены к разрядам шины управления микропроцессорной системы Ввод из устройства ввода, Вывод в устройство вывода соответственно группа информационных выходов дешифратора адреса устройств

(ввода-вывода подключена к первым ходам разрешения соответствующих (пинных формирователей ввода-вывода, вторые входы разрешения подключены к разряду шины управления микропроцессорной системы Ввод из устройства ввода, выходы шинных формирователей ввода-вывода являются информационными выходами микропроцессорной систем а их входы являются информационными входами микропроцессорной системы, этличающая ся тем, что, с целью повышения производительности микропроцессорной системы, допол- нительно содержит дешифратор постоянной памяти данных, первую и вторую постоянные памяти данных, первый и второй триггеры, счетчик, регистр, первьй и второй элементы И и третий элемент ИЛИ, причем информационные входы дешифратора постоянной памяти цанных и дешифратора адреса устройст ввода-вывода подключены к шине адреа микропроцессорной системы, вход разрешения дешифратора постоянной памяти данных соединен с разрядом Чтение памяти шины управления,вы- рсод дешифратора постоянной памяти ранных подключен к первым входам пер вого и второго элементов И, второй выход дешифратора адреса устройств ввода-вывода подключен к входу установки первого триггера, третий выход дешифратора адреса устройств ввода

|ВЫвода подключен к первому входу тре

5 0

5

тьего элемента ИЛИ, второй вход которого подключен к третьему выходу тактового генератора, четвертьй выход дешифратора адреса памяти подключен к входу установки второго триггера, выход третьего элемента ИЛИ подключен к входам сброса первого и второго триггеров, счетчика и регистра, выход первого триггера подключен к вторым входам первого и второго элементов И, выход .второго триггера подключен к входу синхронизации регистра, выход первого элемента И подключен к первому входу разрешения первой постоянной памяти данных, второй вход разрешения которой подключен к разряду шины управления микропроцессорной системы Чтение памяти, подключенному также к второму входу разрешения второй постоянной памяти данных, выход второго элемента И подключен к пе рвому входу разрешения второй постоянной памяти данных, а также к счетному входу счетчика, выходы счетчика подключены к первой группе адресных входов второй постоянной памяти данных, к второй группе которых подключены выходы регистра, выходы первой и второй постоянной памяти данных, а также входы регистра подключены к шине данных микропроцессорной системы, а адресные входы пер- 1ВОЙ постоянной памяти данных подключе- ны к шине адреса микропроцессорной системы.

NTS

crt

СП

SS

«о

ю

Ui

| Пупырев Е.И | |||

| Перестраиваемые автоматы и микропроцессорные системы | |||

| - М.: Наука, 1984, с | |||

| Клапанный регулятор для паровозов | 1919 |

|

SU103A1 |

| Патент США № 4509120, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропроцессорная система | 1981 |

|

SU1172455A3 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство программного управления | 1981 |

|

SU1012205A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Алексенко А.Г., Галицын А.Л., Иванников А.Д | |||

| Проектирование радиоэлектронной аппаратуры на микропроцессорах | |||

| - М.: Радио и связь, 1984, с | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Коффрон Дж | |||

| Технические средства микропроцессорных систем | |||

| - М.: Мир, 1983, с | |||

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

| Шевкопляс Б.В | |||

| Микропроцессорные структуры | |||

| - М.: Радио и связь, 1986, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Лазарев В.Г., Пийль Е.И., Туру- та Е.М | |||

| Построение программируемых: управляющих устройств | |||

| - М.: Энерго- издат, 1984, с | |||

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

Авторы

Даты

1989-11-30—Публикация

1988-03-23—Подача