Изобретение относится к вычислительной технике, в частности к устройствам сопряжения, и может быть использовано для настройки плат при помощи IBM PC электронных устройств, имеющих интерфейс Q-шину.

Известно, что ЭВМ класса "Электроника 60М" имеет Q-шину. Известно также, что Q-шина является одной из основных шин при передаче, приеме и обработке информации в авиаприборостроении. Особенностью Q-шины является мультиплексирование информационной шины, по которой в различные моменты времени пересылаются адреса и данные. Недостатком Q-шины является отсутствие современной вычислительной техники, работающей на Q-шине.

Наиболее близким по техническому решению к предлагаемому является интерфейсная часть (ИЧ) адаптера шины ISA, содержащая 10-разрядный дешифратор адреса порта, 16-разрядный регистр записи данных с шины ISA и 16-разрядный регистр чтения данных с шины ISA [3]. Целью изобретения является повышение надежности Q-шины за счет эффективной работы PC IBM. Протокол обмена по шине ISA был взят из [2], [3], [4], а по Q-шине - из [1].

Поставленная цель достигается тем, что в интерфейсную часть (ИЧ) адаптера шины ISA, содержащую 10-разрядный дешифратор адреса порта, 16-разрядный регистр записи данных с шины ISA и 16-разрядный регистр чтения данных с шины ISA, дополнительно введены: первый логический элемент И, формирователь адреса Q-шины, состоящий из 16-разрядного шинного формирователя, и формирователь сигналов управления Q-шины, содержащий первый, второй, третий и четвертый триггеры, два резистора, первую, вторую, третью, четвертую и пятую линии задержки, второй и третий лог. элементы И.

Первый выход с дешифратора адреса порта соединен с входом управления регистра записи данных с шины ISA, второй, третий и четвертый выходы с дешифратора адреса порта поступают в формирователь сигналов управления Q-шины, причем третий, четвертый выходы поступают на вход первого логического элемента И, выход с которого поступает на вход 16-разрядного формирователя адреса Q-шины. Два выхода с формирователя сигналов управления Q-шины поступают в регистр записи данных с шины ISA и регистр чтения данных с шины ISA, и четыре выхода соединены с Q-шиной, причем один сигнал поступает с Q-шины в формирователь сигналов управления Q-шины.

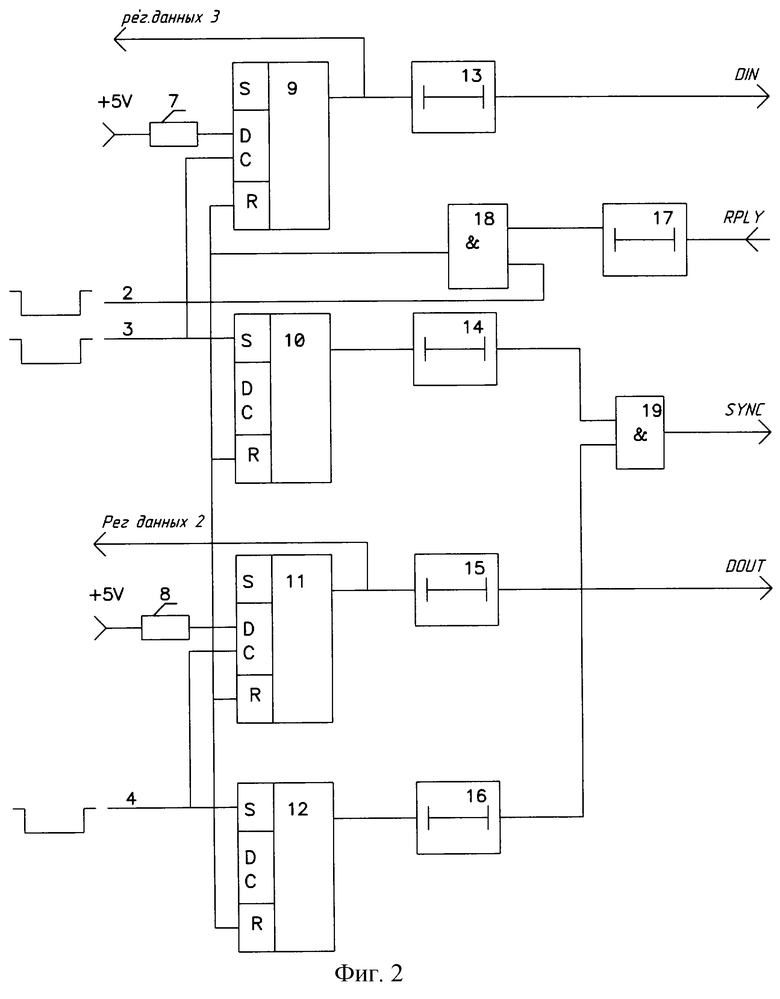

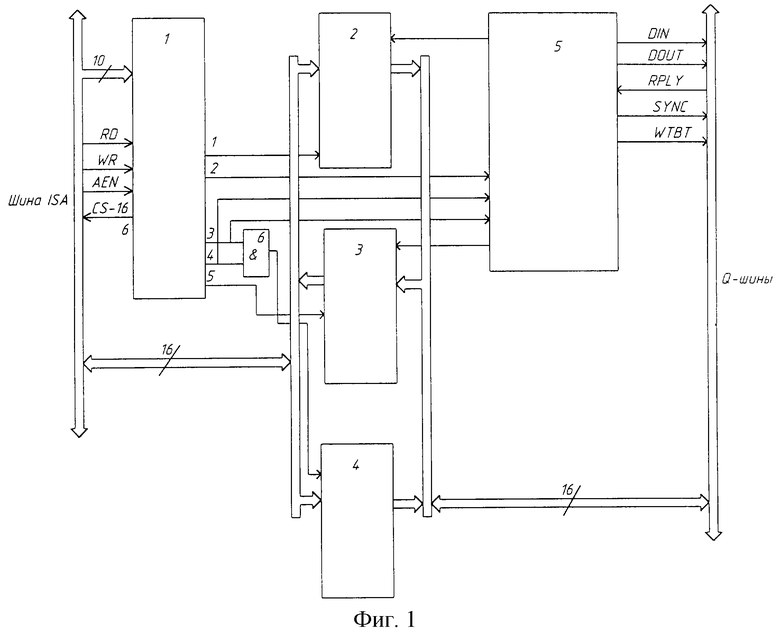

На фиг.1 представлена функциональная схема адаптера шины ISA с Q-шиной, на фиг.2 - схема формирователя сигналов управления Q-шины.

Адаптер шины ISA с Q-шиной содержит 10-разрядный дешифратор адреса порта 1, регистр записи данных с шины ISA-2, регистр чтения данных с шины ISA 3, формирователь адреса Q-шины 4, логический элемент И 6 и формирователь сигналов управления Q-шины 5, содержащий триггеры 9, 10, 11, 12, линии задержки 13, 14, 15, 16, 17, два логических элемента И 18, 19 и два резистора 7, 8. В дешифратор адреса порта 1 с шины ISA поступает 10-разрядный адрес, три сигнала управления, причем шестой выход с дешифратора адреса порта 1 поступает на шину ISA, второй, третий и четвертый выходы с дешифратора адреса порта 1 поступают на вход формирователя сигналов управления Q-шины 3, причем третий и четвертый выходы с дешифратора адреса порта 1 поступают на вход первого логического элемента И 6, выход с которого поступает на управляющий вход формирователя адреса Q-шины 4, первый выход с дешифратора адреса порта 1 поступает на вход регистра записи данных с шины ISA 2, пятый выход поступает на вход регистра чтения данных с шины ISA 3.

16-разрядные входы регистра записи данных с шины ISA 2, формирователя адреса Q-шины 4 и выходы регистра чтения данных с шины ISA 3 объединены и соединены с шиной ISA (данные). 16-разрядные выходы регистра записи данных с шины ISA 2, формирователя адреса Q-шины 4 и входа регистра чтения данных с шины ISA 3 объединены и поступают на Q-шину. Формирователь сигналов управления Q-шины 5 содержит два резистора 7, 8, четыре триггера 9, 10, 11, 12, пять линий задержки 13, 14, 15, 16, 17, второй и третий логические элементы И.

Принцип работы адаптера шины ISA с Q-шиной

При обращении к соответствующему порту дешифратор адреса порта 1 вырабатывает строб длительностью 125 нс. Второй выход с дешифратора адреса порта 1 - это строб, по которому происходит сброс триггеров в исходное состояние (которые находятся в формирователе сигналов управления Q-шины). Первый выход с дешифратора адреса порта 1 - это строб, по которому происходит запись данных в регистр записи данных с шины ISA 2, это те данные, которые выставляем на Q-шину во время выполнения операции запись. Пятый выход с дешифратора адреса порта - это строб, по которому читаем данные с регистра чтения данных с шины ISA 3. Третий и четвертый выходы с дешифратора адреса порта - это стробы, которые объединены через первый лог. элемент И 6, открывают формирователь адреса Q-шины 4, который переводит данные с шины ISA в адрес Q-шины (при выполнении операции чтения или записи данных на Q-шину).

Цикл чтения с Q-шины

1. Сброс - это строб записи второго выхода с дешифратора адреса порта 1.

2. Запись адреса на Q-шину - это строб записи третьего выхода с дешифратора адреса порта 1.

3. Чтение данных с Q-шины - это строб чтения пятого выхода с дешифратора адреса порта 1.

При записи адреса на Q-шину стробом этого сигнала открывается шинный формирователь адреса 4, который переводит данные с шины ISA в адрес Q-шины. Одновременно этот строб поступает в формирователь сигналов управления Q-шины 5, где устанавливает триггер 10, перепад с которого через линию задержки 14 и логический элемент И 19 выставляет сигнал SYNC, по которому фиксируется адрес на Q-шине. По окончании действия строба устанавливается триггер 9, перепад с которого, проходя через линию задержки 13, выставляет на Q-шину сигнал DIN, в ответ переферийное устройство выставляет на Q-шину данные и сигнал подтверждения RPLY, который после прохождения через линию задержки 17 и логический элемент И 18 сбросит триггеры 9, 10, 11 и 12 в исходное состояние и тем самым запишет данные в регистр чтения данных с шины ISA 3. Далее по стробу с пятого выхода дешифратора порта читаем данные с регистра чтения данных с шины ISA 3.

Цикл записи на Q-шину

1. Сброс - это строб записи второго выхода с дешифратора адреса порта 1.

2. Запись в регистр записи данных с шины ISА - это строб записи первого выхода с дешифратора адреса порта 1.

3. Запись адреса на Q-шину - это строб записи четвертого выхода с дешифратора адреса порта 1.

При записи адреса на Q-шину стробом этого сигнала открываем шинный формирователь адреса 4, который переводит данные с шины ISA в адрес Q-шины. Одновременно этот строб поступает в формирователь сигналов управления Q-шины 5, где устанавливает триггер 12, перепад с которого через линию задержки 16 и логический элемент И 19 выставляет сигнал SYNC, по которому фиксируется адрес на Q-шине. По окончании действия строба устанавливается триггер 11, перепад с которого открывает регистр записи данных с шины ISA 2, в который предварительно записаны данные, выставляя их на Q-шину, далее перепад, проходя через линию задержки 15, формирует сигнал DOUT, который фиксирует данные на Q-шине. А сигнал подтверждения RPLY, после прохождения через линию задержки 17 и логический элемент И 18 сбрасывает триггеры 9, 10, 11 и 12 в исходное состояние. Таким образом, введение формирователя адреса Q-шины, первого логического элемента И и формирователя сигналов управления Q-шины, содержащего первый, второй, третий и четвертый триггеры, два резистора, первую, вторую, третью, четвертую и пятую линии задержки, второй и третий логические элементы И, позволяет повысить надежность Q-шины за счет эффективной работы PC-IBM.

Источники информации

1. С.Т.Хвощ, В.В. Дорощенко, В.В. Горовой. Организация последовательных мультиплексных каналов САУ. Л.: Машиностроение, 1989.

2. М. Гук. Аппаратные средства IBM PC. СПб., 2000.

3. Ю.В. Новиков, О.А. Калашников, С.Э. Гуляев. Разработка устройств сопряжения. М.: ЭКОМ, 1997.

4. С.М. Блохнин. Шина ISA П/К PC/AT. M.: ПК Сплайн, 1992.

| название | год | авторы | номер документа |

|---|---|---|---|

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Программируемый многоканальный формирователь серий импульсов | 1991 |

|

SU1775846A1 |

| УНИВЕРСАЛЬНОЕ УСТРОЙСТВО КОДИРОВАНИЯ СИГНАЛОВ | 1993 |

|

RU2037270C1 |

| УСТРОЙСТВО АУТЕНТИФИКАЦИИ ПРОГРАММНЫХ МОДУЛЕЙ | 1998 |

|

RU2146834C1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1594554A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Логическое запоминающее устройство | 1977 |

|

SU661609A1 |

Изобретение относится к вычислительной технике, в частности к устройствам сопряжения. Технический результат заключается в создании адаптера шины ISA с Q-шиной. Адаптер содержит: 10-разрядный дешифратор адреса порта, 16-разрядный регистр записи данных с шины ISA, 16-разрядный регистр чтения данных с шины ISA, формирователь адреса Q-шины, первый логический элемент И и формирователь сигналов управления Q-шины, первый, второй, третий и четвертый триггеры, два резистора, первую, вторую, третью, четвертую и пятую линии задержки, второй и третий логические элементы И. 2 ил.

Адаптер шины ISA, содержащий 10-разрядный дешифратор адреса порта, 16-разрядный регистр записи данных с шины ISA и 16-разрядный регистр чтения данных с шины ISA, отличающийся тем, что в него дополнительно введены: формирователь адреса Q-шины, первый логический элемент И и формирователь сигналов управления Q-шины, содержащий первый, второй, третий и четвертый триггеры, два резистора, первую, вторую, третью, четвертую и пятую линии задержки, второй и третий логические элементы И, причем выход 16-разрядной шины данных ISA поступает на вход регистра записи данных с шины ISA, вход формирователя адреса Q-шины и выход регистра чтения данных с шины ISA, причем выходы регистра записи данных с шины ISA, формирователя адреса Q-шины и вход регистра чтения данных с шины ISA соединены вместе и поступают на Q-шину, десять разрядов адреса и управляющие сигналы RD, WR, AEN, шины ISA соединены со входом дешифратора адреса порта, причем первый выход дешифратора адреса порта соединен с первым входом управления регистра записи данных с шины ISA, а второй выход дешифратора соединен с первым входом второго логического элемента И, второй вход которого через вторую линию задержки соединен с Q-шиной, с которой поступает сигнал RPLY, а выход второго логического элемента И соединен со входом R первого, второго, третьего и четвертого триггеров, а третий выход с дешифратора соединен с входом С первого триггера и входом S второго триггера, причем выход первого триггера соединен со вторым управляющим входом регистра чтения данных с шины ISA и со входом первой линии задержки, с выхода которой сигнал DIN поступает на Q-шину, а выход второго триггера соединен со входом третьей линии задержки, выход которой соединен с первым входом третьего логического элемента И, четвертый выход дешифратора соединен с входом С третьего триггера и с входом S четвертого триггера, причем выход третьего триггера соединен со вторым управляющим входом регистра записи данных с шины ISA и со входом четвертой линии задержки, выход с которой, сигнал DOUT, поступает на Q-шину, а выход четвертого триггера соединен со входом пятой линии задержки, выход с которой соединен со вторым входом третьего логического элемента И, выход с которого, сигнал SYNC, поступает на Q-шину, пятый выход с дешифратора соединен с первым управляющим входом регистра чтения данных с шины ISA, а шестой выход дешифратора соединен с шиной ISA сигналом CS-16, причем третий и четвертый выходы дешифратора соединены с первым и вторым входами первого логического элемента И, выход которого соединен с первым управляющим входом формирователя адреса Q-шины.

| НОВИКОВ Ю.В | |||

| и др | |||

| Разработка устройств сопряжения | |||

| - М.: Эком, 1997 | |||

| US 5724528 A, 03.03.1998 | |||

| US 6098141 A, 01.08.2000 | |||

| WO 9854635 A1, 03.12.1998. |

Авторы

Даты

2003-12-27—Публикация

2002-01-30—Подача