Изобретение относится к вычислительной технике, а именно к элементам памяти, и может быть применено для построения статических ОЗУ.

Цель изобретения - повышение степени интеграции элемента памяти.

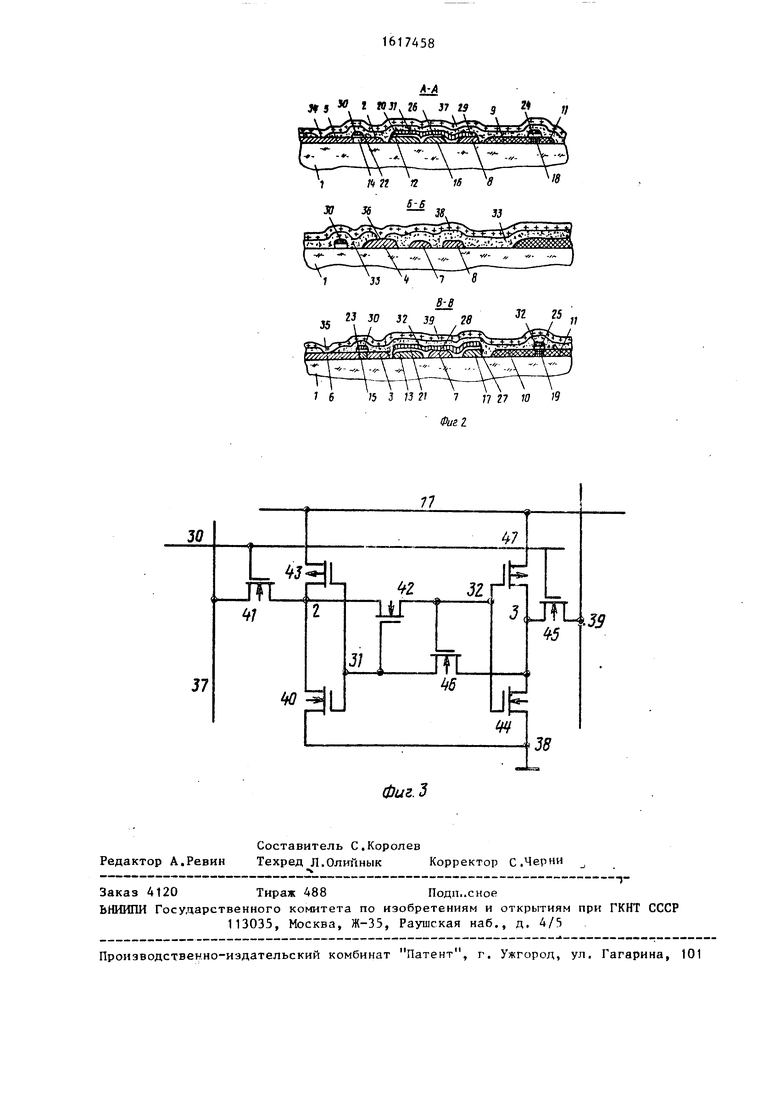

На фиг.1 приведена топология элемента памяти; на фиг.2 - сечения слоев (сечения А-А, 3-Б, В-В на фиг.1), образующих конструкцию элемента памяти; на фиг.З - электрическая схема элемента памяти.

Элемент памяти содержит диэлектрическую подложку 1, например, из монокристаллического сапфира, первую 2, вторую 3, третью 4, четвертую 5, пятую 6, восьмую 7 и девятую 8 диффузионные области первого типа проводимости, девять диффузионных областей 9-17 второго типа проводимости, шестую 18 и седьмую 19 диффузионные области типа проводимости, восемь диэлектрических областей 20-27, два отверстия 28 и 29 в седьмой 26 и восьмой 27 диэлектрических областях под неметаллические контакты, три проводящих области 30-32, например, из поликремния, диэлектрический слой 33 с тремя отверстиями 34-36 и три металлические шины 37-39.

Диффузионная область 2 образует стоки первого 40, второго 41 и седьмого 42 транзисторов и контактирует к истоку пятого транзистора 43, диффузионная область 3 образует стоки третьего 44, четвертого 45 и восьмог 46 транзисторов и контактирует к истоку шестого транзистора 47, диффузионная область 4 образует истоки первого 40 и третьего 44 транзисторов, диффузионные области 5-10 являются истоками второго 41, четвертого 45, седьмого 42, восьмого 46, пятого 43 и шестого 47 транзисторов соответственно. Поликремниевые проводящие области 30-32 образуют затворы всех транзисторов 40-47 элемента памяти, причем проводящая область 30 являетс словарной шиной элемента памяти. Ме- таллические шины 37-39 являются первой разрядной шиной, шиной нулевого потенциала и второй разрядной шиной элемента памяти соответственно.

Элемент памяти работает следующим образом.

В исходном состоянии на затворах первого 40 и пятого 43 транзисторов установлен уровень логического О,

5

0

5

0

35

40

45

50

55

в результате чего н выходе данного первого инвертора устанавливается уровень логической 1.

Это напряжение через седьмой транзистор 42 со встроенным каналом подается на. затворы третьего 44 и шестого 47 транзисторов, в результате чего на выходе данного второго инвертора устанавливается уровень логического О, который через восьмой транзистор 46 прикладывается к затворам первого 40 и пятого 43 транзисторов, устанавливая на выходе первого инвертора уровень логической 1.

Прямая 37 и инверсная 39 разрядные шины предзаряжены до напряжения 2,5 В.

Во время считывания информации, т.е. при поступлении на шину 30 тактового сигнала, второй 41 и четвертый 45 транзисторы открываются, подключая выходы первого и BTopoj-o инвертора к прямой и инверсной разрядным шинам 37 и ЗУ, при этом происходит разряд паразитной емкости шины 39 через четвертый 45 и третий 44 транзисторы и заряд шины 37 через пятый 43 и второй 41 транзисторы. Как только разность потенциалов на шинах 37 и 39 достигнет уровня срабатывания усилителя считывания (-30 мВ), последний фиксирует считанн по информацию.

В процессе яаписи информации на шину 30 поступает тактовый сигнад. Второй 41 и четвертый 45 транзисторы, открыты. Допустим, что на шину 37 подается уровень логического О, а на шину 39 - уровень логической

Через второй транзистор 41 шина 37 подключена к выходу первого инвертора. Уровень логической 1 понижает- ся. Этот потенциал через седьмой транзистор 42 поступает на вход второго инвертора и на его выходе растет потенциал до уровня логической 1 , который в свою очередь через восьмой транзистор 46 поступает на вход первого инвертора. Происходит лавинный процесс переключения инверторов, в результате чего на первом инверторе устанавливается уровень логическо го О, а на втором - логической 1 .

По окончанию тактового сигнала второй 41 и четвертый 45 транзисторы закрываются и записанная информация хранится в элементе памяти.

516

Формула изобретения

Элемент памяти, содержащий диэлектрическую подложку, семь диффузионных областей первого типа проводимости, расположенных на поверхности диэлектрической подложки, семь диффузионных областей второго типа проводимости, расположенных на поверхности диэлектрической подложки, причем диффузионные области второго типа проводимости с четвертой по седьмую расположены соответственно между первой и третьей первой и четвертой, второй и третьей, второй и пятой диффузионными областями первого типа проводимости с примыканием к их краями, а шестая и седьмая диффузионные области первого типа проводимости расположены соответственно между первой и третьей, второй и третьей диффузионными областями второго типа проводимости с примыканием к их краям, шесть диэлектрических областей, расположенных соответственно на поверхностчх шестой и седьмой диффузионных областей первого типа проводимости и на поверхностях диффузионных областей с четвертой по седьмую второго типа проводимости, первую проводящую область, расположенную на поверхностях четвертой и шестой диэлектрических областей, вторую проводящую область, расположенную на поверхностях первой и третьей диэлектрических областей, третью проио- дящую область, расположенную на поверхностях второй и пятой диэлектрических областей, диэлектрический слой, pacпo foжeнный на поверхностях диффузионных областей первого типа проводимости с первую по пятую, вто86

рого типа проводимости с первой по третью, трех проводящих областей и диэлектрической подложки, причем в диэлектрическом слое над третьей, четвертой и пятой диффузионными областями первого типа проводимости соответственно выполнены три отверстия, три металлические шины, расположенные на поверхности диэлектрического слоя и в первом, втором и третьем отверстиях соответственно, отличающийся тем, что, с целью повышения степени интеграции элемента

памяти, он содержит восьмую и девятую диффузионные области первого типа проводимости, расположенные па по- . верхности диэлектрической подложки, восьмую и девятую диффузионные области второго типа проводимости, расположенные на noBepxHocTii диэлектрической подложки между первой и восьмой и второй и девятой диффузионными областями первого типа проводимости

соответственно с примыканием к их краям, седьмую и восьмую диэлектрические области, расположенные на поверхностях восьмой и девятой диффузионных областей BTopoi o типа проводимости соответственно и поверхностях восьмой и девятой диффузионных областей первого типа проводимости соответственно, вторая проводящая область расположена на поверхностях седьмой диэлектрической области и девятой диффузионной области nepBOi o типа проводимости, третья проводящая область расположена на поверхностях восьмой диэлектрической области и

восьмой диффузионной области первого типа проводимости.

2

ft г n )S

18

| название | год | авторы | номер документа |

|---|---|---|---|

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Усилитель считывания (его варианты) | 1983 |

|

SU1137923A1 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 16-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2824472C1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1982 |

|

SU1108915A1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ-НЕ | 2000 |

|

RU2166837C1 |

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| Схема сквозного переноса на КМОП-транзисторах | 1988 |

|

SU1529440A1 |

Изобретение относится к вычислительной технике, а точнее к элементам памяти, и может быть применено для построения статических ОЗУ. Цель изобретения - повышение степени интеграции элемента памяти. Поставленная цель достигается тем, что элемент памяти содержит восьмую и девятую диффузионные области 7, 8 первого типа проводимости, восьмую и девятую диффузионные области 16, 17 второго типа проводимости, седьмую и восьмую диэлектрические области 26, 27. Эти области образуют седьмой и восьмой транзисторы со встроенными каналами. Перекрестные связи триггера элемента памяти образуются с помощью этих транзисторов, что уменьшает количество пересечений проводящих шин и упрощает их разводку. В результате уменьшается количество уровней металлизации элемента памяти, что позволяет уменьшить его площадь. 3 ил.

X X

35

33

BJ Z3 30 32 39 28 P 11

s-s

15 3 /3 r 7 /7 27 10 J9 Фиг 2

| IEEE Journal of Solid-Slate Circuits, V | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| IEEE Journal of Solid-SttUe C.i- rnuits | |||

| V | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1990-12-30—Публикация

1988-12-13—Подача