Изобретение относится к электронной промышленности, в частности к электронным вычислительным машинам.

Известна электронная вычислительная машина, включающая процессор, локальную мультиплексную шину адрес-данные, запоминающее устройство (ЗУ) и системный контроллер (СК), при этом СК обеспечивает связь процессора, ЗУ и внешней шины PCI [1].

Обмен стандартными сигналами процессора и СК обеспечивает выполнение режимов записи и считывания данных по локальной шине адрес-данные в поле адресов ЗУ, а также в поле адресов внешнего адресата по шине PCI в соответствии с протоколом обмена, регламентированным в [1]. Обращение процессора завершается при получении процессором от адресата сигнала Аск (и/или формируемого одновременно с ним сигнала RdCEn).

При обращении внешнего адресата к ЗУ по шине PCI системный контроллер формирует сигнал запроса к процессору Bus Req, если, при этом процессором занята локальная шина адрес-данные, протокол обмена по шине PCI предусматривает ожидание окончания выполнения СК обращения процессора по локальной шине и повторный опрос освобождения процессором локальной шины адрес-данные, о чем процессор сообщает выдачей сигнала Bus Gnt. Однако на время ожидания сигнал Bus Req не снимается и выполнение обращения процессора к внешнему адресату по шине PCI невозможно.

В этом случае, при возникновении сигнала запроса прерывания от другого процессора по шине PCI СК обращается к процессору сигналом Bus Req, однако, если процессор выставил свой запрос на обращение, то есть активны сигналы Rd или Wr, ALE, A/D, процессор не обращает внимания на наличие сигнала Bus Req, ожидает появления сигнала обработки своего обращения - Ack. Протокол обращения по шине PCI предусматривает ожидание разрешения обращения по сигналу Bus Req в виде появления сигнала Bus Gnt и регулярный повтор опроса наличия этого сигнала, не принимая, при этом обращения к себе. СК может в промежутках повторов опросов Bus Gnt провести обращение процессора к ЗУ, после чего процессор освободит шину и выдаст сигнал Bus Gnt, но при обращении процессора к внешнему адресату СК не способен прервать ожидание сигнала Bus Gnt и провести обработку обращения от внешнего адресата

Возникает ситуация зависания, неразрешимая при обмене стандартными сигналами.

Задачей патентуемого изобретения является предотвращение зависания процессоров при совпадении встречных запросов от процессоров, подключенных к внешней шине PCI.

Технический результат заключается в выработке дополнительных сигналов - признак дешифрации адреса обращения внешнего адресата к ЗУ и признак дешифрации адреса обращения процессора к внешнему адресату по внешней шине PCI.

Указанные задача и технический результат достигаются электронной вычислительной машиной, включающей процессор, локальную мультиплексную шину адрес-данные, запоминающее устройство (ЗУ) и системный контроллер (СК), при этом она снабжена блоком обработки встречных запросов (БОВЗ) с восемью входами и пятью выходами, образующим с системным контроллером модернизированный системный контроллер (МСК), связывающий процессор с ЗУ и обеспечивающий связь процессора и ЗУ с внешней шиной PCI, причем первый выход-выход процессора соединен указанной шиной адрес-данные с первым входом-выходом ЗУ, с первым входом СК, с первым входом БОВЗ, с первым выходом БОВЗ, второй выход сигнала записи адреса обращения процессора (ALE) соединен со вторым входом СК, третий выход сигнала режима чтения процессора (Rd) соединен с третьим входом сигнала режима чтения СК и со вторым входом БОВЗ, четвертый выход сигнала режима записи процессора (Wr) соединен с третьим входом БОВЗ, пятый выход сигнала подтверждения передачи управления локальной шиной от процессора к системному контроллеру (Bus Gnt) соединен с четвертым входом БОВЗ, первый выход СК сигнала признака дешифрации адреса обращения процессора к внешнему адресату по шине PCI соединен с пятым входом БОВЗ, второй выход СК сигнала признака дешифрации обращения внешнего адресата по шине PCI к ЗУ соединен с шестым входом БОВЗ, третий выход СК сигнала запроса от внешнего адресата на захват управления локальной шиной (Bus Req) соединен с седьмым входом БОВЗ, четвертый выход СК сигнала подтверждения истинных данных на шине процессора (Ack) соединен с восьмым входом БОВЗ, второй выход БОВЗ соединен с четвертым входом сигнала подтверждения передачи управления системному контроллеру СК (Bus Gnt), третий выход БОВЗ соединен с первым входом сигнала подтверждения истинных данных на шине процессора (Ack), четвертый выход БОВЗ соединен с пятым входом сигнала режима записи СК (Wr), внешняя шина PCI подсоединена к шестому входу СК, пятый выход БОВЗ соединен со вторым входом процессора сигнала запроса к процессору на захват управления системной шиной (Bus Req), пятый выход СК сигналов адресной шины соединены со вторым входом адреса ЗУ, шестой выход СК сигналов режима записи-считывания соединены с третьим входом сигналов режима записи-считывания ЗУ.

Указанная задача и технический результат достигаются также тем, что блок обработки встречных запросов (БОВЗ) включает в себя первую схему И, вторую схему И, третью схему И, схему задержки-формирователя, регистр, четвертую схему И, коммутатор, первую схему ИЛИ, пятую схему И, шестую схему И, инвертор, вторую схему ИЛИ, третью схему ИЛИ, четвертую схему ИЛИ и пятую схему ИЛИ, причем пятый вход БОВЗ соединен с первым входом первой схемы И, выход первой схемы И соединен с первым входом второй схемы И, выход второй схемы И соединен с первым входом третьей схемы И и с первым входом шестой схемы И, выход третьей схемы И соединен с входом схемы задержки-формирователя, выход схемы задержки-формирователя соединен с первым входом регистра сигнала записи в регистр информации со второго входа регистра и с первым входом пятой схемы ИЛИ, первый вход БОВЗ соединен со вторым входом регистра, выход данных регистра соединен с первым входом коммутатора, выход сигнала записи регистра соединен с первым входом четвертой схемы И и первым входом третьей схемы ИЛИ, выход четвертой схемы И соединен со вторым входом коммутатора и с первым входом второй схемы ИЛИ, выход данных коммутатора соединен с первым выходом БОВЗ, третий вход БОВЗ соединен с первым входом первой схемы ИЛИ, со вторым входом третьей схемы И и со вторым входом второй схемы ИЛИ, шестой вход БОВЗ соединен с первым входом пятой схемы И, выход первой схемы ИЛИ соединен со вторым входом пятой схемы И, выход пятой схемы И соединен со вторым входом второй схемы И, второй вход БОВЗ соединен со вторым входом первой схемы ИЛИ и со вторым входом шестой схемы И, выход шестой схемы И соединен с первым входом четвертой схемы ИЛИ, седьмой вход БОВЗ соединен со вторым входом первой схемы И, с входом инвертора и со вторым входом третьей схемы ИЛИ, выход третьей схемы ИЛИ соединен с пятым выходом БОВЗ, выход инвертора соединен со вторым входом четвертой схемы И, выход четвертой схемы ИЛИ соединен со вторым выходом БОВЗ, восьмой вход БОВЗ соединен с третьим входом регистра и вторым входом пятой схемы ИЛИ, выход пятой схемы ИЛИ соединен с третьим выходом БОВЗ, четвертый вход БОВЗ соединен со вторым входом четвертой схемы ИЛИ, выход второй схемы ИЛИ соединен с четвертым выходом БОВЗ.

Блок обработки встречных запросов является функциональным узлом МСК и обеспечивает разрешение указанной конфликтной ситуации, возникающей при совпадении во времени встречных запросов от процессоров, подключенных к шине PCI.

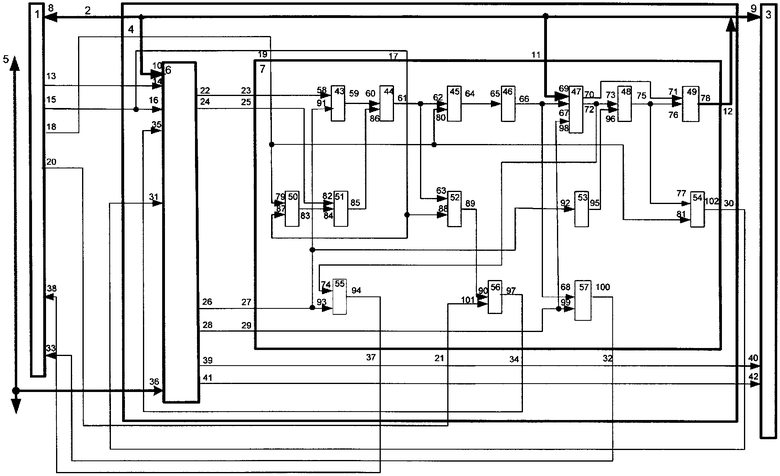

На чертеже представлена блок-схема патентуемой ЭВМ.

Электронная вычислительная машина (ЭВМ) включает процессор 1, локальную мультиплексную шину адрес-данные 2, запоминающее устройство (ЗУ) 3 и модернизированный системный контроллер (МСК) 4, обеспечивающий связь процессора 1, ЗУ 3 и внешней шины PCI 5. Модернизированный системный контроллер состоит из системного контроллера (СК) 6 и блока обработки встречных запросов (БОВЗ) 7 с восемью входами и пятью выходами.

Первый вход-выход 8 процессора 1 соединен указанной шиной адрес-данные 2 с первым входом-выходом 9 ЗУ 3, с первым входом 10 СК 6, с первым входом 11 БОВЗ 7 и с первым выходом 12 БОВЗ 7. Второй выход 13 сигнала записи адреса обращения процессора 1 (ALE) соединен со вторым входом 14 СК 6. Третий выход 15 сигнала режима чтения (Rd) процессора 1 соединен с третьим входом 16 СК 6 и со вторым входом 17 БОВЗ 7. Четвертый выход 18 сигнала режима записи (Wr) процессора 1 соединен с третьим входом 19 БОВЗ 7. Пятый выход 20 сигнала подтверждения передачи управления локальной шиной 2 от процессора 1 к системному контроллеру 6 (Bus Gnt) соединен с четвертым входом 21 БОВЗ 7. Первый выход 22 СК 6 сигнала признака дешифрации адреса обращения процессора 1 к внешнему адресату по шине PCI 5 соединен с пятым входом 23 БОВЗ 7. Второй выход 24 СК 6 сигнала признака дешифрации обращения внешнего адресата по шине PCI 5 к ЗУ 2 соединен с шестым входом 25 БОВЗ 7. Третий выход 26 СК 6 сигнала запроса от внешнего адресата на захват управления локальной шиной (Bus Req) соединен с седьмым входом 27 БОВЗ 7. Четвертый выход 28 СК 6 сигнала подтверждения истинных данных на шине процессора 1 (Ack) соединен с восьмым входом 29 БОВЗ 7. Второй выход 34 БОВЗ 7 соединен с четвертым входом 35 СК 6 сигнала подтверждения передачи управления системному контроллеру СК 6 (Bus Gnt). Третий выход 32 БОВЗ 7 соединен с первым входом 33 процессора 1 сигнала подтверждения истинных данных на шине процессора 1 (Ack). Четвертый выход 30 БОВЗ 7 соединен с пятым входом 31 СК 6 сигнала режима записи (Wr) СК 6. Внешняя шина PCI 5 подсоединена к шестому входу 36 СК 6. Пятый выход 37 БОВЗ 7 соединен со вторым входом 38 процессора 1 сигнала запроса к процессору на захват управления системной шиной (Bus Req). Пятый выход 39 СК 6 сигналов адресной шины соединен со вторым входом 40 адреса обращения к ЗУ 3. Шестой выход 41 СК 6 сигналов режима записи-считывания соединен с третьим входом 42 режима записи-считывания ЗУ3.

Блок обработки встречных запросов включает в своем составе первую схему И 43, вторую схему И 44, третью схему И 45, схему задержки-формирователя 46, регистр 47, четвертую схему И 48, коммутатор 49, первую схему ИЛИ 50, пятую схему И 51, шестую схему И 52, инвертор 53, вторую схему ИЛИ 54, третью схему ИЛИ 55, четвертую схему ИЛИ 56 и пятую схему ИЛИ 57.

Пятый вход 23 БОВЗ 7 соединен с первым входом 58 первой схемы И 43, выход 59 первой схемы И 43 соединен с первым входом 60 второй схемы И 44, выход 61 второй схемы И 44 соединен с первым входом 62 третьей схемы И 45 и с первым входом 63 шестой схемы И 52, выход 64 третьей схемы И 45 соединен с входом 65 схемы задержки-формирователя 46, выход 66 схемы задержки-формирователя 46 соединен с первым входом 67 регистра 47 сигнала записи в регистр 47 информации со второго входа 69 регистра 47 и с первым входом 68 пятой схемы ИЛИ 57, первый вход 11 БОВЗ 7 соединен со вторым входом 69 регистра 47, выход данных 70 регистра 47 соединен с первым входом 71 коммутатора 49, выход сигнала записи 72 регистра 47 соединен с первым входом 73 четвертой схемы И 48 и первым входом 74 третьей схемы ИЛИ 55, выход 75 четвертой схемы И 48 соединен со вторым входом 76 коммутатора 49 и с первым входом 77 второй схемы ИЛИ 54, выход данных 78 коммутатора 49 соединен с первым выходом 12 БОВЗ 7, третий вход 19 БОВЗ 7 соединен с первым входом 79 первой схемы ИЛИ 50, со вторым входом 80 третьей схемы И 45 и со вторым входом 81 второй схемы ИЛИ 54, шестой вход 25 БОВЗ 7 соединен с первым входом 82 пятой схемы И 51, выход 83 первой схемы ИЛИ 50 соединен со вторым входом 84 пятой схемы И 51, выход 85 пятой схемы И 51 соединен со вторым входом 86 второй схемы И 44, второй вход 17 БОВЗ 7 соединен со вторым входом 87 первой схемы ИЛИ 50 и со вторым входом 88 шестой схемы И 52, выход 89 шестой схемы И 52 соединен с первым входом 90 четвертой схемы ИЛИ 56, седьмой вход 27 БОВЗ 7 соединен со вторым входом 91 первой схемы И 43, со входом 92 инвертора 53 и со вторым входом 93 третьей схемы ИЛИ 55, выход 94 третьей схемы ИЛИ 55 соединен с пятым выходом 37 БОВЗ 7, выход 95 инвертора 53 соединен со вторым входом 96 четвертой схемы И 48, выход 97 четвертой схемы ИЛИ 56 соединен со вторым выходом 34 БОВЗ 7, восьмой вход 29 БОВЗ 7 соединен с третьим входом 98 регистра 47 и вторым входом 99 пятой схемы ИЛИ 57, выход 100 пятой схемы ИЛИ 57 соединен с третьим выходом 32 БОВЗ 7, четвертый вход 21 БОВЗ 7 соединен со вторым входом 101 четвертой схемы ИЛИ 56, выход 102 второй схемы ИЛИ 54 соединен с четвертым выходом 30 БОВЗ.

При наличии сигналов Wr или Rd на входах 79 или 87, соответственно, через схему ИЛИ 50 с выхода 83 первой схемы ИЛИ 50 на вход 84 пятой схемы И 51 поступает разрешение прохождения признака дешифрации адреса обращения внешнего адресата к ЗУ со второго выхода 24 СК 6 и первого входа 82 пятой схемы И 51 через схему И 51 на выход 85 схемы И 51 и на второй вход 86 второй схемы И 44. При наличии запроса процессора 1 к внешнему адресату на шине PCI 5 с первого выхода 22 СК 6 на первый вход 58 первой схемы И 43 поступает признак дешифрации адреса обращения процессора 1 к внешнему адресату по шине PCI 5. При наличии, при этом запроса от внешнего адресата с третьего выхода 26 СК 6 сигнал Bus Req поступает на второй вход 91 первой схемы И 43 и дает разрешение прохождения признака дешифрации адреса обращения процессора к внешнему адресату по шине PCI 5 с первого выхода 22 СК 6 и первого входа 58 первой схемы И 43 через первую схему И 43 на выход 59 первой схемы И 43 и на первый вход 60 второй схемы И 44. При наличии на входах 86 и 60 второй схемы И 44 одновременно сигналов встречных запросов на выходе 61 второй схемы И 44 формируется сигнал наличия конфликтной ситуации встречных запросов. Этот сигнал поступает на первые входы 62 и 63 третьей и шестой схем И 45 и И 52, соответственно, на вторые входы 80 и 88 которых, соответственно, поступают сигналы Wr и Rd соответственно. На выходах 64 и 89 третьей и шестой схем И 45 и И 52, соответственно формируются сигналы наличия конфликта в режиме записи и считывания процессора 1 соответственно.

При наличии конфликта в режиме считывания шина 2 свободна, а на выходе 89 шестой схемы И 52 сформирован сигнал наличия конфликта, который поступает на первый вход 90 четвертой схемы ИЛИ 56 и через схему ИЛИ 56 с выхода 97 на вход 35 СК 6 поступает имитация сигнала Bus Gnt, при наличии этого сигнала СК 6 выполняет стандартный протокол обращения внешнего адресата к ЗУ по свободной шине 2, который заканчивается снятием сигнала Bus Req с выхода 26 СК 6 и со входа 91 первой схемы И 43 и на выходе 59 первой схемы И 43 и на входе 60 второй схемы И снимается сигнал признака дешифрации адреса обращения процессора к внешнему адресату по шине PCI 5, следовательно, на выходе 61 второй схемы И 44 и входе 63 шестой схемы И 52 снимается сигнал конфликтной ситуации, на выходе 89 шестой схемы И 52 и на входе 90 четвертой схемы ИЛИ 56 снимается сигнал конфликтной ситуации в режиме считывания. Это приводит к снятию имитации сигнала Bus Gnt на выходе 97 четвертой схемы ИЛИ 56 и со входа 35 СК 6. Конфликт разрешен и СК 6 стандартным протоколом выполняет обращение процессора к внешнему адресату. Цикл обращения заканчивается формированием сигнала Аск, который с выхода 28 СК 6 поступает на второй вход 99 пятой схемы ИЛИ 57 и через схему И 57 с ее выхода 100 поступает на вход 33 процессора 1. Процессор после завершения цикла считывания снимает сигнал Rd. Таким образом, оба встречных запроса удовлетворены.

В режиме записи процессор 1 на своем втором выходе 13 формирует сигнал записи адреса обращения, поступающий на вход 14 СК 6 и через промежуток времени То, заданным мультиплексированным режимом работы локальной шины 2, выставит на шине 2 информацию для внешнего адресата. На выходе 64 третьей схемы И 45 формируется сигнал конфликта при записи, который поступает на вход 65 схемы задержки-формирователя 46, по которому через промежуток времени То на выходе 66 схемы задержки-формирователя 46 формируется имитация сигнала Аск. По входу 67 схемы регистра 47 этот сигнал запишет данные с шины 2 и с входа 69 схемы регистра 47 в регистр 47 и на выходе 70 регистра 47 установится хранимая информация для внешнего адресата, а на выходе 72 установится сигнал записи внешнему адресату. С выхода 66 схемы задержки-формирователя 46 имитация сигнала Аск поступает, также, на вход 68 пятой схемы ИЛИ 57 и через схему 57 с ее выхода 100 имитация сигнал Аск поступает на первый вход 33 процессора 1, по которому процессор закончит режим записи, снимет сигнал Wr и освободит шину 2. Конфликт снят при сохранении сигнала Bus Req на выходе 26 СК 6 и на входе 93 третьей схемы ИЛИ 55, который через схему ИЛИ 55 с ее выхода 94 поступает на второй вход 38 сигнала Bus Req процессора 1. С выхода 26 СК 6 сигнал Bus Req поступает, также, на вход 92 инвертора 53, а через инвертор 53 с его выхода 95 на вход 96 четвертой схемы И 48 поступает запрет прохождения сигнала записи с выхода 72 регистра 47 через схему И 48 на ее выход 75 и на вход 76 коммутатора 49, выход которого в этой ситуации находится в третьем состоянии и не препятствует работе по шине 2. Процессор после окончания режима записи после снятия конфликта в стандартном режиме на сохраняющийся запрос сигнала Bus Req выдает на своем пятом выходе 20 ответ сигналом Bus Gnt, который поступит на вход 101 четвертой схемы ИЛИ 56 и через схему ИЛИ 56 с ее выхода 97 поступит на вход 35 СК 6, после чего СК 6 стандартным протоколом выполнит обращение внешнего адресата к ЗУ, которое закончится снятием сигнала Bus Req с выхода 26 СК 6 и с входа 93 третьей схемы ИЛИ 55. Однако наличие сигнала записи с выхода 72 регистра 47 на входе 74 третьей схемы ИЛИ 55 удерживает на ее выходе 94 и на втором входе 38 процессора 1 сигнал Bus Req, что не позволяет процессору снимать сигнал Bus Gnt и занимать шину 2. При снятии сигнала Bus Req с выхода 26 СК 6 и, следовательно, со входа 92 инвертора 53 на выходе 95 инвертора 53 и входе 96 четвертой схемы И 48 появляется сигнал разрешения прохождения сигнала записи, который через схему И 48 с ее выхода 75 поступает на вход 76 коммутатора 49 и открывает коммутатор 49. Ранее записанная в регистре 47 информация процессора 1 с выхода 70 регистра 47 поступает на вход 71 коммутатора 49 и через открытый коммутатор 49 с его выхода 78 на шину 2, а с выхода 75 четвертой схемы И 48 на вход 77 второй схемы ИЛИ 54 и через схему ИЛИ 54 с ее выхода 102 на вход 31 СК 6 поступает имитация сигнала записи. Внутренний регистр адреса СК 6 не получал нового сигнала записи адреса по входу 14 и сохраняет ранее записанный адрес внешнего адресата по шине PCI. СК 6 по имитированному сигналу записи Wr выполняет стандартный протокол записи данных с выхода коммутатора 49 по шине 2 по сохраненному адресу внешнего адресата на шине PCI. Цикл обращения заканчивается выдачей сигнала Аск с выхода 28 СК 6, который поступает на вход 98 регистра 47 и сбрасывает регистр в исходное состояние, сигнал записи снимается с выхода 72 и через И 48 с ее выхода 75 по входу 76 коммутатора 49 отключает коммутатор 49, переводя его выход в третье состояние и освобождая шину 2, а по входу 77 второй схемы ИЛИ 54 через схему ИЛИ 54 с ее выхода 102 на входе 31 СК 6 снимается сигнал записи Wr, снятие сигнала записи с выхода 72 регистра 47 приводит к снятию имитации сигнала Bus Req со входа 74 третьей схемы ИЛИ 55, с ее выхода 94 и со второго входа 38 процессора 1. Процессор снимает после этого сигнал Bus Gnt с выхода 20. Оба встречных запроса удовлетворены.

При отсутствии конфликта встречных запросов нет сигнала конфликта на выходе 61 второй схемы И 44, сигналов конфликтов в режимах записи и считывания на выходах 64 и 89, соответственно, в исходном состоянии находится регистр 47, закрыт коммутатор, стандартные протоколы обменов обеспечивается прохождением через схемы ИЛИ 54, 55, 56 и 57 сигналов Wr, Bus Req, Bus Gnt и Аск соответственно.

Литература

1. Бетелин В.Б., Бобков С.Г., Дубровский А.Г., Задябин С.О., Крыницкий А.В., Новожилов Е.А., Осипенко П.Н., Романюк С.Г., Сердин О.В. Элементная база аппаратно-программной платформы "Багет", том 1, Москва, НИИСИ РАН, 2004, ISBN 5-93838-017-0 Том 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРХИТЕКТУРА ПРОЦЕССОРА ВВОДА-ВЫВОДА, КОТОРЫЙ ОБЪЕДИНЯЕТ МОСТ МЕЖСОЕДИНЕНИЯ ПЕРВИЧНЫХ КОМПОНЕНТ | 1996 |

|

RU2157000C2 |

| Трехканальная резервированная управляющая система С-01 | 2015 |

|

RU2618365C2 |

| НЕЧУВСТВИТЕЛЬНЫЙ К ЗАДЕРЖКЕ БУФЕР ТРАНЗАКЦИИ ДЛЯ СВЯЗИ С КВИТИРОВАНИЕМ | 2014 |

|

RU2598594C2 |

| Устройство управления доступом к общей памяти | 1977 |

|

SU750490A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для сопряжения микропроцессора с магистралью | 1985 |

|

SU1302287A1 |

| Устройство для сопряжения процессоров | 1990 |

|

SU1807495A1 |

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА СБОРА СЕЙСМИЧЕСКИХ ДАННЫХ | 2003 |

|

RU2244945C1 |

Изобретение относится к вычислительной технике, в частности к электронным вычислительным машинам. Техническим результатом является предотвращение зависания процессоров при совпадении встречных запросов от процессоров, подключенных к внешней шине PCI. Устройство содержит процессор, локальную мультиплексную шину адрес-данные, запоминающее устройство, модернизированный системный контроллер, состоящий из системного контроллера и блока обработки встречных запросов. 2 н.п. ф-лы, 1 ил.

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПОДДЕРЖАНИЯ УПОРЯДОЧЕНИЯ ТРАНЗАКЦИЙ И РАЗРЕШЕНИЯ КОНФЛИКТНЫХ СИТУАЦИЙ В МОСТОВОЙ СХЕМЕ ШИН | 1995 |

|

RU2182356C2 |

| МНОГОПРОЦЕССОРНАЯ КОРАБЕЛЬНАЯ УПРАВЛЯЮЩАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА "ЛАХНА" | 1998 |

|

RU2147379C1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| JP 6083780, 25.03.1994 | |||

| JP 5128060, 25.05.1993. | |||

Авторы

Даты

2007-10-10—Публикация

2005-12-23—Подача