Текст описания приведен в факсимильном виде.

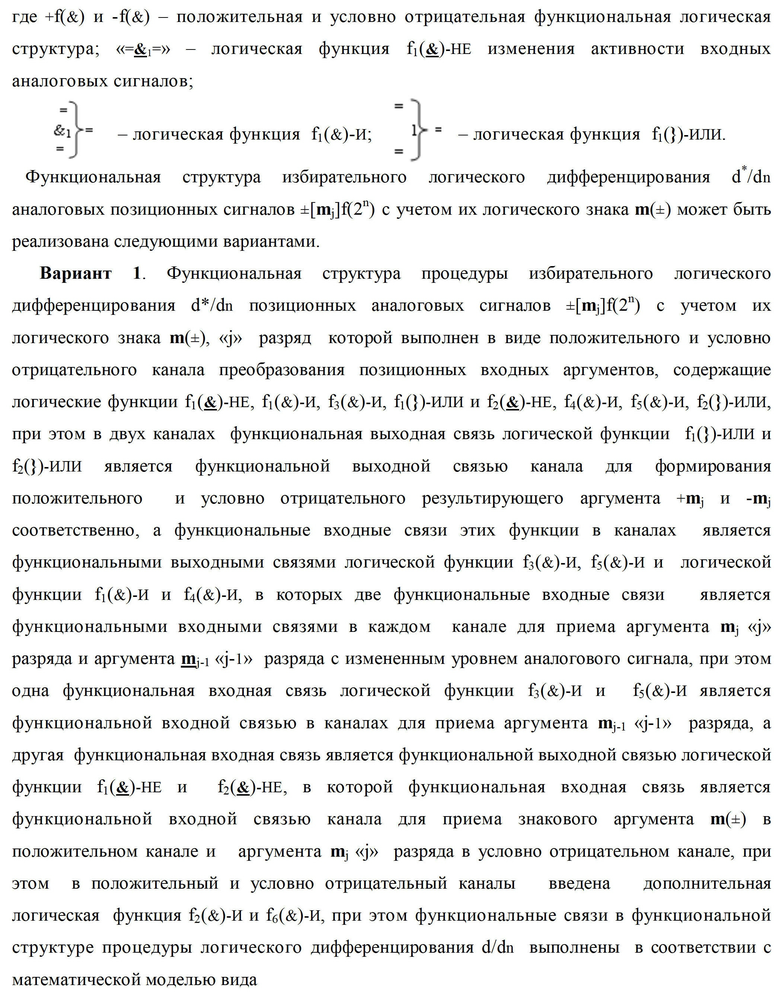

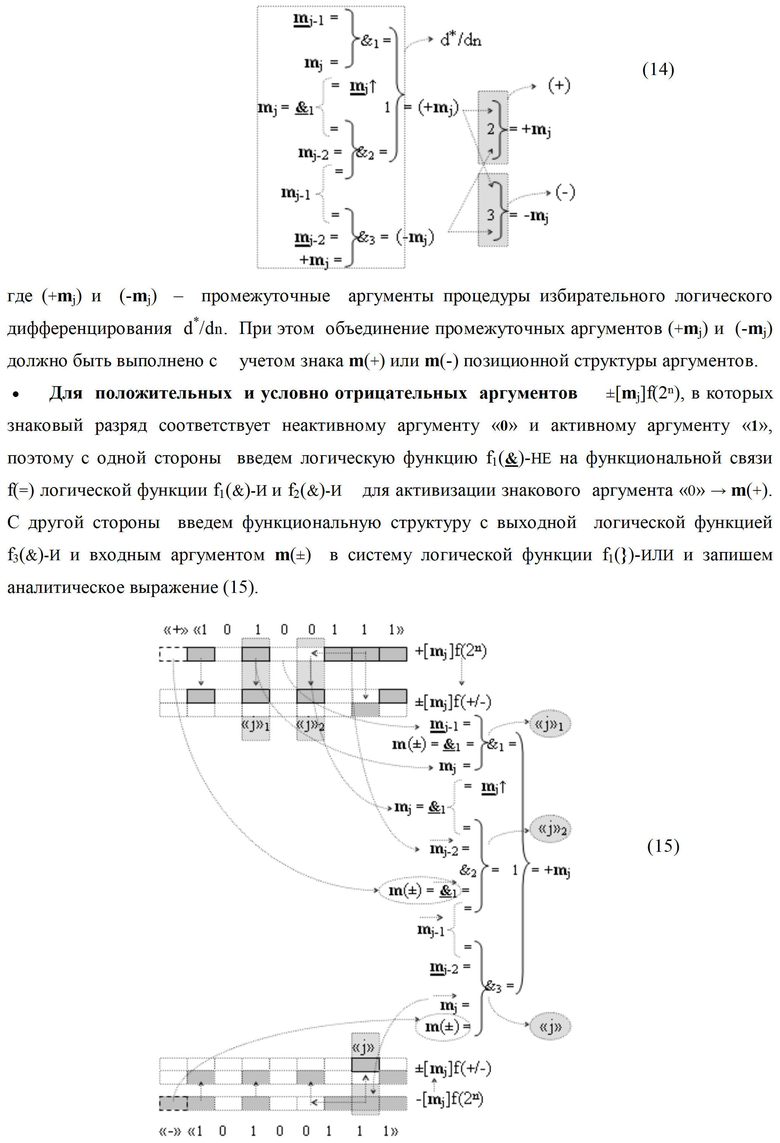

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств и выполнения арифметических операций суммирования и вычитания в позиционно-знаковых кодах. Техническим результатом является повышение быстродействия выполнения арифметических операций. В одном варианте функциональная структура выполнена с использованием элементов, реализующих логические функции И, ИЛИ и НЕ. При этом каждый «j»-ый разряд функциональной структуры выполнен в виде положительного и условно отрицательного канала преобразования входных аргументов mj «j»-го разряда, mj-1 «j-1»-го разряда, mj-2 «j-2»-го разряда и аргумента знака m(±), в положительном канале результирующий аргумент +mj формируют посредством логических функций И1, И2, И3, логической функции НЕ1 и логической функции ИЛИ1, в условно отрицательном канале результирующий аргумент -mj формируют посредством логических функций И4, И5, И6, логической функции НЕ2 и логической функции ИЛИ2. 6 н.п. ф-лы.

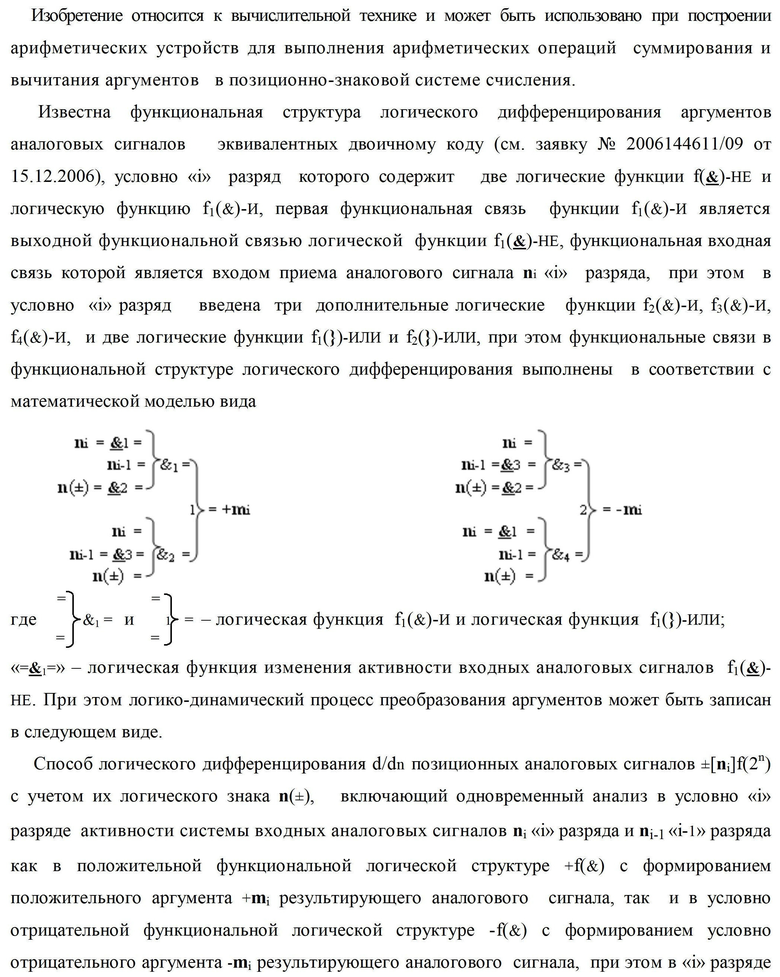

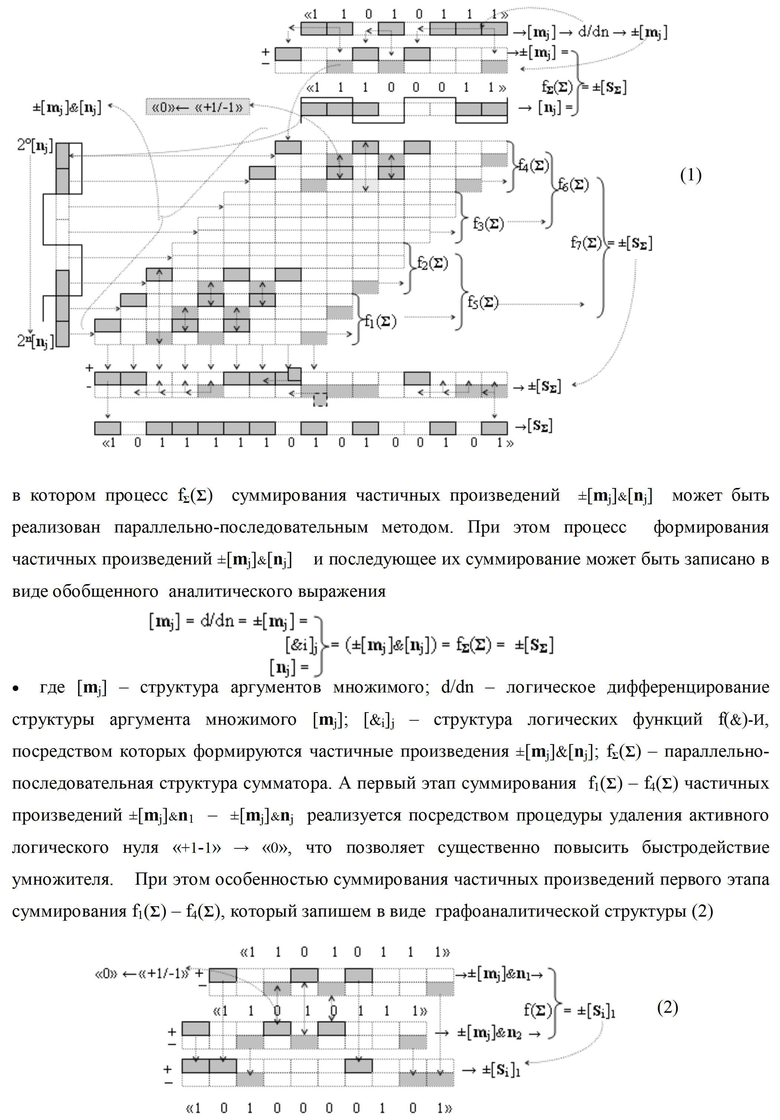

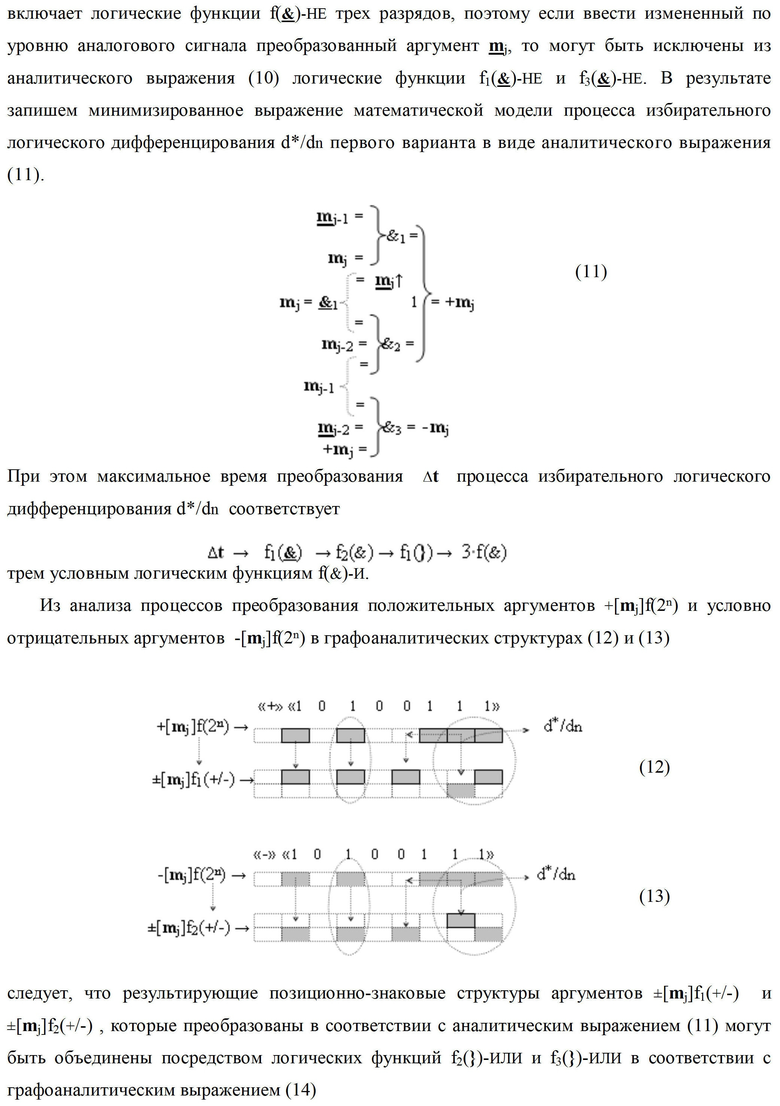

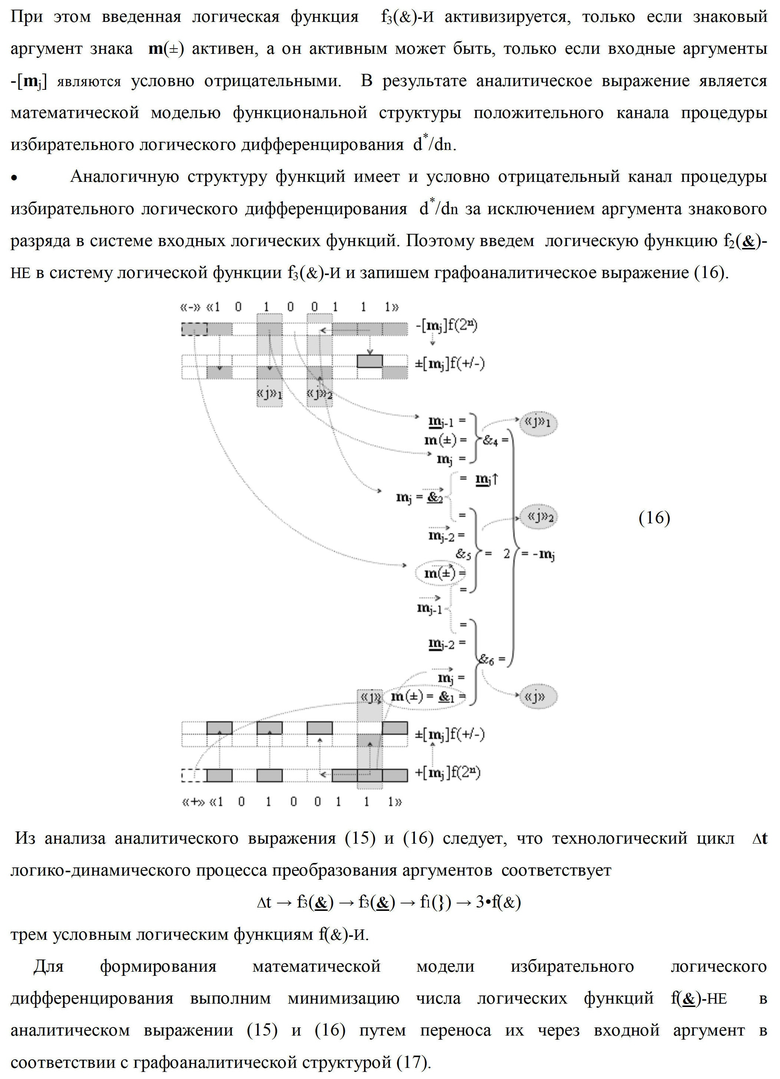

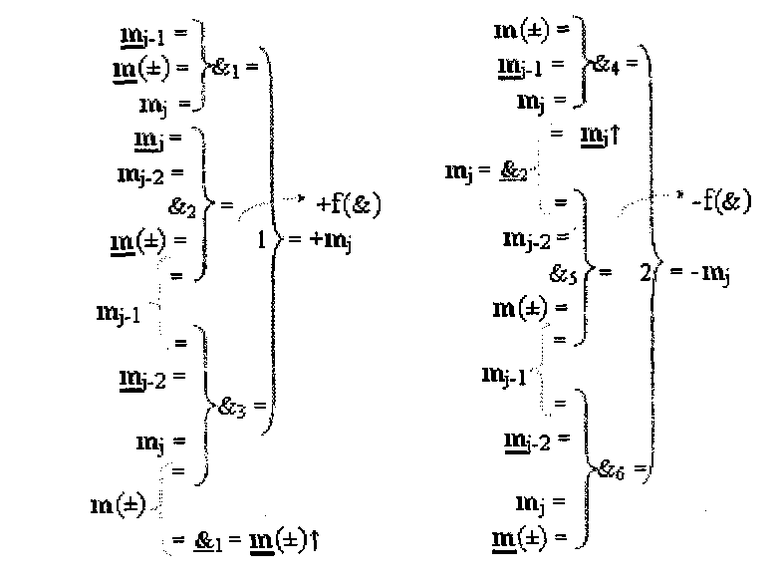

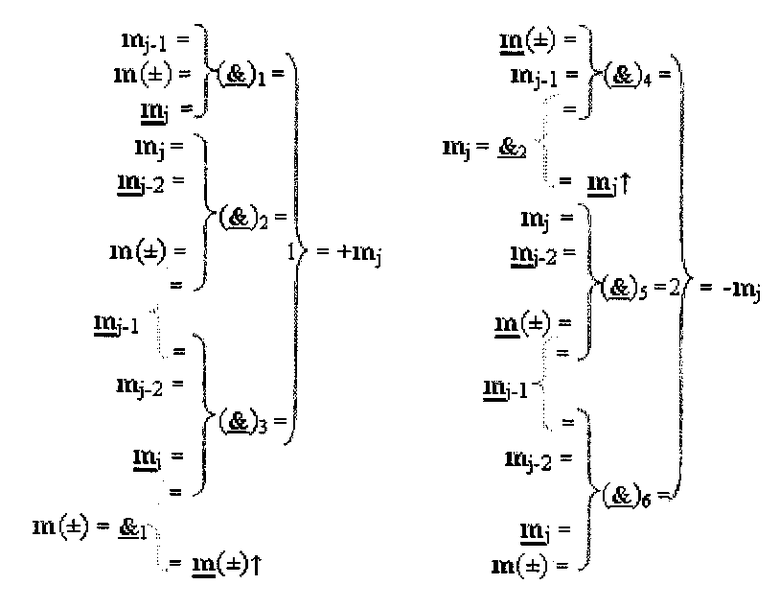

1. Способ избирательного логического дифференцирования d*/dn позиционных аналоговых сигналов ±[mj]f(2n) с учетом их логического знака m(±), включающий одновременный анализ в условно «j» разряде активности системы входных аналоговых сигналов mj условно «j» разряда и mj-1 условно «j-1» разряда с формированием положительного аргумента +mj результирующего аналогового сигнала, так и с формированием условно отрицательного аргумента -mj результирующего аналогового сигнала, отличающийся тем, что одновременный анализ в условно «j» разряде выполняют посредством функциональной логической структуры с учетом аналогового сигнала логического знака m(±), который включает либо условно низкий уровень аналогового сигнала m(+), либо условно высокий уровень аналогового сигнала m(-), при этом в неактивном условно «j» разряде позиционно-знаковой структуры активизируют либо положительный аргумент +mj, либо условно отрицательный аргумент -mj, если в результате анализа посредством функциональной логической структуры предыдущий аргумент mj-1 аналогового сигнала условно «j-1» разряда того же знака также активен, а при активности аргумента mj в условно «j» и активности аргумента mj-1 аналогового сигнала в условно «j-1» разряде и неактивности предыдущего аргумента mj-2 аналогового сигнала в условно «j-2» разряда того же знака активизируют в условно «j» разряде позиционно-знаковой структуры аргумент противоположного знака в соответствии с логико-динамическими процессами преобразования аргументов вида

где  и

и  - активный положительный аргумент и активный условно отрицательный аргумент в позиционно-знаковой структуре.

- активный положительный аргумент и активный условно отрицательный аргумент в позиционно-знаковой структуре.

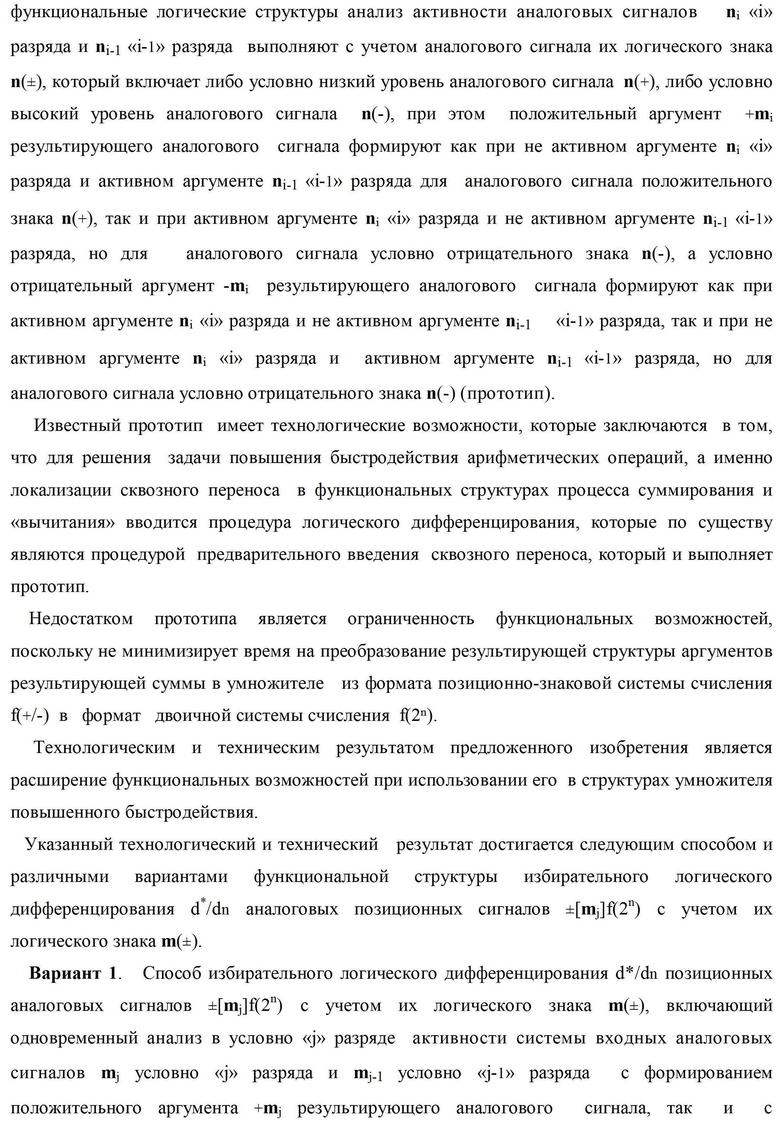

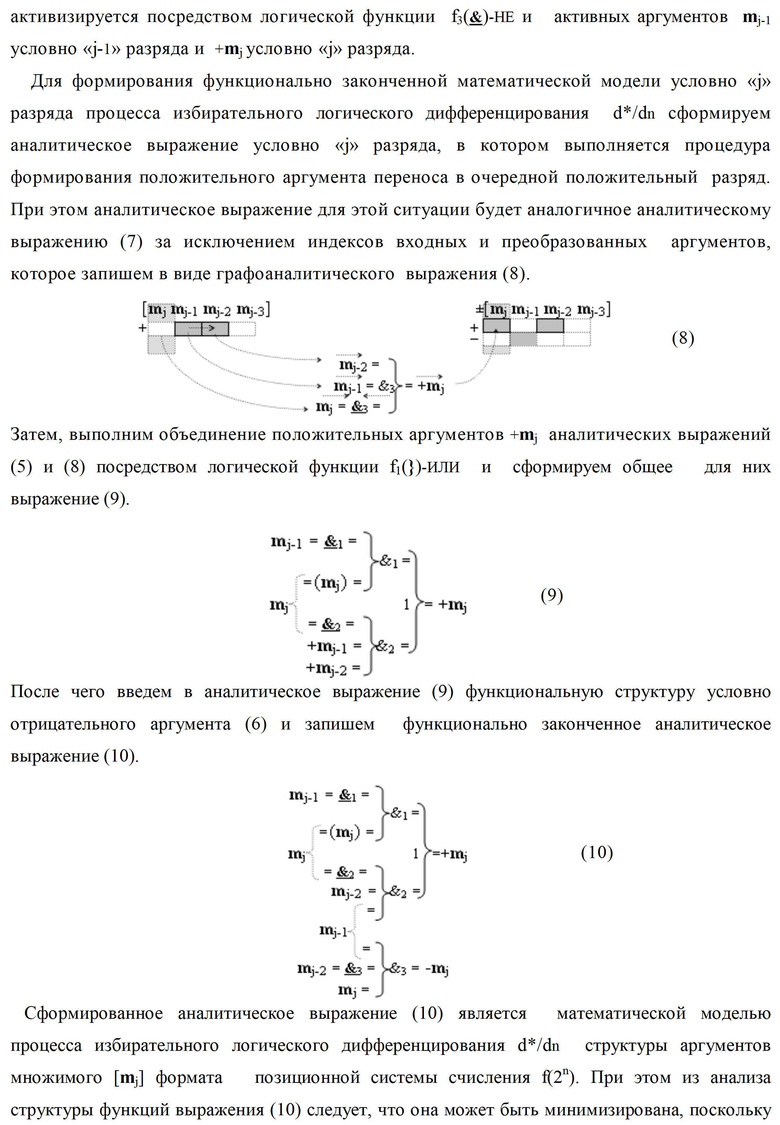

2. Способ избирательного логического дифференцирования d*/dn позиционных аналоговых сигналов ±[mj]f(2n) с учетом их логического знака m(±), включающий одновременный анализ в условно «i» разряде активности системы входных аналоговых сигналов mj «j» разряда и mj-1 «j-1» разряда с учетом аналогового сигнала их логического знака m(±), который включает либо условно низкий уровень аналогового сигнала m(+), либо условно высокий уровень аналогового сигнала m(-) как в положительной функциональной логической структуре +f(&) с формированием положительного аргумента +mj результирующего аналогового сигнала, так и в условно отрицательной функциональной логической структуре -f(&) с формированием условно отрицательного аргумента -mj результирующего аналогового сигнала, при этом посредством логической функции f1(})-ИЛИ активизируют положительный аргумент +mj результирующего аналогового сигнала из входного сигнала, сформированного посредством логической функции f2(&)-И из неактивного аргумента mj «j» разряда, полученного посредством изменения логической функцией f2(&)-HE активности входного аргумента mj, активного аргумента mj-1 «j-1» разряда и аналогового сигнала знака условно низкого уровня m(+), полученного посредством изменения логической функцией f1(&)-НЕ активности входного аналогового сигнала знака m(±), посредством логической функции f2(})-ИЛИ активизируют условно отрицательный аргумент -mj результирующего аналогового сигнала из выходного сигнала, сформированного посредством логической функции f5(&)-И из неактивного аргумента mj «j» разряда, активного аргумента mj-1 «j-1» разряда и аналогового сигнала знака условно высокого уровня n(-), отличающийся тем, что в систему для анализа активности аргументов вводят дополнительный аргумент mj-2 «j-2» разряда, для преобразования посредством логических функций f2(&)-И и f5(&)-И, и положительный аргумент +mj активизируют дополнительно выходным сигналом, который сформирован посредством логической функции f3(&)-И из аналогового аргумента mj «j» разряда, активного аргумента mj-1 «j-1» разряда, не активного аргумента m

j-2 «j-2» разряда и условно высокого аналогового сигнала знака m(-), и из выходного сигнала, сформированного посредством логической функции f1(&)-И из активного аргумента mj «j» разряда, не активного аргумента mj-1 «j-1» разряда и условно низкого уровня аналогового сигнала знака m(+), а условно отрицательный аргумент -mj активизируют дополнительно выходным сигналом, который сформирован посредством логической функции f6(&)-И из активного аргумента mj «j» разряда, активного аргумента аргумента mj-1 «j-1» разряда, неактивного аргумента m

j-2 «j-2» разряда и условно низкого аналогового сигнала m(+), и выходного сигнала, который сформирован посредством логической функции f4(&)-И из активного аргумента mj «j» разряда, неактивного аргумента m

j-1 «j-1» разряда и условно высокого аналогового сигнала знака m(-), при этом математическая модель избирательного логического дифференцирования позиционных аналоговых сигналов имеет вид

где +f(&) и -f(&) - положительная и условно отрицательная функциональная логическая структура; «=&

1=» - логическая функция f1(&)-HE изменения активности входных аналоговых сигналов;

- логическая функция f1(&)-И;

- логическая функция f1(&)-И;  - логическая функция f1(})-ИЛИ.

- логическая функция f1(})-ИЛИ.

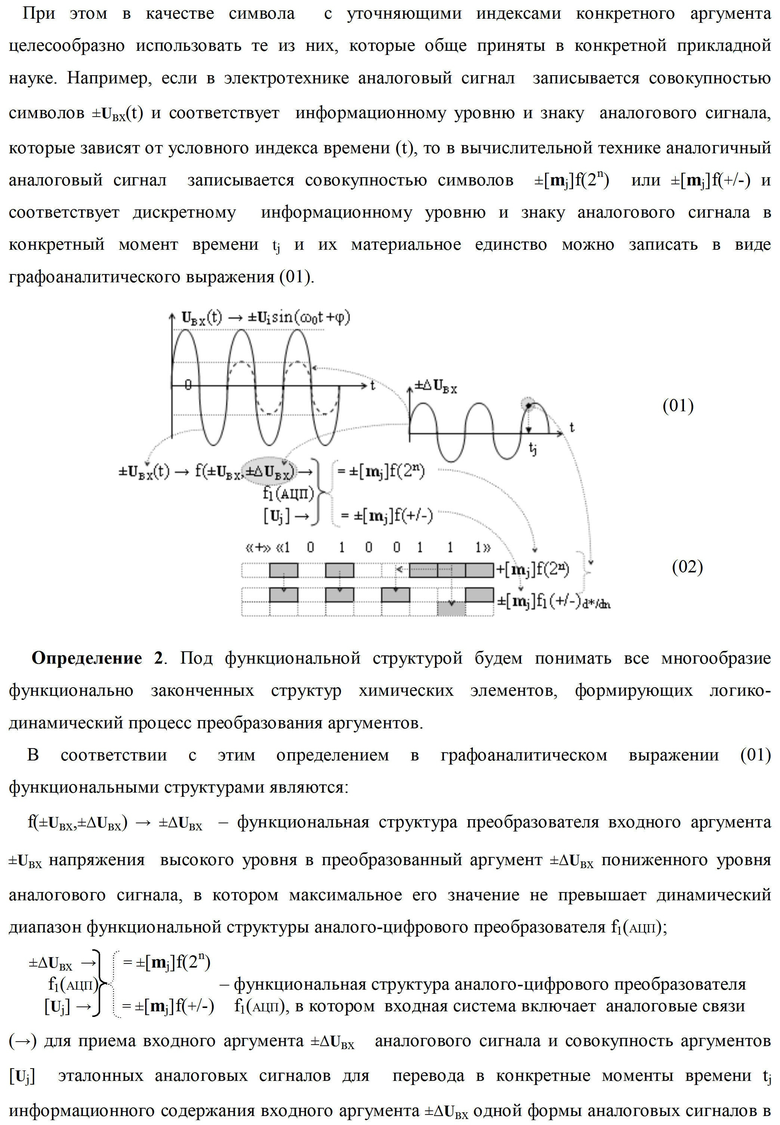

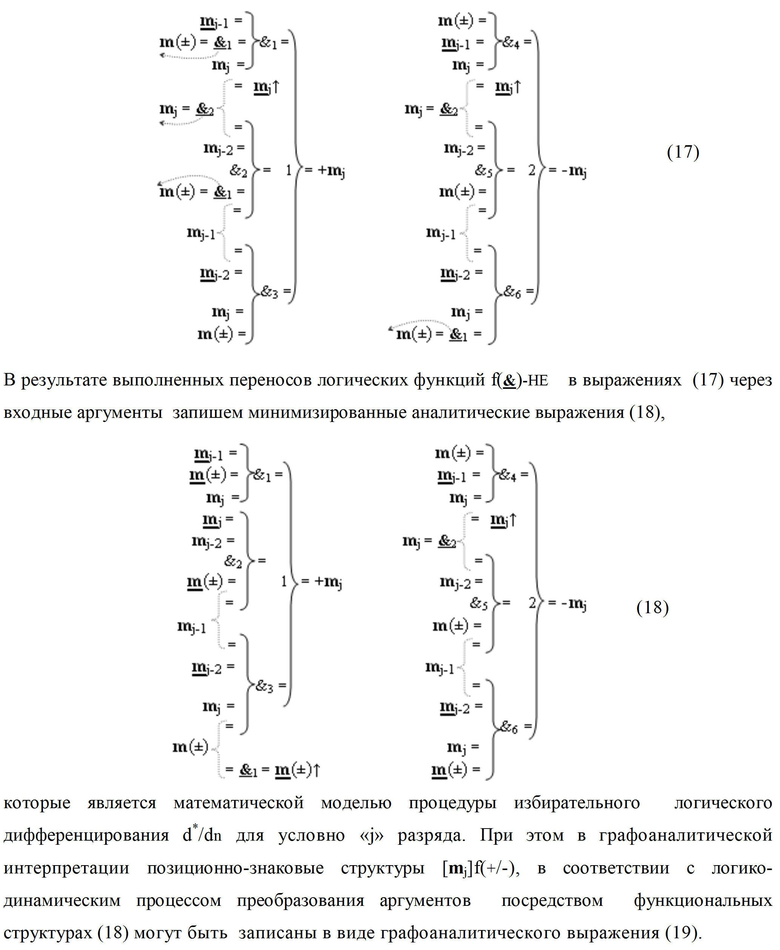

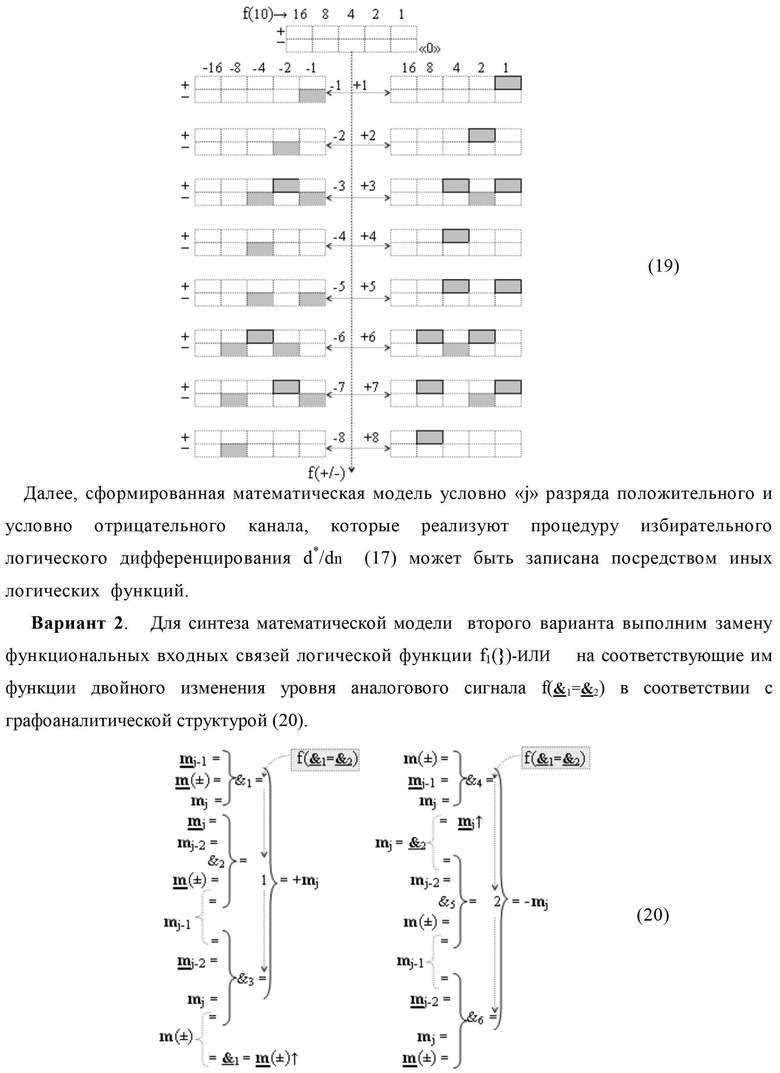

3. Функциональная структура процедуры избирательного логического дифференцирования d*/dn позиционных аналоговых сигналов ±[mj]f(2n) с учетом их логического знака m(±), «j» разряд которой выполнен в виде положительного и условно отрицательного канала преобразования позиционных входных аргументов, содержащие логические функции f1(&)-HE, f1(&)-И, f3(&)-И, f1(})-ИЛИ и f2(&)-HE, f4(&)-И, f5(&)-И, f2(})-ИЛИ, при этом в двух каналах функциональная выходная связь логической функции f1(})-ИЛИ и f2(})-ИЛИ является функциональной выходной связью канала для формирования положительного и условно отрицательного результирующего аргумента +mj и -mj соответственно, а функциональные входные связи этих функции в каналах является функциональными выходными связями логической функции f3(&)-И, f5(&)-И и логической функции f1(&)-И и f4(&)-И, в которых две функциональные входные связи является функциональными входными связями в каждом канале для приема аргумента mj «j» разряда и аргумента m

j-1 «j-1» разряда с измененным уровнем аналогового сигнала, при этом одна функциональная входная связь логической функции f3(&)-И и f5(&)-И является функциональной входной связью в каналах для приема аргумента mj-1 «j-1» разряда, а другая функциональная входная связь является функциональной выходной связью логической функции f1(&)-HE и f2(&)-HE, в которой функциональная входная связь является функциональной входной связью канала для приема знакового аргумента m(±) в положительном канале и аргумента mj «j» разряда в условно отрицательном канале, отличающаяся тем, что в положительный и условно отрицательный каналы введена дополнительная логическая функция f2(&)-И и f6(&)-И, при этом функциональные связи в функциональной структуре процедуры логического дифференцирования d/dn выполнены в соответствии с математической моделью вида

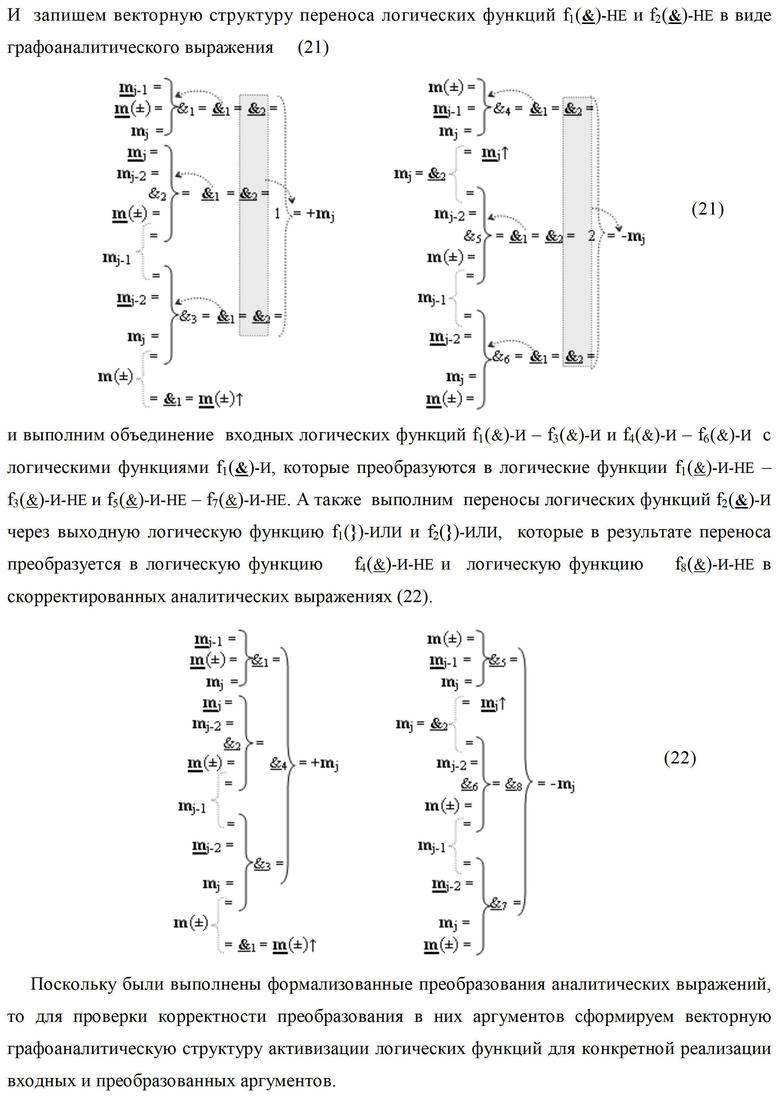

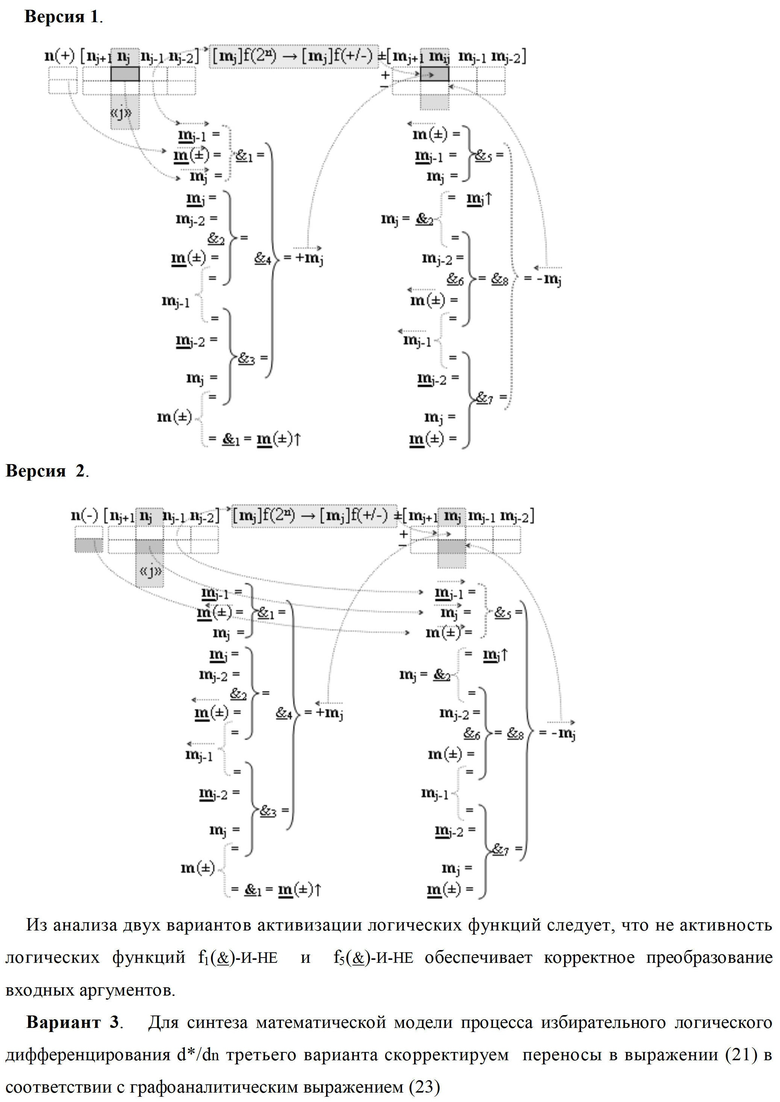

4. Функциональная структура процедуры избирательного логического дифференцирования d*/dn позиционных аналоговых сигналов ±[mj]f(2n) с учетом их логического знака m(±), «j» разряд которой выполнен в виде положительного и условно отрицательного канала преобразования позиционных входных аргументов и формирования положительного и условно отрицательного результирующих аргументов +mj и -mj, содержащие логическую функцию f1(&)-HE и f2(&)-HE, в которой функциональная входная связь является функциональной входной связью канала для приема знакового аргумента m(±) в положительном канале и аргумента mj «j» разряда в условно отрицательном канале, отличающаяся тем, что в положительный канал введены дополнительные логические функции f1(&)-И-HE, f2(&)-И-HE, f3(&)-И-HE и f4(&)-И-HE, а в условно отрицательный канал преобразования аргументов введены дополнительные логические функции f5(&)-И-HE, f6(&)-И-HE, f7(&)-И-НЕ и f8(&)-И-HE, при этом функциональные связи в функциональной структуре процедуры логического дифференцирования d/dn выполнены в соответствии с математической моделью вида

где  - логическая функция f1(&)-И-HE.

- логическая функция f1(&)-И-HE.

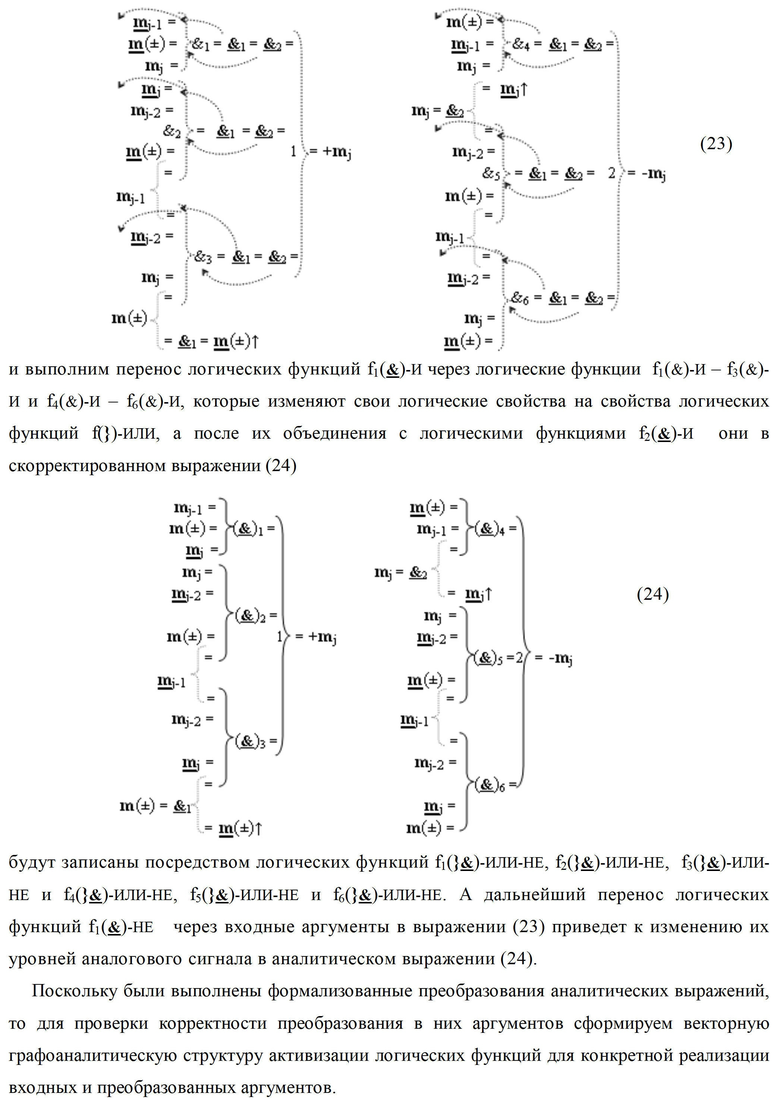

5. Функциональная структура процедуры избирательного логического дифференцирования d*/dn позиционных аналоговых сигналов ±[mj]f(2n) с учетом их логического знака m(±), «j» разряд которой выполнен в виде положительного и условно отрицательного канала преобразования позиционных входных аргументов, содержащие логические функции f1(&)-HE, f1(&)-И, f1(})-ИЛИ и f2(&)-HE, f2(})-ИЛИ, при этом в двух каналах функциональная выходная связь логической функции f1(})-ИЛИ и f2(})-ИЛИ является функциональной выходной связью канала для формирования положительного и условно отрицательного результирующего аргумента +mj и -mj соответственно, а функциональная входная связь логических функций f1(&)-HE и f2(&)-HE, является функциональной входной связью канала для приема знакового аргумента n(±) в положительном канале и аргумента mj «j» разряда в условно отрицательном канале, отличающаяся тем, что в положительный канал введены дополнительные логические функции f1(}&)-ИЛИ-HE, f2(}&)-ИЛИ-НЕ и f3(}&)-ИЛИ-HE, а в условно отрицательный канал введены дополнительные логические функции f4(}&)-ИЛИ-HE, f5(}&)-ИЛИ-НЕ и f6(}&)-ИЛИ-HE, при этом функциональные связи в функциональной структуре процедуры логического дифференцирования d/dn выполнены в соответствии с математической моделью вида

где  - логическая функция f1(}&)-ИЛИ-НЕ.

- логическая функция f1(}&)-ИЛИ-НЕ.

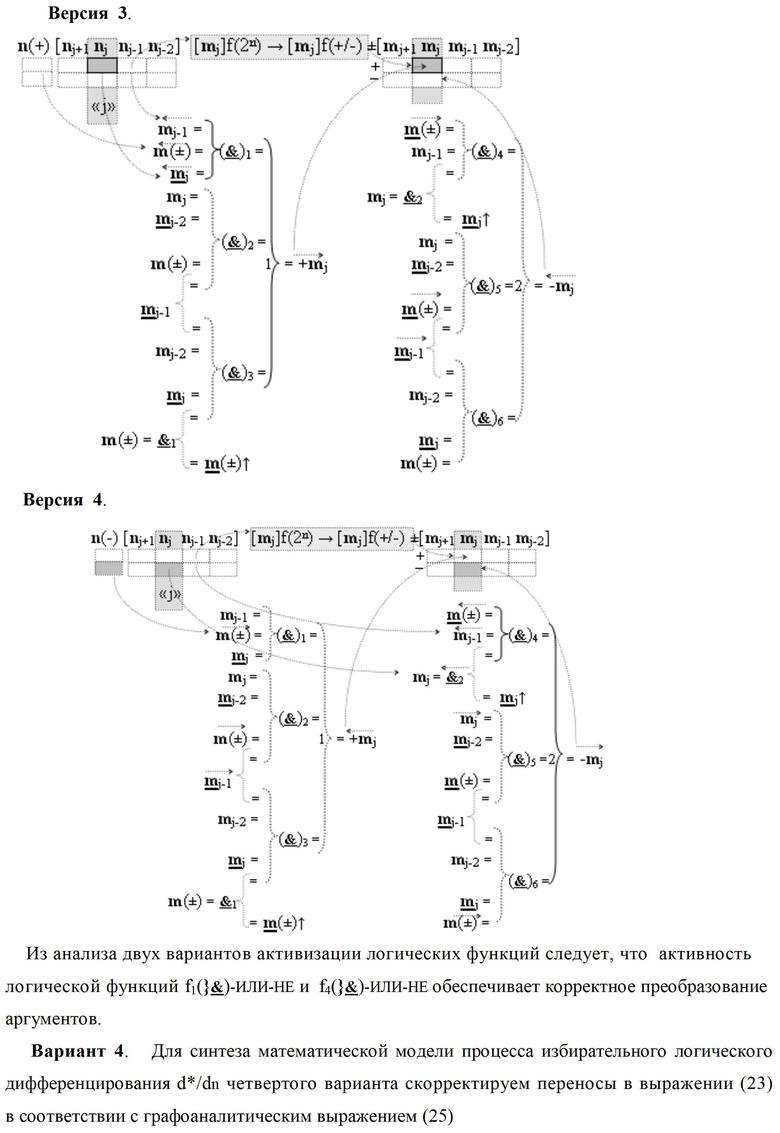

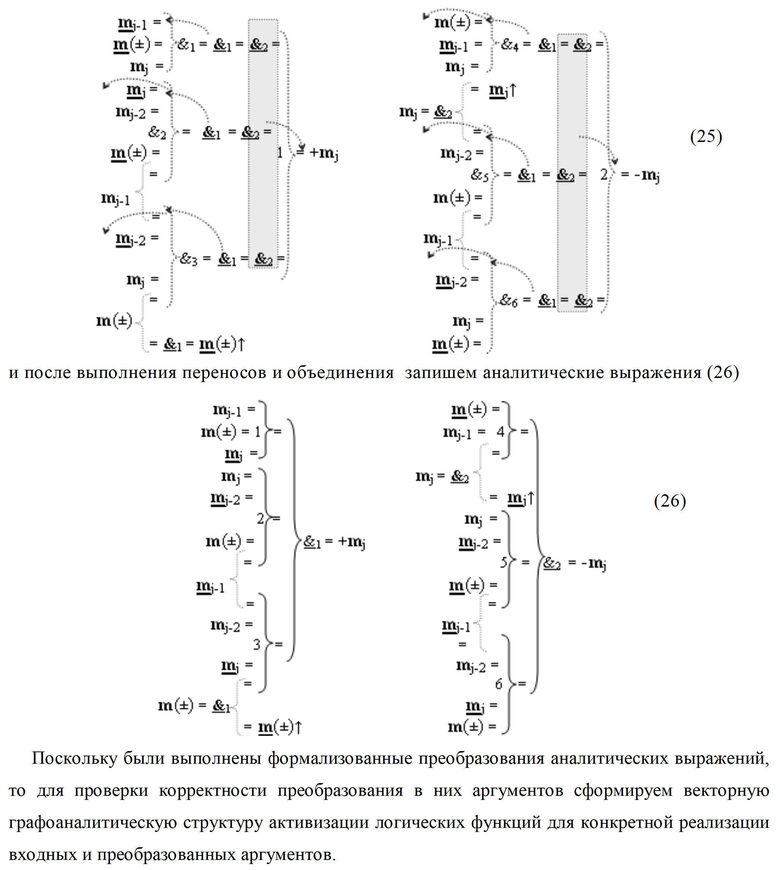

6. Функциональная структура процедуры избирательного логического дифференцирования d*/dn позиционных аналоговых сигналов ±[mj]f(2n) с учетом их логического знака m(±), «j» разряд которой выполнен в виде положительного и условно отрицательного канала преобразования позиционных входных аргументов и формирования положительного и условно отрицательного результирующих аргументов +mj и -mj, содержащие логические функции f1(})-ИЛИ и f4(})-ИЛИ и логическую функцию f1(&)-HE и f2(&)-HE, в которой функциональная входная связь является функциональной входной связью канала для приема знакового аргумента n(±) в положительном канале и аргумента mj «j» разряда в условно отрицательном канале, отличающаяся тем, что в положительный канал введены дополнительные логические функции f2(})-ИЛИ, f3(})-ИЛИ и f1(&)-И-НЕ, а в условно отрицательный канал введены дополнительные логические функции f5(})-ИЛИ, f6(})-ИЛИ и f2(&)-И-НЕ, при этом функциональные связи в функциональной структуре процедуры логического дифференцирования d/dn выполнены в соответствии с математической моделью вида

| RU 2006144611 А, 20.06.2008 | |||

| RU 2006144612 А, 20.06.2008 | |||

| Преобразователь двоичного кода в троичный код | 1983 |

|

SU1169172A1 |

| Преобразователь двоичного кода в позиционно-знаковый код | 1987 |

|

SU1438005A1 |

| JP 57157350 A, 28.09.1982 | |||

| КАРЕТОЧНЫЙ УЗЕЛ ПЕДАЛЬНОГО ПРИВОДА ВЕЛОСИПЕДА | 0 |

|

SU180100A1 |

Авторы

Даты

2011-04-27—Публикация

2009-08-03—Подача