Текст описания приведен в факсимильном виде.

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств и выполнения арифметических операций суммирования частичных произведений. Техническим результатом является повышение быстродействия процесса предварительного суммирования множимого в параллельно-последовательном умножителе. В одном из вариантов изобретения функциональная структура в каждом разряде содержит элементы, реализующие логические функции ИЛИ, И, И-НЕ, ИЛИ-НЕ, при этом каждый разряд выполнен в виде двух каналов суммирования - для формирования положительной результирующей суммы и условно отрицательной результирующей суммы. 4 н.п. ф-лы.

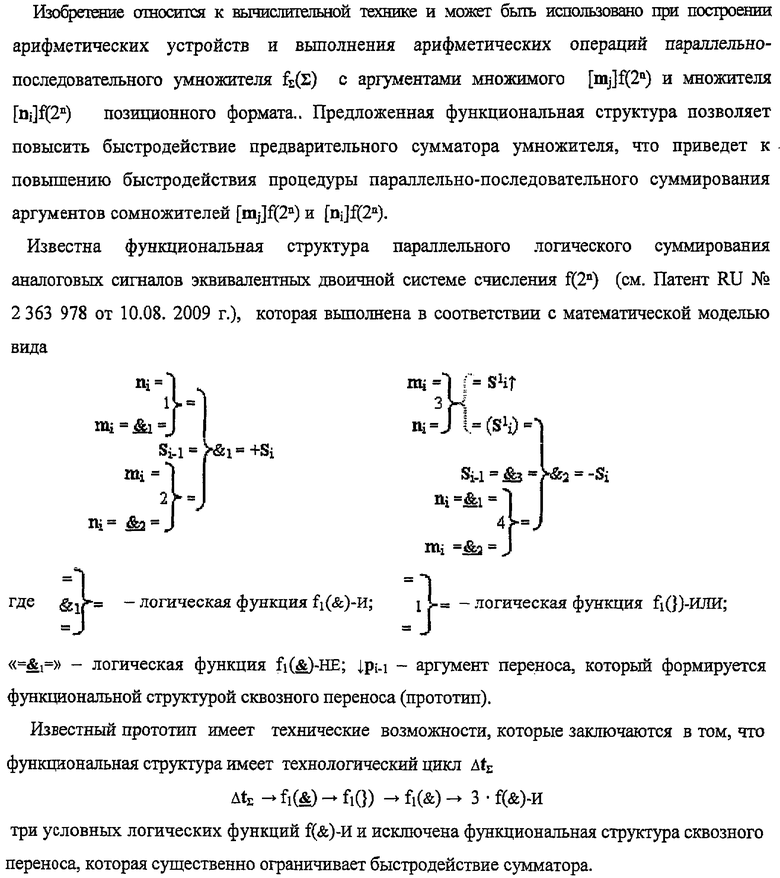

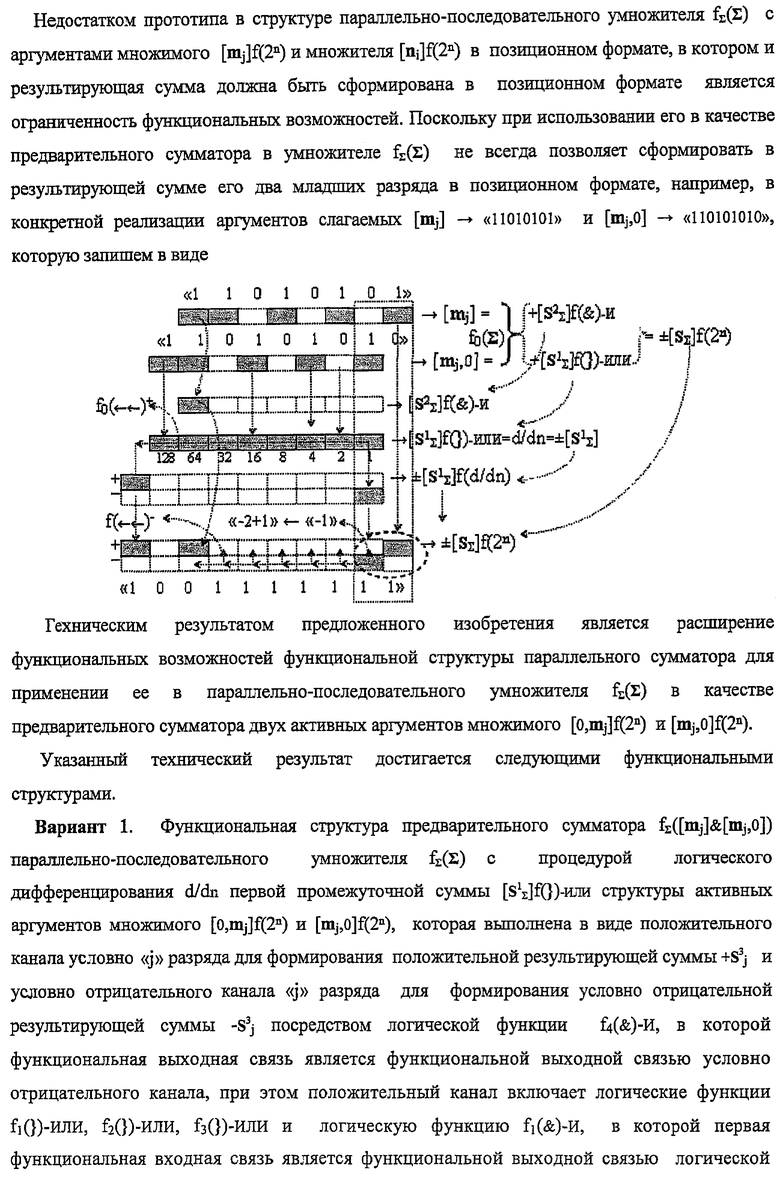

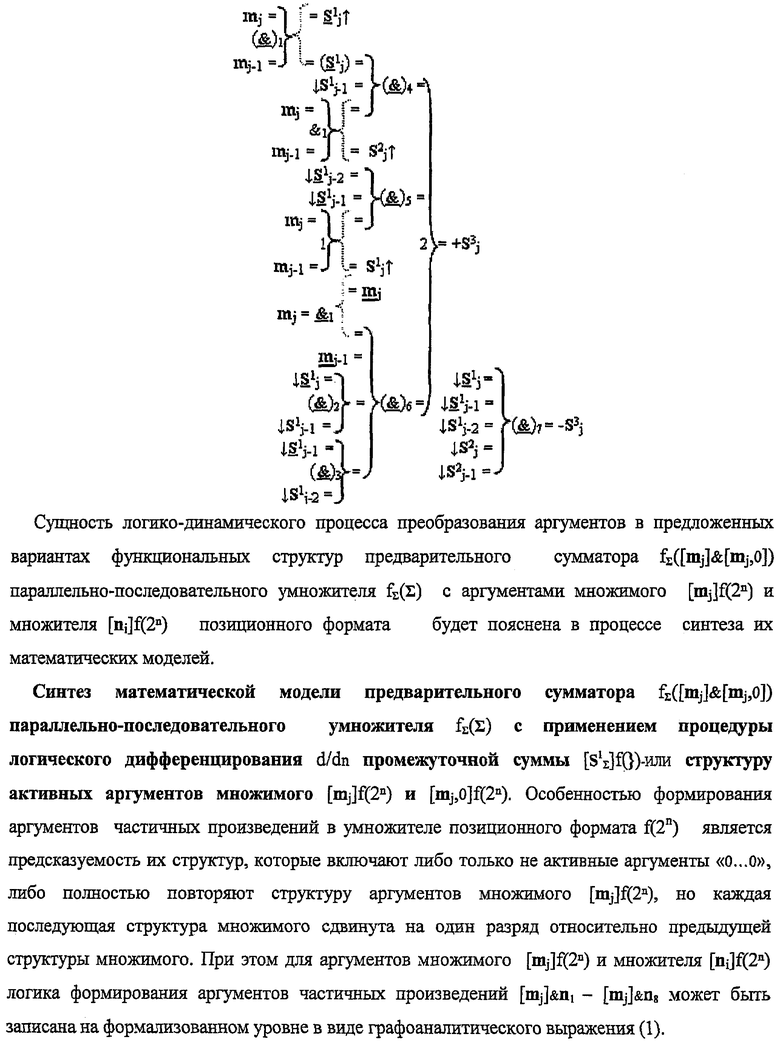

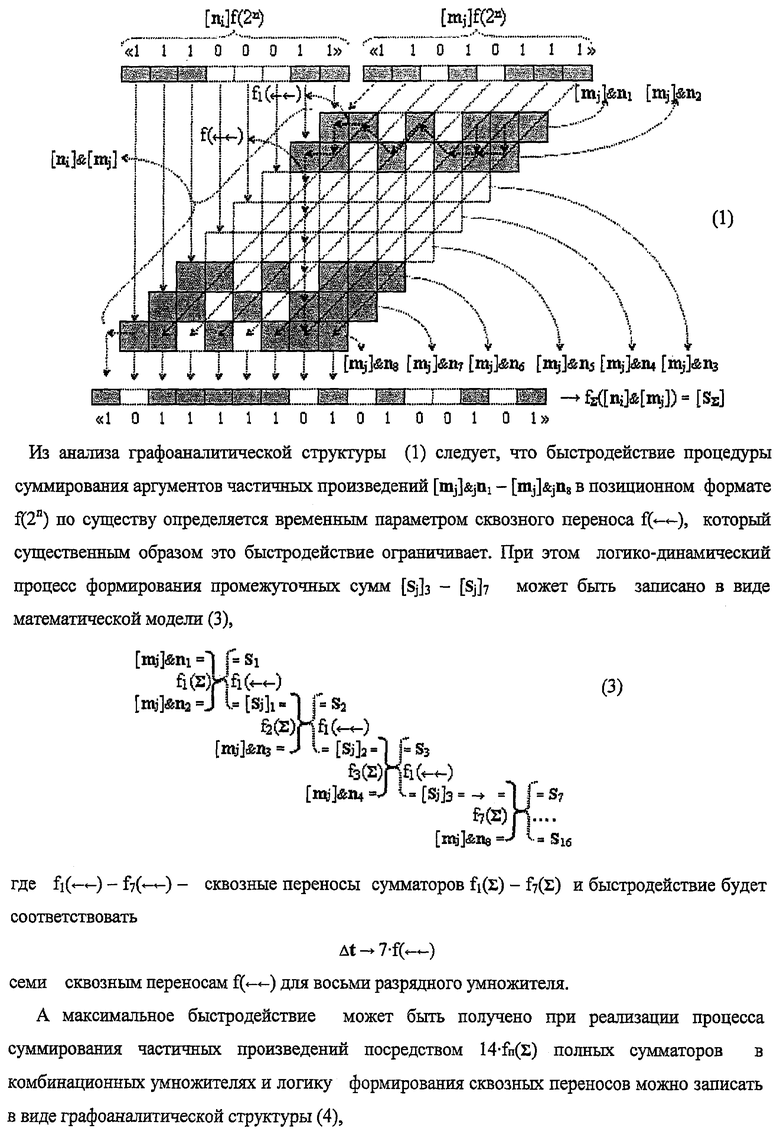

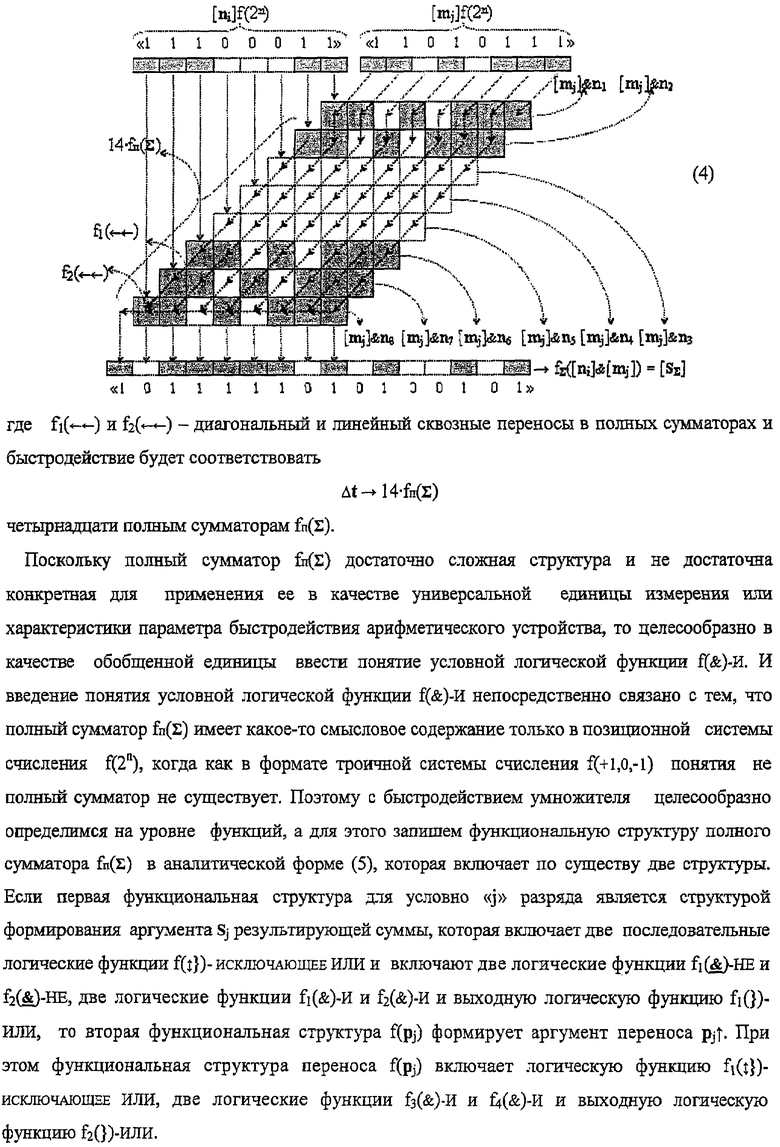

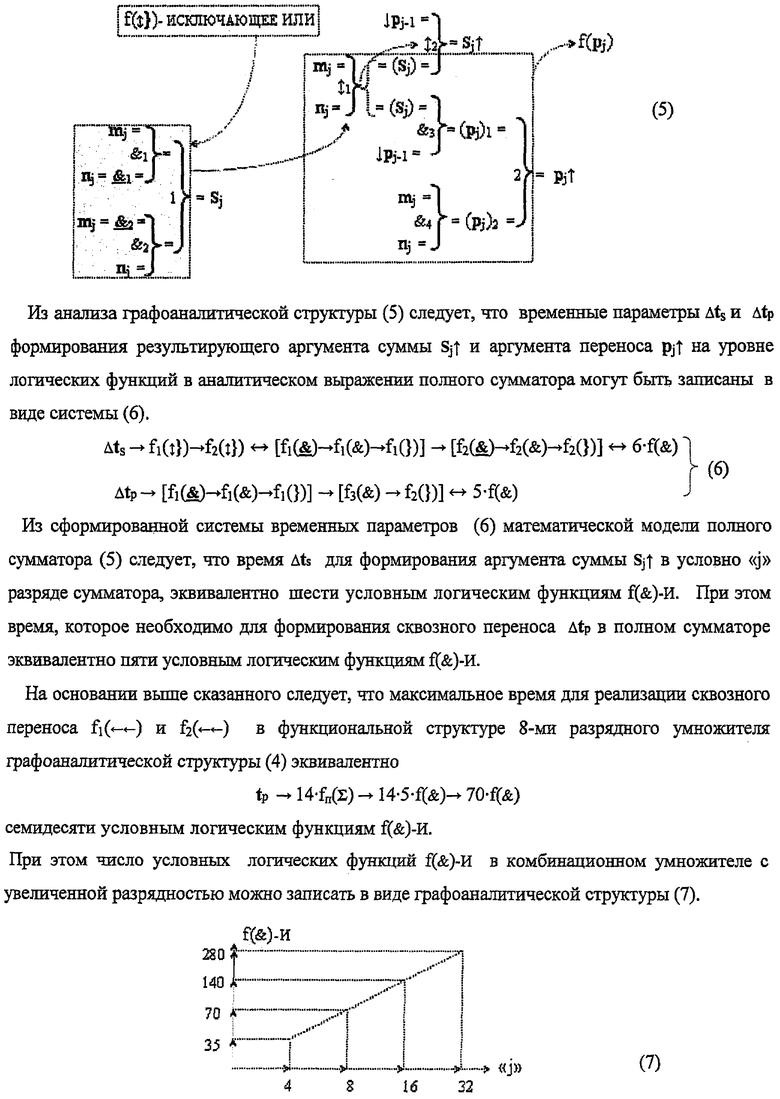

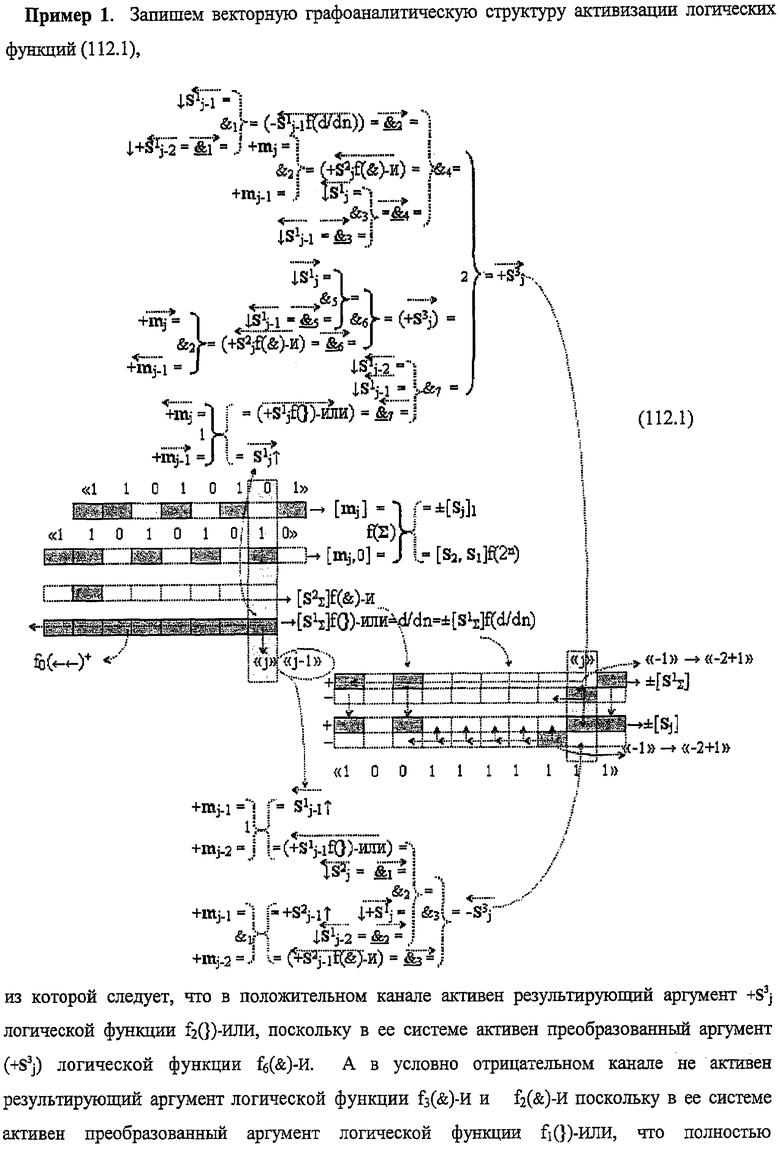

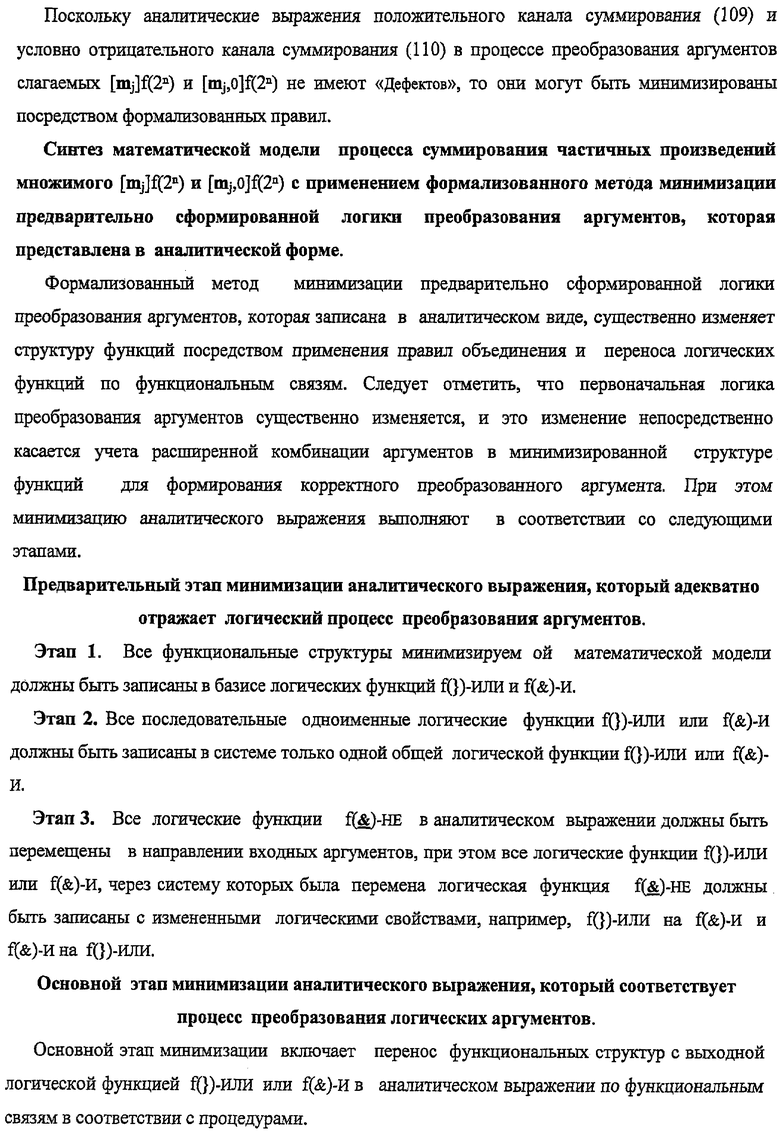

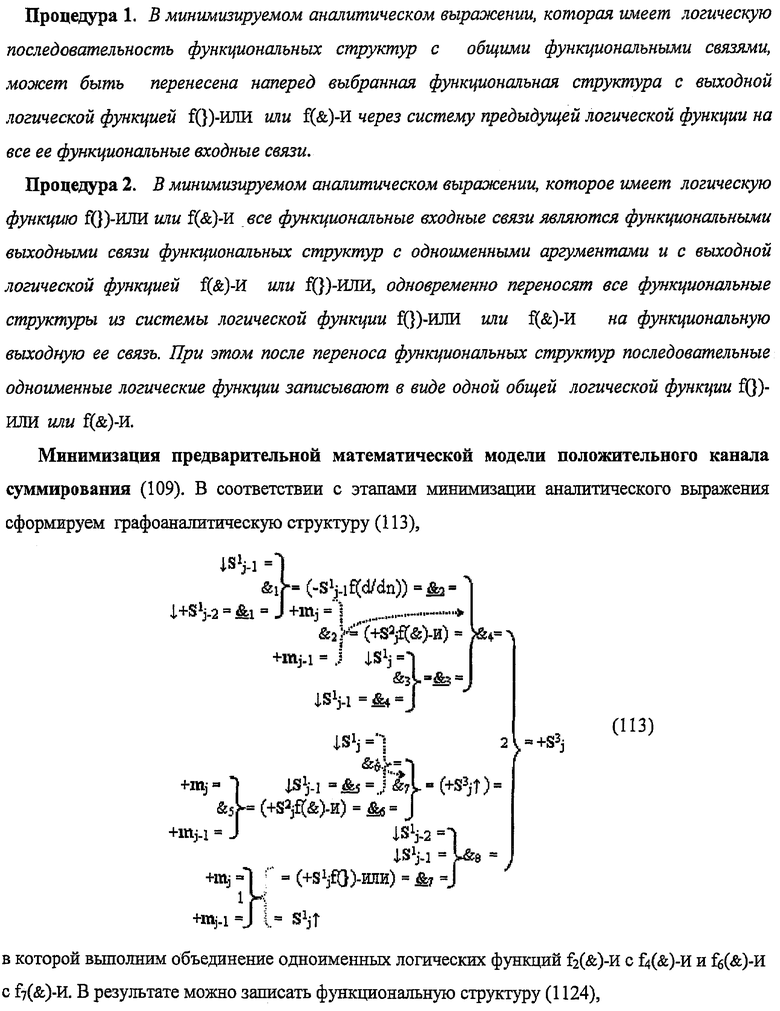

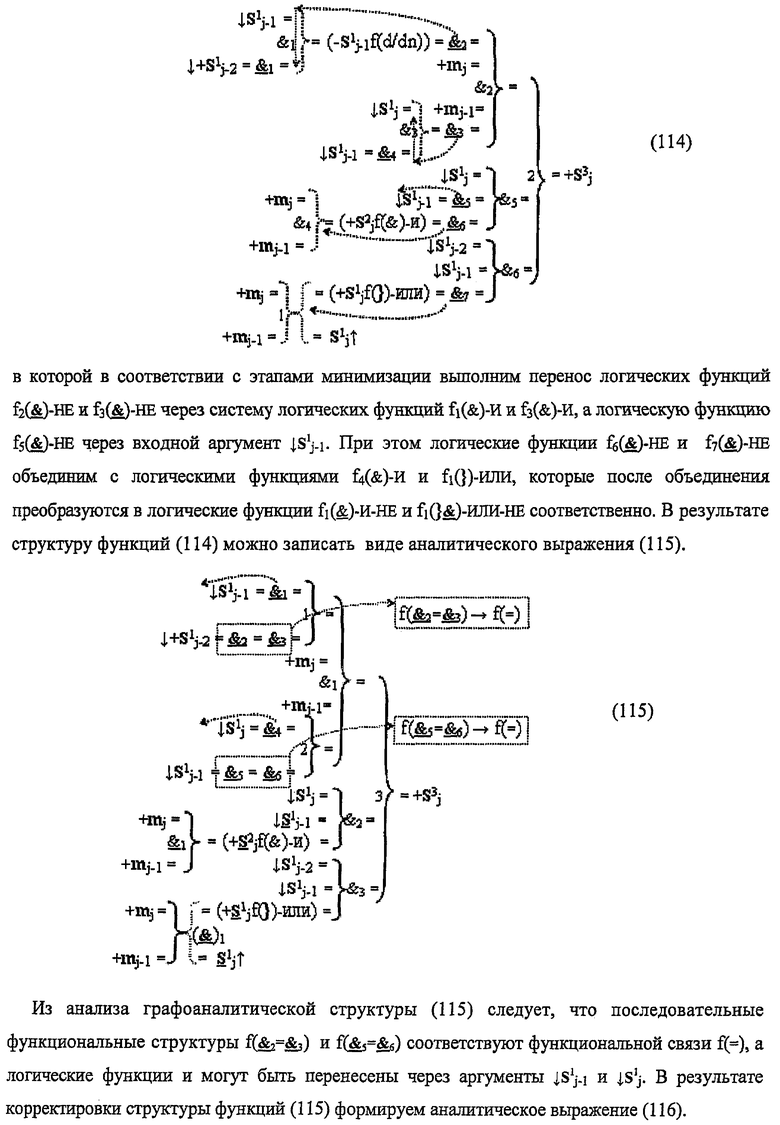

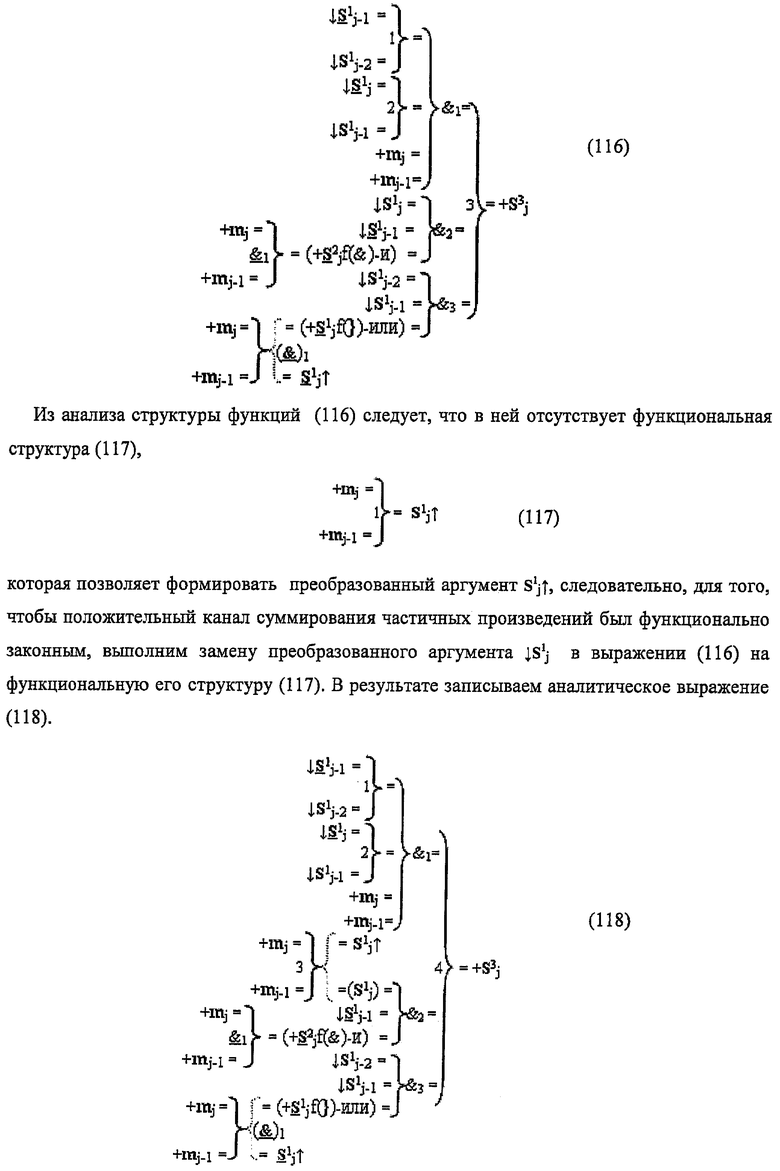

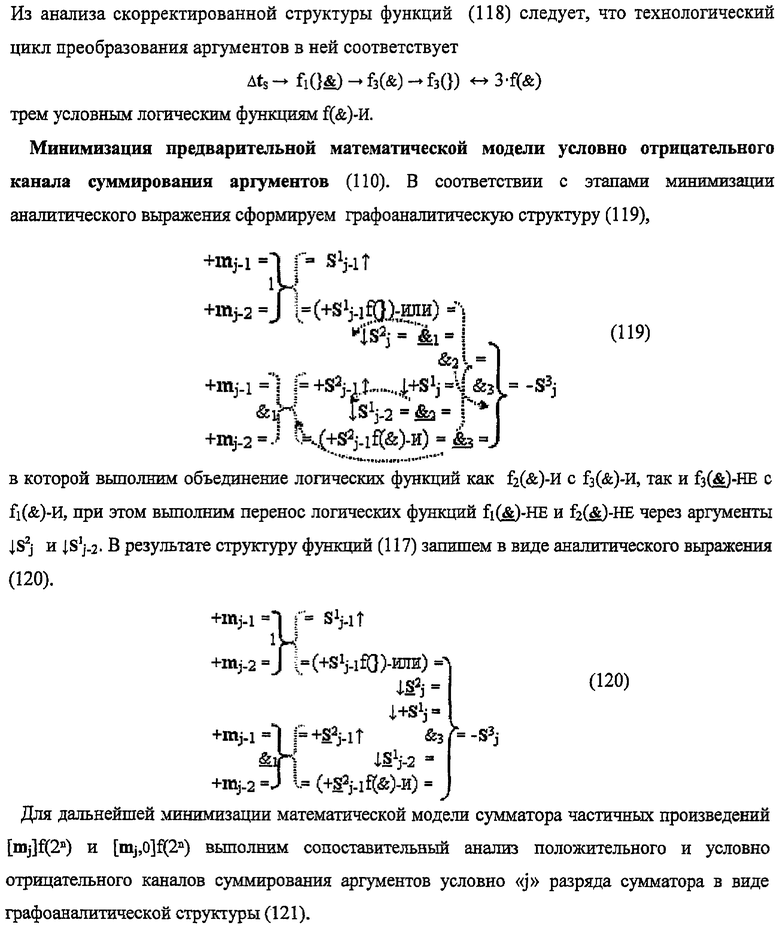

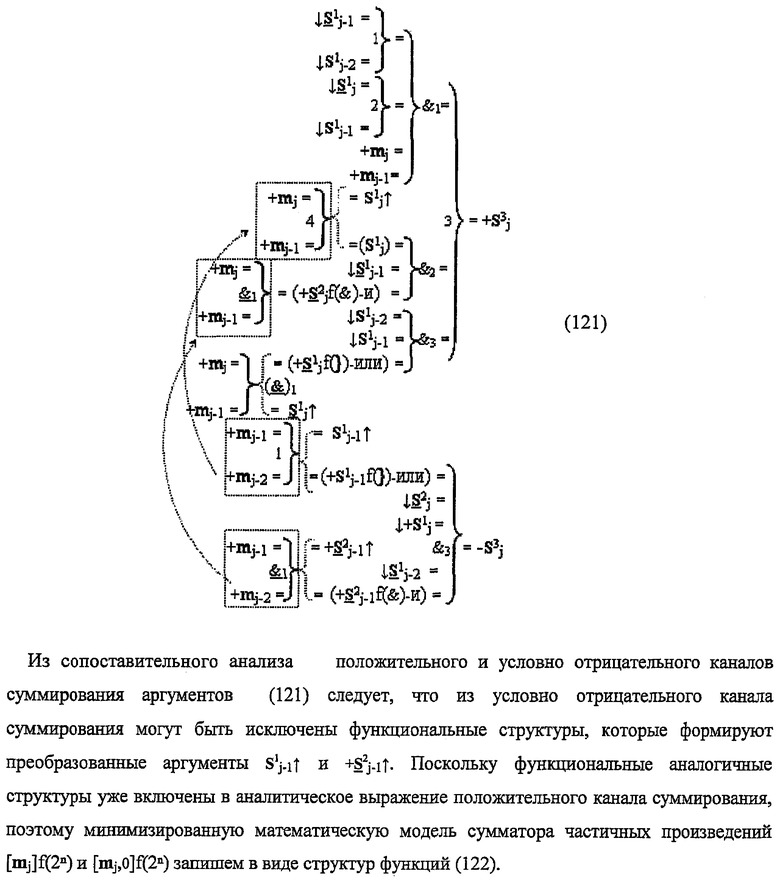

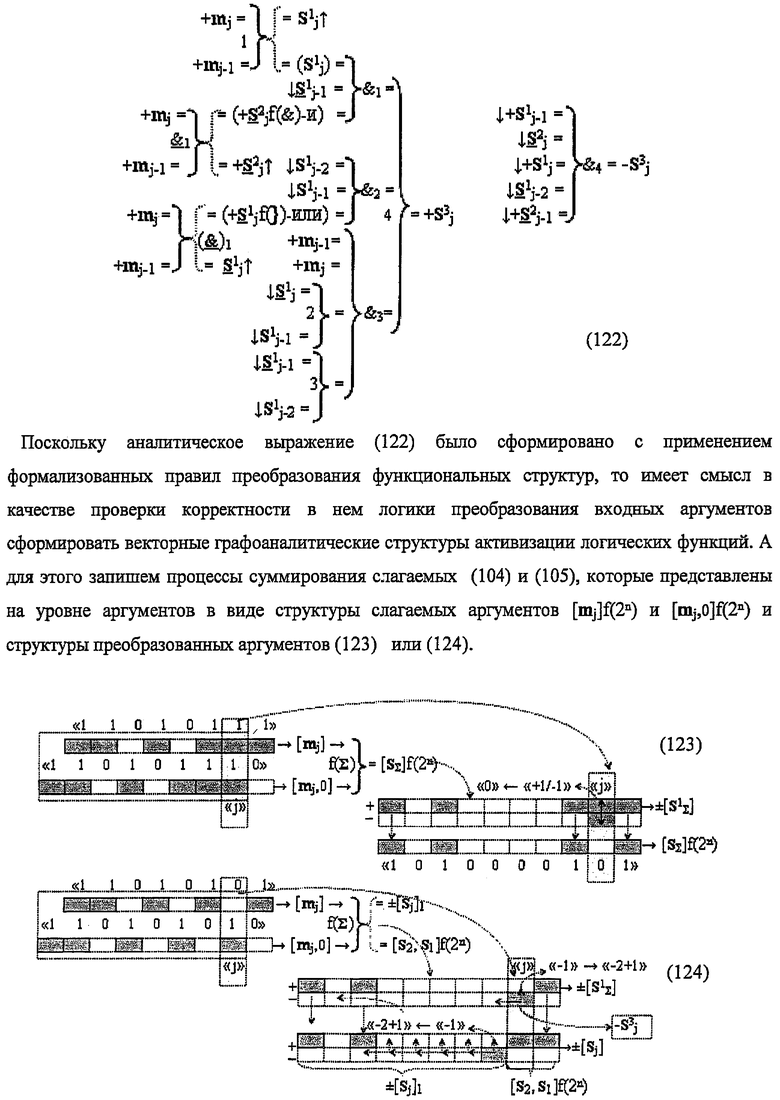

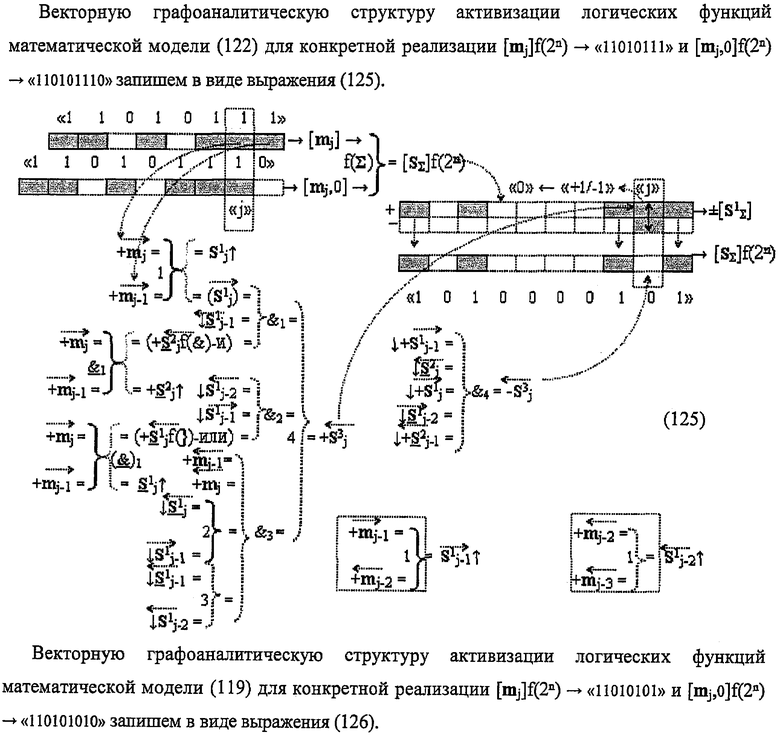

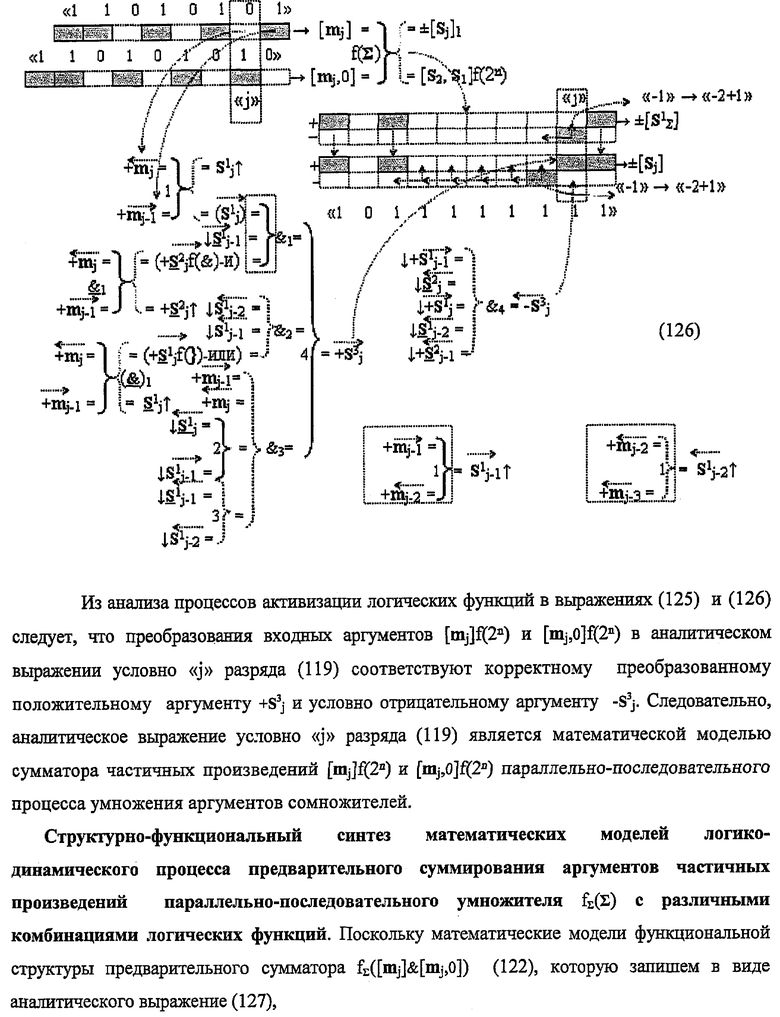

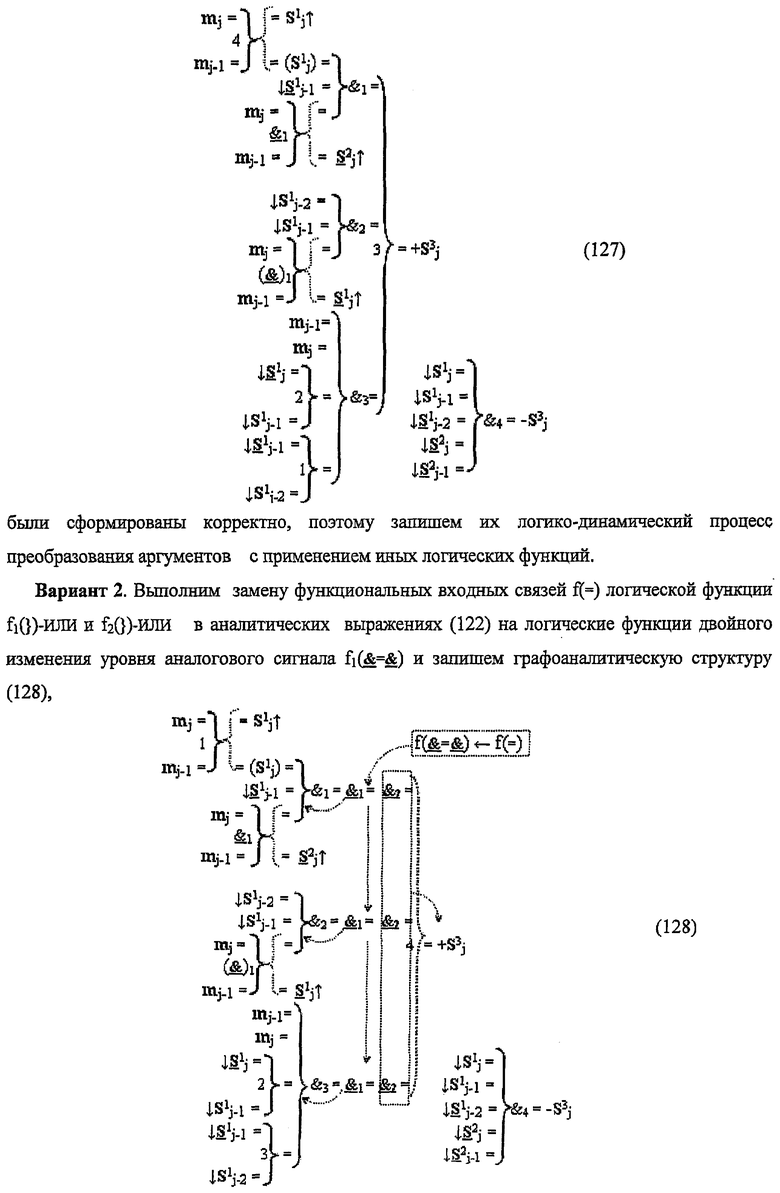

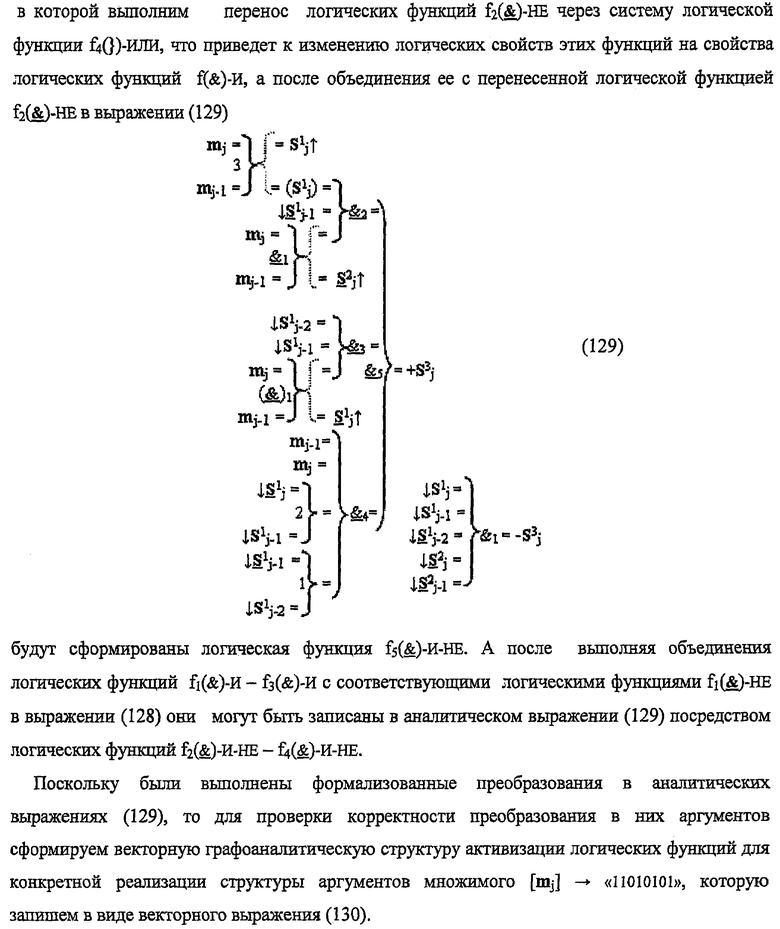

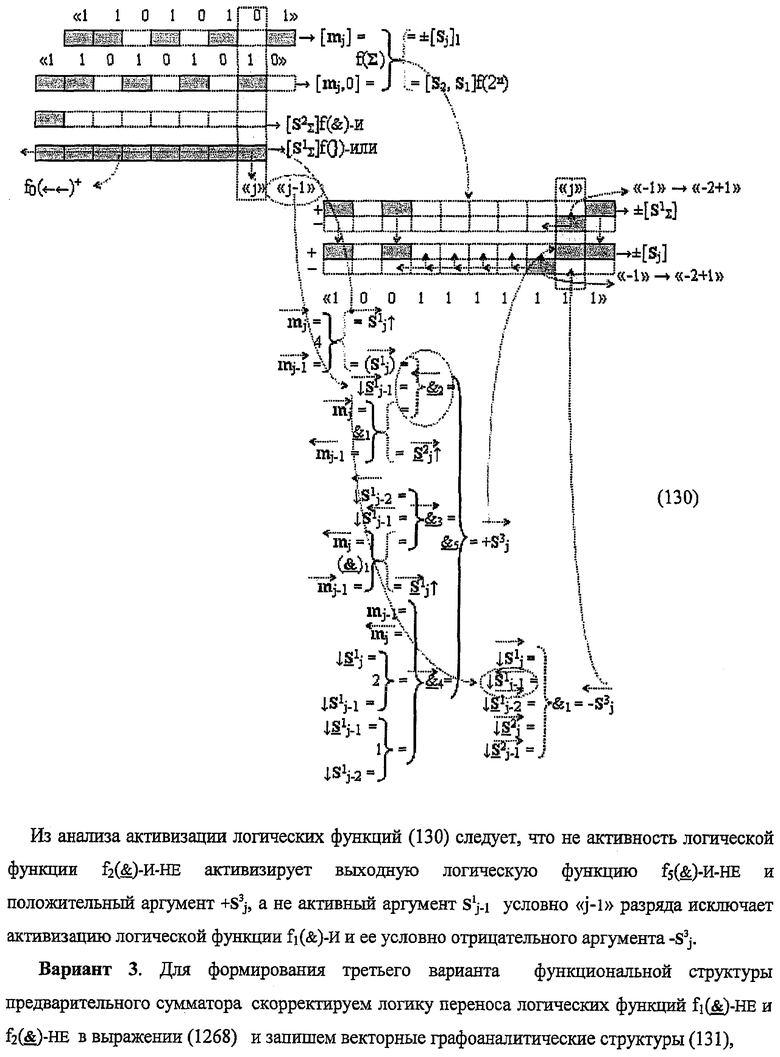

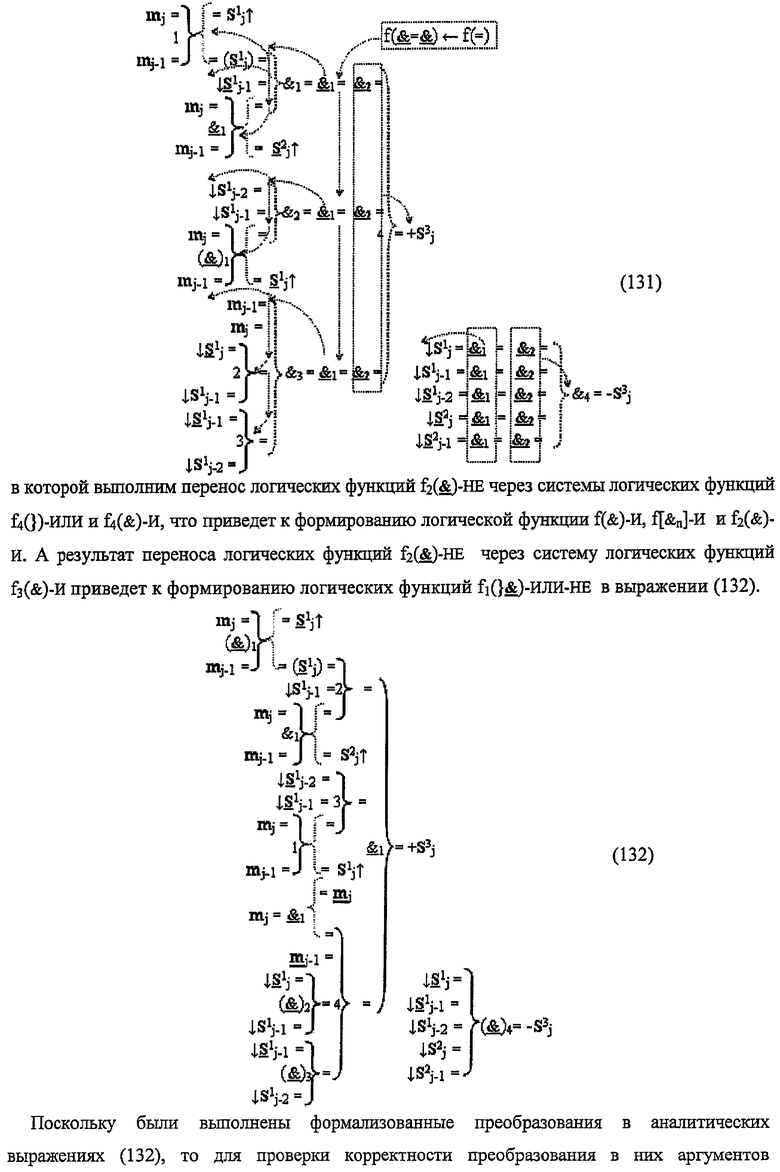

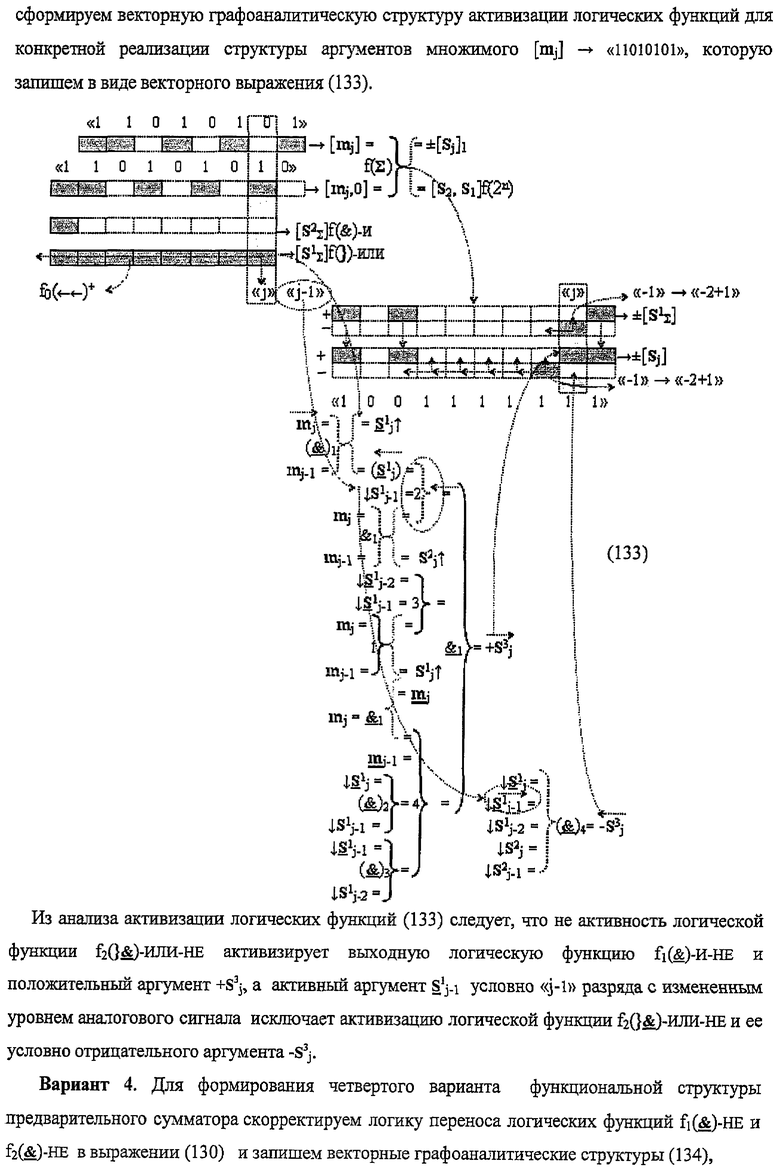

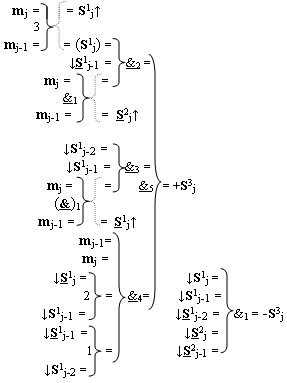

1. Функциональная структура предварительного сумматора fΣ([mj]&[mj,0]) параллельно-последовательного умножителя fΣ(Σ) с процедурой логического дифференцирования d/dn первой промежуточной суммы [S1 Σ]f(})-ИЛИ структуры активных аргументов множимого [0,mj]f(2n) и [mj,0]f(2n), которая выполнена в виде положительного канала условно «j» разряда для формирования положительной результирующей суммы +S3 j и условно отрицательного канала «j» разряда для формирования условно отрицательной результирующей суммы -S3 j посредством логической функции f4(&)-И, в которой функциональная выходная связь является функциональной выходной связью условно отрицательного канала, при этом положительный канал включает логические функции f1(})-ИЛИ, f2(})-ИЛИ, f3(})-ИЛИ и логическую функцию f1(&)-И, в которой первая функциональная входная связь является функциональной выходной связью логической функции f4(})-ИЛИ, в которой первая функциональная входная связь является функциональной входной связью канала для приема аргумента mj условно «j» разряда структуры аргументов множимого, отличающаяся тем, что в положительный канал условно «j» разряда дополнительно введены логические функции f1(&)-И-НЕ, f1(}&)-ИЛИ-НЕ, f2(&)-И и f3(&)-И, при этом функциональные связи логических функций в структуре предварительного сумматора выполнены в соответствии с математической моделью вида

где  - логическая функция f1(&)-И;

- логическая функция f1(&)-И;  - логическая функция f1(})-ИЛИ;

- логическая функция f1(})-ИЛИ;

- логическая функция f1(&)-И-НЕ;

- логическая функция f1(&)-И-НЕ;  - логическая функция f1(}&)-ИЛИ-НЕ;

- логическая функция f1(}&)-ИЛИ-НЕ;

«=&1=» - логическая функция f1(&)-НЕ изменения активности входных аналоговых сигналов.

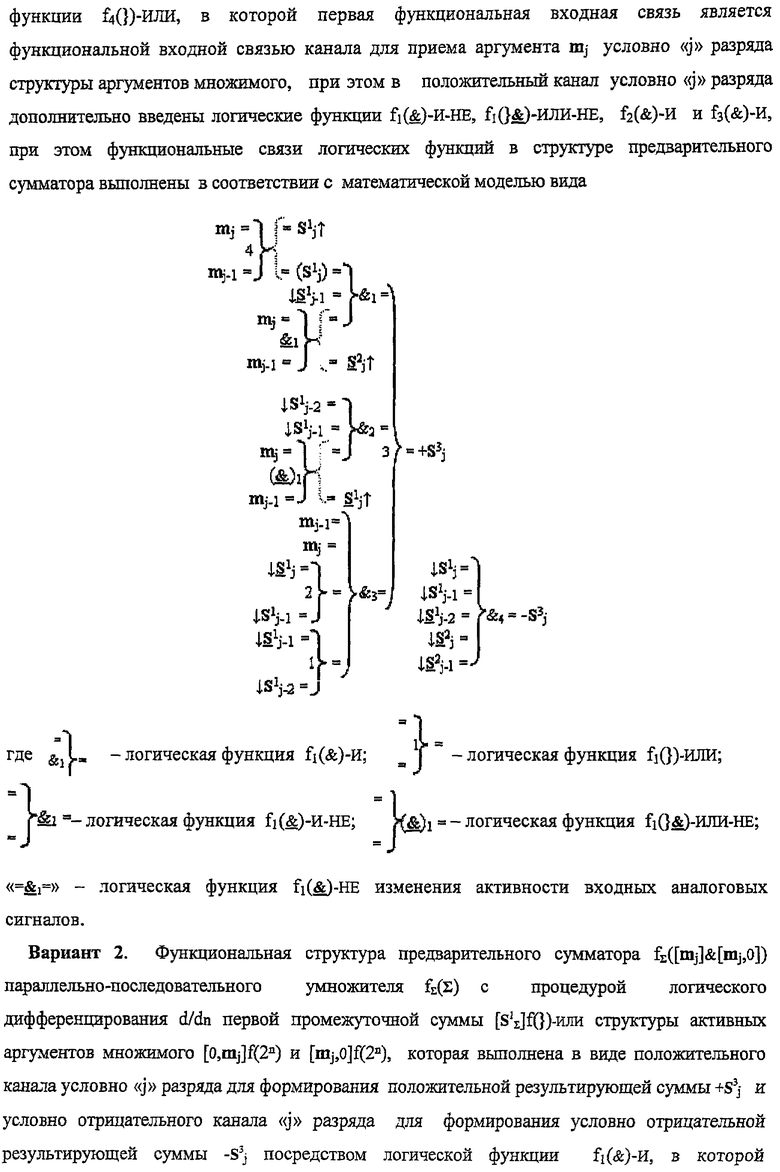

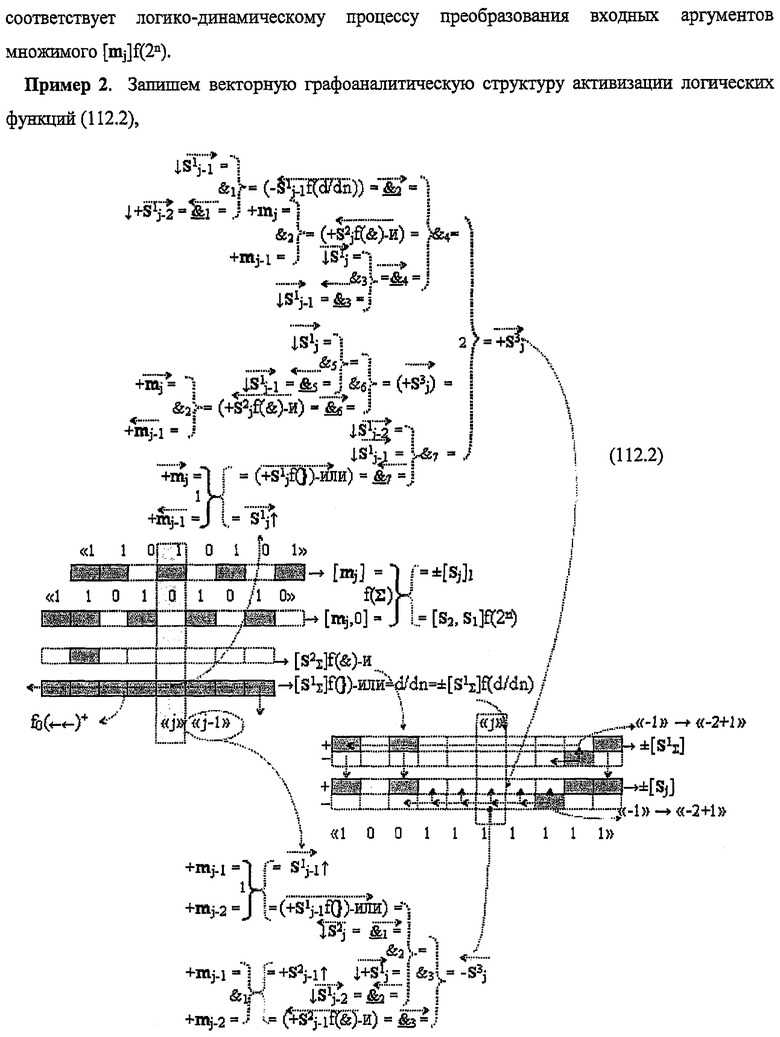

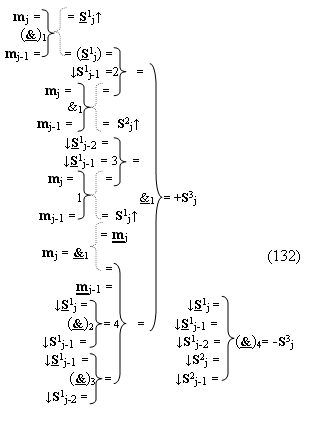

2. Функциональная структура предварительного сумматора fΣ([mj]&[mj,0]) параллельно-последовательного умножителя fΣ(Σ) с процедурой логического дифференцирования d/dn первой промежуточной суммы [S1 Σ]f(})-ИЛИ структуры активных аргументов множимого [0,mj]f(2n) и [mj,0]f(2n), которая выполнена в виде положительного канала условно «j» разряда для формирования положительной результирующей суммы +S3 j и условно отрицательного канала «j» разряда для формирования условно отрицательной результирующей суммы -S3 j посредством логической функции f1(&)-И, в которой функциональная выходная связь является функциональной выходной связью условно отрицательного канала, при этом положительный канал включает логические функции f1(})-ИЛИ, f2(})-ИЛИ и логическую функцию f3(})-ИЛИ, в которой первая функциональная входная связь является функциональной входной связью канала для приема аргумента mj условно «j» разряда структуры аргументов множимого, отличающаяся тем, что в положительный канал условно «j» разряда дополнительно введены логические функции f1(&)-И-НЕ, f1(}&)-ИЛИ-НЕ, f2(&)-И-НЕ, f3(&)-И-НЕ, f4(&)-И-НЕ и f5(&)-И-НЕ, при этом функциональные связи логических функций в структуре предварительного сумматора выполнены в соответствии с математической моделью вида

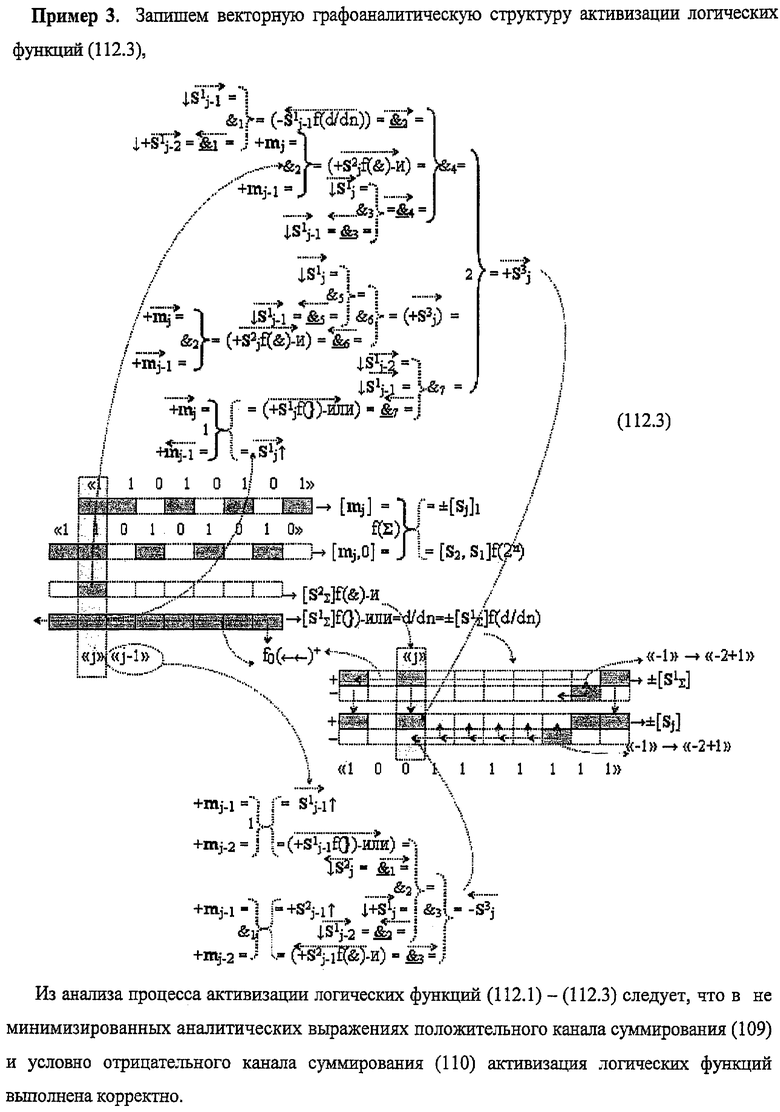

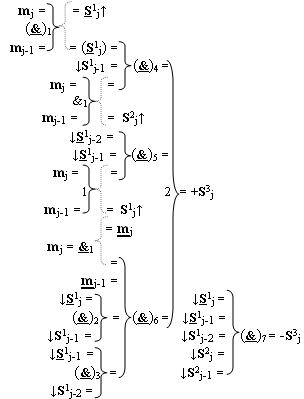

3. Функциональная структура предварительного сумматора fΣ([mj]&[mj,0]) параллельно-последовательного умножителя fΣ(Σ) с процедурой логического дифференцирования d/dn первой промежуточной суммы [S1 Σ]f(})-ИЛИ структуры активных аргументов множимого [0,mj]f(2n) и [mj,0]f(2n), которая выполнена в виде положительного канала условно «j» разряда для формирования положительной результирующей суммы +S3 j и условно отрицательного канала «j» разряда для формирования условно отрицательной результирующей суммы -S3 j, при этом положительный канал включает логические функции f1(&)-И, f2(})-ИЛИ, f3(})-ИЛИ, f4(})-ИЛИ и логические функции f1(})-ИЛИ и f1(&)-НЕ, в которых функциональная входная связь является функциональной входной связью канала для приема аргумента mj условно «j» разряда структуры аргументов множимого, отличающаяся тем, что в положительный канал условно «j» разряда дополнительно введены логические функции f1(}&)-ИЛИ-НЕ, f2(}&)-ИЛИ-НЕ, f3(}&)-ИЛИ-НЕ и f1(&)-И-НЕ, а в условно отрицательный канал введена логическая функция f4(}&)-ИЛИ-НЕ, при этом функциональные связи логических функций в структуре предварительного сумматора выполнены в соответствии с математической моделью вида

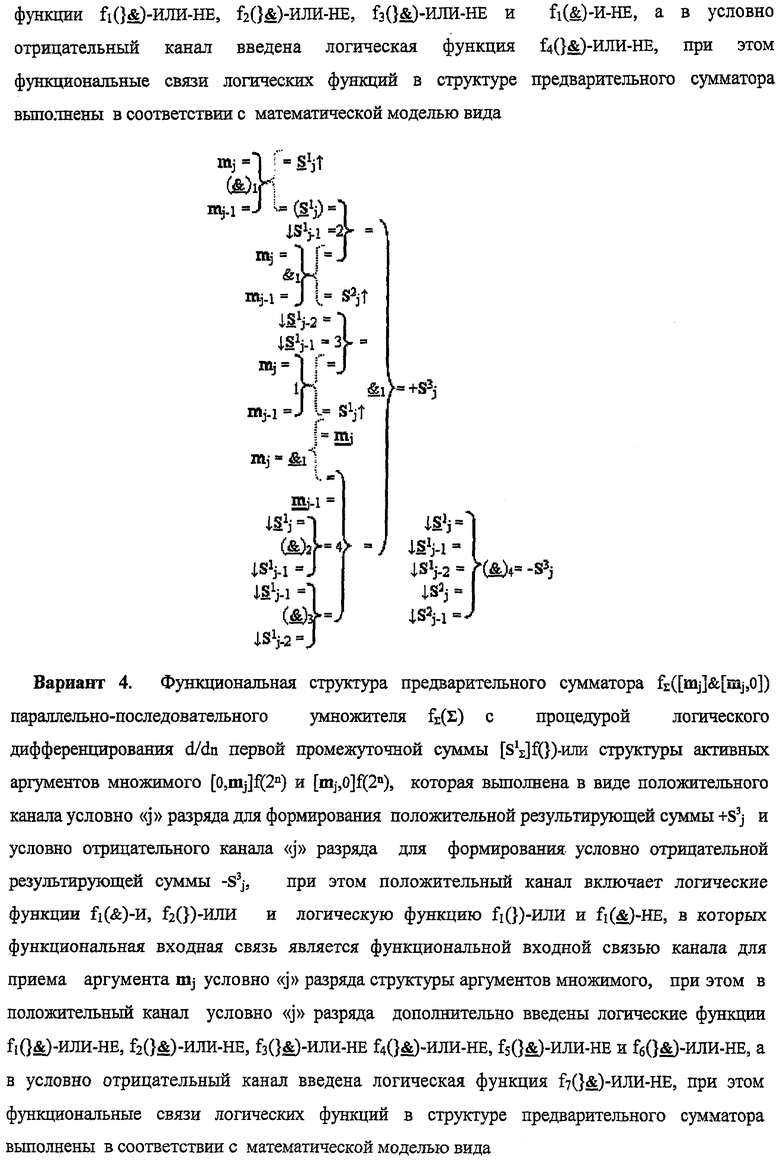

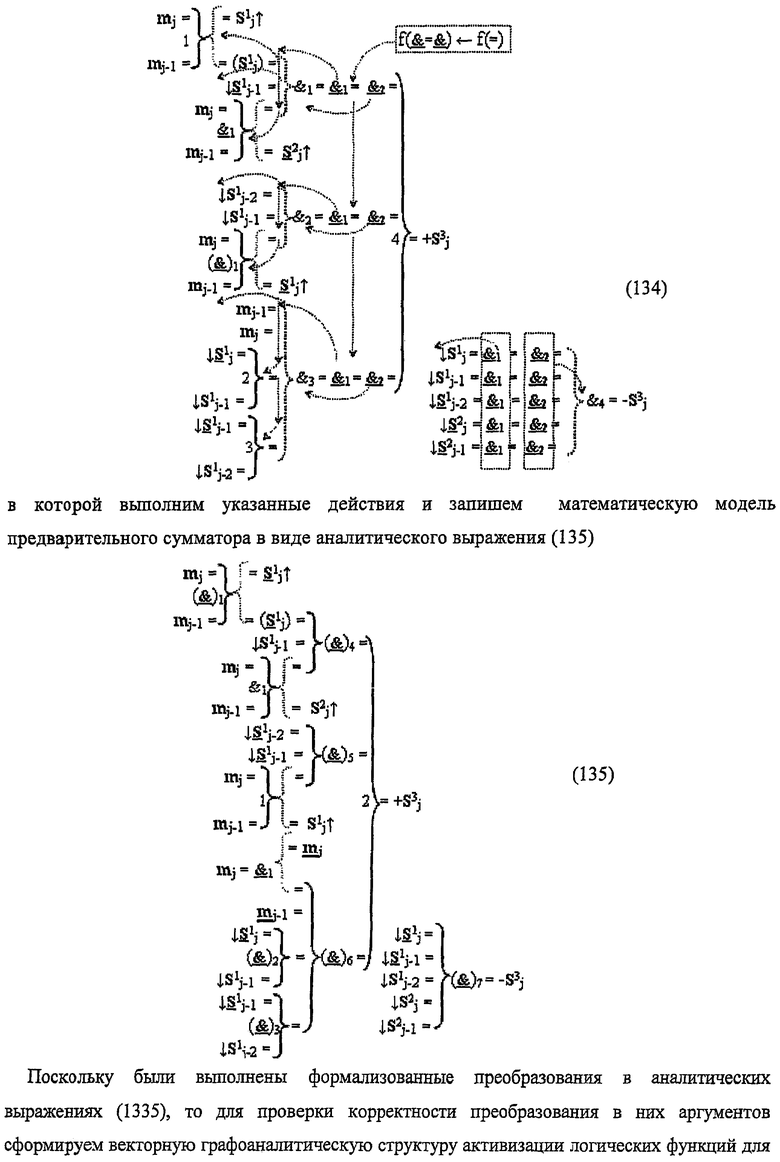

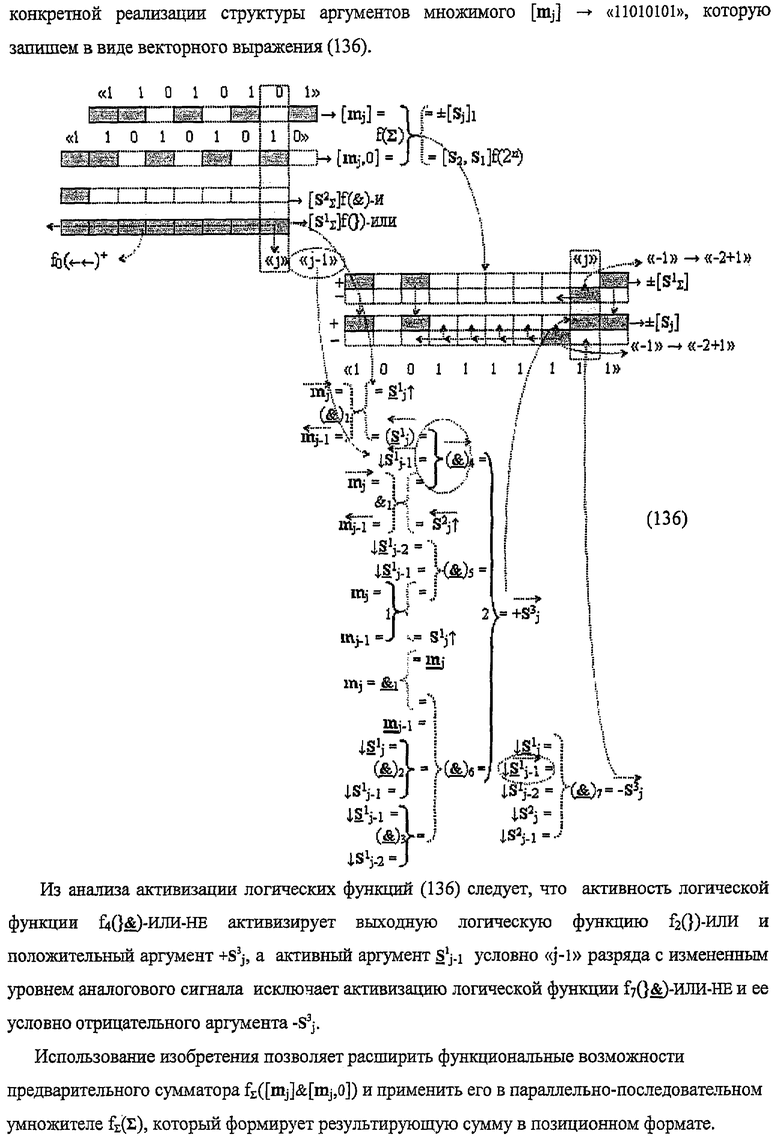

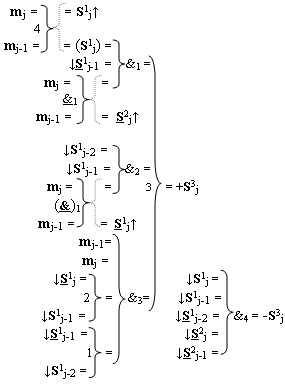

4. Функциональная структура предварительного сумматора fΣ([mj]&[mj,0]) параллельно-последовательного умножителя fΣ(Σ) с процедурой логического дифференцирования d/dn первой промежуточной суммы [S1 Σ]f(})-ИЛИ структуры активных аргументов множимого [0,mj]f(2n) и [mj,0]f(2n), которая выполнена в виде положительного канала условно «j» разряда для формирования положительной результирующей суммы +S3 j и условно отрицательного канала «j» разряда для формирования условно отрицательной результирующей суммы -S3 j, при этом положительный канал включает логические функции f1(&)-И, f2(})-ИЛИ и логическую функцию f1(})-ИЛИ и f1(&)-НЕ, в которых функциональная входная связь является функциональной входной связью канала для приема аргумента mj условно «j» разряда структуры аргументов множимого, отличающаяся тем, что в положительный канал условно «j» разряда дополнительно введены логические функции f1(}&)-ИЛИ-НЕ, f2(}&)-ИЛИ-НЕ, f3(}&)-ИЛИ-НЕ, f4(}&)-ИЛИ-НЕ, f5(}&)-ИЛИ-НЕ и f6(}&)-ИЛИ-НЕ, а в условно отрицательный канал введена логическая функция f7(}&)-ИЛИ-НЕ, при этом функциональные связи логических функций в структуре предварительного сумматора выполнены в соответствии с математической моделью вида

| УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО ЛОГИЧЕСКОГО СУММИРОВАНИЯ АНАЛОГОВЫХ СИГНАЛОВ СЛАГАЕМЫХ, ЭКВИВАЛЕНТНЫХ ДВОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ | 2006 |

|

RU2363978C2 |

| Устройство для параллельного сложения чисел, представленных в двоичной знакоразрядной системе счисления | 1989 |

|

SU1727120A1 |

| Последовательный сумматор в избыточной двоичной системе счисления | 1988 |

|

SU1619251A1 |

| JP 9016378 A, 17.01.1997 | |||

| JP 1304532 A, 08.12.1989. | |||

Авторы

Даты

2011-07-20—Публикация

2010-03-22—Подача