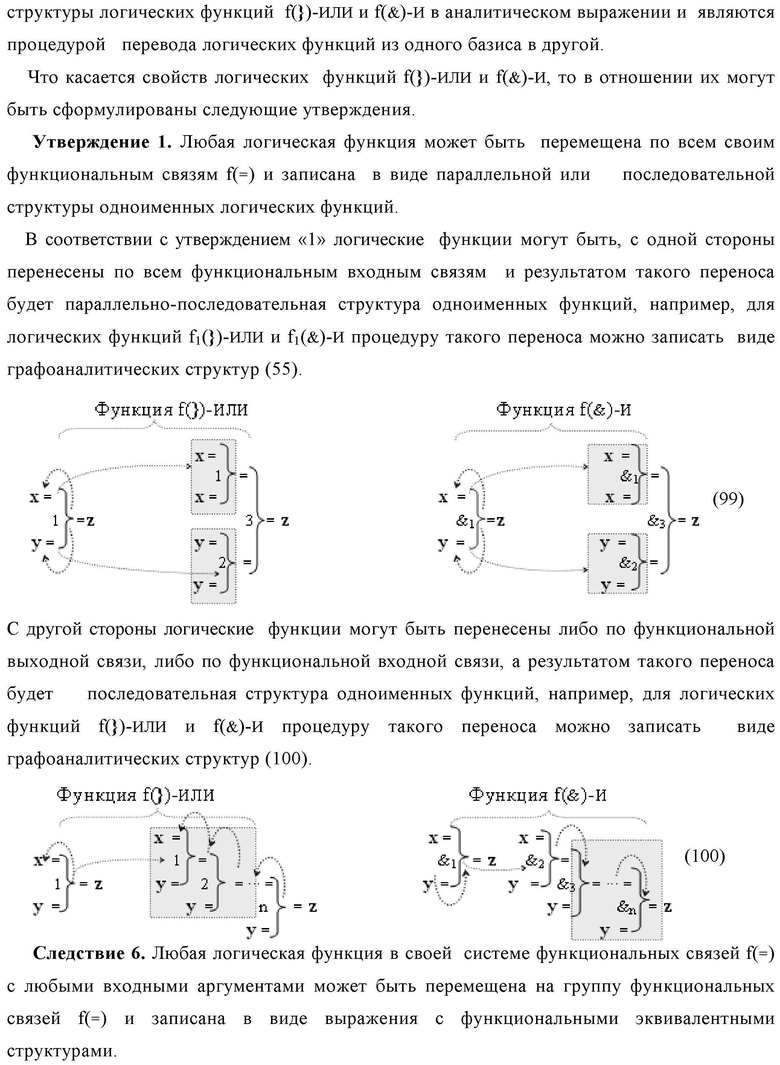

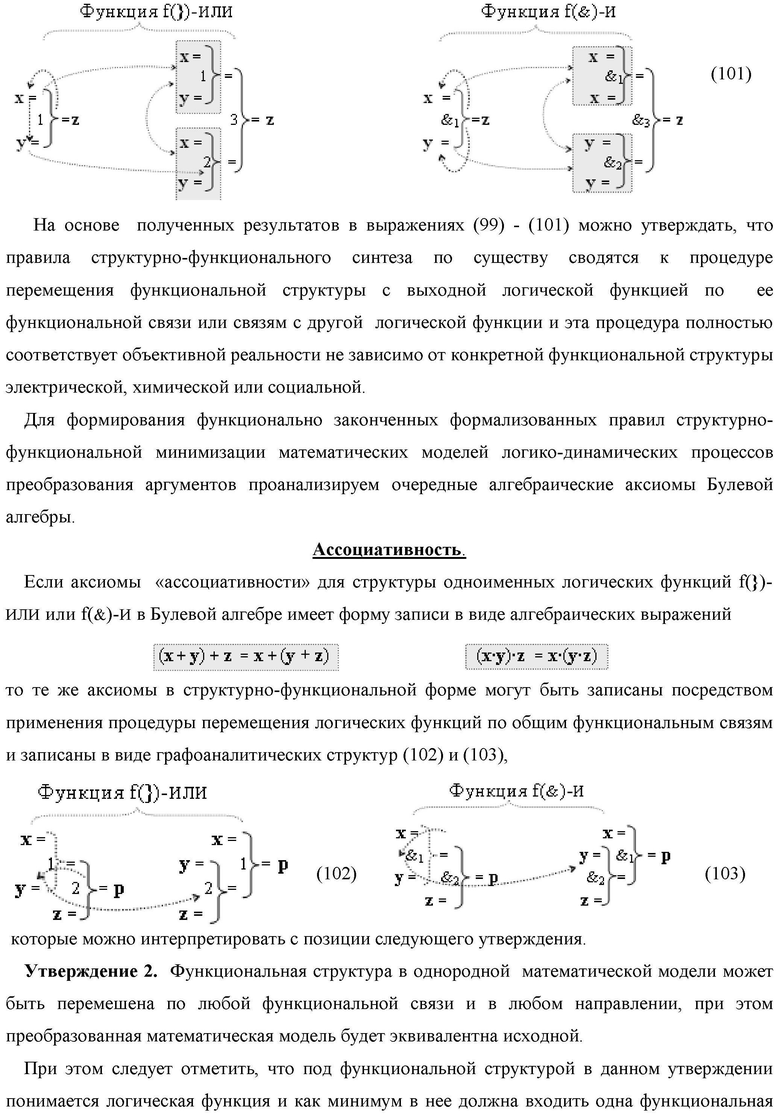

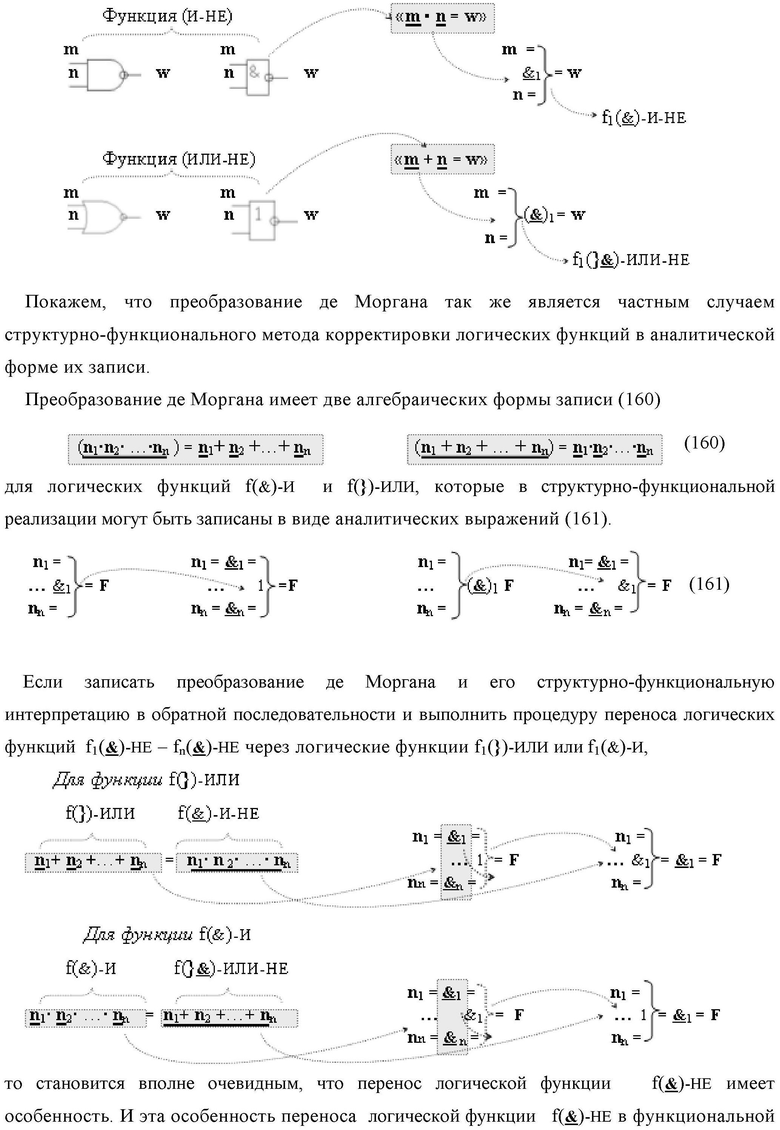

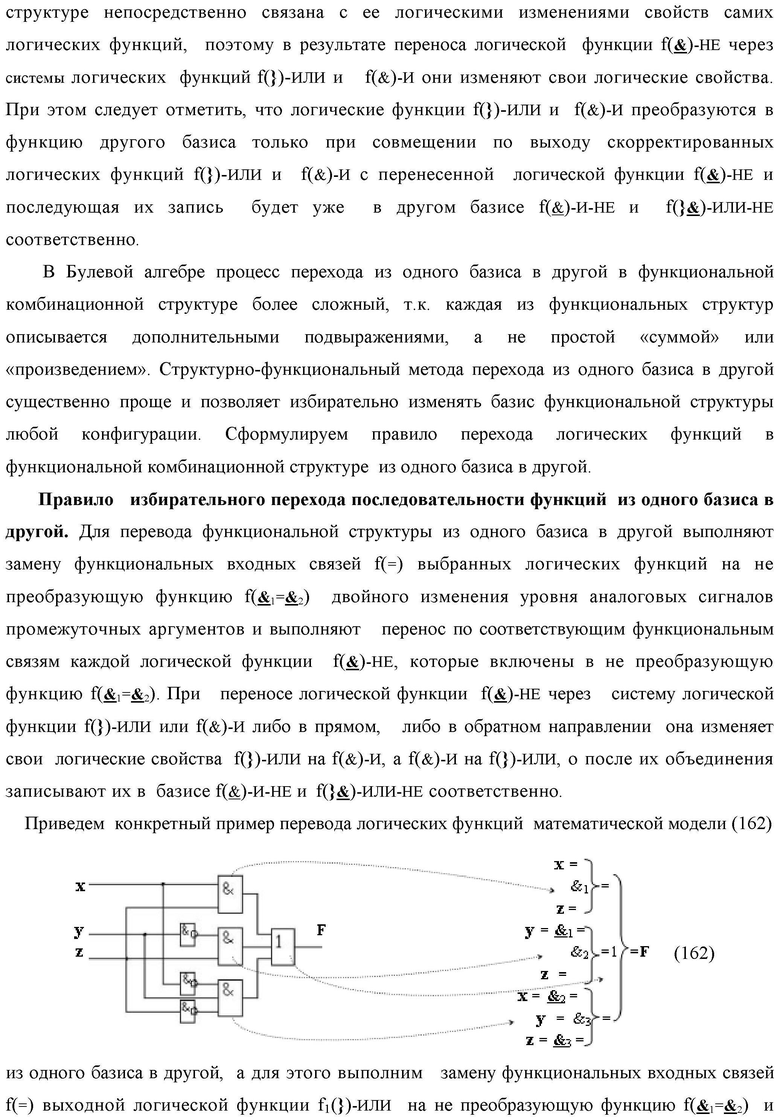

Текст описания приведен в факсимильном виде.

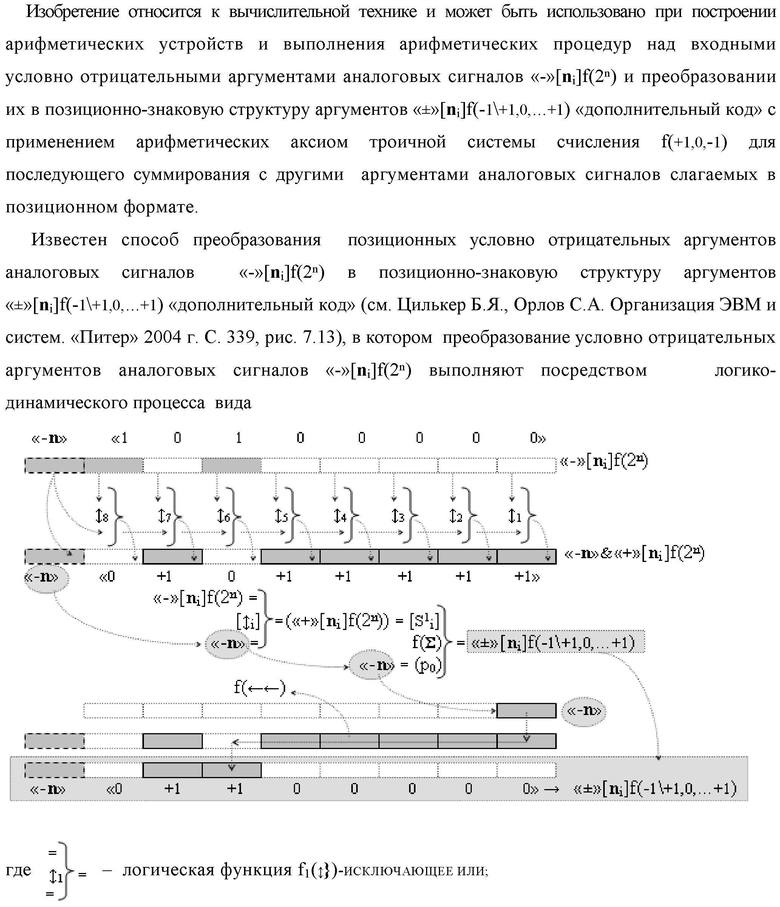

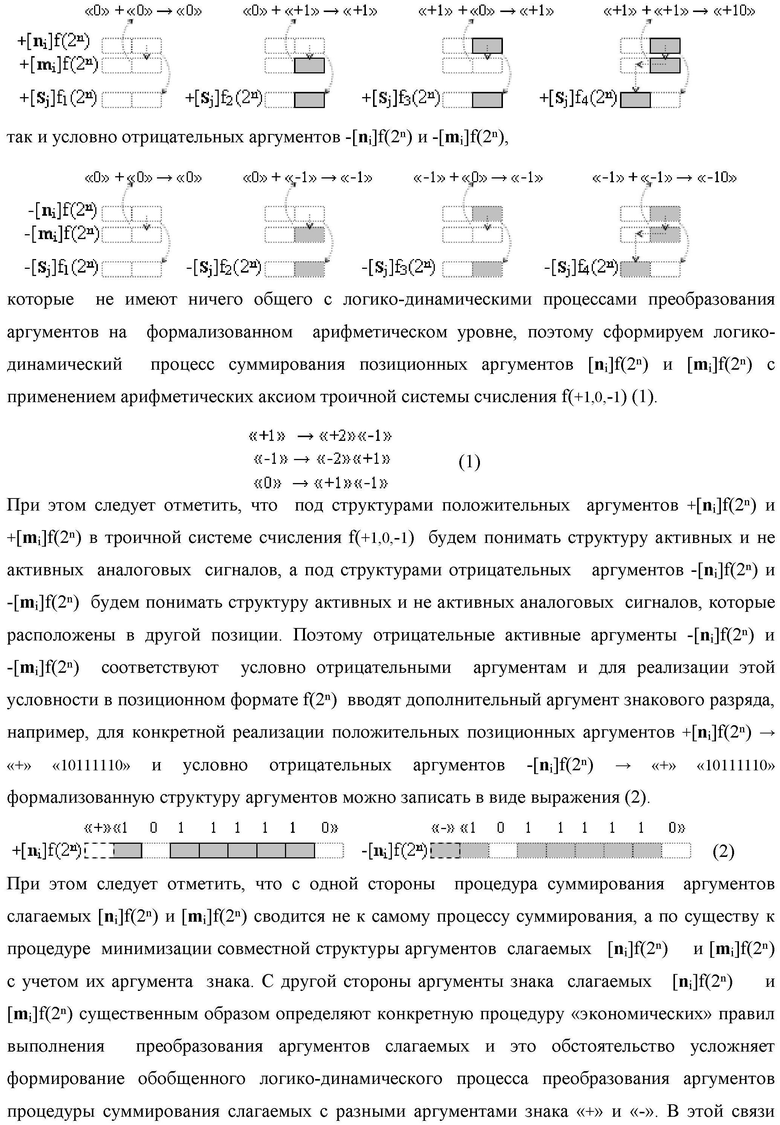

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств и выполнения арифметических процедур над входными условно отрицательными аргументами аналоговых сигналов «-»[ni]f(2n) и преобразовании их в позиционно-знаковую структуру аргументов «±»[ni]f(-1\+1,0,…+1) «дополнительный код» с применением арифметических аксиом троичной системы счисления f(+1,0,-1) для последующего суммирования с другими аргументами аналоговых сигналов слагаемых в позиционном формате. Техническим результатом является повышение быстродействия функциональной структуры преобразователя за счет сокращения технологического цикла формирования результирующей позиционно-знаковой структуры аргументов «±»[ni]f(-1\+1,0,…+1). 2 н.п. ф-лы.

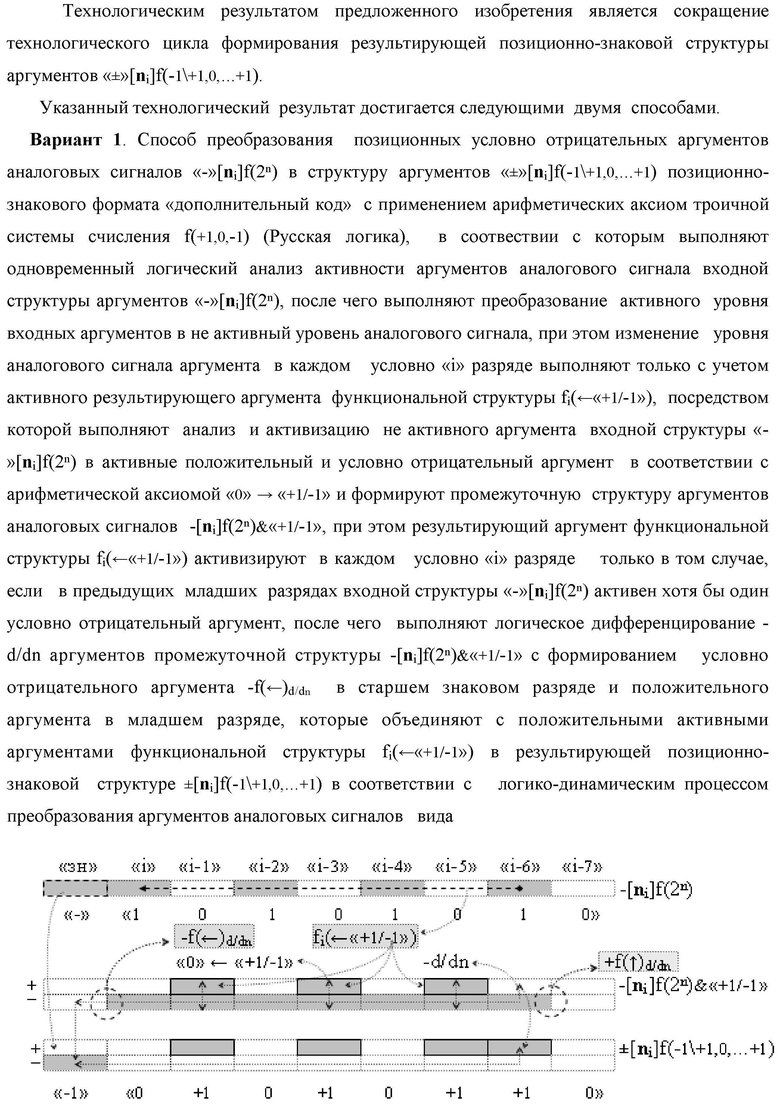

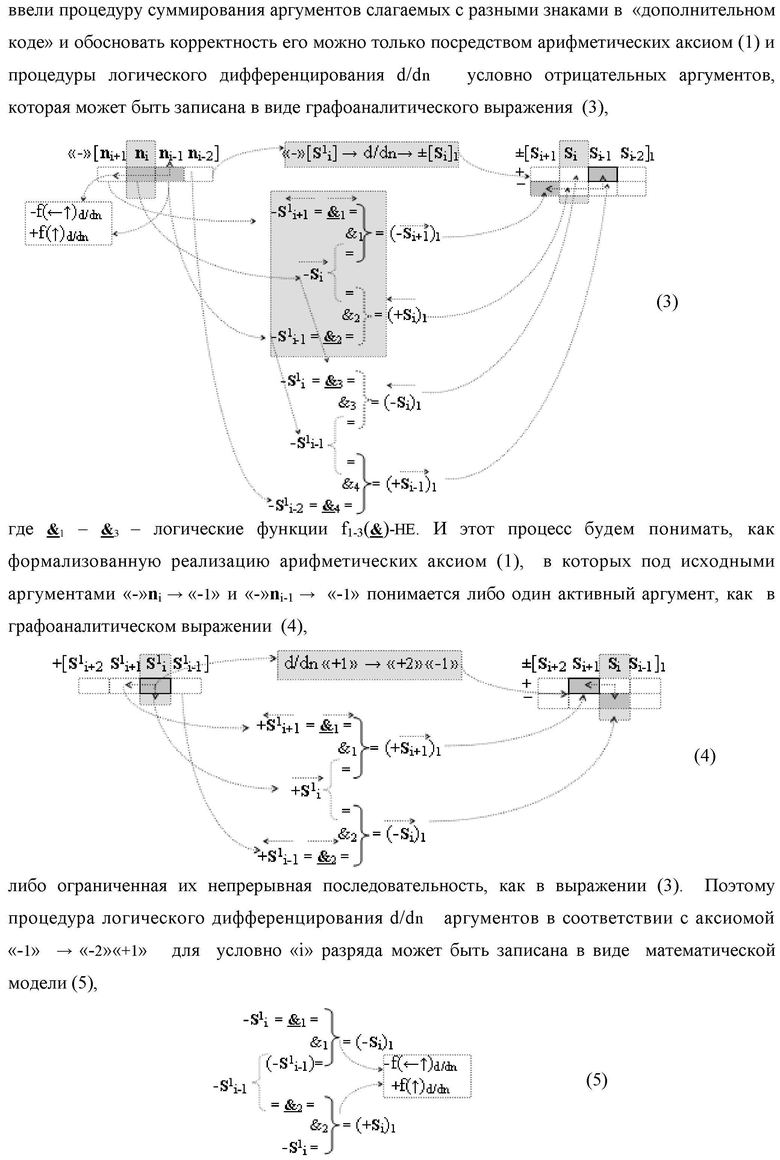

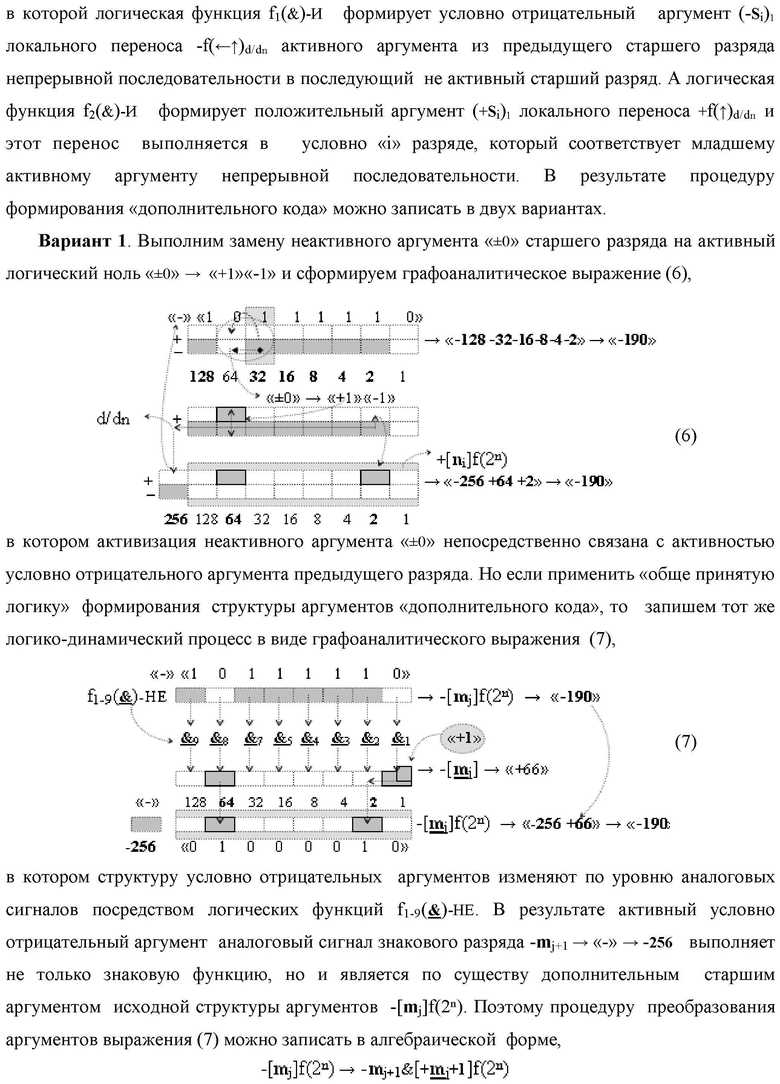

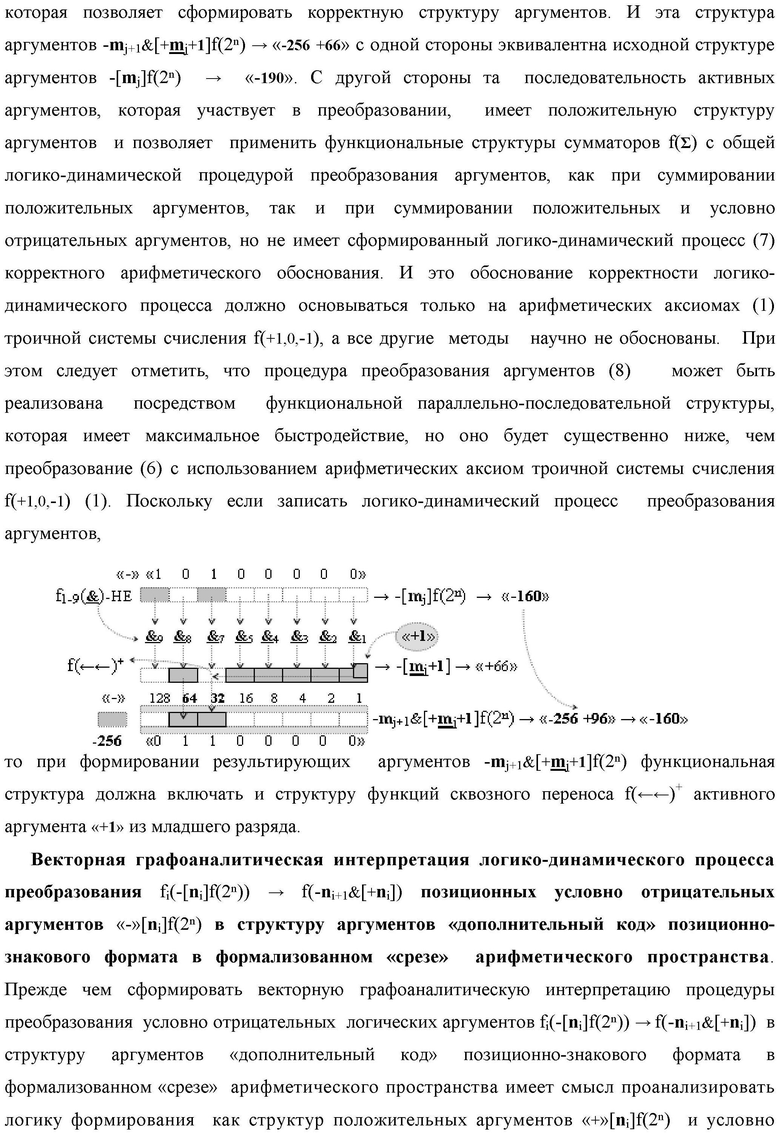

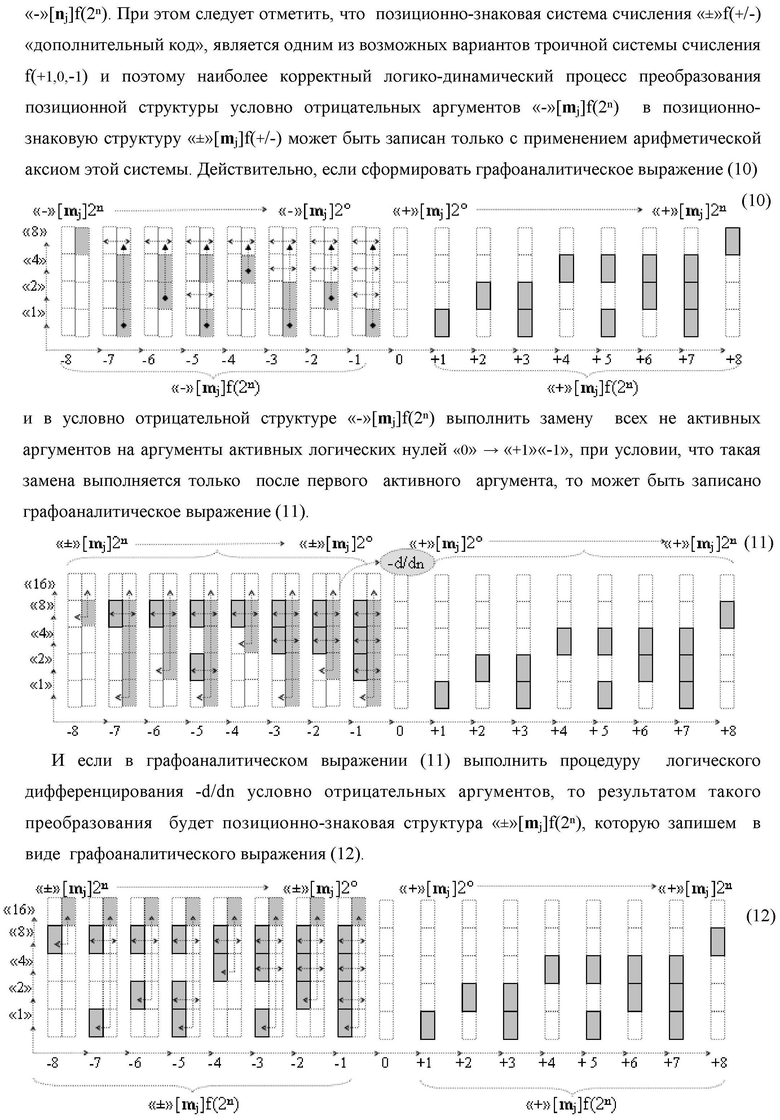

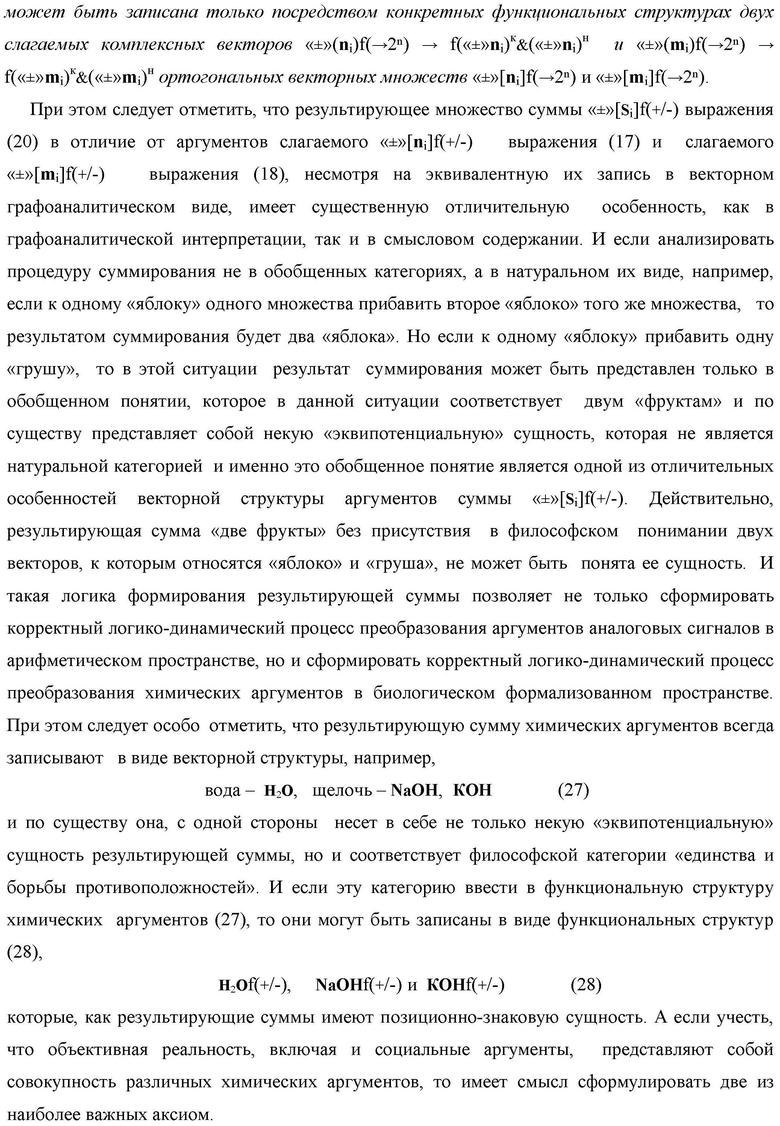

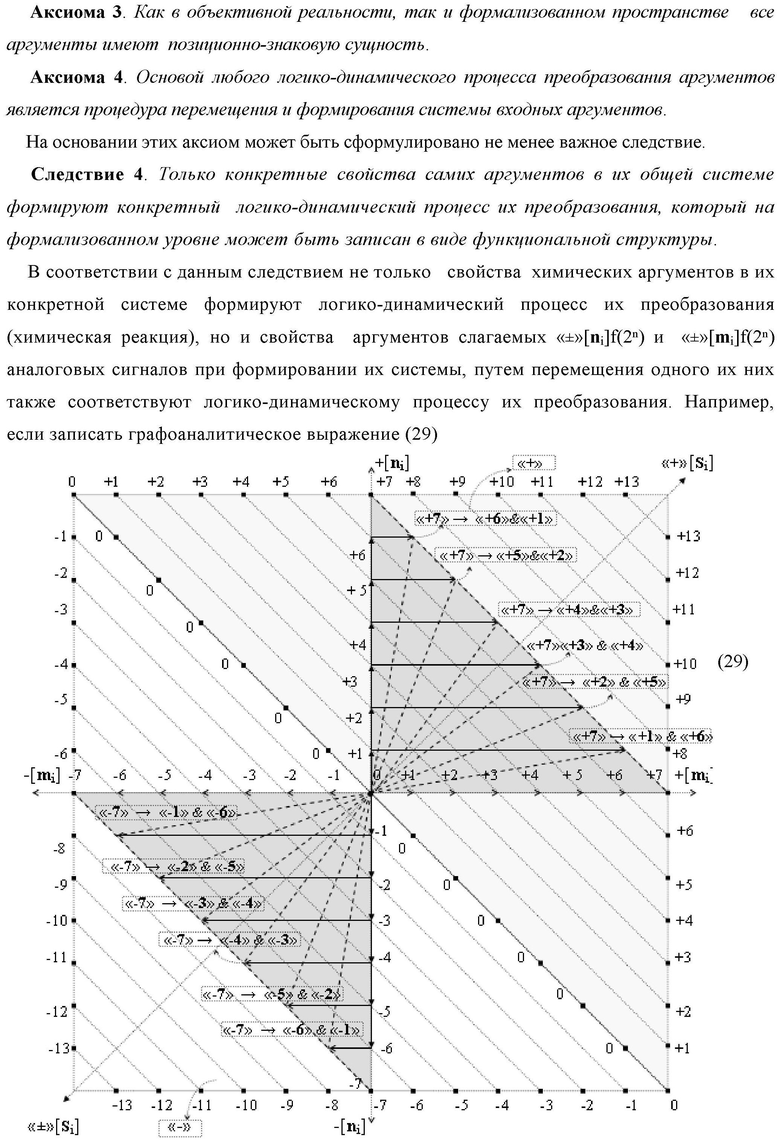

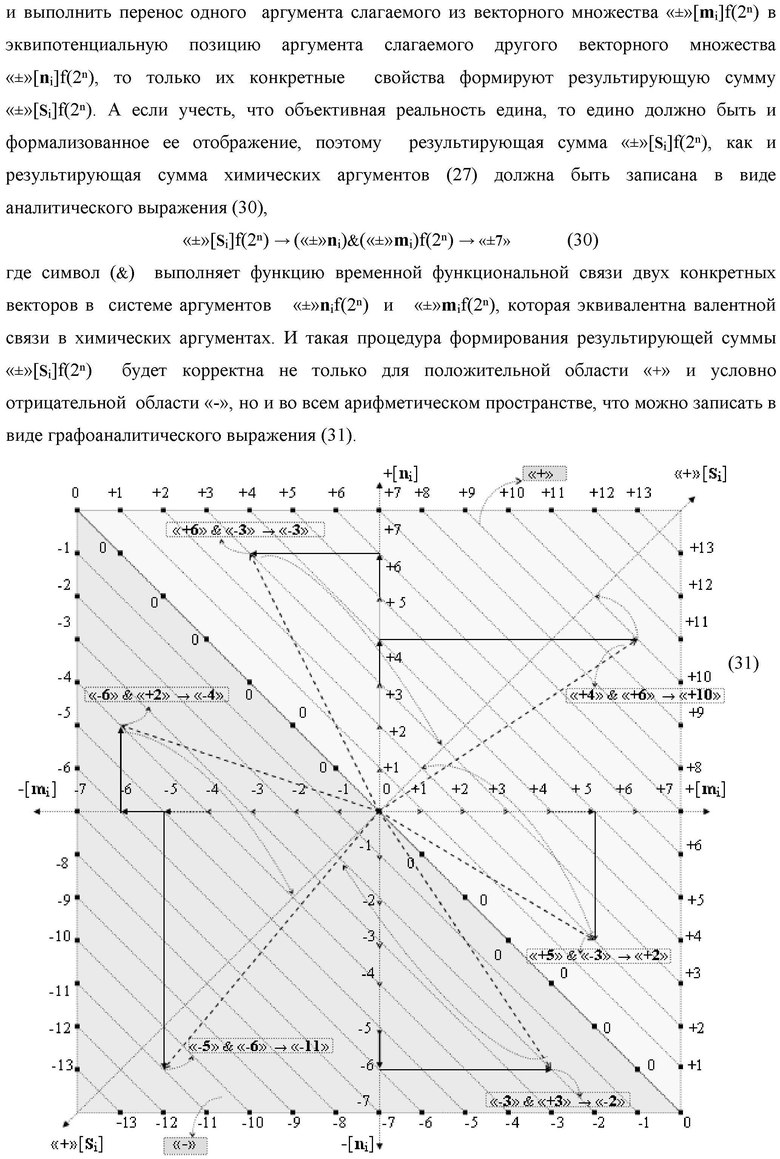

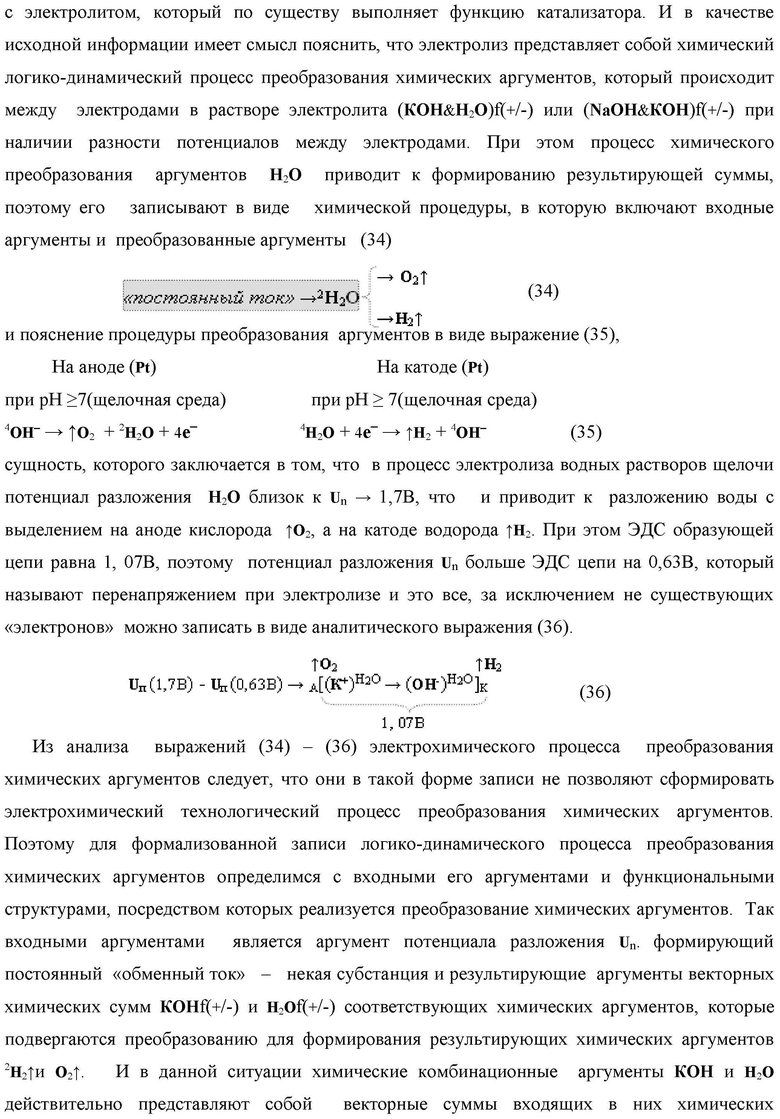

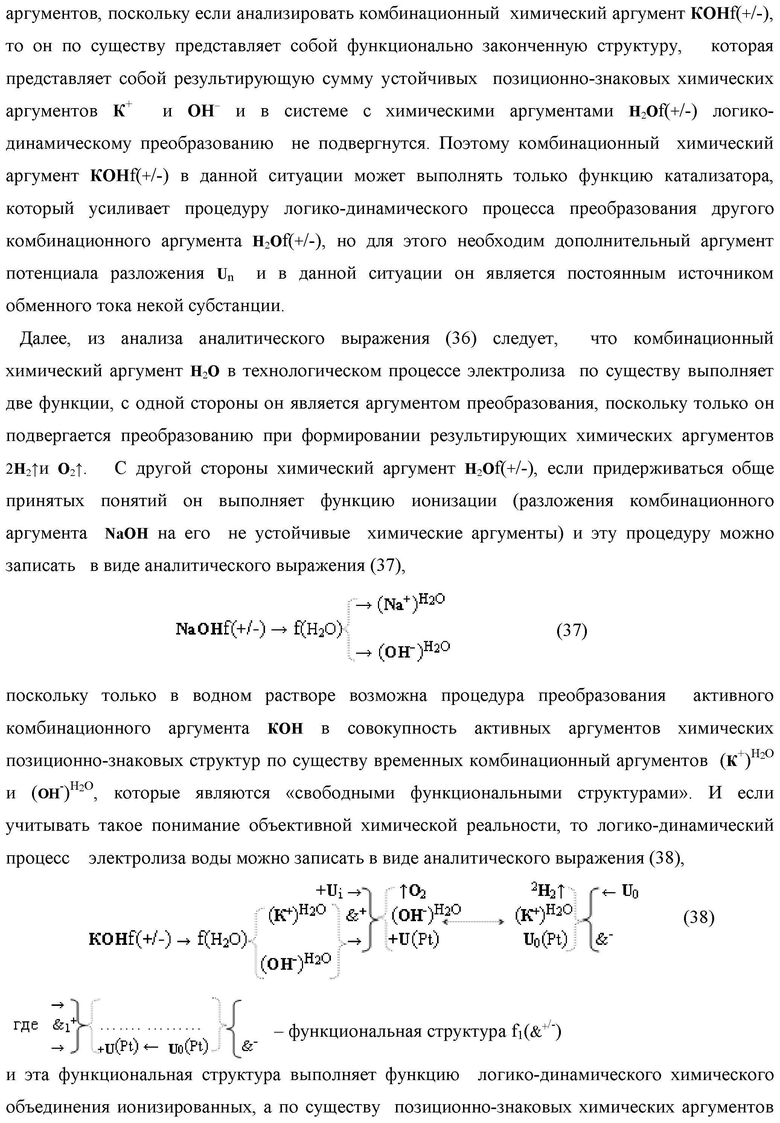

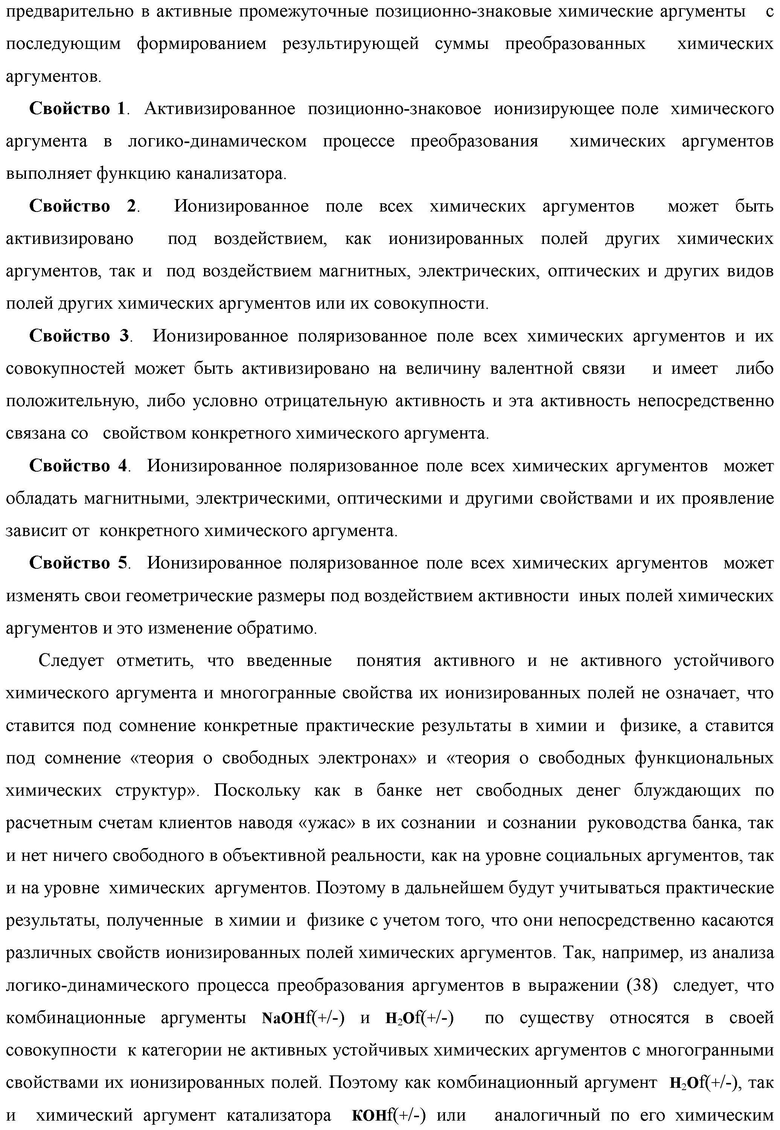

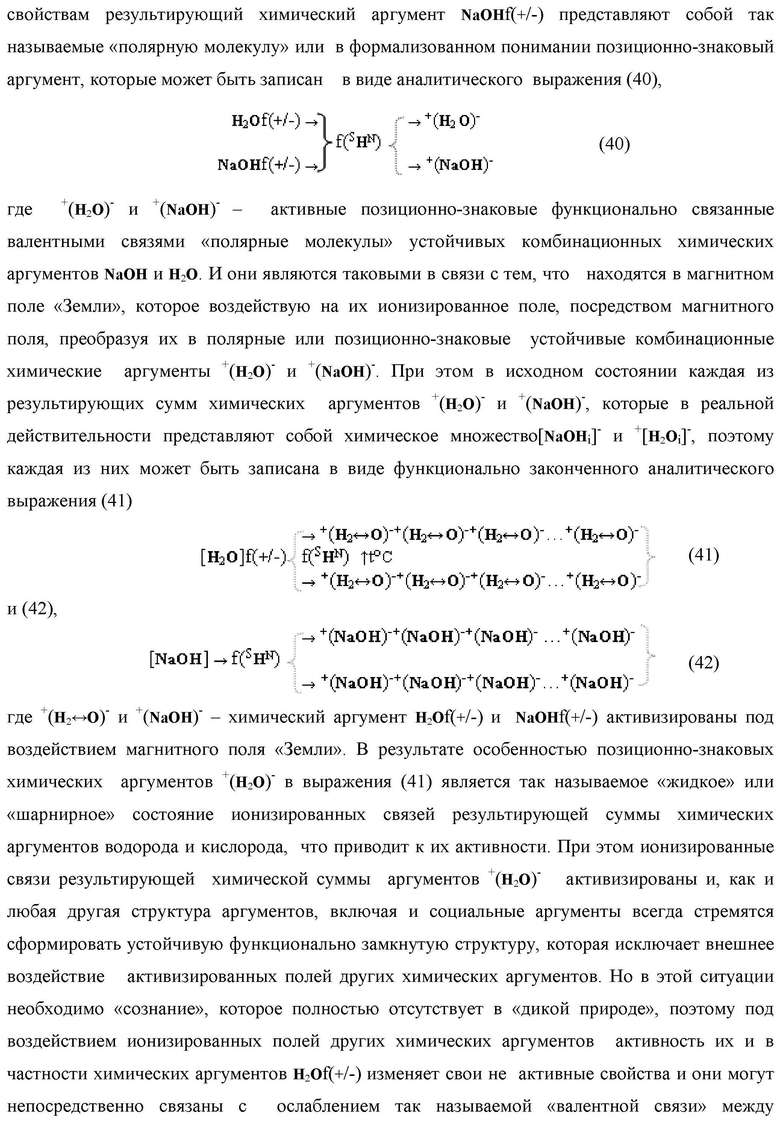

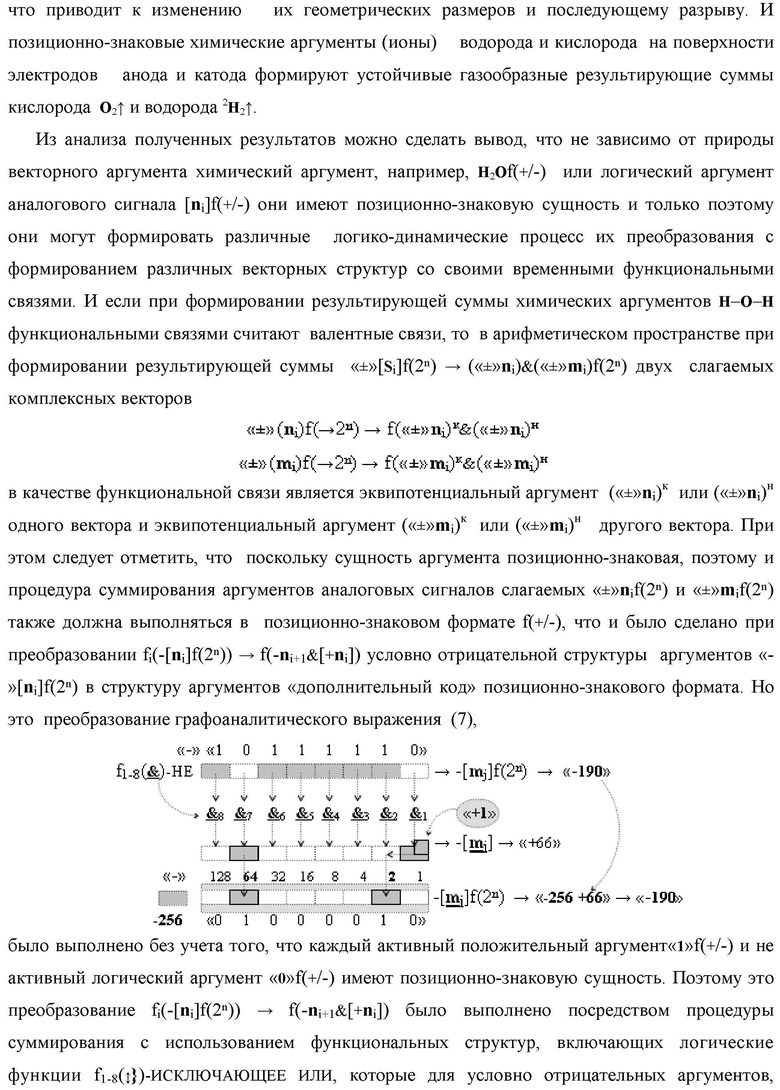

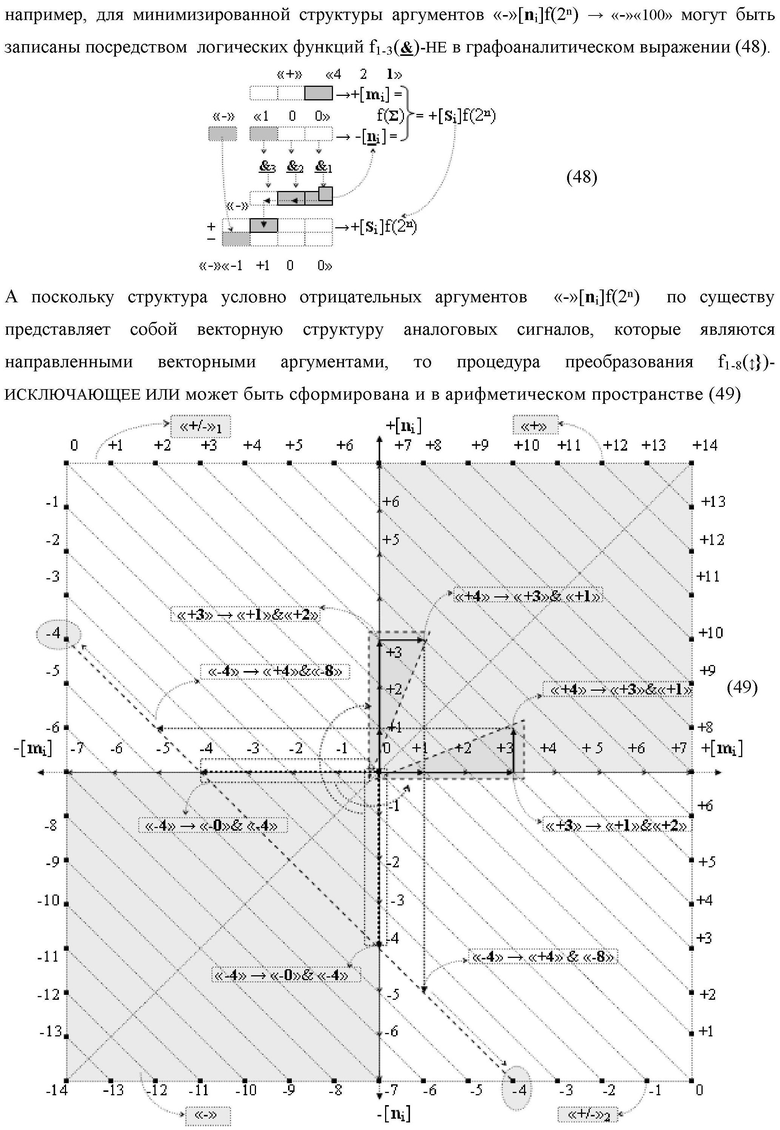

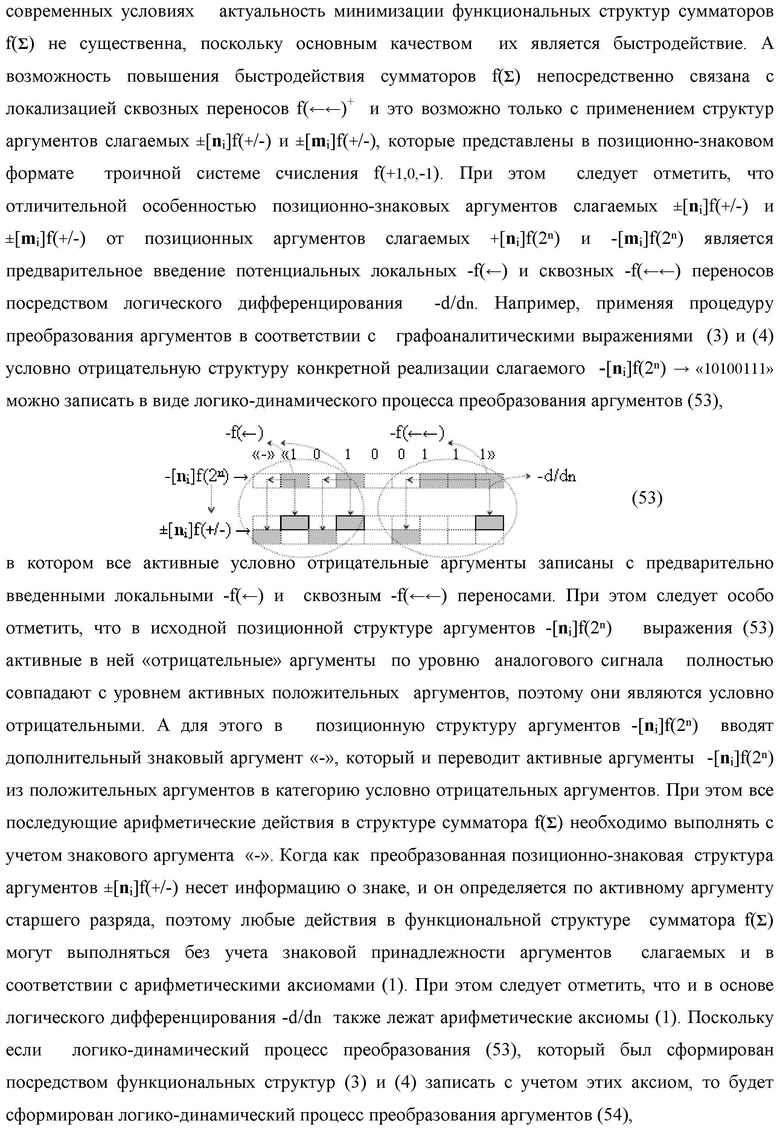

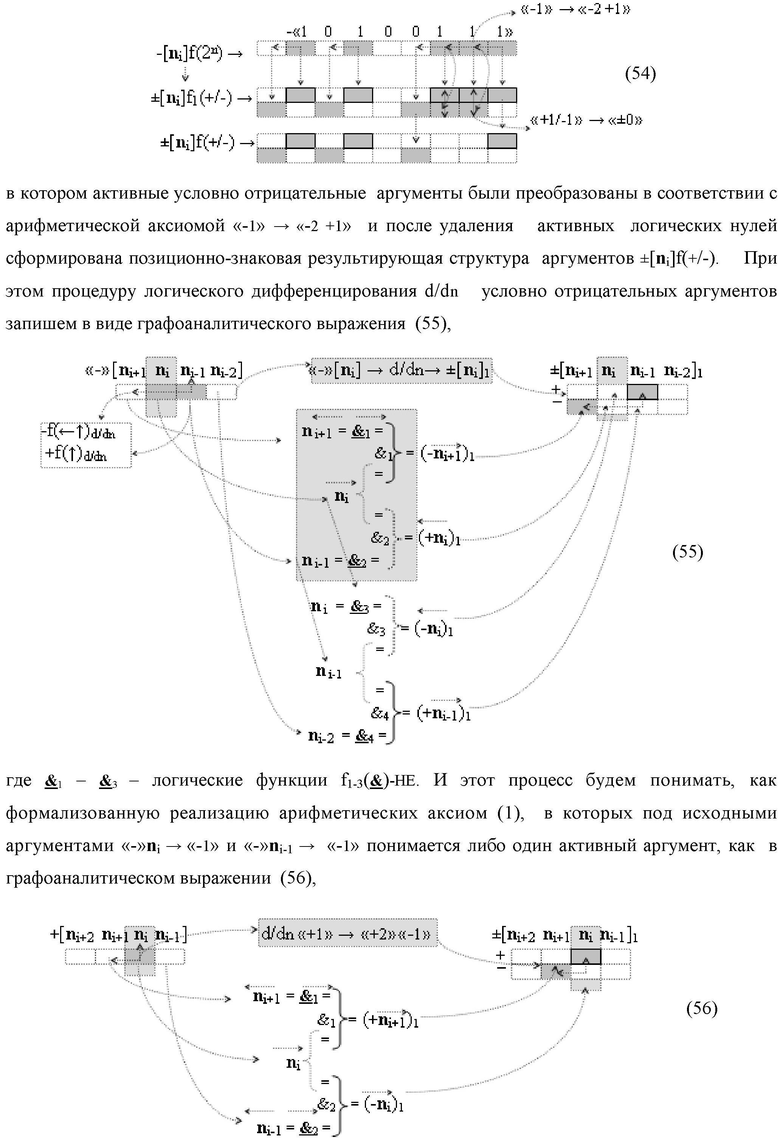

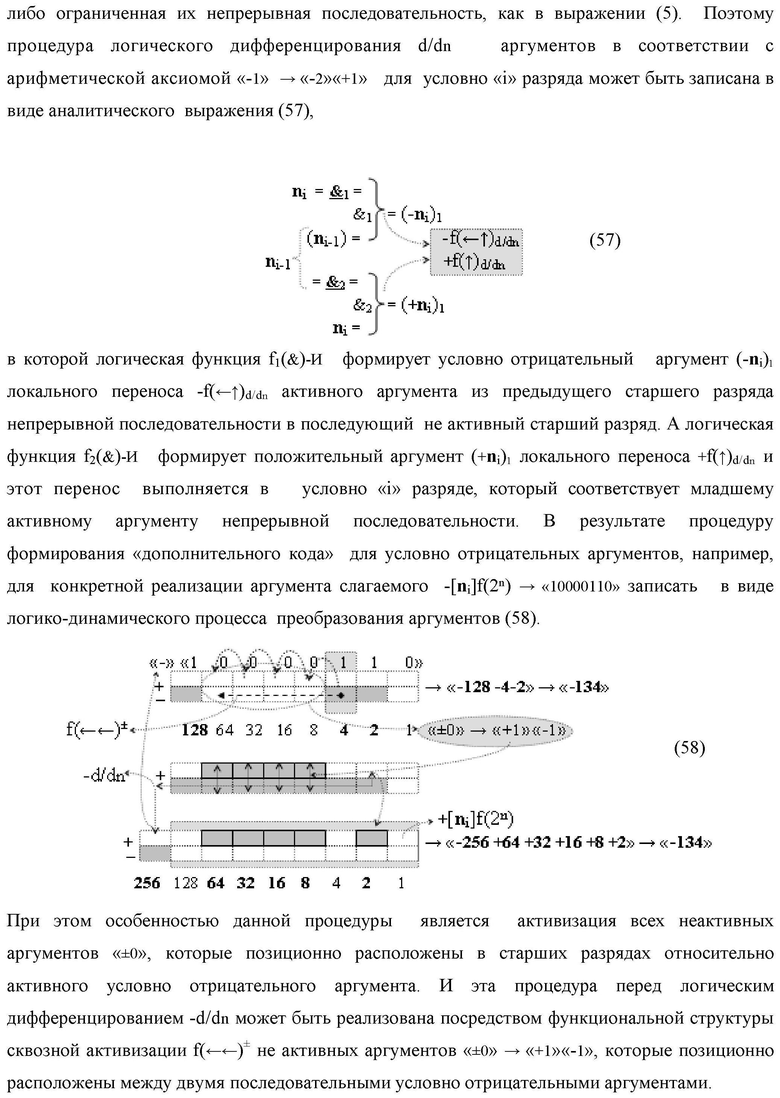

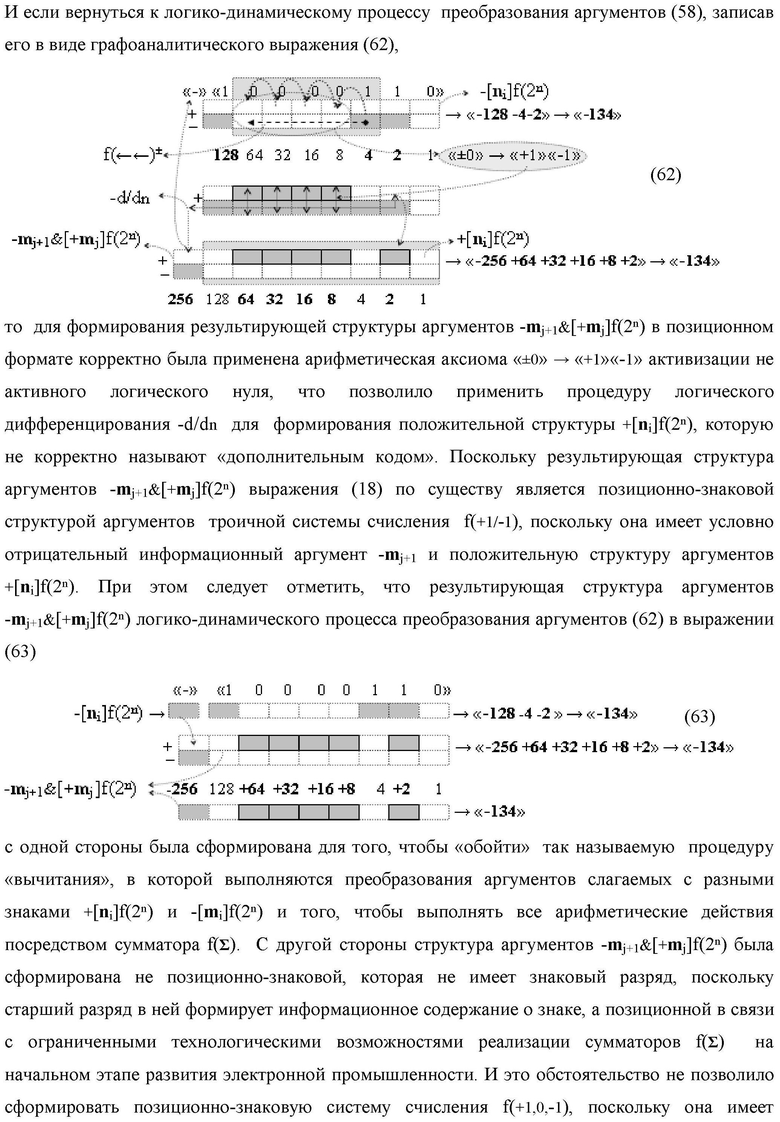

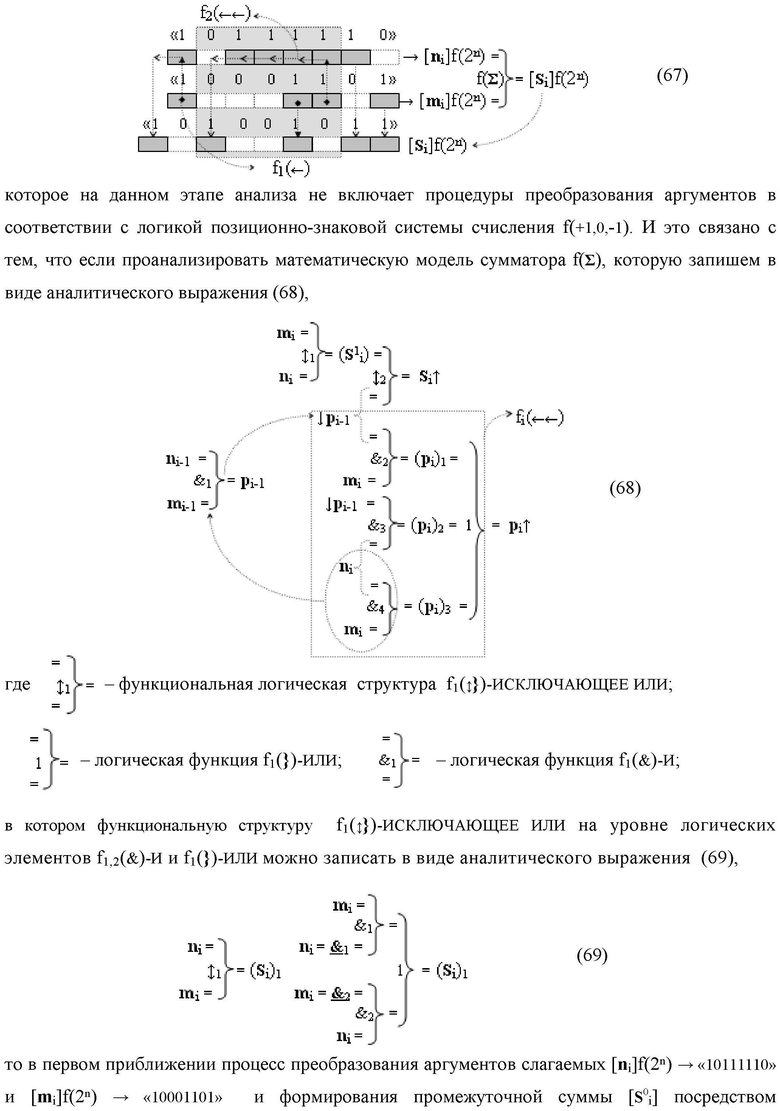

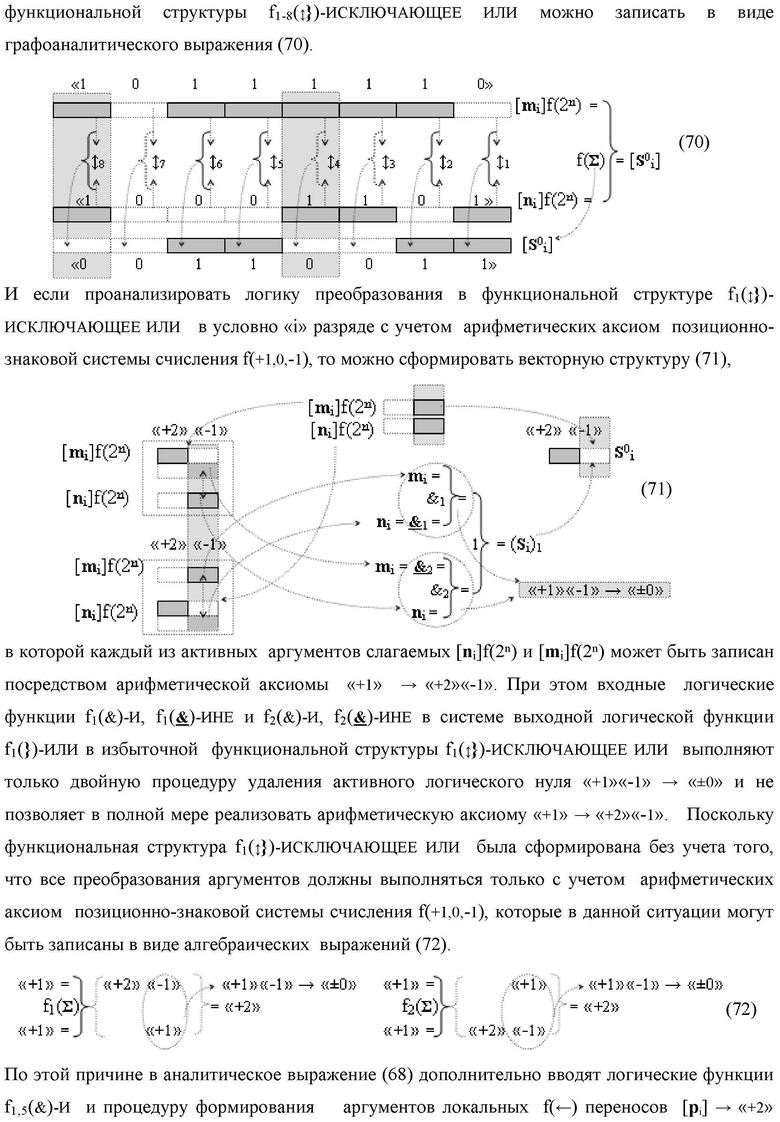

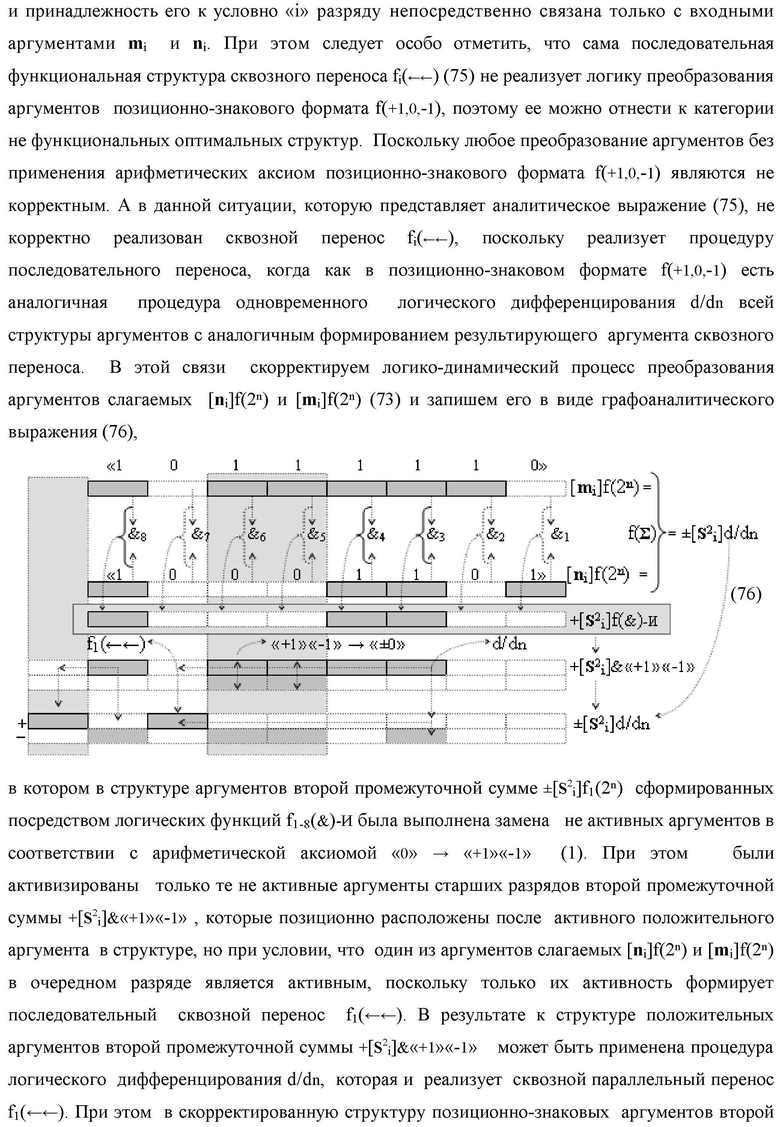

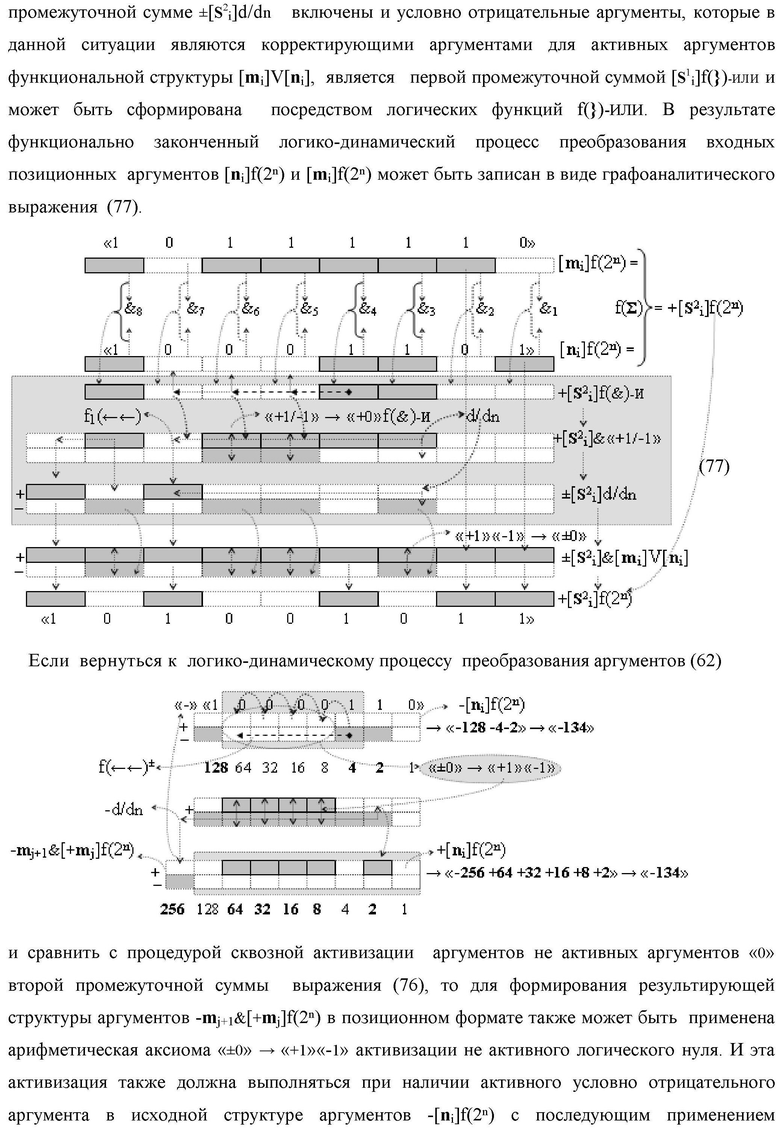

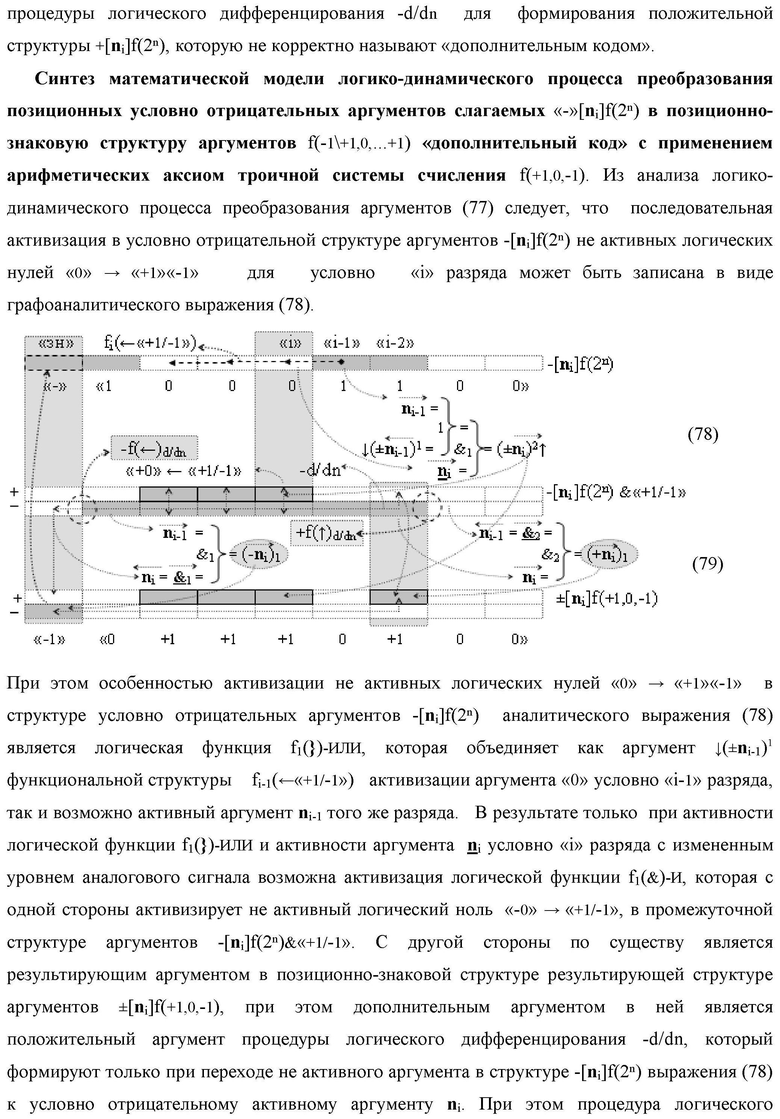

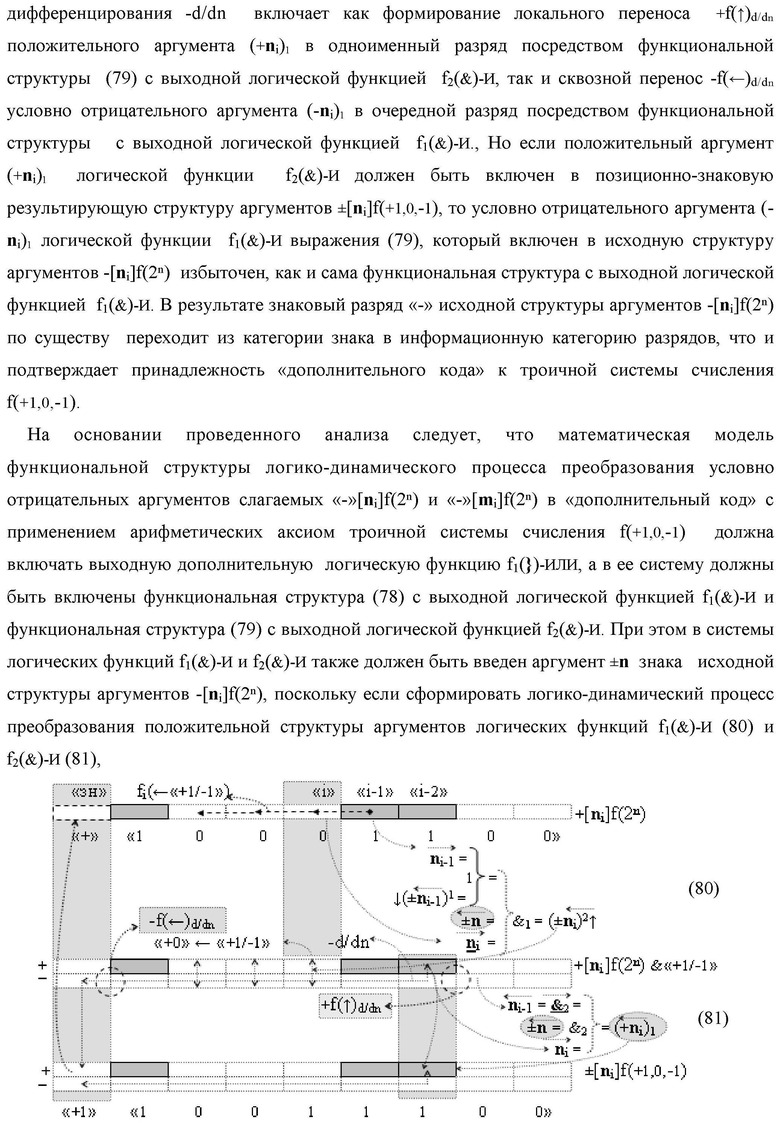

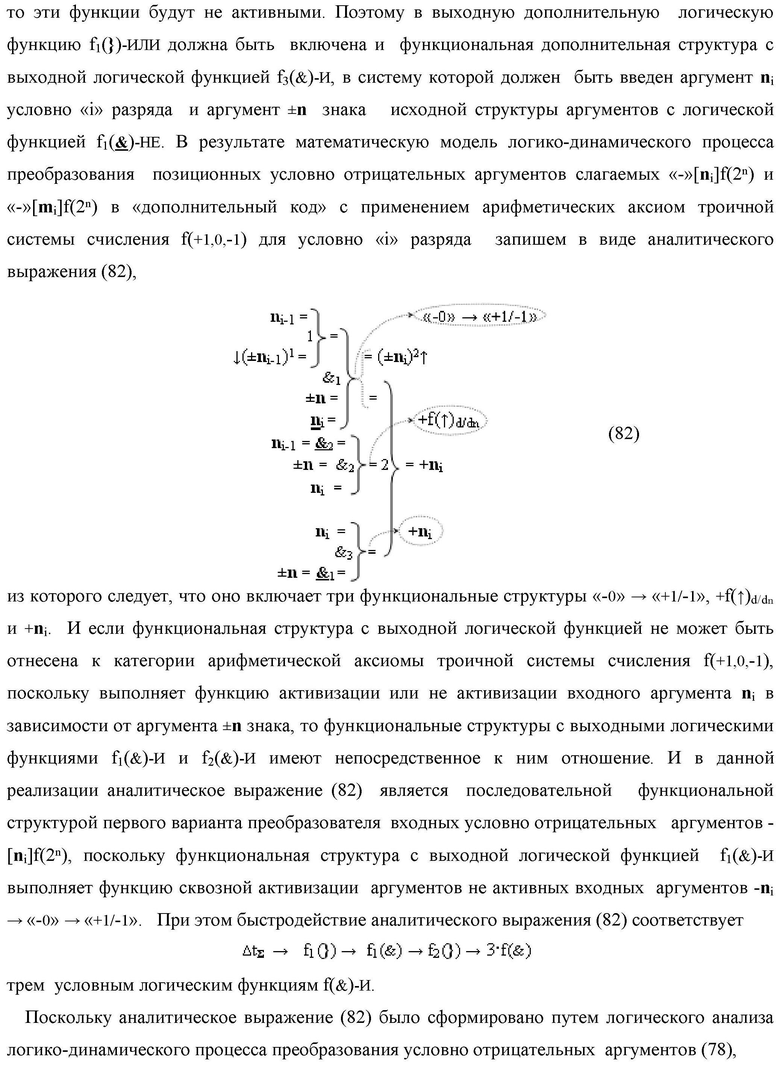

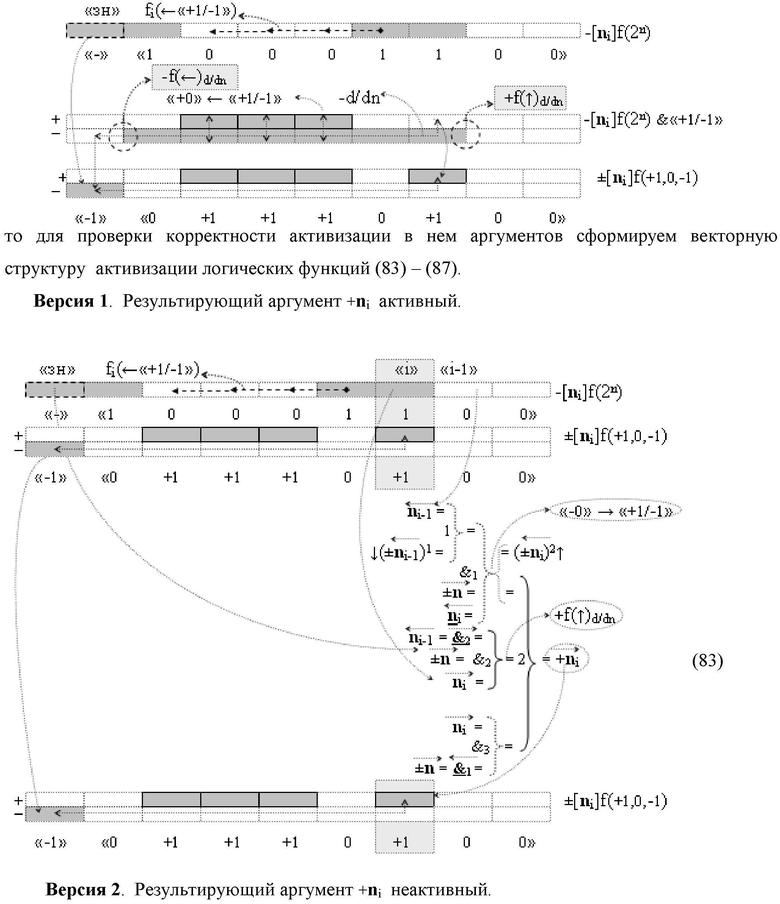

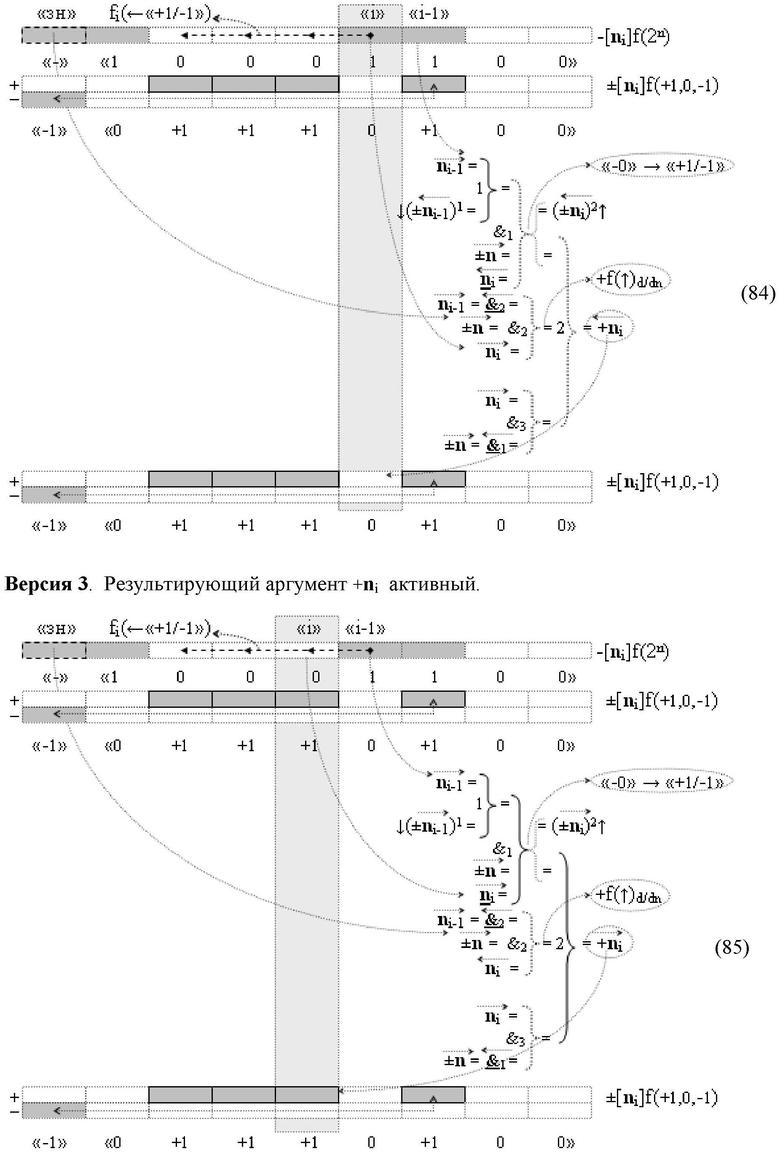

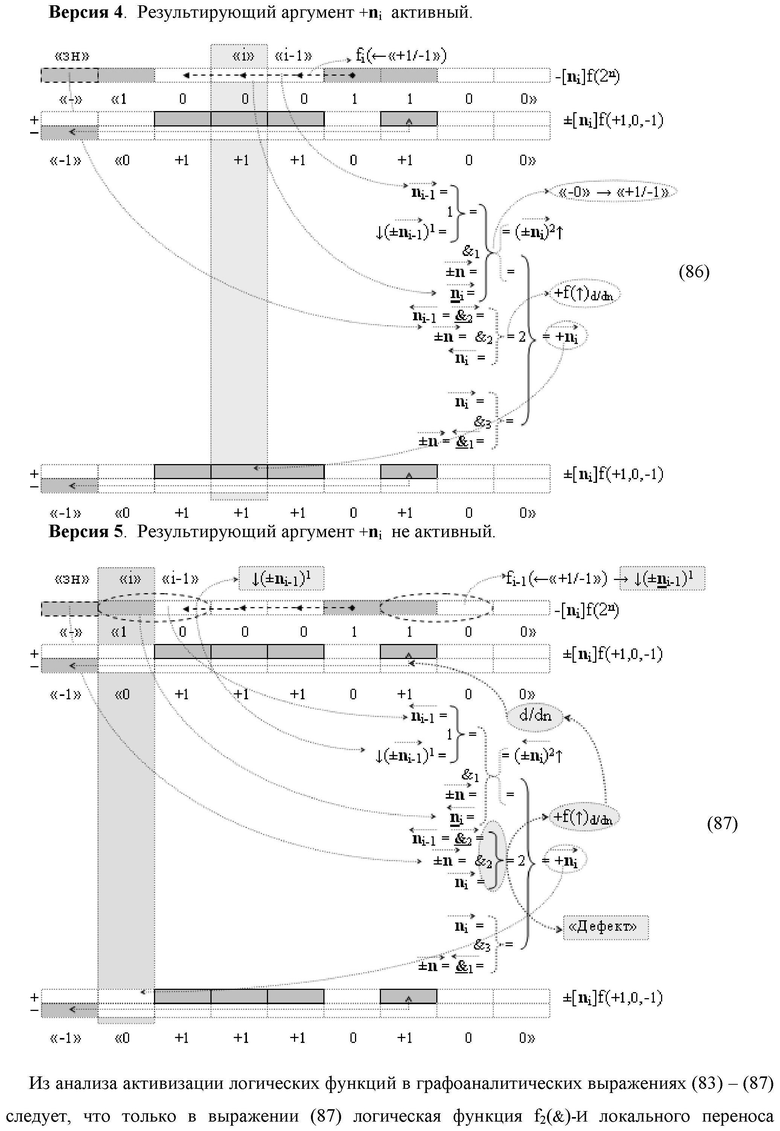

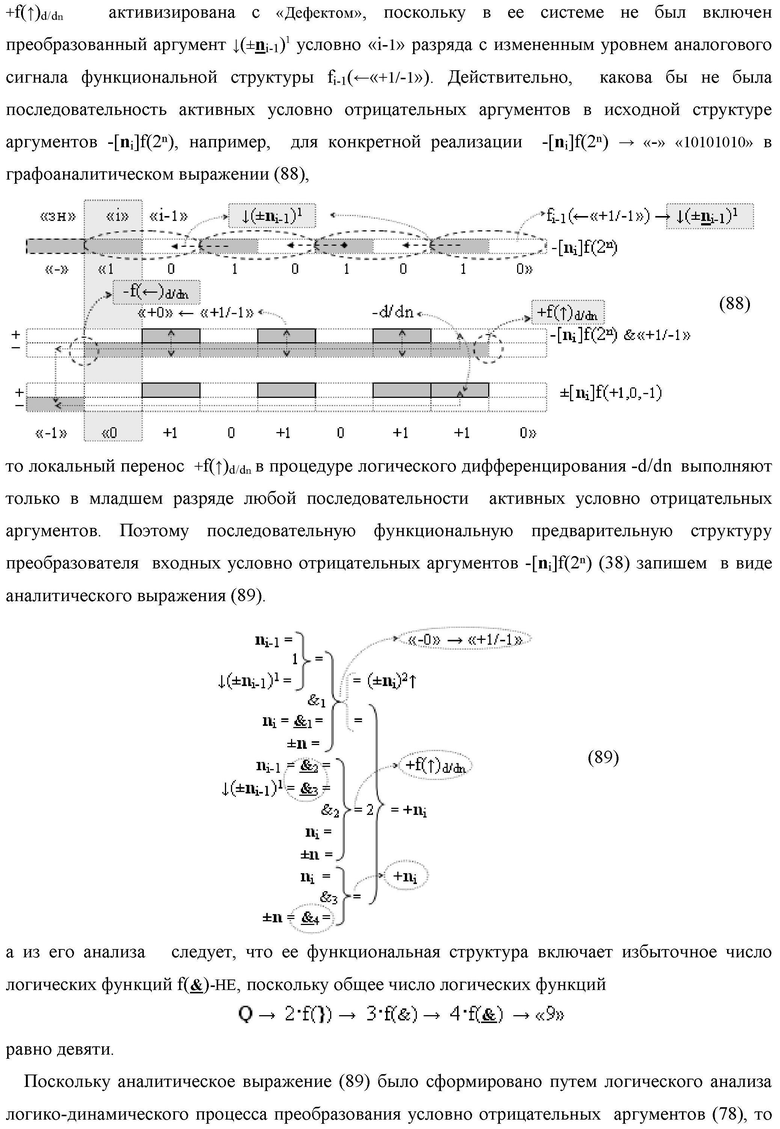

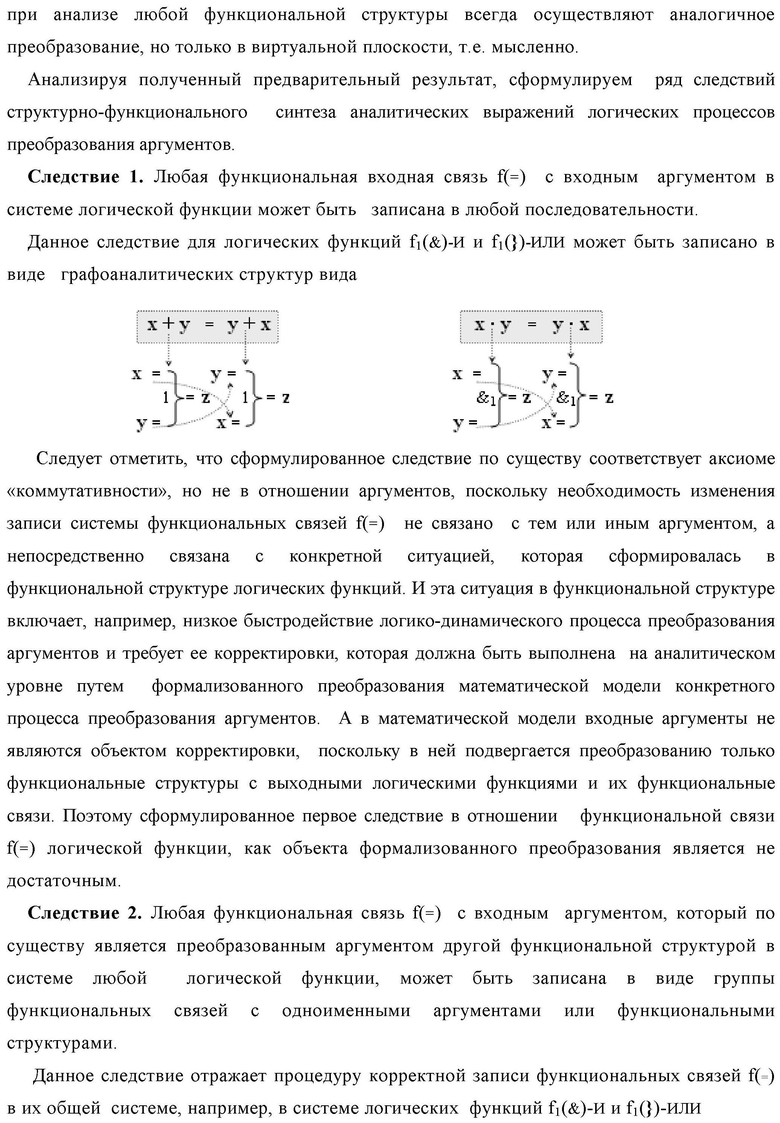

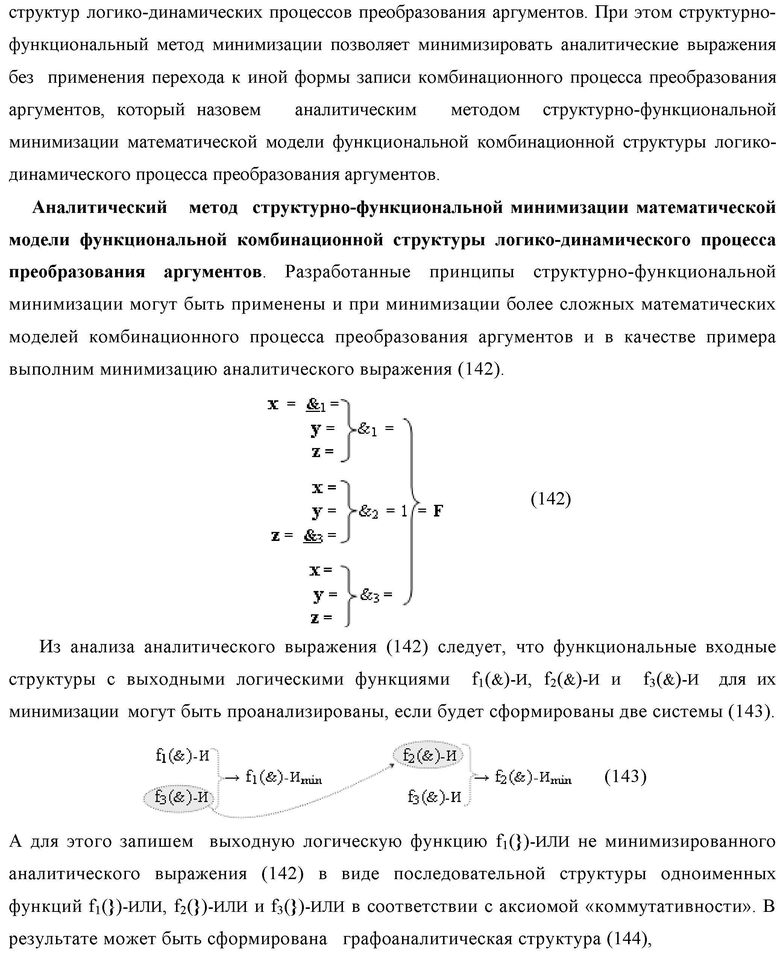

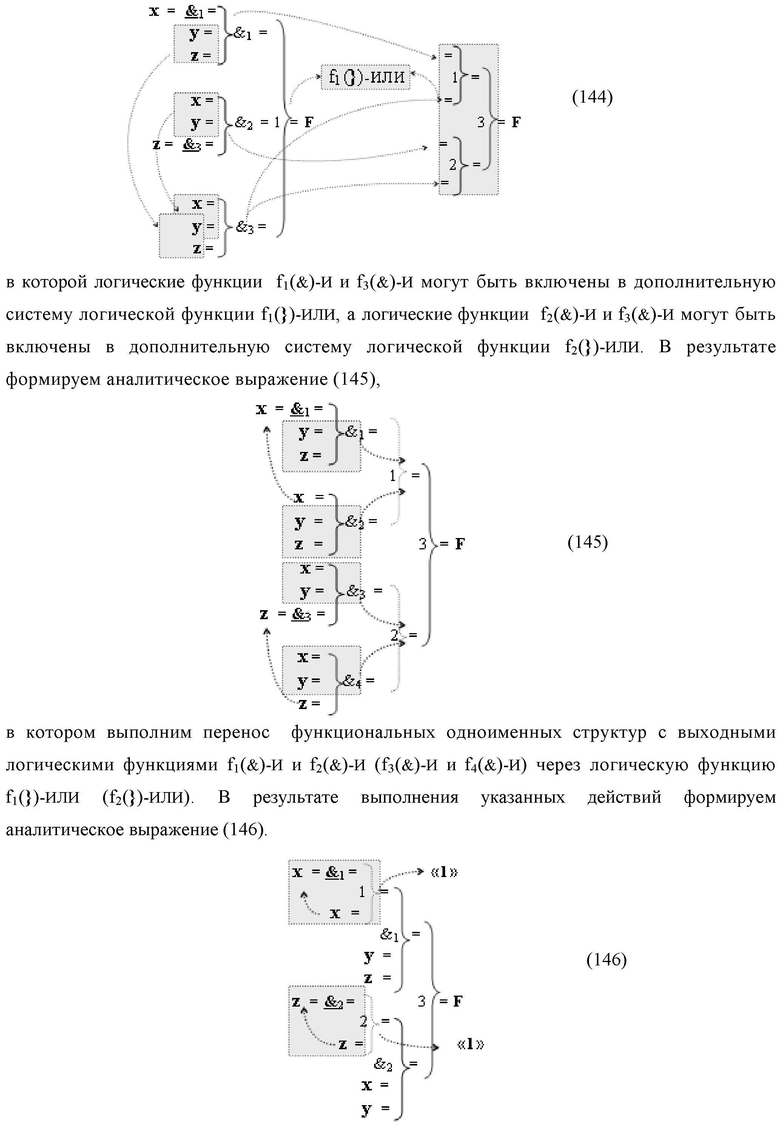

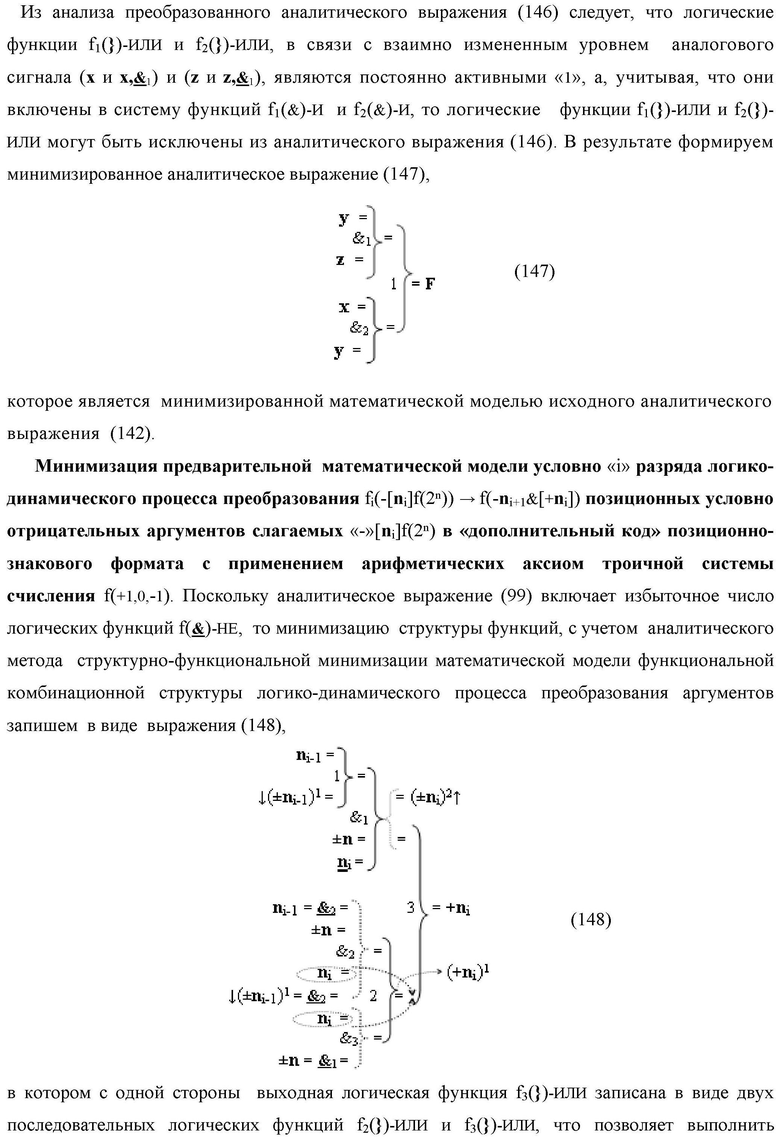

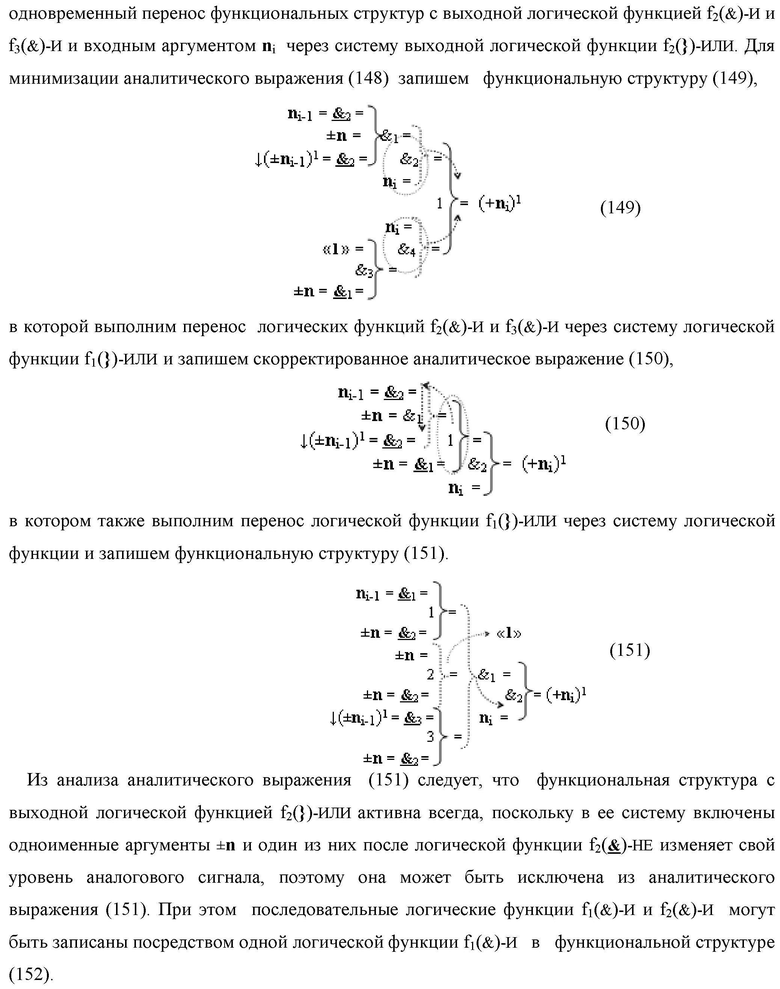

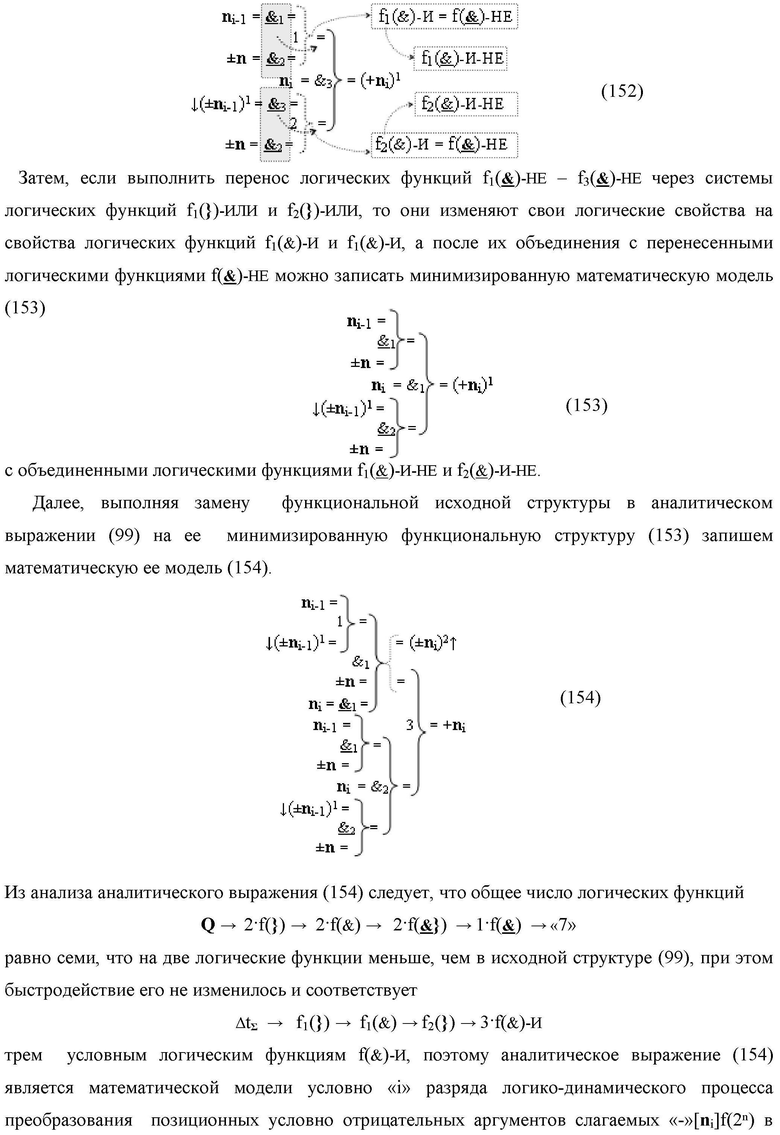

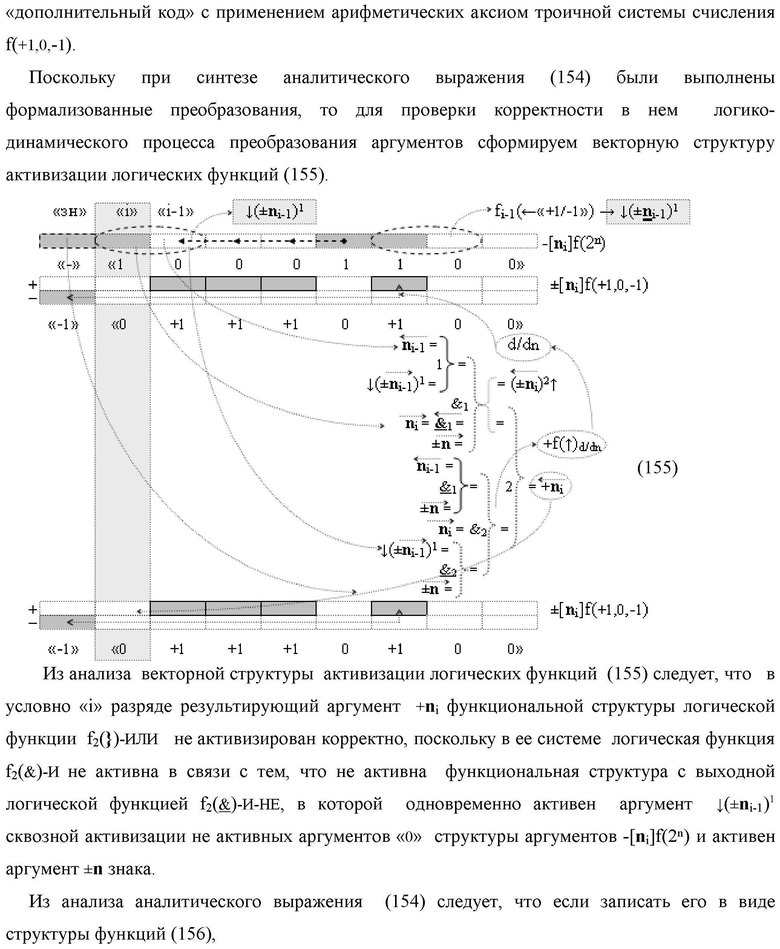

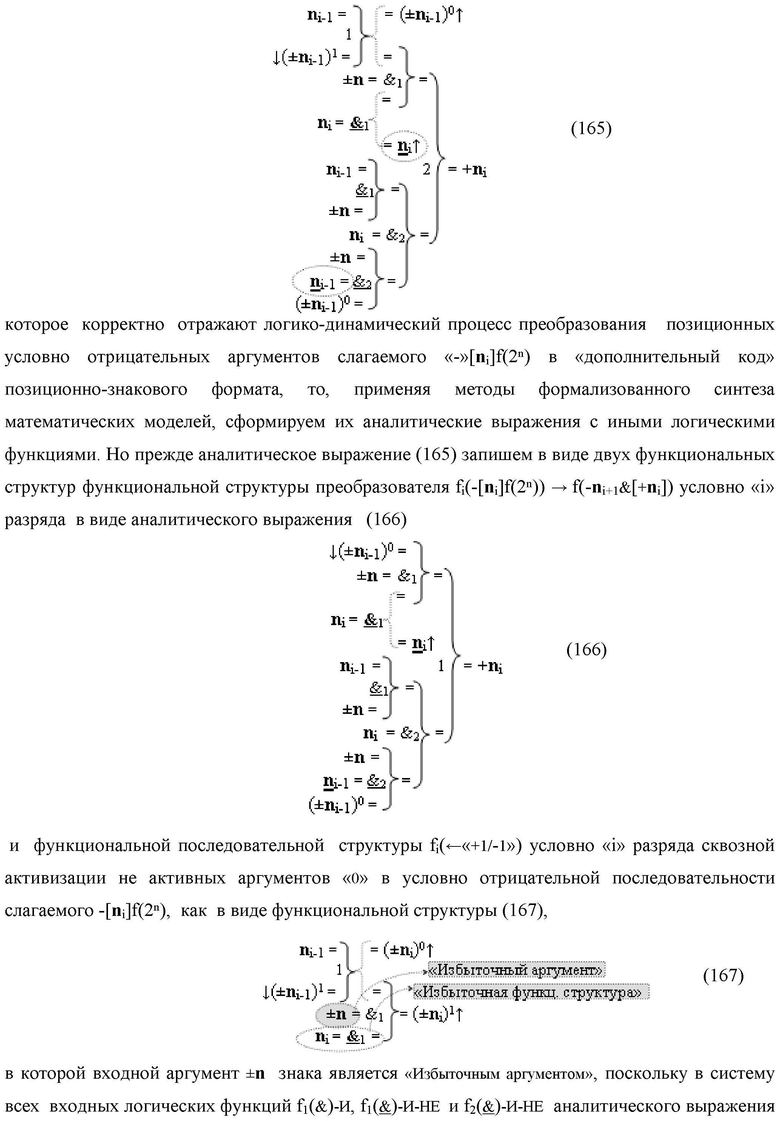

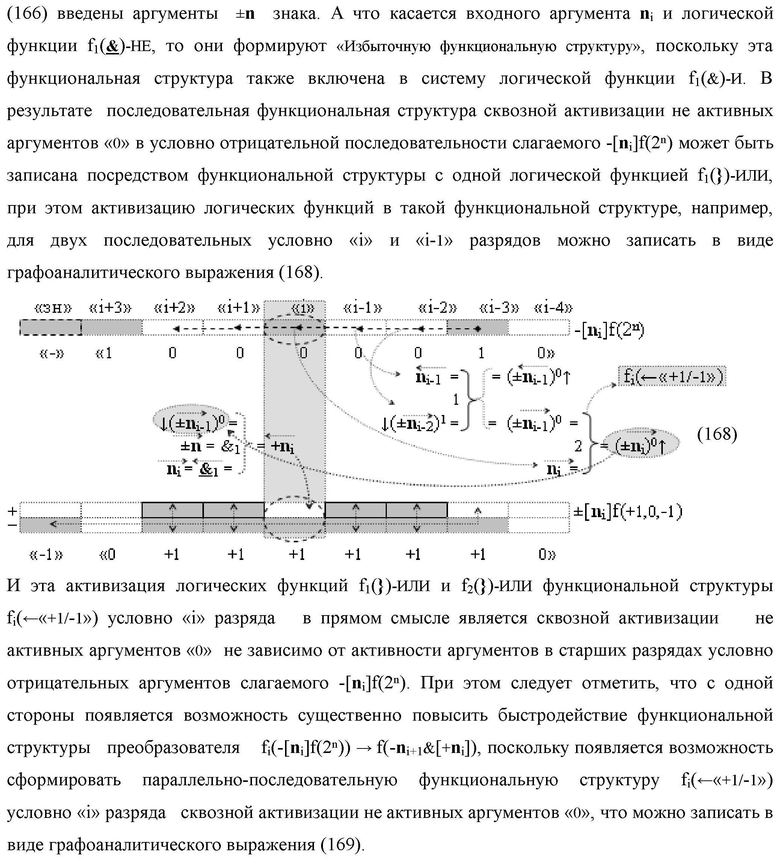

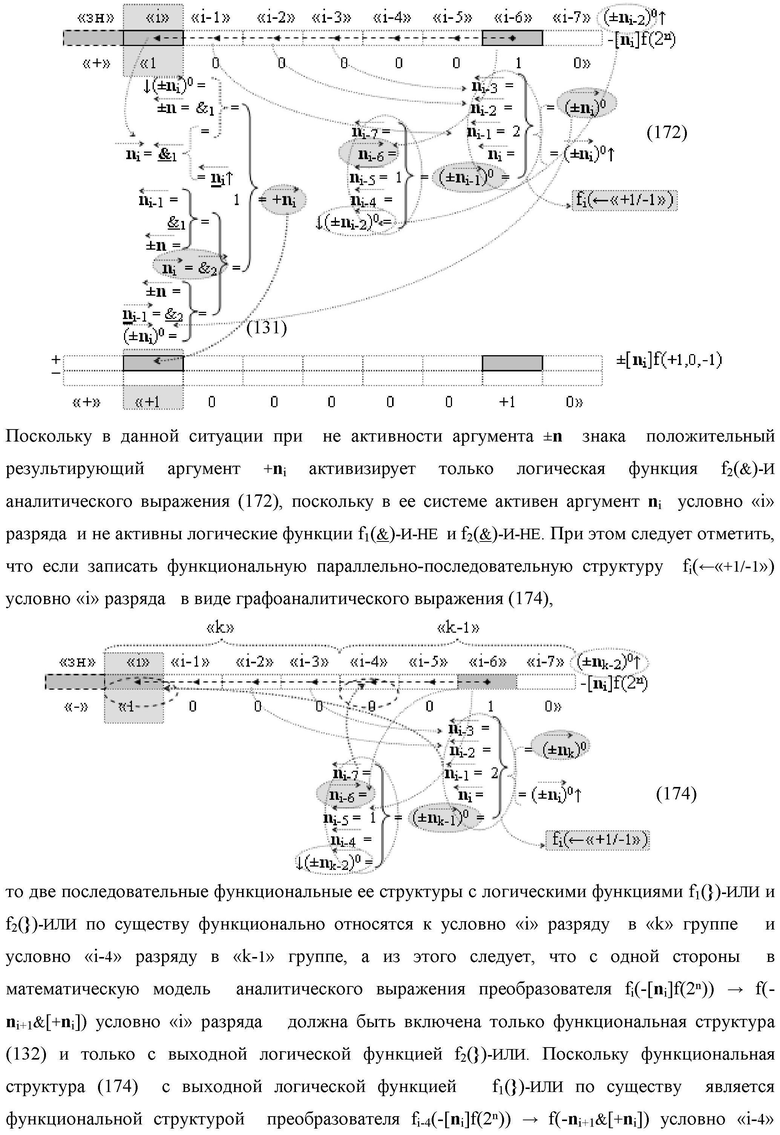

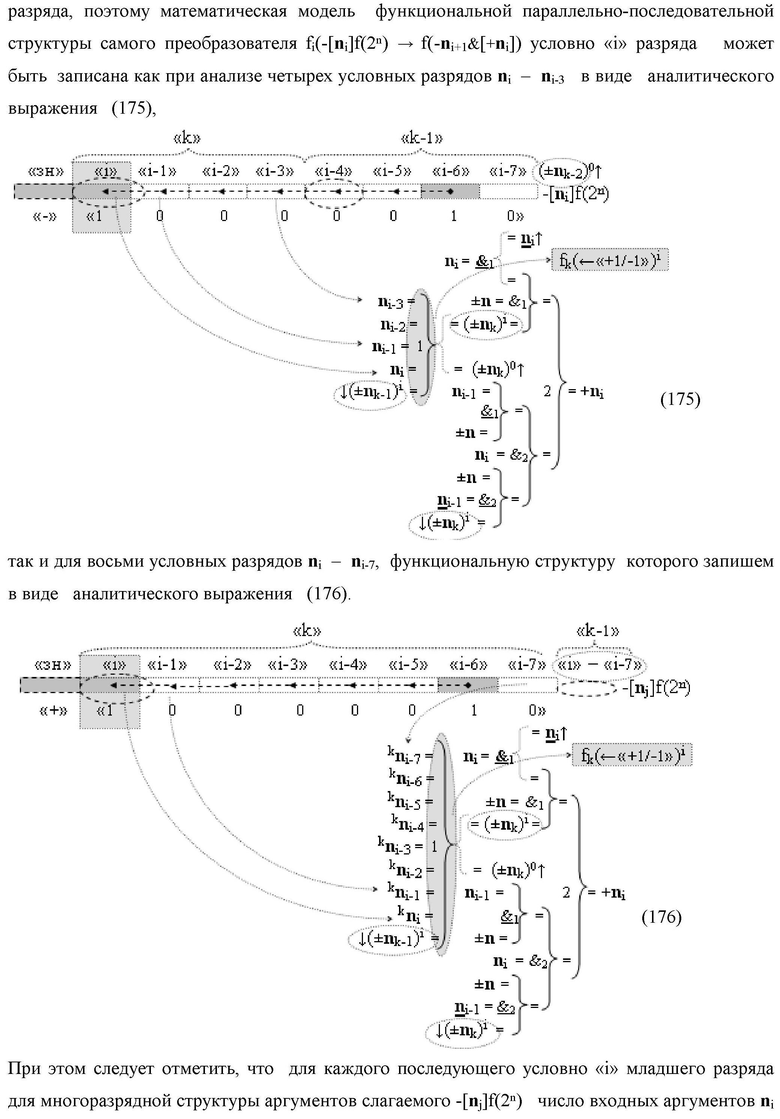

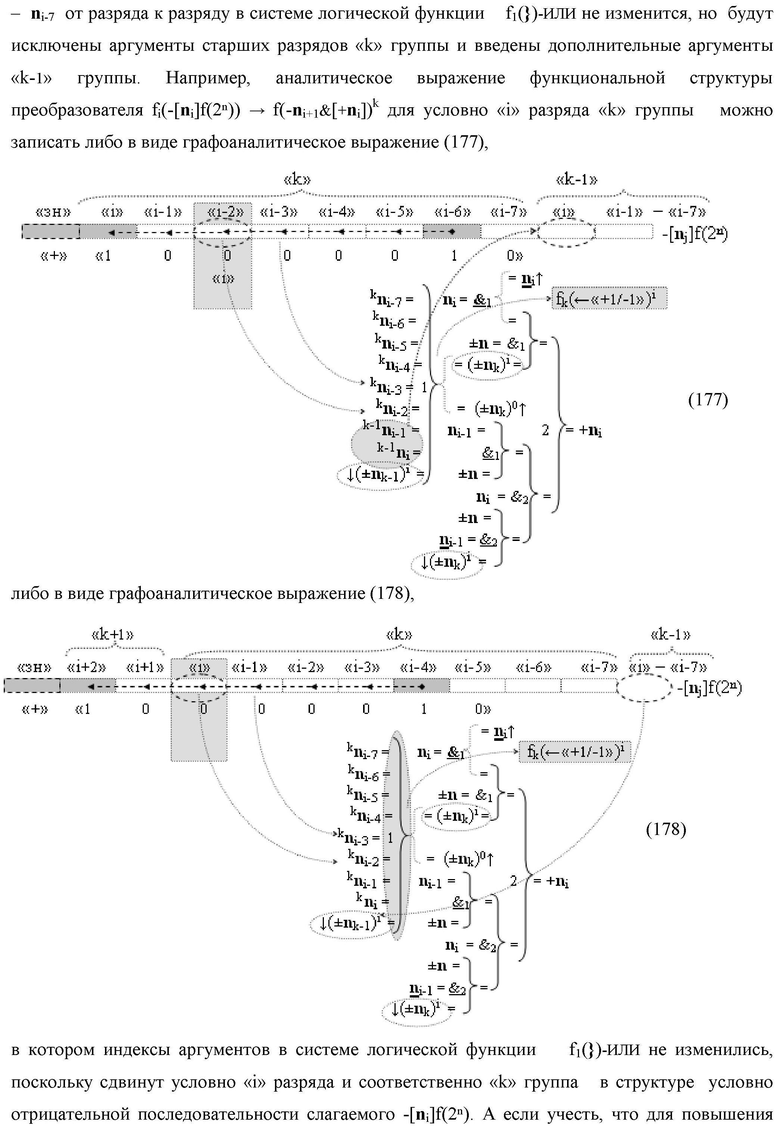

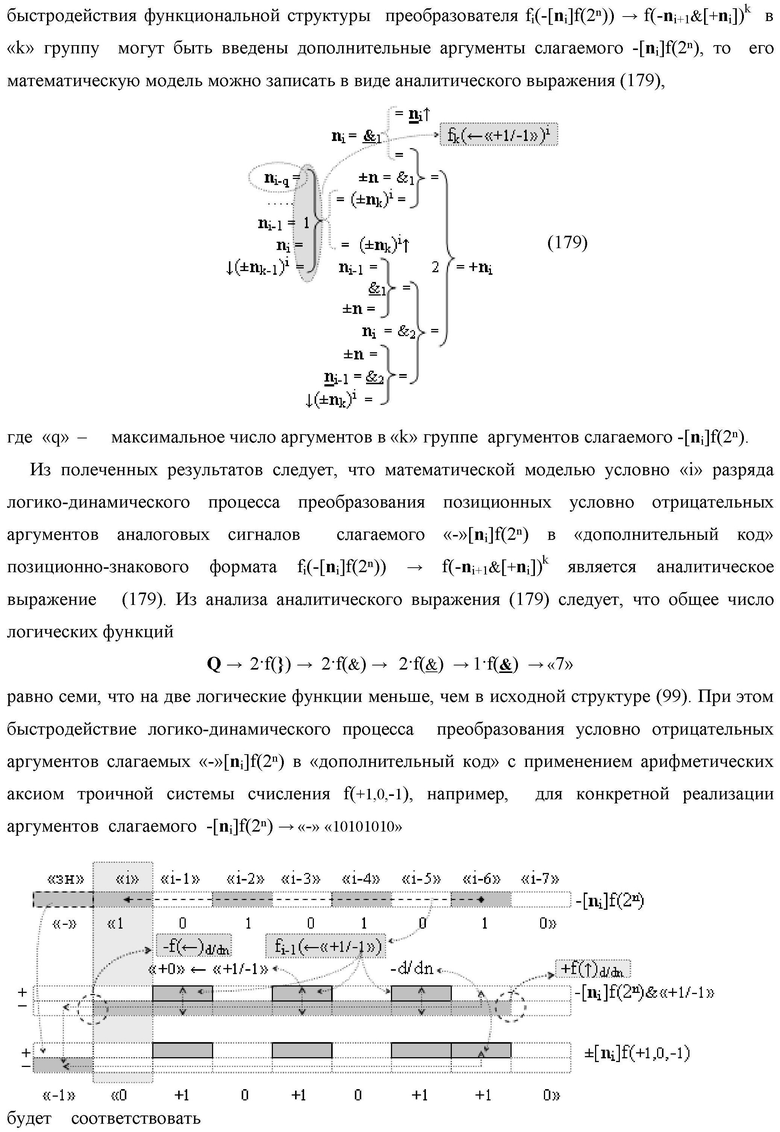

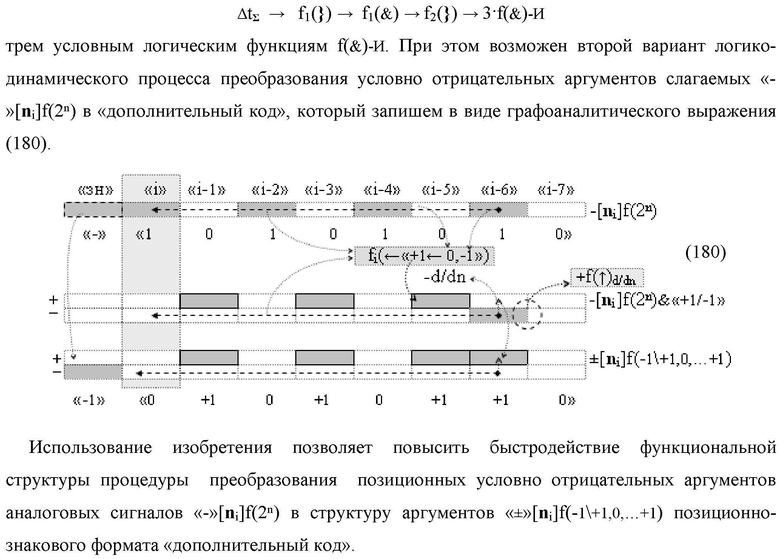

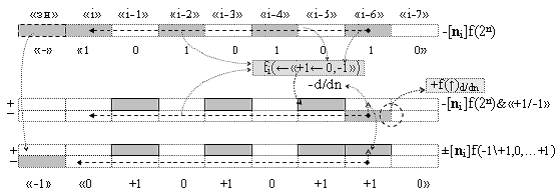

1. Способ преобразования позиционных условно отрицательных аргументов аналоговых сигналов «-»[ni]f(2n) в структуру аргументов «±»[ni]f(-1\+1,0,…+1) позиционно-знакового формата «дополнительный код» с применением арифметических аксиом троичной системы счисления f(+1,0,-1) (Русская логика), в соотвествии с которым выполняют одновременный логический анализ активности аргументов аналогового сигнала входной структуры аргументов «-»[ni]f(2n), после чего выполняют преобразование активного уровня входных аргументов в неактивный уровень аналогового сигнала, отличающийся тем, что изменение уровня аналогового сигнала аргумента в каждом условно «i» разряде выполняют только с учетом активного результирующего аргумента функциональной структуры fi(←«+1/-1»), посредством которой выполняют анализ и активизацию неактивного аргумента входной структуры «-»[ni]f(2n) в активные положительный и условно отрицательный аргументы в соответствии с арифметической аксиомой «0» → «+1/-1» и формируют промежуточную структуру аргументов аналоговых сигналов - [ni]f(2n)&«+1/-1», при этом результирующий аргумент функциональной структуры fi(←«+1/-1») активизируют в каждом условно «i» разряде только в том случае, если в предыдущих младших разрядах входной структуры «-»[ni]f(2n) активен хотя бы один условно отрицательный аргумент, после чего выполняют логическое дифференцирование -d/dn аргументов промежуточной структуры - [ni]f(2n)&«+1/-1» с формированием условно отрицательного аргумента -f(←)d/dn в старшем знаковом разряде и положительного аргумента в младшем разряде, которые объединяют с положительными активными аргументами функциональной структуры fi(←«+1/-1») в результирующей позиционно-знаковой структуре ±[ni]f(-1\+1,0,…+1) в соответствии с логико-динамическим процессом преобразования аргументов аналоговых сигналов вида

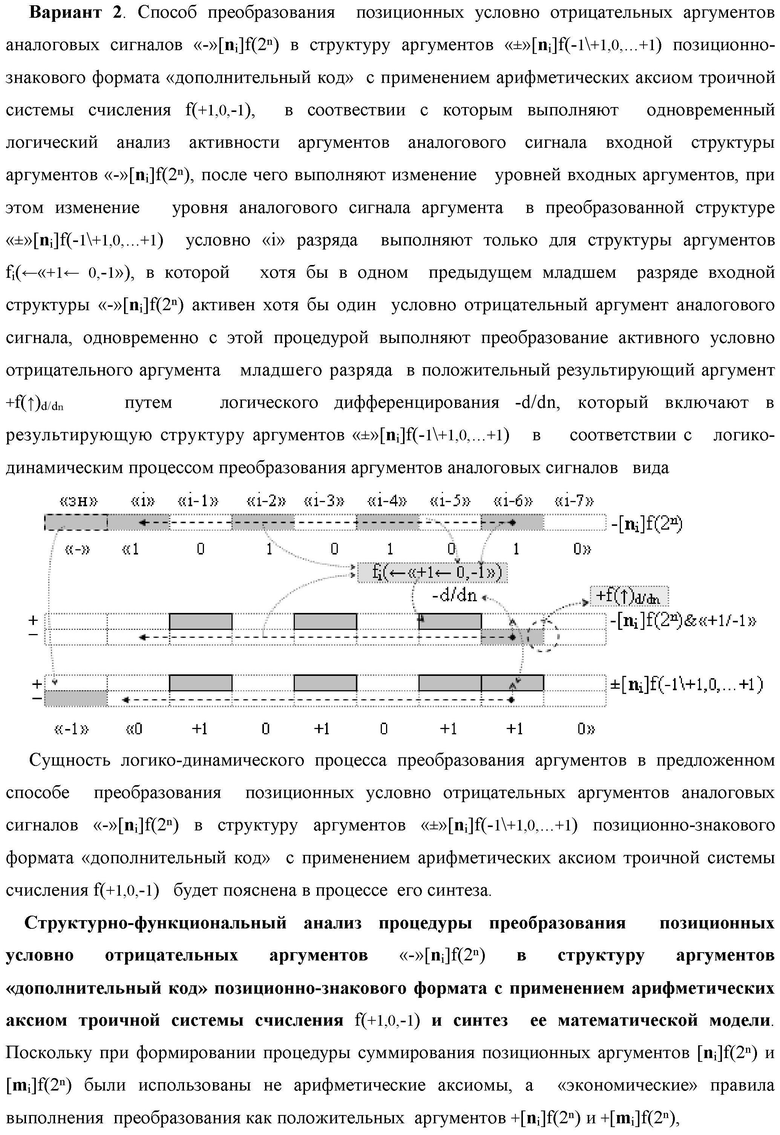

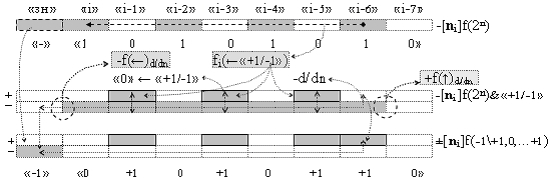

2. Способ преобразования позиционных условно отрицательных аргументов аналоговых сигналов «-»[ni]f(2n) в структуру аргументов «±»[ni]f(-1\+1,0,…+1) позиционно-знакового формата «дополнительный код» с применением арифметических аксиом троичной системы счисления f(+1,0,-1), в соотвествии с которым выполняют одновременный логический анализ активности аргументов аналогового сигнала входной структуры аргументов «-»[ni]f(2n), после чего выполняют изменение уровней входных аргументов, отличающийся тем, что изменение уровня аналогового сигнала аргумента в преобразованной структуре «±»[ni]f(-1\+1,0,…+1) условно «i» разряда выполняют только для структуры аргументов fi(←«+1←0,-1»), в которой хотя бы в одном предыдущем младшем разряде входной структуры «-»[ni]f(2n) активен хотя бы один условно отрицательный аргумент аналогового сигнала, одновременно с этой процедурой выполняют преобразование активного условно отрицательного аргумента младшего разряда в положительный результирующий аргумент +f(↑)d/dn путем логического дифференцирования -d/dn, который включают в результирующую структуру аргументов «±»[ni]f(-1\+1,0,…+1) в соответствии с логико-динамическим процессом преобразования аргументов аналоговых сигналов вида

| СПОСОБ ЛОГИЧЕСКОГО ДИФФЕРЕНЦИРОВАНИЯ АНАЛОГОВЫХ СИГНАЛОВ, ЭКВИВАЛЕНТНЫХ ДВОИЧНОМУ КОДУ, И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2006 |

|

RU2375749C2 |

| Преобразователь двоичного кода в позиционно-знаковый код | 1987 |

|

SU1438005A1 |

| Преобразователь двоичного кода в троичный код | 1983 |

|

SU1169172A1 |

| JP 57157350 A, 28.09.1982 | |||

| US 4566044 A, 21.01.1986 | |||

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

Авторы

Даты

2011-09-20—Публикация

2010-05-25—Подача