Данное изобретение относится к вычислительной технике и автоматике, может быть использовано в аппаратуре с повышенной надежностью, не имеющей доступа для ремонта, например для космических аппаратов.

Известно устройство для вывода информации, содержащее дешифратор адреса, первый и второй элемент И, элемент ИЛИ, элемент задержки, первый и второй одновибратор и регистр данных (А.С. №1548781, G06F 3/00, G06F 13/00, автор В.П.Ткачев).

Однако это устройство имеет недостаточную надежность.

Наиболее близким к предлагаемому по технической сущности является устройство для вывода цифровой информации с параллельной магистрали, содержащее регистр, элемент И, элемент задержки, дешифратор адреса, блок сравнения, информационные входы регистра являются информационными входами устройства, а выходы соединены с входами блока сопряжения (магистральные усилители), выходы которого являются информационными выходами устройства, вход записи регистра соединен с выходом дешифратора, входы которого являются адресными входами устройства, первая группа входов блока сравнения соединена с информационными входами регистра, вторая группа входов блока сравнения соединена с выходами блока сопряжения, а выход соединен с первым входом элемента И, выходы которого является управляющим выходом устройства, второй вход элемента И соединен с выходом элемента задержки, вход которого соединен с выходом дешифратора (А.С. №1608631, G06F 3/00, автор В.В.Виноградов), которое выбрано в качестве прототипа.

Данное устройство имеет недостаточную сбоеустойчивость и надежность. А именно, при наличии сбоев на информационных входах устройства в момент записи в регистр будет занесена сбойная информация, следовательно, и на информационных выходах устройства будет сбойная информация, а если на момент сравнения информация на информационных входах устройства восстановится, то информация, записанная в регистр и на информационных выходах устройства, будет разная, следовательно, информация на информационных выходах устройства будет пропущена. Кроме того, в устройстве отсутствует сигнал о наличии неисправности, например, регистра за счет действия тяжелых заряженных частиц (ТЗЧ) космического пространства, которому особенно подвержены элементы памяти.

Целью изобретения является устранение указанных недостатков.

Поставленная цель достигается тем, что в устройство введены второй и третий регистры, группа мажоритарных элементов, число которых определяется количеством разрядов информационного входа устройства, информационные входы второго и третьего регистров соединены с соответствующими информационными входами устройства, информационные выходы первого регистра соединены с первыми входами мажоритарных элементов, информационные выходы второго регистра соединены со вторыми входами мажоритарных элементов, информационные выходы третьего регистра соединены с третьими входами мажоритарных элементов, выходы которых соединены с входами блока сопряжения, второй выход дешифратора адреса соединен с входом запись второго регистра, третий выход дешифратора адреса соединен с входом запись третьего регистра и с входом элемента задержки.

Кроме того, в него ведены второй элемент И и элемент ИЛИ, а блок сравнения содержит выходы «больше» и «меньше», которые соединены с входами элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом элемента задержки, выход второго элемента И является сигнальным выходом «неисправность» устройства.

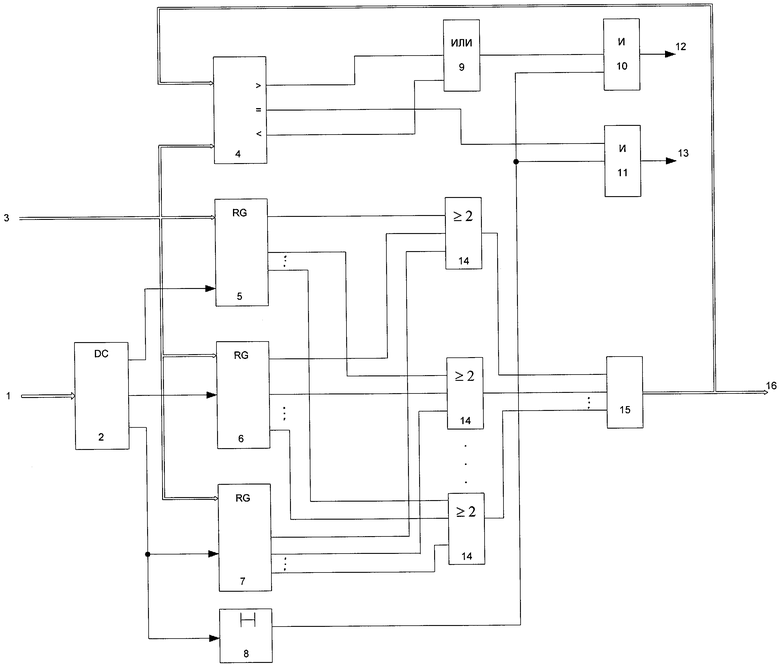

На чертеже представлена функциональная схема устройства для вывода цифровой информации.

Устройство для вывода цифровой информации содержит адресные входы 1, соединенные с дешифратором адреса 2, информационные входы 3, соединенные с первой группой входов блока сравнения 4 и с информационными входами первого, второго, третьего регистров 5, 6, 7, элемент задержки 8, элемент ИЛИ 9, два элемента И 10 и 11, выходы которых соответственно являются выходом «Управление» 12 устройства и выходом «Неисправность» 13 устройства, группу мажоритарных элементов 14 по числу разрядов информационного входа устройства, выходы которых соединены с входами блока сопряжения 15, выходы которых соединены со второй группой входов блока сравнения 4 и являются информационными выходами 16 устройства, первый выход дешифратора 2 соединен с входом записи первого регистра 5, второй выход соединен с входом записи второго регистра 6, третий выход соединен с входом записи третьего регистра 7 и с входом элемента задержки 8, выход которого соединен с первыми входами элементов И 10 и 11, второй вход первого элемента И 10 соединен с выходом «равно» блока сравнения 4, а выходы «больше» и «меньше» соединены со входами элемента ИЛИ 9, выход которого соединен со вторым входом второго элемента И 11, информационные выходы первого регистра 5 соединены с первыми входами мажоритарных элементов 14, информационные выходы второго регистра 6 соединены со вторыми входами мажоритарных элементов 14, информационные выходы третьего регистра 7 соединены с третьими входами мажоритарных элементов 14.

Устройство работает следующим образом. Обмен информацией между управляющим устройством и устройством вывода осуществляется по адресному входу 1 и информационному входу 3. Требуемые данные для вывода устанавливаются на информационные входы 3, при последовательной подаче на адресные входы 1 адресов первого регистра 5, второго регистра 6 и третьего регистра 7 данные последовательно записываются в соответствующие регистры 5, 6, 7, информация с которых мажорируется в мажоритарных элементах 14 и через блок сопряжения 15 поступает на выход 16, в случае совпадения данных на входе 3 и выходе 16 устройства на выходе «равно» блока сравнения 4 формируется логическая 1. Через время, определяемое элементом задержки 8, на выходе первого элемента И 10 появляется сигнал о готовности информации на выходе устройства 16. В случае не совпадения данных на входе 3 и выходе 16 устройства на выходе «больше» или «меньше» блока сравнения 4 формируется логическая 1, которая через элемент ИЛИ 9 поступает на второй вход второго элемента И 11 и через время, определяемое элементом задержки 8, на выходе второго элемента И 11 и, следовательно, на выходе 13 появляется сигнал о неисправности устройства. Элемент задержки 8 обеспечивает время завершения переходных процессов в регистре 7, в мажоритарных элементах 14, в блоке сопряжения 15 и в блоке сравнения 4. Разнесение во времени записи в регистры позволяет парировать кратковременные одиночные сбои на информационных входах устройства, а отказ одного из трех регистров не повлечет за собой выход из строя самого устройства.

Данное устройство предполагается использовать в аппаратуре управления космических аппаратов. Опытный образец выполнен на интегральных микросхемах серии 1526, элемент задержки выполнен на RC цепочке.

Из известных автору источников информации и патентных материалов не известна совокупность признаков, сходных с совокупностью признаков заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫВОДА ИНФОРМАЦИИ | 2011 |

|

RU2451323C1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ ОШИБОК В ПАРАЛЛЕЛЬНОЙ МАГИСТРАЛИ | 2013 |

|

RU2524854C1 |

| Резервированное устройство | 1982 |

|

SU1102068A1 |

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

| Мажоритарно-резервированный интерфейс памяти | 1980 |

|

SU953639A1 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| Резервированное оперативное запоминающее устройство | 1987 |

|

SU1471225A1 |

Изобретение относится к вычислительной технике и автоматике. Техническим результатом является повышение надежности и сбоеустойчивости. В устройство введены второй и третий регистры, группа мажоритарных элементов, число которых определяется количеством разрядов информационного входа устройства, информационные входы второго и третьего регистров соединены с соответствующими информационными входами устройства, информационные выходы первого регистра соединены с первыми входами мажоритарных элементов, информационные выходы второго регистра соединены со вторыми входами мажоритарных элементов, информационные выходы третьего регистра соединены с третьими входами мажоритарных элементов, выходы которых соединены с входами блока сопряжения, второй выход дешифратора адреса соединен с входом запись второго регистра, третий выход дешифратора адреса соединен с входом запись третьего регистра и с входом элемента задержки. 1 з.п. ф-лы, 1 ил.

1. Устройство для вывода информации, содержащее дешифратор адреса, блок сравнения, регистр, элемент задержки, элемент И, блок сопряжения, информационные входы устройства соединены с информационными входами регистра и с первой группой входов блока сравнения, вторая группа входов которой соединена с выходами блока сопряжения, которые являются информационными выходами устройства, выход блока сравнения соединен с первым входом элемента И, выходы которого является управляющим выходом устройства, адресные входы дешифратора являются адресными входами устройства, а выход соединен с входом запись регистра, выход элемента задержки соединен со вторым входом элемента И, отличающееся тем, что в него введены второй и третий регистры, группа мажоритарных элементов, число которых определяется количеством разрядов информационного входа устройства, информационные входы второго и третьего регистров соединены с соответствующими информационными входами устройства, информационные выходы первого регистра соединены с первыми входами мажоритарных элементов, информационные выходы второго регистра соединены со вторыми входами мажоритарных элементов, информационные выходы третьего регистра соединены с третьими входами мажоритарных элементов, выходы которых соединены с входами блока сопряжения, второй выход дешифратора адреса соединен с входом запись второго регистра, третий выход дешифратора адреса соединен с входом запись третьего регистра и с входом элемента задержки.

2. Устройство по п.1, отличающееся тем, что в него введен второй элемент И и элемент ИЛИ, а блок сравнения содержит выходы «больше» и «меньше», которые соединены с входами элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом элемента задержки, выход второго элемента И является сигнальным выходом «неисправность» устройства.

| Устройство для обработки информации | 1990 |

|

SU1758649A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМ ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2007751C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1999 |

|

RU2159952C1 |

| Устройство для ввода-вывода информации | 1989 |

|

SU1615694A2 |

| JP 2007148900, A, 14.06.2007. | |||

Авторы

Даты

2011-02-10—Публикация

2009-04-29—Подача