Группа изобретений относится к устройствам цифровой вычислительной техники, в частности к недвоичной схемотехнике, и предназначена для создания многоцелевого схемотехнического устройства - Узла Троичной Схемотехники (УТС) на основе которого реализованы троичные логические устройства, такие как троичные дешифраторы-переключатели.

Полупроводниковая интегральная схемотехника не имеет в своем арсенале эквивалента электрически изолированным обмоткам, что делает невозможным отказ от кондуктивных связей между элементами. Поэтому перенос схемных решений, используемых в узлах и устройствах ЦВМ "Сетунь", в среду полупроводниковой интегральной электроники требует специфической схемотехники.

Задача, решаемая предлагаемой группой изобретений, направлена на создание универсального схемотехнического узла, применение которого обеспечит реализацию логических и операционных устройств цифровой техники, использующей симметричную троичную систему «-1,0,+1», средствами интегральных полупроводниковых технологий.

Наиболее близким техническим решением к заявляемой группе изобретений является Пороговый Элемент Троичной Логики (ПЭТЛ) [1](RU 2394366 C1,H03K19/00, 10.07.2010), выполненный на основе полупроводниковых интегральных технологий и представляющий собой функциональный аналог элементов ЦВМ "Сетунь", выполненных средствами электромагнитной техники [2,3,4]. Однако, будучи функциональным аналогом, ПЭТЛ не является схемотехническим аналогом элементов ЦВМ "Сетунь". Чтобы реализовать на ПЭТЛ логические и операционные узлы "Сетуни", недостаточно просто заменить элементы "Сетуни" на ПЭТЛ. Известная группа изобретений имеет ограниченные функциональные возможности, так как позволяет воспроизводить двухвходовую схему «И» и троичный сумматор на базе порогового элемента троичной логики. Реализации других устройств троичной логики на базе ПЭТЛ известная группа изобретений не раскрывает.

Техническим результатом предлагаемой группы изобретений является расширение функциональных возможностей троичных логических и операционных устройств в среде полупроводниковых интегральных технологий, обеспечивающих выполнение функций троичных дешифраторов-переключателей разной разрядности.

Раскрытие изобретения

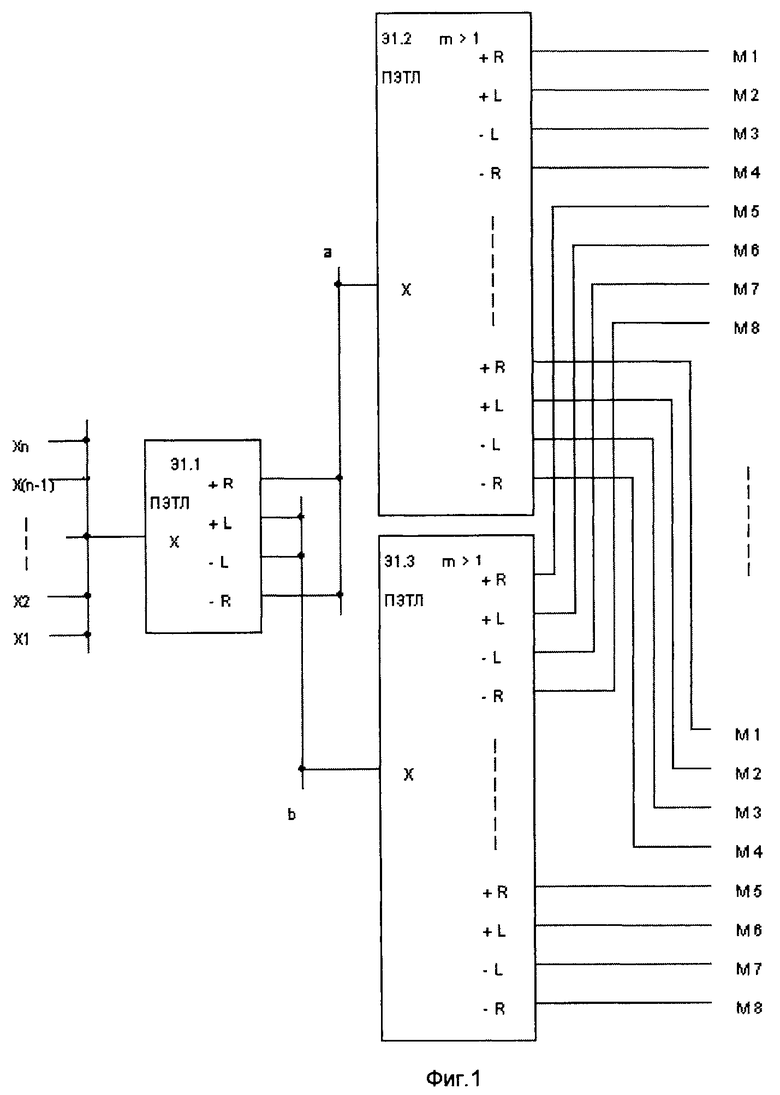

Первым аспектом группы изобретений является создание "Узла троичной схемотехники", содержащего три пороговых элемента троичной логики. Узел троичной схемотехники (УТС) содержит три пороговых элемента троичной логики (ПЭТЛ), при этом вход первого ПЭТЛ соединен входной шиной узла, третий и четвертый выходы через первую сборку и первый и второй выходы через вторую сборку первого ПЭТЛ соединены с входами второго и третьего ПЭТЛ соответственно, выходы которых являются выходами узла троичной схемотехники, причем одна группа выходов второго ПЭТЛ и одна группа выходов третьего ПЭТЛ образуют одну группу выходов узла троичной схемотехники.

Вторым аспектом группы изобретений является создание устройства "Одноразрядный дешифратор-переключатель на три направления", который содержит узел троичной схемотехники (УТС) и переключатель, включающий семь пороговых элементов троичной логики (ПЭТЛ), причем первый ПЭТЛ имеет три группы выходов. Вход данных первого ПЭТЛ является входом данных дешифратора-переключателя, управляющий вход которого является входом УТС. Первый положительный R выход первого ПЭТЛ через сборку с четвертым и восьмым выходами УТС соединен с входом второго ПЭТЛ. Первый отрицательный R выход первого ПЭТЛ через сборку с первым и пятым выходами УТС соединен с входом третьего ПЭТЛ. Второй положительный R выход первого ПЭТЛ через сборку с седьмым выходом УТС соединен с входом четвертого ПЭТЛ. Второй отрицательный R выход первого ПЭТЛ через сборку со вторым выходом УТС соединен с входом пятого ПЭТЛ. Третий положительный R выход первого ПЭТЛ через сборку с третьим выходом УТС соединен с входом шестого ПЭТЛ. Третий отрицательный R выход первого ПЭТЛ через сборку с шестым выходом УТС соединен с входом седьмого ПЭТЛ. Попарно соединенные положительный R выход второго и отрицательный R выход третьего, положительный R выход четвертого и отрицательный R выход пятого, положительный R выход шестого и отрицательный R выход седьмого ПЭТЛ являются с первого по третий выходами одноразрядного дешифратора-переключателя на три направления, причем положительные и отрицательные L выходы всех ПЭТЛ объединены с положительными R выходами третьего, пятого и седьмого ПЭТЛ, отрицательными R выходами второго, четвертого и шестого ПЭТЛ и подключены к земляной шине.

Третьим аспектом изобретения является создание устройства "двухразрядный дешифратор-переключатель на девять направлений", который содержит два узла троичной схемотехники (УТС) и девятнадцать пороговых элементов троичной логики (ПЭТЛ), причем первый ПЭТЛ имеет девять групп выходов. Два управляющих входа дешифратора-переключателя соединены с входами первого и второго УТС соответственно, каждый из которых имеет три группы по восемь выходов. Первый и пятый выходы первой группы первого УТС через сборку со вторым выходом второй группы второго УТС и четвертым отрицательным R выходом первого ПЭТЛ соединен с входом девятого ПЭТЛ. Второй выход первой группы выходов первого УТС через сборку со вторым выходом первой группы выходов второго УТС и первым отрицательным R выходом первого ПЭТЛ соединен с входом третьего ПЭТЛ. Третий выход первой группы первого УТС через сборку с седьмым выходом третьей группы второго УТС и седьмым положительным R выходом первого ПЭТЛ соединен с входом четырнадцатого ПЭТЛ. Четвертый и восьмой выходы первой группы первого УТС соединены через сборку с седьмым выходом второй группы второго УТС и четвертым положительным R выходом первого ПЭТЛ и входом восьмого ПЭТЛ. Шестой выход первой группы первого УТС соединен через сборку со вторым выходом третьей группы второго УТС и седьмым отрицательным R выходом первого ПЭТЛ и с входом пятнадцатого ПЭТЛ. Седьмые выходы первой группы первого и второго УТС через сборку с первым положительным R выходом первого ПЭТЛ соединены с входом второго ПЭТЛ, первый и пятый выходы вторых групп первого и второго УТС через сборку с пятым отрицательным R выходом первого ПЭТЛ соединены с входом одиннадцатого ПЭТЛ. Второй выход второй группы первого УТС через сборку с первым и пятым выходами первой группы второго УТС и вторым отрицательным R выходом первого ПЭТЛ соединен с входом пятого ПЭТЛ. Третьи выходы вторых групп первого и второго УТС через сборку с девятым положительным R выходом первого ПЭТЛ соединены с входом восемнадцатого ПЭТЛ. Седьмой выход второй группы первого УТС через сборку с четвертым и восьмым выходами первой группы второго УТС и вторым положительным R выходом первого ПЭТЛ соединены с входом четвертого ПЭТЛ. Шестой выход второй группы первого УТС через сборку с первым и пятым выходами третьей группы второго УТС и восьмым отрицательным R выходом первого ПЭТЛ соединены с входом семнадцатого ПЭТЛ. Первый и пятый выходы третьей группы первого УТС через сборку с шестым выходом второй группы второго УТС и шестым отрицательным R выходом первого ПЭТЛ соединены с входом тринадцатого ПЭТЛ. Второй выход третьей группы первого УТС через сборку с шестым выходом первой группы второго УТС и третьим отрицательным R выходом первого ПЭТЛ соединен с входом седьмого ПЭТЛ. Восьмой выход второй группы первого УТС через сборку с четвертым выходом третьей группы первого и четвертым и восьмым выходами второй группы второго УТС и пятым положительным R выходом первого ПЭТЛ соединены с входом десятого ПЭТЛ. Третий выход третьей группы первого УТС через сборку с четвертым и восьмым выходами третьей группы второго УТС и восьмым положительным R выходом первого ПЭТЛ соединены с входом шестнадцатого ПЭТЛ. Шестой выход третьей группы первого УТС через сборку с шестым выходом третьей группы второго УТС и девятым отрицательным R выходом первого ПЭТЛ соединен с входом девятнадцатого ПЭТЛ. Седьмой выход третьей группы первого УТС через сборку с третьим выходом первой группы второго УТС и третьим положительным R выходом первого ПЭТЛ соединен с входом шестого ПЭТЛ. Четвертый выход второй группы и восьмой выход третьей группы первого УТС через сборку с третьим выходом третьей группы второго УТС и шестым положительным R выходом первого ПЭТЛ соединен с входом двенадцатого ПЭТЛ. Вход данных дешифратора-переключателя соединен с входом первого ПЭТЛ, положительный R выход 2j-го и отрицательный R выход (2j+1)-го ПЭТЛ объединены и являются j-выходом дешифратора-переключателя, где j=1,2…9, отрицательные и положительные L выходы с первого по девятнадцатый ПЭТЛ объединены с отрицательным выходом 2j-го и положительным выходом (2j+1)-го ПЭТЛ и подключены к земляной шине.

На фиг.1 представлен Узел Троичной Схемотехники (УТС), который содержит три Пороговых Элемента Э1.1, Э1.2,Э1.3 Троичной Логики (ПЭТЛ). Вход X ПЭТЛ Э1.1 является входом УТС. Третий и четвертый выходы ПЭТЛ Э1.1: +R, -R соединены со входом X ПЭТЛ Э1.2 через первую сборку (a); первый и второй выходы ПЭТЛ Э1.1: +L, -L - со входом X ПЭТЛ Э1.3 через вторую сборку (b). Выходы ПЭТЛ Э1.2: +R, +L, -R, -L соединены соответственно с выходами УТС: M 1, M 2, M 3, M 4, а выходы ПЭТЛ Э1.3: +R, +L, -R, -L соединены соответственно с выходами УТС: M 5, M 6, M 7, M 8. Поскольку ПЭТЛ Э1.2 и Э1.3 могут иметь более одной группы выходов: +R, +L, -R, -L, УТС также может иметь более одной группы выходов. Значения на одноименных выходах любой группы тождественны. Чтобы не загромождать рисунков, в дальнейшем УТС будет изображаться в виде прямоугольника, имеющего вход X слева и выходы: M 1, M 2, M 3, M 4, M 5, M 6, M 7, M 8 - справа. Если УТС имеет более одной группы выходов, внутри прямоугольника будет указано: m=<число групп>.

Описание УТС будет основано на описании ПЭТЛ из [1]: на входы X каждого из трех ПЭТЛ, входящих в состав УТС, поступают, вообще говоря, n дискретных сигналов (для ПЭТЛ Э1.2 и Э1.3 n=2). Каждый сигнал может иметь одно из трех значений: +1,0 или -1.

n = n+1 + n-1 + n0

где n+1 - число сигналов, текущие значения которых +1

n-1 - число сигналов, текущие значения которых -1

n0 - число сигналов, текущие значения которых 0

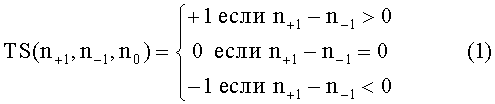

Выполняемое на входе ПЭТЛ преобразование трехзначных сигналов Xi описывается функцией TS(n+1,n-1,n0), определяемой выражением

Троичная переменная TS(n+1,n-1,n0) представляется на 4 выходах ПЭТЛ: +R, +L, -R, -L двумя парами ее двузначных компонент - двухразрядных двоичных значений [+R,-R] и [+L,-L]. Соответствие значений двузначных компонент +R, +L, -R, -L, формируемым на входе ПЭТЛ, значениям TS(n+1,n-1,n0) дано в таблице 1.

Соотношение (1) определяет значения на сборках a, b и на выходах УТС: M 1, M 2, M 3, M 4, M 5, M 6, M 7, M 8. Эти значения содержатся в таблице 2.

Сборки,

Выходы

Таким образом УТС преобразует поступающие на его вход сигналы Xi в соответствии с выражением (1) и формирует на любой из групп выходов: M 1, M 2, M 3, M 4, M 5, M 6, M 7, M 8 набор приведенных таблице 2 значений. Включая в параллель выходы М1-М8, можно сформировать различные троичные и двоичные значения для реализации различных логических и операционных устройств.

Ниже приведены примеры реализации на базе УТС троичных дешифраторов-переключателей разной разрядности и на разное число направлений.

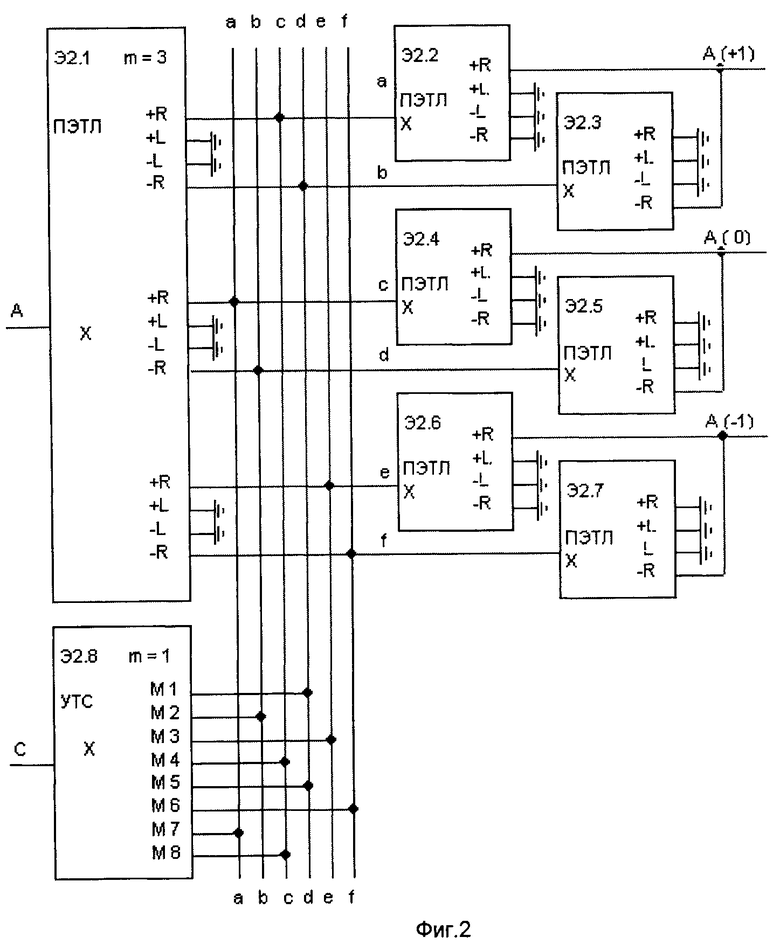

На Фиг.2 показан одноразрядный дешифратор-переключатель на три направления, выполненный с использованием одного узла троичной схемотехники (УТС) и семи пороговых элементов троичной логики (ПЭТЛ). Переключатель, выполненный на ПЭТЛ: Э2.1, Э2.2 Э2.3, Э2.4, Э2.5, Э2.6, Э2.7, имеет один вход и три выхода. Дешифратор выполнен на УТС (Э2.8). Вход C дешифратора-управляющий. Формируемое на нем одноразрядное троичное значение определяет, на какой из трех выходов A(+1), A(0), A(-1) поступит троичное значение A со входа данных дешифратора-переключателя.

ПЭТЛ Э2.1 разделяет троичную переменную A на ее двузначные компоненты. Он имеет три (m=3) группы тождественных выходов: +R,-R,+L,-L. Используются только R выходы. Выходы +R соединены со входами ПЭТЛ Э2.2, Э2.4, Э2.6, а выходы -R - со входами ПЭТЛ Э2.3, Э2.5, Э2.7. На входы ПЭТЛ Э2.2, Э2.4, Э2.6 поступают положительные значения (+R) двузначных компонент троичной переменной A, а на входы ПЭТЛ Э2.3, Э2.5, Э2.7 - отрицательные (-R). Выходы ПЭТЛ Э2.2, Э2.3; Э2.4, Э2.5 и Э2.6, Э2.7 попарно соединены и являются выходами переключателя: A(+1), A(0), A(-1).

Дешифрация значения C осуществляются путем соответствующего подсоединения выходов УТС к сборкам: a, b,c, d, e, f. Это отражено как на Фиг.2, так и в таблице 3, где для каждой из сборок (столбец 1) указаны подключенные к ней выходы УТС (столбец 2) и значения на сборках, определенные из выражения (1) для различных троичных значений C (столбцы 3,4,5).

При таком подсоединении для каждого из трех значений на входе C имеется пара сборок, на которых будет формироваться значение 0, в то время как для остальных двух значений C на одной из сборок пары будут формироваться +1, а на другой - (-1). Сборки: a, c, e соединены соответственно со входами четных ПЭТЛ переключателя: Э2.2, Э2.4, Э2.6. На них с выходов Э2.8 поступают положительные компоненты A (+R). Сборки: b, d, f соединены соответственно со входами нечетных ПЭТЛ переключателя: Э2.3, Э2.5, Э7. На них с выходов Э2.8 поступают отрицательные компоненты A (-R). Только в том случае, когда от сборок на входы пары ПЭТЛ поступают 0, соответствующие компоненты троичной переменной A с входов пары ПЭТЛ пройдут на выходы этих ПЭТЛ и, после объединения сформируют на соответствующем выходе переключателя троичное значение, тождественное входному. На остальных парах ПЭТЛ прохождение положительной компоненты A (+R) блокируется (запрещается) -1, а прохождение отрицательной компоненты A (-R) блокируется (запрещается) +1, поступающих от сборок. В результате на остальных 2 выходах переключателя будут 0. Поскольку межэлементные сигналы в описываемой схемотехнике являются токовыми, все незадействованные выходы элементов заземлены.

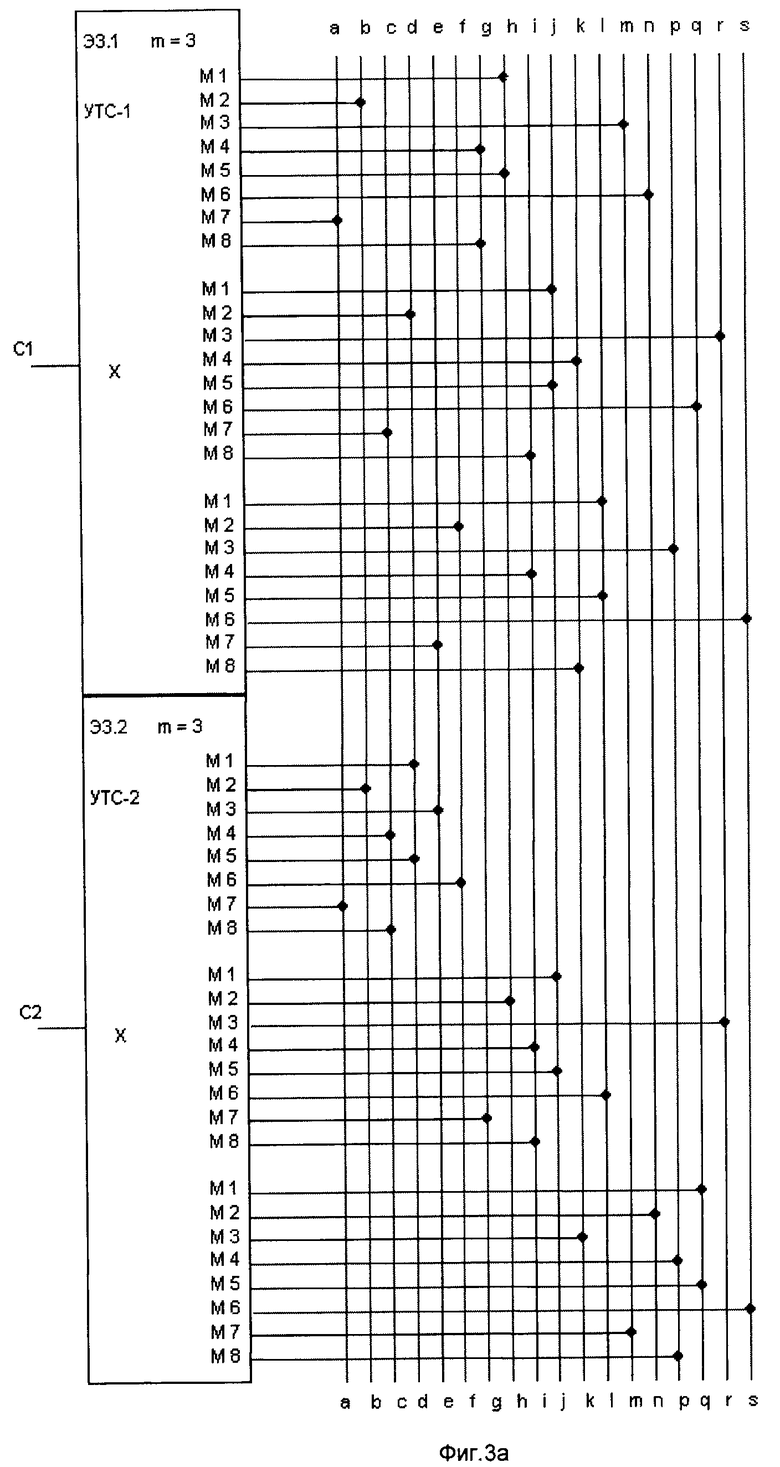

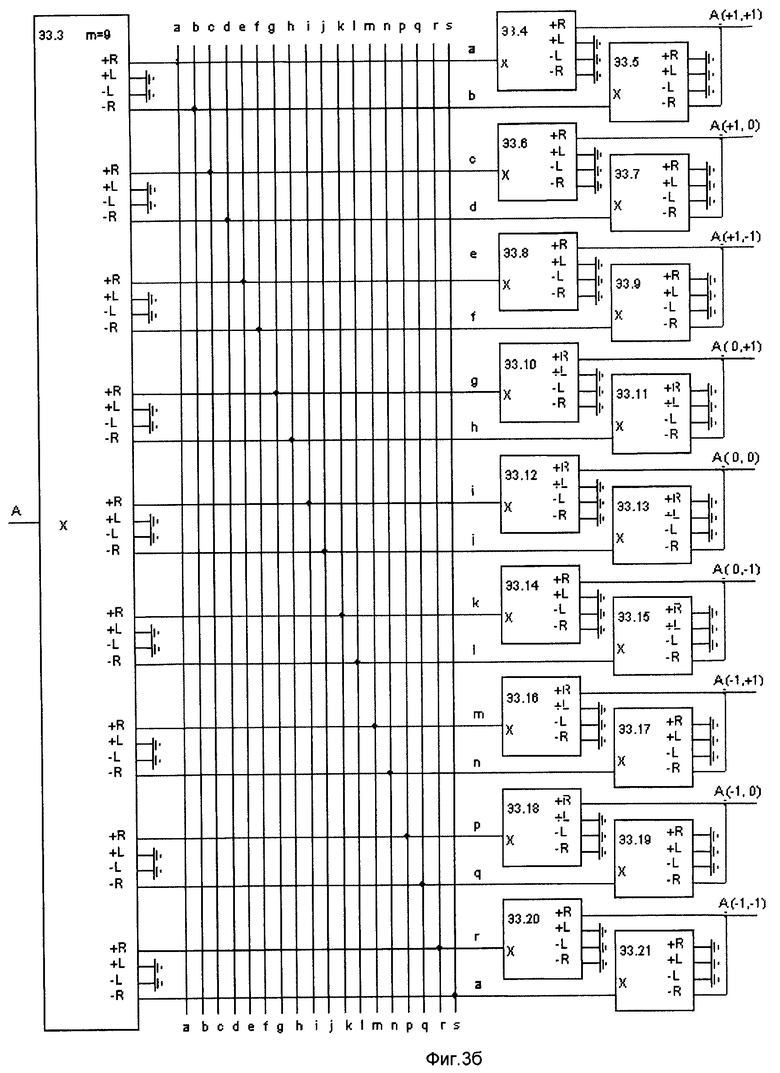

На фиг.3а и 3б представлен двухразрядный дешифратор-переключатель на девять направлений, выполненного с использованием 2 узлов троичной схемотехники (УТС): Э3.1, Э3.2 (фиг.3а) и 19-и пороговых элементов троичной логики (ПЭТЛ) (фиг.3б): Э3.3, Э3.4, Э3.5, Э3.6, Э3.7, Э3.8, Э3.9, Э3.10, Э3.11, Э2.12, Э3.13, Э3.14, Э3.15, Э3.16, Э3.17, Э3.18, Э3.19, Э3.20, Э3.21.

Входы C1,C2 - управляющие. Формируемые на них пары троичных значений, определяют, на какой из девяти выходов: A(+1,+1), A(+1,0), A(+1,-1), A(0,+1), A(0,0), A(0,-1), A(-1,+1), A(-1,0), A(-1,-1) дешифратора-переключателя поступит троичное значение со входа данных A.

ПЭТЛ Э3.3 разделяет троичную переменную A на ее двузначные компоненты. Он имеет девять (m=9) тождественных групп выходов +R,-R,+L,-L. Используются только R выходы. Выходы +R соединены со входами четных ПЭТЛ: Э3.4, Э3.6, Э2.8, Э3.10, Э3.12, Э3.14, Э3.16, Э3.18 и Э3.20, а выходы -R - со входами нечетных ПЭТЛ: Э3.5, Э3.7, Э2.9, Э3.11, Э3.13, Э3.15, Э3.17, Э3.19 и Э3.21. На входы четных ПЭТЛ поступают положительные значения (+R) двузначных компонент троичной переменной A, а на входы нечетных - отрицательные (-R). Выходы соответствующих четных и нечетных ПЭТЛ попарно объединены и являются выходами дешифратора-переключателя: A(+1,+1), A(+1,0), A(+1,-1), A(0,+1), A(0,0), A(0,-1), A(-1,+1), A(-1,0), A(-1,-1).

Дешифрация троичных значений, формируемых на управляющих входах C1, C2, осуществляются путем соответствующего подсоединения выходов двух УТС (Э3.1, 3.2) к 18-и сборкам: a, b, c, d, e, f, g, h, i, j, k, l, m, n, p, q, r, s. Это подключение отражено как на Фиг.3а, так и в таблице 4, где для каждой из сборок (столбец 1) указаны подключенные к ней выходы УТС (столбец 2) и значения на сборках, полученные из выражения (1) при различных комбинациях троичных значений на C1,C2 (столбцы 3 - 11). В столбце 2 первая цифра означает номер УТС (1 или 2), выход которого подключен к сборке, затем, после тире через запятую, указаны сами выходы (выход).

При таком подсоединении, как это видно из таблицы 4, для каждой пары значений C1,C2 можно найти пару сборок, на которых будут 0, в то время как для остальных восьми значений C1,C2 на одной из сборок пары будут +1, а на другой - (-1). Сборки связывают дешифратор с переключателем (Фиг.3б), причем, сборки: a, c, e, g, i, k, n, p, r соединены соответственно со входами четных ПЭТЛ переключателя: Э3.4, Э3.6, Э3.8 Э3.10, Э3.12, Э3.14, Э3.16, Э3.18, Э3.20, а сборки: b, d, f, h, j, l, n, q, s - со входами нечетных ПЭТЛ переключателя: Э3.5, Э3.7, Э3.9 Э3.11, Э3.13, Э3.15, Э3.17, Э3.19, Э3.21. На входы четных ПЭТЛ переключателя поступают с выходов Э3.3 положительные двузначные компоненты (+R), а на входы нечетных ПЭТЛ переключателя поступают с выходов Э3.3 отрицательные двузначные компоненты (-R). При любом из девяти значений C1,C2 на входы единственной пары ПЭТЛ поступают 0 и соответствующие компоненты троичной переменной A проходят на выходы этих ПЭТЛ, где, после объединения, формируют на одном из выходов переключателя: A(+1,+1), A(+1,0), A(+1,-1), A(0,+1), A(0,0), A(0,-1), A(-1,+1), A(-1,0), A(-1,-1) троичное значение, тождественное входному. На остальных парах ПЭТЛ прохождение положительных компонент (+R) блокируется (запрещается) -1, а отрицательных компонент (-R) - +1, поступающих от сборок. В результате на остальных восьми выходах дешифратора-переключателя будут 0. Поскольку межэлементные сигналы в описываемой схемотехнике являются токовыми, все незадействованные выходы элементов заземлены.

Литература

1. Маслов С.П. Пороговый элемент троичной логики и устройства на его основе. Патент РФ на изобретение: RU № 2278469 C1. Опубликовано: 10.07.2010.

2. Брусенцов Н.П., Маслов С.П., Розин В.П., Тишулина А.М. Малая цифровая вычислительная машина "Сетунь". - М.: Изд-во Московского университета, 1965. 145 с.

3. Брусенцов Н.П. Пороговая реализация трехзначной логики электромагнитными средствами. // Вычислительная техника и вопросы кибернетики. Вып.9. - М.: Изд-во Моск. ун-та, 1972. С.3-35. (Текст статьи в формате.pdf содержится на прилагаемом МЧН, а также доступен по запросу: mailto:spmaslov@gmail.com).

4. Брусенцов Н.П. Электромагнитные цифровые устройства с однопроводной передачей трехзначных сигналов. - В кн.: Магнитные элементы автоматики и вычислительной техники. XIV Всесоюзное совещание (Москва, сентябрь 1972 г.). М., "Наука", 1972, с. 242 - 244.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ТРОИЧНОГО СЛОЖЕНИЯ И ВЫЧИТАНИЯ | 2017 |

|

RU2645279C1 |

| ТРОИЧНЫЙ D-ТРИГГЕР (ВАРИАНТЫ) | 2012 |

|

RU2510129C1 |

| ТРОИЧНЫЙ РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 2015 |

|

RU2585263C1 |

| ТРОИЧНЫЙ Т-ТРИГГЕР И ТРОИЧНЫЙ РЕВЕРСИВНЫЙ СЧЕТЧИК НА ЕГО ОСНОВЕ | 2014 |

|

RU2562370C2 |

| УСТРОЙСТВО ТРОИЧНОЙ СХЕМОТЕХНИКИ НА ТОКОВЫХ ЗЕРКАЛАХ | 2017 |

|

RU2648565C1 |

| ТРОИЧНЫЙ ПОЛНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ СУММАТОР (ВАРИАНТЫ) | 2016 |

|

RU2616887C1 |

| ТРОИЧНЫЙ ПОРАЗРЯДНЫЙ УМНОЖИТЕЛЬ | 2016 |

|

RU2631166C1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ НА ТОКОВЫХ ЗЕРКАЛАХ | 2016 |

|

RU2618901C1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| ТРОИЧНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 2017 |

|

RU2642408C1 |

Изобретения относятся к устройствам цифровой вычислительной техники, в частности к недвоичной схемотехнике и предназначены для создания многоцелевого схемотехнического устройства - узла троичной схемотехники (УТС), на основе которого реализованы троичные логические устройства, такие как троичные дешифраторы-переключатели. Техническим результатом является обеспечение возможности выполнения троичными логическими и операционными устройствами функций троичных дешифраторов-переключателей разной разрядности. Узел троичной схемотехники содержит три пороговых элемента троичной логики. 3 н.п. ф-лы, 4 ил., 4 табл.

1. Узел троичной схемотехники содержит три пороговых элемента троичной логики (ПЭТЛ), причем вход первого ПЭТЛа соединен с входной шиной узла, третий и четвертый выходы через первую сборку и первый и второй выходы через вторую сборку первого ПЭТЛа соединены с входами второго и третьего ПЭТЛа соответственно, выходы которых являются выходами узла троичной схемотехники, причем одна группа выходов второго ПЭТЛа и одна группа выходов третьего ПЭТЛа образуют одну группу выходов узла троичной схемотехники.

2. Одноразрядный дешифратор-переключатель на три направления содержит узел троичной схемотехники (УТС) по п.1 и переключатель, включающий семь пороговых элементов троичной логики (ПЭТЛ), причем первый ПЭТЛ имеет три группы выходов, а вход первого ПЭТЛа является входом данных дешифратора-переключателя, управляющий вход которого является входом УТС, первый положительный R выход первого ПЭТЛа через сборку с четвертым и восьмым выходами УТС соединен с входом второго ПЭТЛа, первый отрицательный R выход первого ПЭТЛа через сборку с первым и пятым выходами УТС соединен с входом третьего ПЭТЛа, второй положительный R выход первого ПЭТЛа через сборку с седьмым выходом УТС соединен с входом четвертого ПЭТЛа, второй отрицательный R выход первого ПЭТЛа через сборку со вторым выходом УТС соединен с входом пятого ПЭТЛа, третий положительный R выход первого ПЭТЛа через сборку с третьим выходом УТС соединен с входом шестого ПЭТЛа, третий отрицательный R выход первого ПЭТЛа через сборку с шестым выходом УТС соединен с входом седьмого ПЭТЛа, причем попарно соединенные положительный R выход второго и отрицательный R выход третьего, положительный R выход четвертого и отрицательный R выход пятого, положительный R выход шестого и отрицательный R выход седьмого ПЭТЛов являются с первого по третий выходами одноразрядного дешифратора-переключателя на три направления, причем положительные и отрицательные L выходы всех ПЭТЛов объединены с положительными R выходами третьего, пятого и седьмого ПЭТЛов, отрицательными R выходами второго, четвертого и шестого ПЭТЛов и подключены к земляной шине.

3. Двухразрядный дешифратор-переключатель на девять направлений содержит два узла троичной схемотехники (УТС) по п.1 и девятнадцать пороговых элементов троичной логики (ПЭТЛ), причем первый ПЭТЛ имеет девять групп выходов, причем два управляющих входа дешифратора-переключателя соединены с входами первого и второго УТС соответственно, каждый из которых имеет три группы по восемь выходов, при этом первый и пятый выходы первой группы первого УТС через сборку со вторым выходом второй группы второго УТС и четвертым отрицательным R выходом первого ПЭТЛа соединены с входом девятого ПЭТЛа, второй выход первой группы выходов первого УТС через сборку со вторым выходом первой группы выходов второго УТС и первым отрицательным R выходом первого ПЭТЛа соединен с входом третьего ПЭТЛа, третий выход первой группы первого УТС через сборку с седьмым выходом третьей группы второго УТС и седьмым положительным R выходом первого ПЭТЛа соединен с входом четырнадцатого ПЭТЛа, четвертый и восьмой выходы первой группы первого УТС соединены через сборку с седьмым выходом второй группы второго УТС и четвертым положительным R выходом первого ПЭТЛа и входом восьмого ПЭТЛа, шестой выход первой группы первого УТС соединен через сборку со вторым выходом третьей группы второго УТС и седьмым отрицательным R выходом первого ПЭТЛа и с входом пятнадцатого ПЭТЛа, седьмые выходы первой группы первого и второго УТС через сборку с первым положительным R выходом первого ПЭТЛа соединены с входом второго ПЭТЛа, первый и пятый выходы вторых групп первого и второго УТС через сборку с пятым отрицательным R выходом первого ПЭТЛа соединены с входом одиннадцатого ПЭТЛа, второй выход второй группы первого УТС через сборку с первым и пятым выходами первой группы второго УТС и вторым отрицательным R выходом первого ПЭТЛа соединен с входом пятого ПЭТЛа, третьи выходы вторых групп первого и второго УТС через сборку с девятым положительным R выходом первого ПЭТЛа соединены с входом восемнадцатого ПЭТЛа, седьмой выход второй группы первого УТС через сборку с четвертым и восьмым выходами первой группы второго УТС и вторым положительным R выходом первого ПЭТЛа соединены с входом четвертого ПЭТЛа, шестой выход второй группы первого УТС через сборку с первым и пятым выходами третьей группы второго УТС и восьмым отрицательным R выходом первого ПЭТЛа соединены с входом семнадцатого ПЭТЛа, первый и пятый выходы третьей группы первого УТС через сборку с шестым выходом второй группы второго УТС и шестым отрицательным R выходом первого ПЭТЛа соединены с входом тринадцатого ПЭТЛа, второй выход третьей группы первого УТС через сборку с шестым выходом первой группы второго УТС и третьим отрицательным R выходом первого ПЭТЛа соединен с входом седьмого ПЭТЛа, восьмой выход второй группы первого УТС через сборку с четвертым выходом третьей группы первого и четвертым и восьмым выходами второй группы второго УТС и пятым положительным R выходом первого ПЭТЛа соединен с входом десятого ПЭТЛа, третий выход третьей группы первого УТС через сборку с четвертым и восьмым выходами третьей группы второго УТС и восьмым положительным R выходом первого ПЭТЛа соединен с входом шестнадцатого ПЭТЛа, шестой выход третьей группы первого УТС через сборку с шестым выходом третьей группы второго УТС и девятым отрицательным R выходом первого ПЭТЛа соединен с входом девятнадцатого ПЭТЛа, седьмой выход третьей группы первого УТС через сборку с третьим выходом первой группы второго УТС и третьим положительным R выходом первого ПЭТЛа соединен с входом шестого ПЭТЛа, четвертый выход второй группы и восьмой выход третьей группы первого УТС через сборку с третьим выходом третьей группы второго УТС и шестым положительным R выходом первого ПЭТЛа соединены с входом двенадцатого ПЭТЛа, вход данных дешифратора-переключателя соединен с входом первого ПЭТЛа, положительный R выход 2j-го и отрицательный R выход (2j+1)-го ПЭТЛов объединены и являются j-выходом дешифратора - переключателя, где j=1, 2…9, отрицательные и положительные L выходы с первого по девятнадцатый ПЭТЛов объединены с отрицательным выходом 2j-го и положительным выходом (2j+1)-го ПЭТЛа и подключены к земляной шине.

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| УСТРОЙСТВО КОММУТАЦИИ | 1990 |

|

RU2010425C1 |

| Дешифратор троичного кода 1,0,1 | 1978 |

|

SU748407A1 |

| JP 56153841 A, 28.11.1981 | |||

| Инструмент для выделения и отрезания нерва | 1984 |

|

SU1183084A1 |

Авторы

Даты

2012-09-10—Публикация

2011-08-26—Подача