Изобретение относится к устройствам цифровой вычислительной техники, в частности к недвоичной технике, и предназначено для создания реализуемого в среде полупроводниковой интегральной электроники троичного реверсивного регистра сдвига.

Известной успешной реализацией недвоичных цифровых устройств являются троичные ЦВМ "Сетунь" и "Сетунь-70" [1, 2]. Логические элементы этих ЦВМ выполнены на основе электромагнитной техники [8, 9], имеют малое быстродействие, большие потребляемую мощность и размеры. Устройства на таких элементах не могут быть реализованы в среде современной полупроводниковой интегральной электроники.

Известен функциональный аналог элементов ЦВМ "Сетунь" "Пороговый Элемент Троичной Логики" (ПЭТЛ), реализуемый в среде полупроводниковой интегральной электроники [3]. На ПЭТЛ, используя ПЭТЛ-схемотехнику [7], можно создавать троичные цифровые устройства. Ассортимент средств, которыми в настоящее время располагает ПЭТЛ-схемотехника, недостаточен для создания всего спектра троичных устройств. В частности, в нем отсутствует троичный реверсивный регистр сдвига.

Задача, решаемая заявляемым изобретением, направлена на пополнение ассортимента средств ПЭТЛ-схемотехники троичным реверсивным регистром сдвига, благодаря чему обеспечивается создание в среде интегральной полупроводниковой электроники более широкого набора логических и операционных устройств, работающих в симметричной троичной системе с цифрами -1, 0, +1.

Наиболее близкими техническими решениями к заявляемому изобретению являются группы изобретений: "Пороговый Элемент Троичной Логики и устройства на его основе" [3], "Узел Троичной схемотехники и дешифраторы-переключатели на его основе" [4] и "Троичный D-триггер (варианты)" [5].

Известные группы изобретений поддерживает реализацию ограниченного числа троичных устройств:

Комбинационные схемы: троичная схема "И", троичный полусумматор, троичные дешифраторы и троичные переключатели.

Схемы с памятью: четыре варианта троичных D-триггеров с управлением по уровню и по фронту сигнала.

Реализацию троичного реверсивного регистра сдвига известные группы изобретений не раскрывают.

Раскрытие изобретения

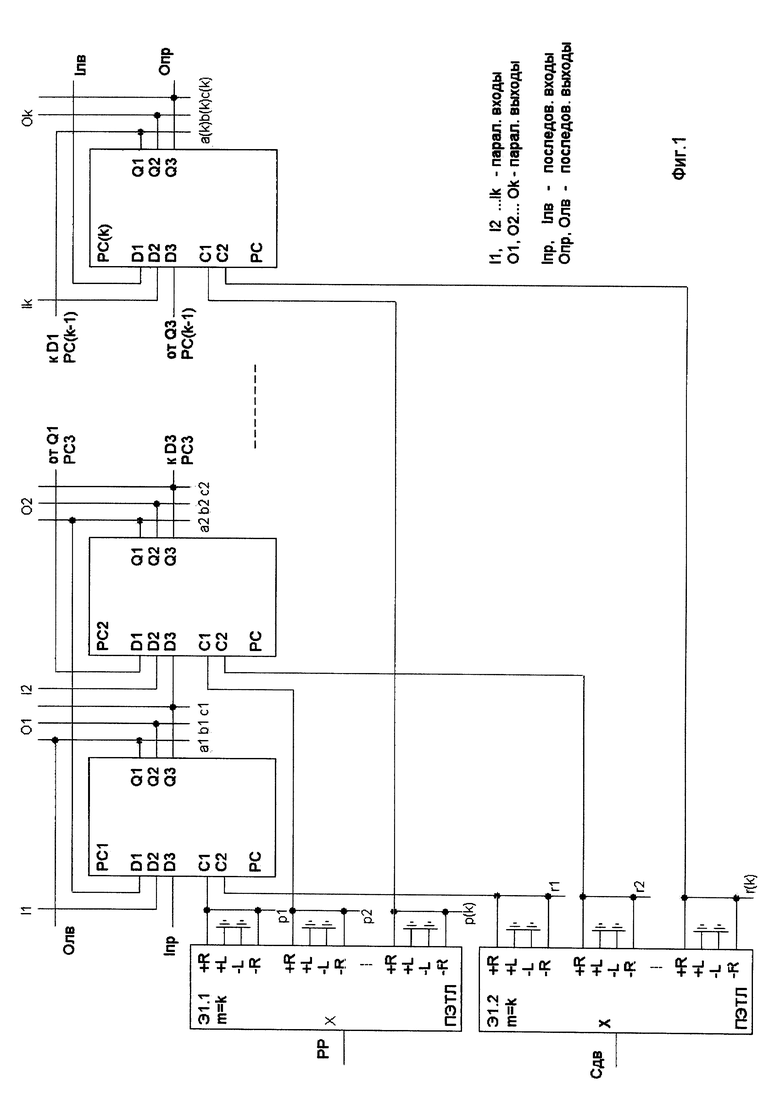

Троичный Реверсивный Регистр Сдвига (ТРРС) состоит из k Регистровых Секций (PC) и двух Пороговых Элементов Троичной Логики (ПЭТЛ), каждый из которых имеет по k групп выходов (k-число разрядов ТРРС).

Входы X первого и второго ПЭТЛ являются соответственно входами РР и Сдв ТРРС; выходы +R и -R n-й группы выходов первого ПЭТЛ через n-ю р-сборку подключены к входу C1 n-го PC, а выходы +R и -R n-й группы выходов второго ПЭТЛ через n-ю r-сборку подключены к входу С2 n-ого PC; вход D2 и выход Q2 n-го PC подключены соответственно к входу In и выходу On ТРРС (n=1…k); вход D3 первого PC является входом Iпр ТРРС и выход Q3 k-го PC является выходом Опр ТРРС; вход D1 k-го PC является входом Iлв ТРРС и выход Q1 первого PC является выходом Олв ТРРС; выход Q3 n-го PC через n-ю с-сборку подключен к входу D3 (n+1)-го PC (n=1…(k-1)); выход Q1 n-го PC через n-ю а-сборку подключен к входу D1 (n-1)-го PC (n=2…k).

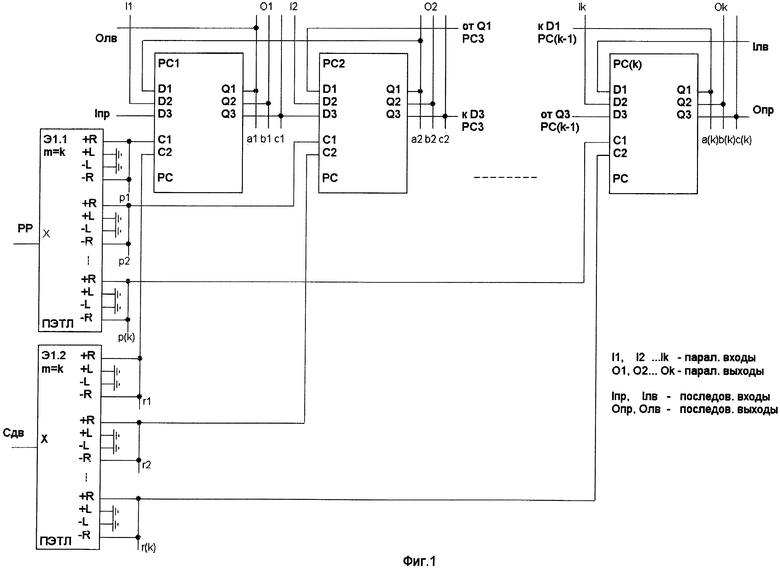

Регистровая Секция (PC) содержит девять ПЭТЛ, Узел Троичной Схемотехники (УТС) и D-Триггер (TDT), причем четвертый, шестой и восьмой ПЭТЛ имеют только выходы +R и +L, а пятый, седьмой и девятый ПЭТЛ имеют только выходы -R и -L; TDT имеет три группы выходов; входы X первого, второго и третьего ПЭТЛ являются соответственно входами D1, D2 и D3 PC; вход X УТС является входом C1 PC, а вход С TDT является входом С2 PC; выходы +R и -R первой, второй и третьей групп TDT посредством соответственно i-й, j-й и k-й сборок подключены к выходам Q1, Q2 и Q3 PC; выход +R первого ПЭТЛ и выход М7 УТС через сборку а подключены к входу X четвертого ПЭТЛ; выход -R первого ПЭТЛ и выход М2 УТС через сборку b подключены к входу X пятого ПЭТЛ; выход +R второго ПЭТЛ и выходы М4 и М8 УТС через сборку с подключены к входу X восьмого ПЭТЛ; выход -R второго ПЭТЛ и выходы M1 и М5 УТС через сборку d подключены к входу X девятого ПЭТЛ; выход +R третьего ПЭТЛ и выход М3 УТС через сборку е подключены к входу X шестого ПЭТЛ; выход -R третьего ПЭТЛ и выход М6 УТС через сборку f подключены к входу X седьмого ПЭТЛ; выходы +R четвертого, шестого и восьмого ПЭТЛ и выходы -R пятого, седьмого и девятого ПЭТЛ через сборку g подключены к входу D TDT; выходы +L и -L всех ПЭТЛ и TDT подключены к земляной шине.

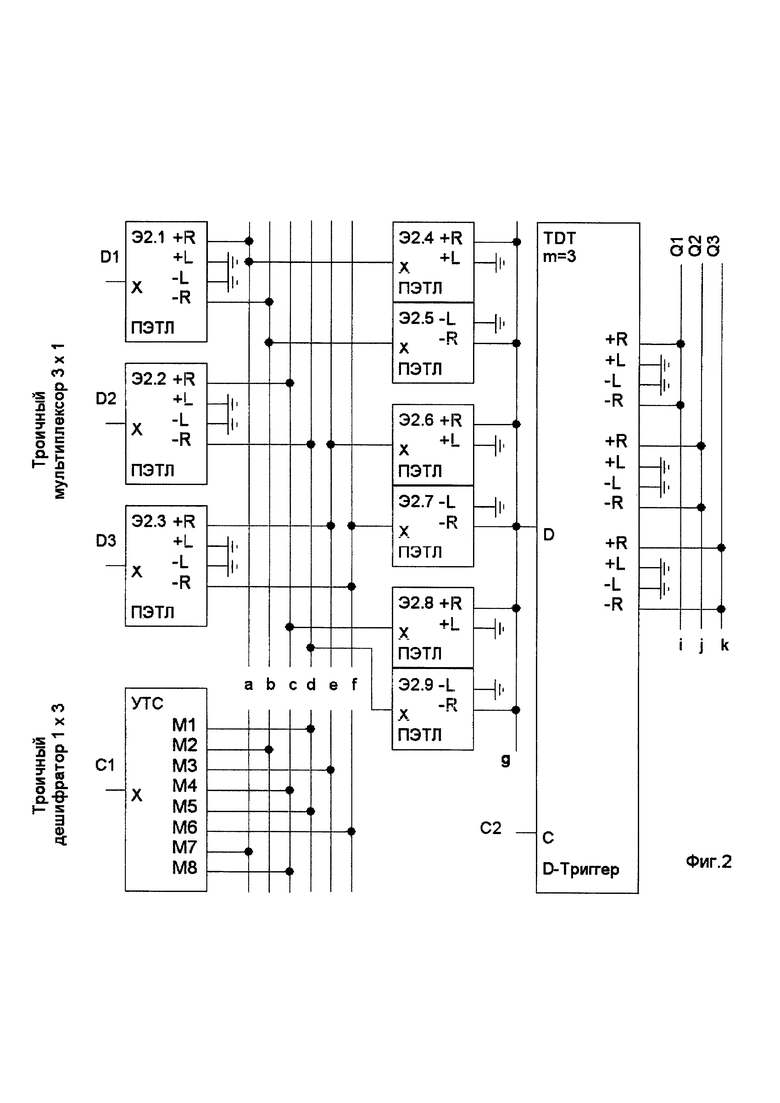

На Фиг. 1 изображен Троичный Реверсивный Регистр Сдвига (ТРРС). На Фиг. 2 представлена схема Регистровой Секции (PC) ТРРС.

Троичный Реверсивный Регистр Сдвига (ТРРС) выполнен на основе ПЭТЛ-схемотехники, под которой подразумевается совокупность элементов, узлов, правил их соединения, приемов, типовых схемных решений и изобразительных средств, поддерживающих реализацию цифровых устройств в троичной системе с цифрами +1, 0, -1.

ПЭТЛ-схемотехника появилась недавно (первый патент получен в 2009 году) и отличается от других интегральных схемотехник (ТТЛ, К-МОП, ЭСЛ). Она описана в [3, 4, 5, 6, 7]. Краткие сведения о ПЭТЛ-схемотехнике приведены ниже:

1. Троичные значения +1, 0, -1 на физическом уровне представлены дискретными токами +Iф, 0, -Iф. Эти же токи протекают в цепях межэлементных связей.

2. Пороговый Элемент Троичной Логики (ПЭТЛ) имеет 1 вход X и группу из 4-х выходов:+R, +L, -L, -R.

3. Узел Троичной Схемотехники (УТС) состоит из 3-х ПЭТЛ, имеет 1 вход X и группу из 8 выходов: М1, М2, М3, М4, М5, М6, М7, М8.

4. ПЭТЛ и УТС могут иметь более одной группы выходов. Значения на одноименных выходах групп тождественны.

5. На входах X ПЭТЛ и УТС происходит алгебраическое сложение разнонаправленных дискретных токов +IФ, и -IФ и формируется троичное значение X. Если число +IФ больше числа -IФ-Х=+1, если число +Iф меньше числа -Iф-Х=-1, если число +Iф равно числу -Iф-Х=0.

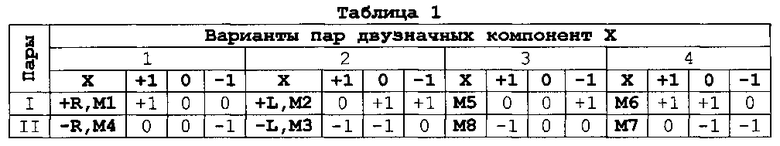

Сформированным на входах ПЭТЛ и УТС значениям X соответствуют пары двузначных компонент на их выходах. Соответствие для 4-х вариантов пар дано в Таблице 1. Варианты пар пронумерованы арабскими цифрами, компоненты в паре римскими.

Отметим, что каждая из компонент двоична: компоненты в строке I имеют значения +1 или 0; компоненты в строке II -1 или 0.

Терминология ПЭТЛ-схемотехники не устоялась. Используются сопоставимые термины из двоичных схемотехник и из лексикона "Сетуней". Во избежание недоразумений следует руководствоваться таблицами истинности и сопроводительным текстом.

Алгебраическое сложение дискретных токов на входах элементов и объединение (сборка) их выходов являются основными приемами ПЭТЛ-схемотехники. Так, объединяя выходы +R и -R ПЭТЛ или M1 и М4 УТС, получим на сборке повторение входного троичного значения, объединяя +L и -L ПЭТЛ или М2 и М3 УТС - его нециклическую инверсию, объединяя +R и +L или -R и -L ПЭТЛ-постоянные значения +1 или -1. Практикуется объединение выходов разных ПЭТЛ и УТС.

Сборки изображаются вертикальными линиями, нижние концы которых помечены буквами, а верхние (необязательно) - либо наименованием элемента, ко входу которого сборка подключена, либо названием сигнала. Как правило, слева от сборки располагаются элементы, выходы которых к ней подключены, справа - элемент, на входе которого формируется троичное значение X.

Помимо ПЭТЛ с полным набором выходов используют элементы с половинным числом выходов: либо только положительных (+R, +L), либо только отрицательных (-L, -R). Так, на Фиг. 2 у ПЭТЛ Э1.4, Э1.6, Э1.8 только положительные выходы, у ПЭТЛ Э1.5, Э1.7, Э1.9 - только отрицательные. Если у ПЭТЛ или УТС более одной группы выходов, их число m указывают под номером элемента. Если выход ПЭТЛ не используется, его соединяют с земляной шиной.

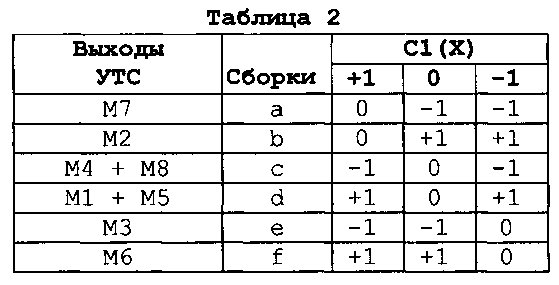

Проиллюстрируем применение ПЭТЛ-схемотехники на примере троичного дешифратора 1×3, который входит в состав PC. Дешифратор реализован на Узле Троичной Схемотехники (УТС) путем соответствующей коммутации его выходов. (На Фиг. 2 дешифратор изображен внизу слева). В зависимости от троичного значения С1 на входе X дешифратор формирует на трех парах сборок a, b; c, d и e, f троичные значения в соответствии с Таблицей 2.

Подключение выходов УТС к сборкам дано в 2-х левых столбцах.

Алгоритм заполнения ячеек таблицы следующий:

1. Задают значение С1 на входе X УТС;

2. Из Таблицы 1 берут значения на объединенных в сборки выходах УТС, соответствующие заданному С1.

3. Определяют значение на сборке и заносят его в ячейку;

4. Переходят к другому значению С1 и выполняют пп. 2 и 3.

(К сборкам а, b, е и f подключено по одному выходу УТС и в ячейки таблицы занесены текущие значения на этих выходах, взятые из Таблицы 1. К сборкам c и d подключены по два выхода УТС и в ячейки таблицы занесены результаты алгебраического сложения текущих значений на этих выходах. См. выше).

Крупные узлы ПЭТЛ-схемотехники изображают условно (без подробностей их устройства) в виде прямоугольников. Так, входящий в состав Регистровой Секции (PC) Троичный D-триггер (TDT) [5] с тремя группами выходов (m=3) условно изображен на Фиг. 2 справа. Триггер запоминает троичное значение на входе данных D, когда значение на управляющем входе С изменяется с -1 на +1. Значение доступно на трех тождественных выходах Q1, Q2, Q3.

Узлы состоят из ПЭТЛ и для них справедливо все, относящееся к ПЭТЛ: на входах алгебраически суммируются троичные значения; узлы могут иметь более одной группы выходов.

Троичный Реверсивный Регистр Сдвига (ТРРС) оперирует с данными, представленными в троичном коде с цифрами +1, 0 и -1, и реализует следующие функции:

1. Хранение k-разрядных троичных значений.

2. Параллельные запись и чтение.

3. Последовательные запись и чтение.

4. Сдвиги вправо и влево на заданное число разрядов.

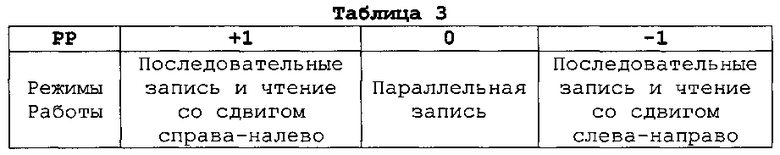

Работа ТРРС определяется управляющим входом РР (Режим Работы). Соответствие функций ТРРС значениям РР дано в таблице 3.

Схема k-разрядного ТРРС представлена на Фиг. 1. В его состав входят ПЭТЛ Э1.1 и Э1.2, имеющих по k групп выходов, и k Регистровых Секций (PC). Схема PC представлена на Фиг. 2.

PC содержит троичный дешифратор на УТС, троичный мультиплексор на ПЭТЛ Э2.1-Э2.9 и троичный D-триггер (TDT). В зависимости от значения на управляющем входе С1 данные с одного из входов данных D1, D2, D3 помещаются в TDT по фронту сигнала на управляющем входе С2. Содержимое TDT доступно на выходах Q1, Q2, Q3.

Троичный одноразрядный дешифратор 1×3 (на Фиг. 2 внизу слева), устройство и функционирование которого были описаны выше, управляет Троичным мультиплексором 3×1 (на Фиг. 2 вверху слева). В ПЭТЛ Э2.1, Э2.2 и Э2.3 троичные значения, подаваемые на входы Dl, D2, D3, разделяются на пары двузначных компонент +R и -R в соответствии с Таблицей 1. Эти компоненты подаются на входы трех пар ПЭТЛ. Компоненты +R поступают на входы ПЭТЛ Э2.4, Э2.6, Э2.8, имеющих только положительные выходы, компоненты -R - на входы ПЭТЛ Э2.5, Э2.7, Э2.9, имеющих только отрицательные выходы.

В соответствии с Таблицей 2 для любого значения С1 на входе дешифратора существует единственная пара сборок а, b или c, d или e, f, на которых устанавливается 0. На остальных сборках при этом будет либо +1 (b, d, f), либо -1 (а, с, е).

Значения +1 для входов ПЭТЛ, куда поступают компоненты -R, являются запирающими, значения -1 являются запирающими для входов, куда поступают компоненты +R. Каждому значению С1 соответствует единственная незапертая пара ПЭТЛ: Э2.4; Э2.5 для С1=+1, Э2.6; Э2.7 для С1=0 и Э2.8; Э2.9 для С1=-1. Со входов этих ПЭТЛ компоненты +R и -R проходят на их выходы. На выходах запертых пар ПЭТЛ при этом поддерживается 0. В результате на сборке g и на входе данных D-триггера формируется троичное значение, повторяющее значение на незапертом входе D1, D2 или D3. Это значение сохраняется в TDT по фронту сигнала на С2 и становится доступным на каждом из его выходов Q1, Q2, Q3.

ТРРС содержит k PC и ПЭТЛ Э1.1 и Э1.2, имеющих по k групп выходов. Они разветвляют сигналы РР (Режим Работы) и Сдв (Сдвиг), чтобы подать их соответственно на входы С1 и С2 PC.

ТРРС имеет последовательные входы Iпр, Iлв и выходы Опр, Олв; параллельные входы I(n) и выходы O(n)(n=1…k); вход РР, задающий режим работы (последовательные запись и чтение со сдвигами вправо или влево, параллельная запись), вход Сдв, фронты сигнала на котором инициируют запись/сдвиги/чтение.

Функционирование ТРРС в разных режимах достигается за счет соответствующей коммутации входов и выходов PC (Фиг. 1):

Если РР=+1, выходы Q3 PC подключены к входам D3 следующих PC. По сигналу Сдв происходит сдвиг содержимого ТРРС слева-направо одновременно с последовательными приемом с Iпр и выдачей на Опр.

Если РР=-1, выходы Q1 PC подключены к входам D1 предыдущих PC. По сигналу Сдв происходит сдвиг содержимого ТРРС справа-налево одновременно с последовательными приемом с Iлв и выдачей на Олв.

Если РР=0, подключение PC друг к другу отсутствует. Входы D2 PC подключены к входам I(n) ТРРС. По сигналу Сдв происходит параллельная запись в ТРРС.

Содержимое ТРРС доступно на выходах O(n)РС.

Литература

1. Брусенцов Н.П., Маслов С.П., Розин В.П., Тишулина A.M. Малая цифровая вычислительная машина "Сетунь". - М.: Изд-во Московского университета, 1965. 145 с.

2. Брусенцов Н.П., Жоголев Е.А., Маслов С.П., Рамиль Альварес X. Опыт создания троичных цифровых машин. // Компьютеры в Европе. Прошлое, настоящее и будущее. - Киев: Феникс, 1998. С. 67-71.

3. Маслов С.П. Пороговый элемент троичной логики и устройства на его основе. Патент РФ на изобретение RU №2394366 С1. Зарегистрирован: 10.07.2010.

4. Маслов С.П. Узел троичной схемотехники и дешифраторы-переключатели на его основе. Патент РФ на изобретение RU №2461122 С1. Зарегистрирован: 10.09.2012.

5. Маслов С.П. Троичный D-триггер (варианты). Патент РФ на изобретение RU №2510129 С1. Зарегистрирован: 20.03.2014.

6. Маслов С.П. Об одной возможности реализации троичных цифровых устройств. Тематический сборник №12 "Программные системы и инструменты", М.: Изд-во факультета ВМиК МГУ, 2011. С. 222-227.

7. Маслов С.П. Троичная схемотехника. Тематический сборник №13 "Программные системы и инструменты", М.: Изд-во факультета ВМиК МГУ, 2012. С. 152-158.

8. Брусенцов Н.П. Пороговая реализация трехзначной логики электромагнитными средствами. // Вычислительная техника и вопросы кибернетики. Вып. 9. - М.: Изд-во Моск. ун-та, 1972. С. 3-35.

9. Брусенцов Н.П. Электромагнитные цифровые устройства с однопроводной передачей трехзначных сигналов. - В кн.: Магнитные элементы автоматики и вычислительной техники. XIV Всесоюзное совещание (Москва, сентябрь 1972 г.). М., "Наука", 1972, с. 242-244.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРОИЧНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 2017 |

|

RU2642408C1 |

| ТРОИЧНЫЙ Т-ТРИГГЕР И ТРОИЧНЫЙ РЕВЕРСИВНЫЙ СЧЕТЧИК НА ЕГО ОСНОВЕ | 2014 |

|

RU2562370C2 |

| ТРОИЧНЫЙ ПОЛНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ СУММАТОР (ВАРИАНТЫ) | 2016 |

|

RU2616887C1 |

| ТРОИЧНЫЙ D-ТРИГГЕР (ВАРИАНТЫ) | 2012 |

|

RU2510129C1 |

| УСТРОЙСТВО ТРОИЧНОЙ СХЕМОТЕХНИКИ НА ТОКОВЫХ ЗЕРКАЛАХ | 2017 |

|

RU2648565C1 |

| УСТРОЙСТВО ТРОИЧНОГО СЛОЖЕНИЯ И ВЫЧИТАНИЯ | 2017 |

|

RU2645279C1 |

| ТРОИЧНЫЙ ПОРАЗРЯДНЫЙ УМНОЖИТЕЛЬ | 2016 |

|

RU2631166C1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ НА ТОКОВЫХ ЗЕРКАЛАХ | 2016 |

|

RU2618901C1 |

| УЗЕЛ ТРОИЧНОЙ СХЕМОТЕХНИКИ И ДЕШИФРАТОРЫ-ПЕРЕКЛЮЧАТЕЛИ НА ЕГО ОСНОВЕ | 2011 |

|

RU2461122C1 |

Изобретение относится к устройствам цифровой вычислительной техники, в частности к недвоичной схемотехнике. Технический результат заключается в обеспечении в среде интегральной полупроводниковой электроники устройств на основе симметричной троичной системы с цифрами +1, 0 и -1. Технический результат достигается за счет включения в троичного реверсивного регистра сдвига, который содержит троичные дешифраторы 1×3, троичные мультиплексоры, троичные D-триггеры и два пороговых элемента троичной логики. 2 ил., 3 табл.

Троичный Реверсивный Регистр Сдвига (ТРРС) содержит k Регистровых Секций (PC) и два Пороговых Элемента Троичной Логики (ПЭТЛ), причем ПЭТЛ имеют по k групп выходов, причем k - число разрядов ТРРС, причем входы X первого и второго ПЭТЛ являются соответственно входами РР и Сдв ТРРС, причем положительный и отрицательный R-выходы n-й группы выходов первого ПЭТЛ через n-ю р-сборку подключены к первому С входу n-й PC, причем положительный и отрицательный R-выходы n-й группы выходов второго ПЭТЛ через n-ю r-сборку подключены к второму С входу n-й PC, причем вход D2 и выход Q2 n-й PC подключены соответственно к n-му входу I и n-му выходу О ТРРС, причем n=1…k, причем вход D3 первой PC является входом Iпр ТРРС и выход Q3 k-й PC является выходом Опр ТРРС, причем вход D1 к-й PC является входом Iлв ТРРС и выход Q1 первой PC является выходом Олв ТРРС, причем выход Q3 n-й PC через n-ю с-сборку подключен к входу D3 (n+1)-й PC, причем n=1…(k-1), причем выход Q1 n-й PC через n-ю а-сборку подключен к входу D1 (n-1)-й PC, причем n=2…k, причем PC содержит девять ПЭТЛ, Узел Троичной Схемотехники (УТС) и D-Триггер (TDT), причем четвертый, шестой и восьмой ПЭТЛ имеют только положительные выходы, а пятый, седьмой и девятый ПЭТЛ имеют только отрицательные выходы, причем TDT имеет три группы выходов, причем входы X первого, второго и третьего ПЭТЛ являются соответственно входами D1, D2 и D3 PC, вход X УТС является входом C1 PC, а вход С TDT является входом С2 PC, причем положительные и отрицательные R-выходы первой, второй и третьей групп TDT посредством соответственно i-й, j-й и k-й сборок подключены соответственно к выходам Ql, Q2 и Q3 PC, причем положительный R-выход первого ПЭТЛ и выход М7 УТС через сборку а подключены к входу X четвертого ПЭТЛ, причем отрицательный R-выход первого ПЭТЛ и выход М2 УТС через сборку b подключены к входу X пятого ПЭТЛ, причем положительный R-выход второго ПЭТЛ и выходы М4 и М8 УТС через сборку с подключены к входу X восьмого ПЭТЛ, причем отрицательный R-выход второго ПЭТЛ и выходы M1 и М5 УТС через сборку d подключены к входу X девятого ПЭТЛ, причем положительный R-выход третьего ПЭТЛ и выход М3 УТС через сборку е подключены к входу X шестого ПЭТЛ, причем отрицательный R-выход третьего ПЭТЛ и выход М6 УТС через сборку f подключены к входу X седьмого ПЭТЛ, причем положительные R-выходы четвертого, шестого и восьмого ПЭТЛ и отрицательные R-выходы пятого, седьмого и девятого ПЭТЛ через сборку g подключены к входу D TDT, причем положительные и отрицательные L-выходы всех ПЭТЛ и TDT подключены к земляной шине.

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| ТРИГГЕР, РЕГИСТР СДВИГА, СХЕМА ВОЗБУЖДЕНИЯ УСТРОЙСТВА ОТОБРАЖЕНИЯ, УСТРОЙСТВО ОТОБРАЖЕНИЯ И ПАНЕЛЬ УСТРОЙСТВА ОТОБРАЖЕНИЯ | 2010 |

|

RU2507680C2 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2001 |

|

RU2203520C2 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

Авторы

Даты

2016-05-27—Публикация

2015-07-24—Подача