Область техники, к которой относится изобретение

Изобретение относится в основном к области кэширования однокристальных мультипроцессоров. Кроме того, настоящее изобретение относится, в частности, к аморфным кэшам для однокристальных мультипроцессоров.

Уровень техники

Система с однокристальным мультипроцессором (СМР), содержащая несколько процессорных ядер, может использовать ячеистую архитектуру, где каждая ячейка имеет процессорное ядро, частный кэш (L1), второй, частный или общий кэш (L2) и директорий для сопровождения копий среди кэшированных частных копий. Исторически такие ячеистые архитектуры могут иметь один из двух возможных типов организации кэша L2.

Благодаря конструктивному распределению данных между потоками системы СМР, осуществляющие многопоточную обработку данных, могут использовать принцип общего кэша L2. Такой подход общего кэша L2 способен максимизировать эффективную емкость кэша L2, поскольку отсутствует дублирование данных, но при этом увеличивается средняя задержка попадания в кэш по сравнению с частным кэшем L2. Такие схемы могут рассматривать кэш L2 и директорий как одну структуру.

Системы СМР, выполняющие скалярные и чувствительные к задержке процессы, могут предпочитать организацию частного кэша L2 для оптимизации задержки ценой потенциального уменьшения эффективной емкости кэша вследствие потенциального дублирования данных. Частный кэш L2 может предложить изоляцию кэша, но при этом не допускает заимствования емкости кэша. Приложения с интенсивным использованием кэша, работающие на некоторых ядрах, уже не смогут заимствовать емкость кэша у неактивных ядер или ядер, выполняющих приложения с небольшими объемами обрабатываемых данных.

Некоторые семейства систем СМР могут иметь кэш трех уровней. Кэш L1 и кэш L2 могут образовать два частных уровня. Третий кэш L3 может совместно использоваться всеми ядрами.

Краткое описание чертежей

Понимая, что эти чертежи представляют только типичные варианты изобретения и потому их не следует рассматривать в качестве ограничений объема изобретения, настоящее изобретение будет описано и разъяснено более конкретно и подробно с использованием прилагаемых чертежей, на которых:

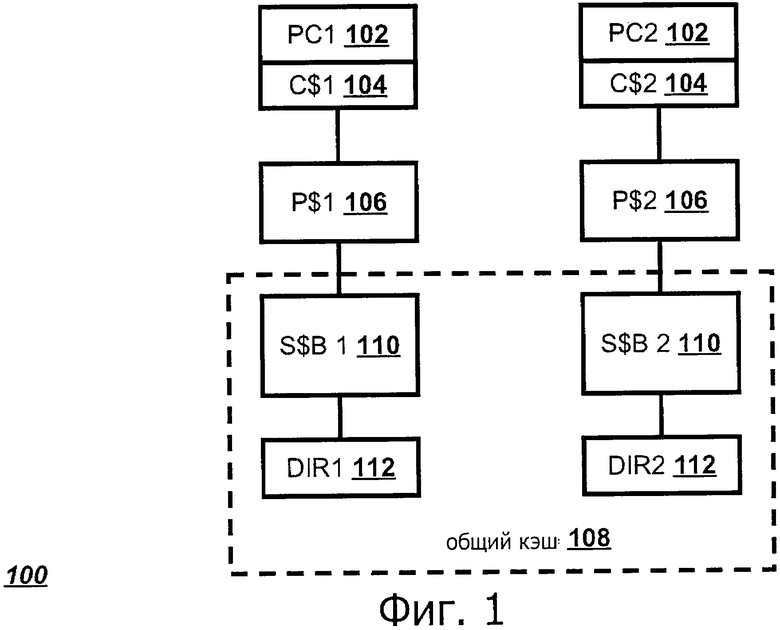

фиг.1 иллюстрирует блок-схему одного варианта однокристального мультипроцессора с частными и общим кэшами;

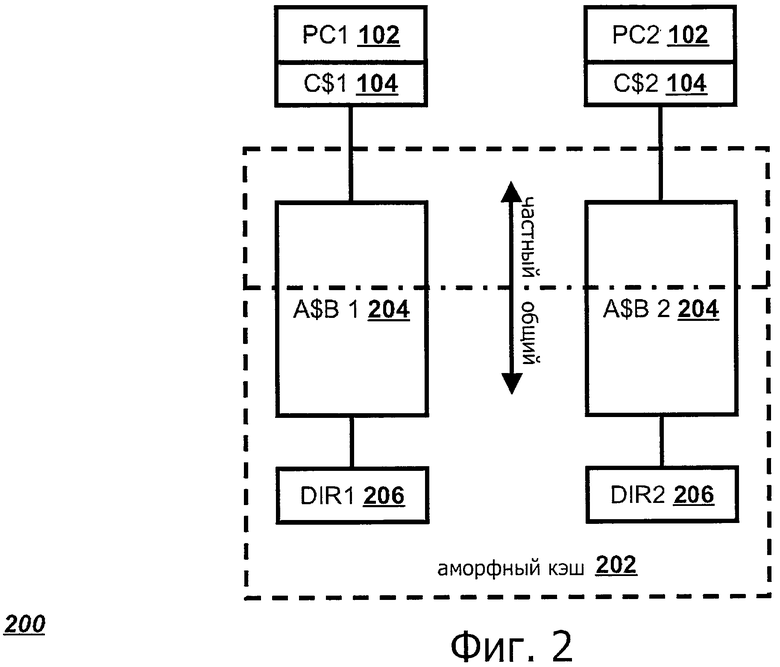

фиг.2 иллюстрирует блок-схему одного варианта однокристального мультипроцессора с архитектурой аморфного кэша;

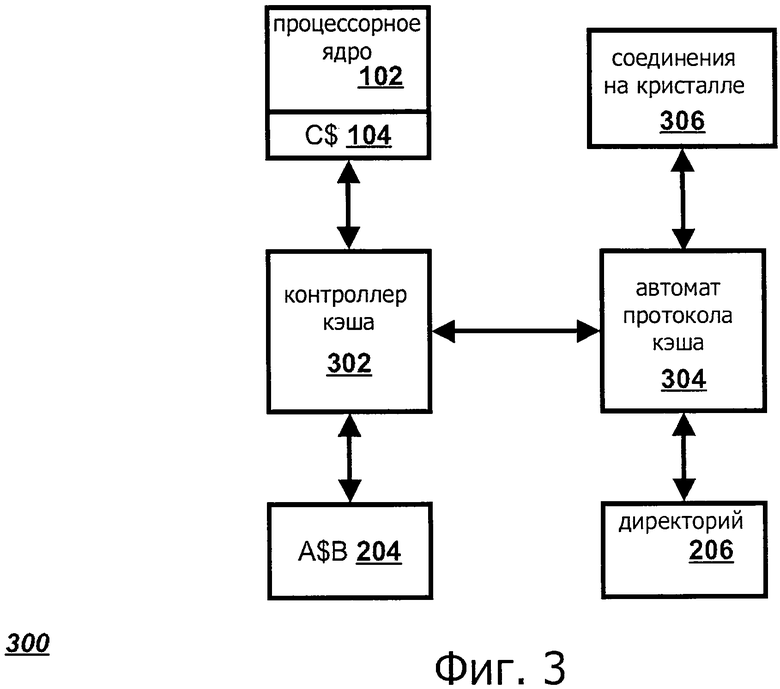

фиг.3 иллюстрирует блок-схему одного варианта ячейки однокристального мультипроцессора;

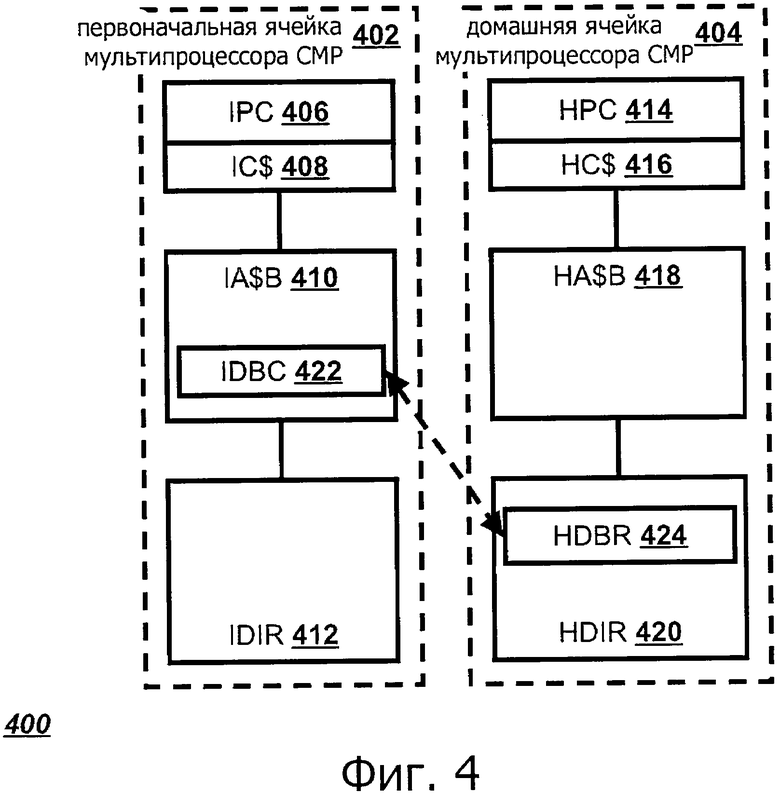

фиг.4 иллюстрирует блок-схему одного варианта однокристального мультипроцессора с аморфными кэшами, осуществляющими распределение данных;

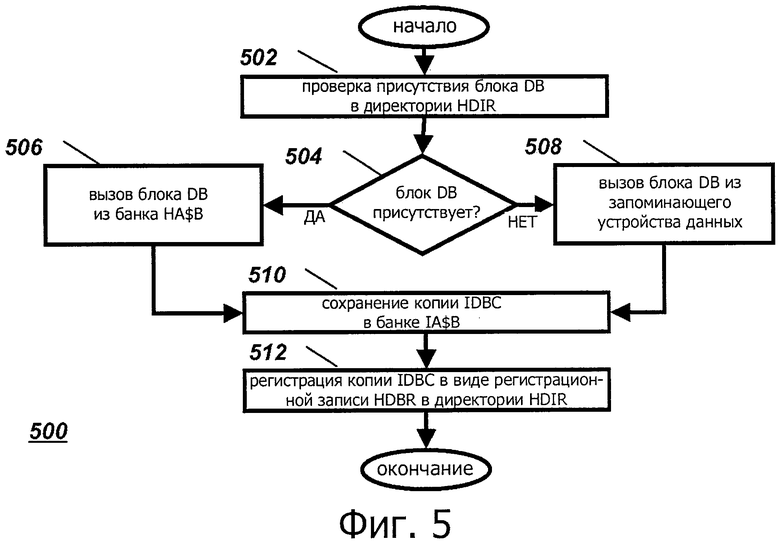

фиг.5 иллюстрирует логическую схему одного варианта способа распределения копий блоков данных в однокристальном мультипроцессоре с аморфным кэшем;

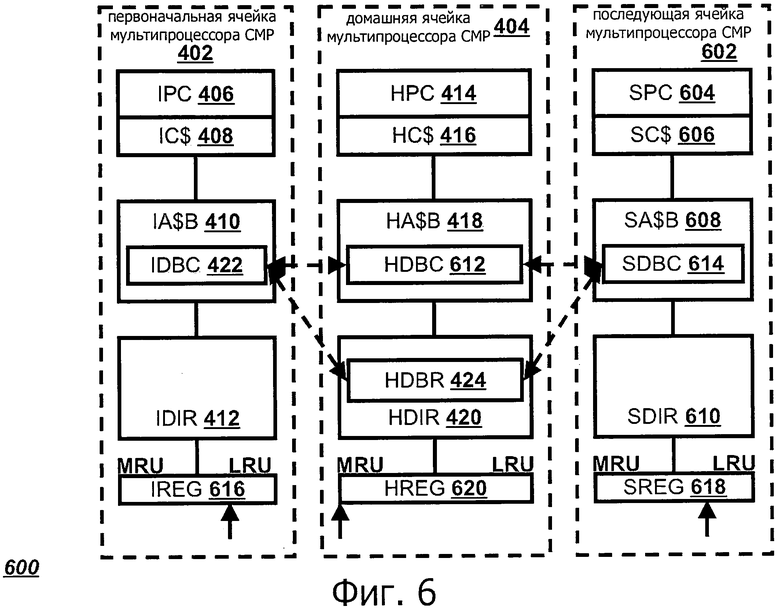

фиг.6 иллюстрирует блок-схему одного варианта однокристального мультипроцессора с аморфным кэшем, осуществляющим миграцию данных;

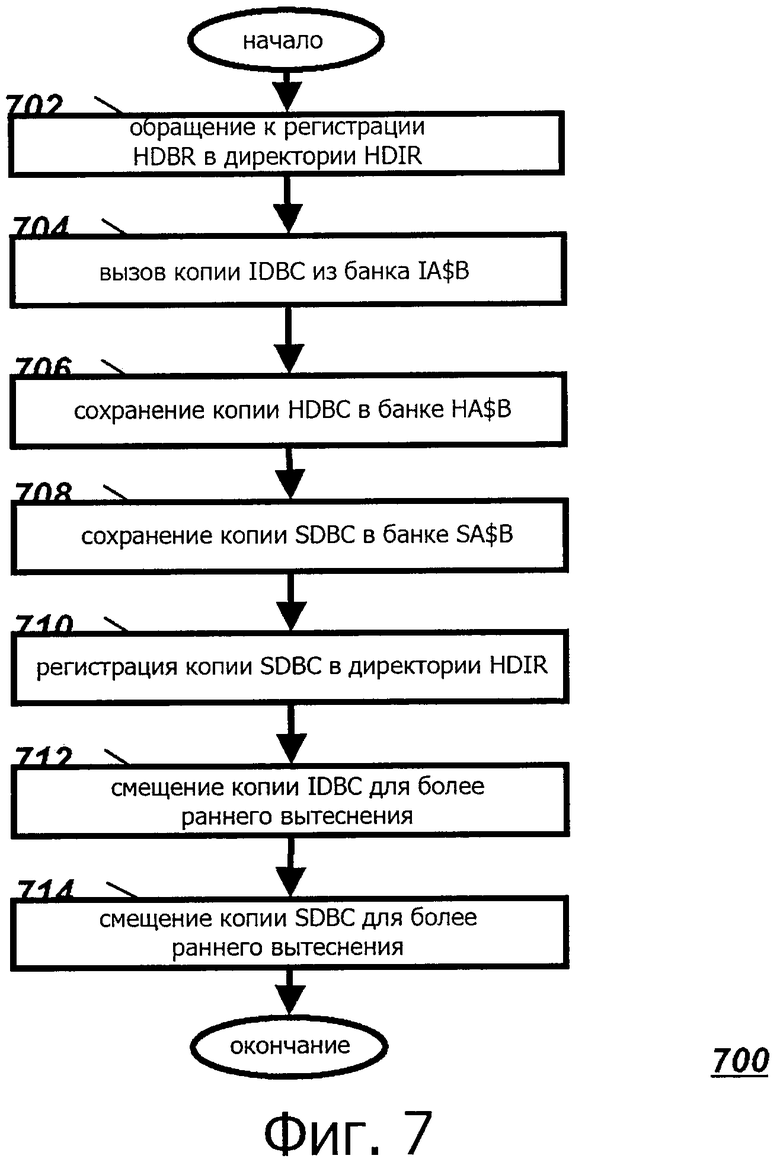

фиг.7 иллюстрирует логическую схему одного варианта способа копирования данных в однокристальном мультипроцессоре с аморфным кэшем;

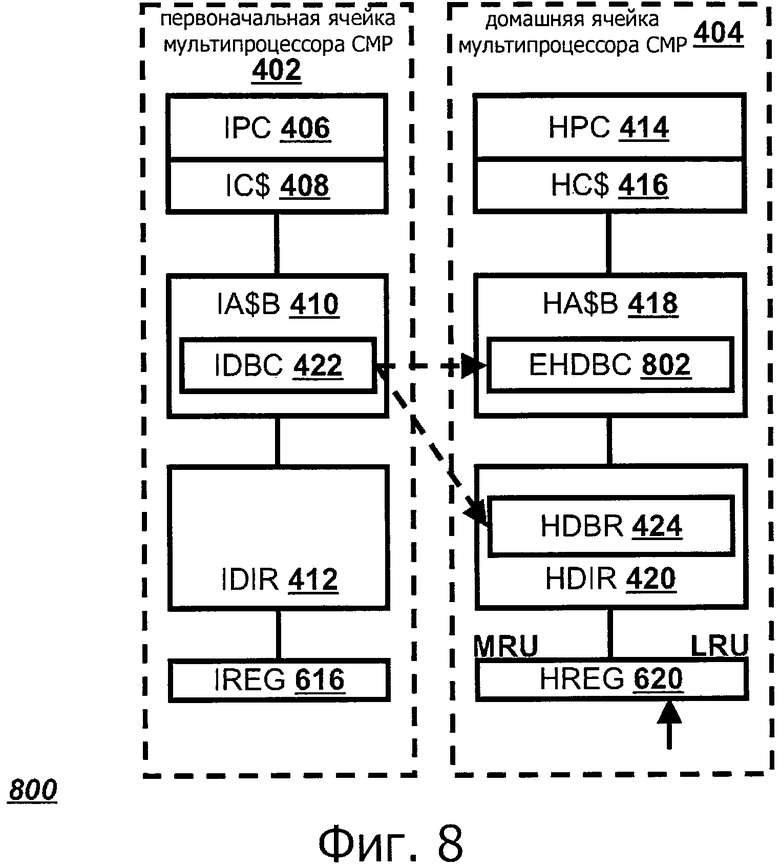

фиг.8 иллюстрирует блок-схему одного варианта однокристального мультипроцессора с аморфным кэшем, осуществляющим виктимизацию копий;

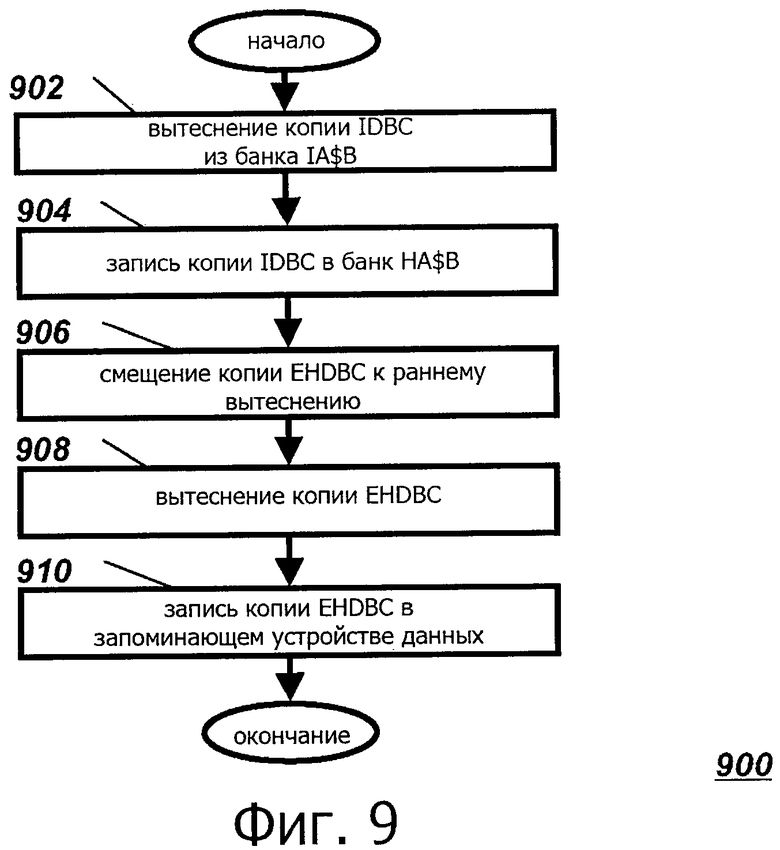

фиг.9 иллюстрирует логическую схему одного варианта способа виктимизации данных в однокристальном мультипроцессоре с аморфным кэшем;

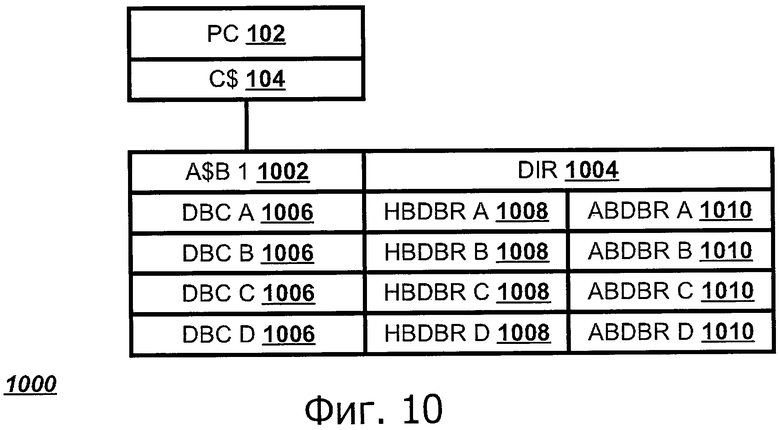

фиг.10 иллюстрирует блок-схему одного варианта однокристального мультипроцессора с объединенной структурой банка аморфного кэша и директория.

Подробное описание изобретения

Дополнительные признаки и преимущества настоящего изобретения будут сформулированы в последующем описании и станут частично ясны из этого описания либо их можно будет уяснить из опыта практической реализации изобретения. Эти признаки и преимущества могут быть реализованы и получены посредством инструментов и сочетаний, конкретно указанных в прилагаемой формуле изобретения. Эти и другие признаки настоящего изобретения станут более полно понятны из последующего описания и прилагаемой формулы изобретения либо могут быть ясны из практического опыта реализации изобретения, как установлено здесь.

Ниже подробно описаны различные варианты изобретения. Хотя здесь обсуждаются конкретные варианты, следует понимать, что они приведены только в иллюстративных целях. Специалист в соответствующей области должен понимать, что можно также использовать другие компоненты и конфигурации, не выходя за рамки духа и объема настоящего изобретения.

Настоящее изобретение содержит несколько вариантов, таких как способ, устройство и набор компьютерных команд, а также другие варианты, связанные с базовыми принципами изобретения. Рассмотрены способ, «ячейка» однокристального мультипроцессора и однокристальный мультипроцессор с аморфным кэшированием. Первоначальное процессорное ядро может вызвать блок данных из запоминающего устройства. Первоначальный банк аморфного кэша, расположенный рядом с этим первоначальным процессорным ядром, может сохранять первоначальную копию блока данных. Собственный директорий этого банка может зарегистрировать эту первоначальную копию блока данных.

Однокристальный мультипроцессор (СМР) может иметь несколько выполненных на одном кристалле процессоров, каждый из которых имеет один или несколько кэшей. Эти кэши могут быть частными кэшами, сохраняющими данные исключительно для соответствующего процессора, либо общими кэшами, сохраняющими данные, доступные для всех процессоров. На фиг.1 показана упрощенная блок-схема одного варианта мультипроцессора СМР 100 с частным и общим кэшами. Мультипроцессор СМР 100 может иметь одно или несколько процессорных ядер (PC) 102 на одном кристалле. Ядро PC 102 может представлять собой процессор, сопроцессор, контроллер с фиксированными функциями или процессорное ядро другого типа. С каждым ядром PC 102 может быть соединен кэш (С$) 104 ядра.

Ядро PC 102 может быть соединено с частным кэшем (Р$) 106. Этот кэш Р$ 106 может быть ограничен для доступа только от локального ядра PC 102, но может быть также открыт для слежения (снупинга (snooping)) другими ядрами PCs 102 на основе информации в директории и операций протокола. Локальное ядро PC 102 может назначить линию в кэше Р$ 106 любому адресу. Ядро PC 102 может обратиться в кэш Р$ 100 перед тем, как передать запрос автомату протокола когерентности для направления в директорий или другие источники памяти. Линия кэша Р$ 106 может быть дублирована в любом банке кэша Р$ 106.

Ядра PC 102 могут быть дополнительно соединены с общим кэшем 108. Этот общий кэш 108 может быть доступен для всех ядер PC 102. Любое ядро PC 102 может назначить линию в общем кэше 108 подмножеству адресов. Ядро PC 102 может обращаться к общему кэшу 108 после выполнения операций автомата протокола когерентности и может при этом просматривать другие источники памяти. Общий кэш 108 может иметь отдельный банк (S$B) 110 общего кэша для каждого ядра PC 102. Каждый блок данных может иметь свое единственное место среди всех банков S$Bs 110. Каждый банк S$B 110 может иметь директорий (DIR) 112 для отслеживания блоков данных кэша, записанных в кэше С$ 104, кэше Р$ 106, банке S$B 110 кэша или каком-либо сочетании этих трех компонентов.

Структура единственного кэша, именуемая здесь «аморфный кэш», может в любой данный момент выполнять функции частного кэша, общего кэша или обоих кэшей. Аморфный кэш может быть построен таким образом, чтобы предоставлять одновременно преимущества малой задержки, присущие частному кэшу, и преимущества увеличенной емкости, свойственные общему кэшу. Кроме того, такая архитектура допускает также конфигурирование во время работы, чтобы увеличить емкость частного кэша или общего кэша. Структура единственного кэша может работать в качестве частного кэша, общего кэша или гибридного кэша с динамическим распределением емкости между частной и общей областями. К аморфному кэшу могут обращаться все ядра PC 102. Локальное ядро PC 102 может назначать линию аморфного кэша для любого адреса. Другие ядра PC 102 могут назначать линию аморфного кэша для подмножества адресов. Аморфный кэш может позволить скопировать линию в любой банк аморфного кэша по запросам локального ядра PC 102. Локальное ядро PC 102 может обратиться в аморфный кэш перед выполнением операций автомата протокола когерентности. Другие ядра PC 102 могут обращаться в банк аморфного кэша посредством автомата протокола когерентности.

Фиг.2 иллюстрирует упрощенную блок-схему одного из вариантов мультипроцессора СМР с архитектурой 200 аморфного кэша. С аморфным кэшем 202 могут быть соединены одно или несколько ядер PC 102, каждое с присоединенным к нему кэшем С$ 104. Аморфный кэш 202 может быть разделен на несколько отдельных банков (А$В) 204 аморфного кэша для каждого ядра PC 102. Каждый банк А$В 204 может иметь отдельный директорий (DIR) 206 для отслеживания блоков данных кэша, записанных в банке А$В 204.

Такая организация кэша может использовать ячеистую архитектуру, гомогенную архитектуру, гетерогенную архитектуру или другую мультипроцессорную (СМР) архитектуру. Ячейки в ячеистой архитектуре могут быть соединены посредством когерентного коммутатора, шины или другим способом. На фиг.3 показана блок-схема одного из вариантов «ячейки» 300 однокристального мультипроцессора СМР. Ячейка 300 мультипроцессора СМР может иметь одно или несколько процессорных ядер 102, совместно использующих кэш С$ 104. Ядро PC 102 может через контроллер 302 кэша обратиться в банк А$В 204, динамически разбиваемый на частную и общую части. Ячейка 300 мультипроцессора СМР может иметь компонент директория DIR 206 для отслеживания всех блоков частного кэша на кристалле. Контроллер 302 кэша может передавать входящие запросы от ядра в локальный банк А$В 204, где хранятся частные данные для ячейки 300. Автомат 304 протокола кэша может передавать информацию о промахе в локальном банке А$В в свою домашнюю ячейку через соединительный модуль 306 на кристалле. Этот банк А$ в домашней ячейке, доступный через указанный соединительный модуль 306 на кристалле, может удовлетворить запрос на данные промаха. Автомат 304 протокола кэша может просматривать директорий DIR 206 банка в домашней ячейке для отслеживания удаленных частных банков А$В при необходимости. Промах в домашней ячейке после разрешения всех необходимых прослеживаний может привести к тому, что домашняя ячейка инициирует запрос на поиск вне своего сокета. Банк А$В 204, конфигурированный для работы в качестве чисто частного кэша, может пропустить операцию просмотра локального банка А$В 204 в домашней ячейке, но может следовать потоку в директории. Банк А$В 204, конфигурированный для работы в качестве чисто общего кэша, может пропустить операцию просмотра локального банка А$В 204 и перейти сразу к домашней ячейке. Динамическое разбиение банка А$В 204 может быть реализовано посредством операций протокола кэширования с учетом распределения блоков, миграции, виктимизации, копирования, замены и обратной инвалидации.

На фиг.4 показана блок-схема одного из вариантов СМР с аморфным кэшем 400, осуществляющим распределение данных. Первоначальная ячейка 402 мультипроцессора СМР может запросить доступ к блоку данных в запоминающем устройстве данных после проверки, нет ли этого блока данных в домашней ячейке 404 мультипроцессора СМР. Эта первоначальная ячейка 402 мультипроцессора СМР может иметь первоначальное процессорное ядро (IPC) 406, кэш (IС$) 408 первоначального ядра, банк (IА$В) 410 первоначального аморфного кэша и первоначальный директорий (IDIR) 412. Домашняя ячейка 404 мультипроцессора СМР может иметь домашнее процессорное ядро (НРС) 414, кэш (НС$) 416 домашнего ядра, банк (НА$В) 418 домашнего аморфного кэша и домашний директорий (HDIR) 420. Первоначальная ячейка 402 мультипроцессора СМР может записать первоначальную копию (IDBC) 422 блока данных или блок кэша в банке IА$В 410. Домашняя ячейка 404 мультипроцессора СМР может осуществить домашнюю регистрацию (HDBR) 424 блока данных в директории HDIR 420 для отслеживания копий блока данных в каждом банке аморфного кэша. В известных архитектурах общего кэша блок данных мог быть назначен в домашнюю ячейку 404 мультипроцессора СМР независимо от близости первоначальной ячейки 402 мультипроцессора СМР к домашней ячейке 404 мультипроцессора СМР.

На фиг.5 показана логическая схема одного из вариантов способа 500 распределения копий блока данных в мультипроцессоре СМР 200 с аморфным кэшем. Первоначальная ячейка 402 мультипроцессора СМР может проверить директорий HDIR для обнаружения блока (DB) данных (Этап 502). Если блок DB присутствует в банке НА$В (Этап 504), первоначальная ячейка 402 мультипроцессора СМР может вызвать этот блок DB из банка НА$В (Этап 506). Если блока DB в банке НА$В нет (Этап 506), первоначальная ячейка 402 мультипроцессора СМР может вызвать этот блок DB из запоминающего устройства данных (Этап 508). Первоначальная ячейка 402 мультипроцессора СМР может записать копию IDBC 422 в банке IА$В 410 (Этап 510). Домашняя ячейка 404 мультипроцессора СМР может выполнить регистрацию HDBR 424 в директории HDIR 420 (Этап 512).

Фиг.6 иллюстрирует блок-схему одного из вариантов мультипроцессора СМР с аморфным кэшем, выполняющего миграцию данных. Последующая ячейка 602 мультипроцессора СМР может искать блок данных, записанный в качестве копии IDBC 422 в банке IА$В 410. Эта последующая ячейка 602 мультипроцессора СМР может иметь последующее процессорное ядро (SPC) 604, кэш (SC$) 606 последующего ядра, банк (SA$B) 608 последующего аморфного кэша и последующий директорий (SDIR) 610. Перед обращением в запоминающее устройство для поиска блока данных последующая ячейка 602 мультипроцессора СМР может проверить директорий HDIR 420, чтобы определить, не находится ли уже копия этого блока данных в банке кэша на кристалле. Если копия банка данных присутствует, домашняя ячейка 404 мультипроцессора СМР может скопировать эту копию IDBC 422 в качестве домашней копии (HDBC) 612 блока данных в банк НА$В 418. Последующая ячейка 602 мультипроцессора СМР может создать последующую копию (SDBC) 614 блока данных в банке SA$B 608 на основе копии HDBC 612. В альтернативном варианте последующая ячейка 602 мультипроцессора СМР может создать последующую копию (SDBC) 614 блока данных в банке SA$B 608 на основе копии IDBC 422, а затем уже создать копию HDBC 612. Более поздние копии блока данных могут быть выполнены на основе копии HDBC 612. Такая схема миграции может создать выигрыш по емкости в общем кэше. В дальнейшем запросы могут встретить уменьшенную задержку для этого блока данных по сравнению с удаленными частными кэшами. Миграция может происходить при появлении второго запроса, хотя порог миграции можно корректировать в каждом случае. Обе - первоначальная ячейка 402 мультипроцессора СМР и последующая ячейка 602 мультипроцессора СМР могут сохранять копию блока данных в кэше ядра в дополнение к аморфному кэшу в зависимости от применяемой стратегии копирования.

Совместно используемая (общая) копия блока данных может мигрировать в банк НА$В 418 для реализации выигрыша по емкости. Каждый частный кэш может кэшировать копию этого общего блока данных, жертвуя емкостью в пользу уменьшения задержки. Аморфный кэш может поддерживать копирование, но не требует такого копирования. Аморфный кэш может копировать данные в зависимости от конкретной ситуации и смещать копии для замены в каждом отдельном случае.

Первоначальная ячейка 402 мультипроцессора СМР может иметь первоначальный регистр (IREG) 616 для контроля виктимизации копии IDBC 422 в банке IА$В 410. Данные в регистре IREG 616 могут быть организованы по порядку от использованного позже всех блока кэша (MRU) к использованному раньше всех блоку кэша (LRU), при этом блок (LRU), использованный раньше всех, является первым кандидатом на вытеснение. При копировании копии IDBC 422 из запоминающего устройства или из банка НА$В 418, копия IDBC 422 может быть внесена в регистр IREG 616 в качестве блока (MRU), использованного позже всех, так что эта копия IDBC 422 оказывается последней в очереди на вытеснение. Домашняя ячейка 404 мультипроцессора СМР может иметь домашний регистр (HREG) 618 для контроля виктимизации копии HDBC 612 в банке НА$В 418. При копировании указанной копии IDBC 422 блока данных из банка IА$В 410 в банк НА$В 418, чтобы сделать ее доступной для последующей ячейки 602 мультипроцессора СМР, копия HDBC 612 может быть внесена в регистр HREG 618 в качестве блока, использованного позже всех, (MRU), так что эта копия HDBC 612 оказывается последней в очереди на вытеснение. Далее, копия IDBC 422 может быть передвинута в регистре IREG 616 ближе к концу, где располагаются блоки, использованные раньше (LRU), приближая тем самым эту копию IDBC 422 к более раннему вытеснению. Последующая ячейка 602 мультипроцессора СМР может иметь последующий регистр (SREG) 620 для контроля виктимизации копии SDBC 614 в банке SA$B 608. При копировании этой копии SDBC 614 блока данных из банка НА$В 418, копия SDBC 614 может быть внесена в регистр SREG 620 ближе к концу, где располагаются блоки, использованные раньше (LRU), приближая тем самым эту копию SDBC 614 к более раннему вытеснению.

Регистр IREG 616 может быть использован с целью конфигурирования аморфного кэша для работы в качестве частного кэша или общего кэша на основе размещения копии IDBC 422 в регистре IREG 616. Для настройки в качестве общего кэша копия IDBC 422 может быть помещена в позицию блока, использованного раньше всех, (LRU) в регистре IREG 616 или оставлена неразмещенной. Кроме того, копия HDBC 612 может быть помещена в позицию блока, использованного позже всех, (MRU) в регистре HREG 620. Для настройки в качестве частного кэша копия IDBC 422 может быть помещена в позицию MRU. Кроме того, копия HDBC 612 может быть помещена в позицию LRU в регистре 620 или оставлена неразмещенной.

Фиг.7 иллюстрирует вариант логической схемы способа 700 копирования данных в мультипроцессоре СМР 200 с аморфным кэшем. Последующая ячейка 602 мультипроцессора СМР может обратиться к регистрационной записи HDBR 424 в директории HDIR 420 (Этап 702). Домашняя ячейка 404 мультипроцессора СМР может вызвать копию IDBC 422 из банка IА$В 410 (Этап 704). Эта домашняя ячейка 404 мультипроцессора СМР может сохранить копию HDBC 612 в банке НА$В 418 (Этап 706). Последующая ячейка 602 мультипроцессора СМР может сохранить копию SDBC 614 в банке SA$B 608 (Block 708). Эта последующая ячейка 602 мультипроцессора СМР может зарегистрировать копию SDBC 614 в директории HDIR 420 (Этап 710). Первоначальная ячейка 402 мультипроцессора СМР может сместить копию IDBC 422 к более раннему вытеснению (Этап 712). Последующая ячейка 602 мультипроцессора СМР может сместить копию SDBC 614 к более раннему вытеснению (Этап 714).

Фиг.8 иллюстрирует блок-схему одного из вариантов мультипроцессора СМР с аморфными кэшами 800, осуществляющими виктимизацию копий. Когда исключаемая чистая или грязная копия блока данных вытесняется из банка аморфного кэша, первоначальная ячейка 402 мультипроцессора СМР может записать грязную или чистую копию IDBC 422 в качестве вытесняемой домашней копии (EHDBC) 802 в банк НА$В 418. Эта копия EHDBC 802 может быть внесена в регистр HREG 620 ближе к концу, где располагаются блоки, использованные раньше всех, (LRU), что приближает эту копию EHDBC 802 к более раннему вытеснению. Если ячейка мультипроцессора СМР со структурой или конфигурацией частного кэша запрашивает копию EHDBC 802, эта копия EHDBC 802 может остаться в позиции LRU, а вновь запрашивающее устройство может поместить свою копию блока данных в позицию блока, использованного позже всех, (MRU). Если более поздняя ячейка мультипроцессора СМР делает запрос из домашней ячейки 404 мультипроцессора СМР, копия EHDBC 802 может быть перемещена в позицию MRU, а более позднее запрашивающее устройство может переместить более позднюю копию блока данных в позицию LRU.

В известной архитектуре частный кэш или общий кэш может отбросить чистую жертву или неизмененный блок кэша и записать назад в память грязную жертву или измененный блок кэша. При аморфном кэшировании запись копии IDBC 422 в банк НА$В 418 может привести к заимствованию емкости кэша. Заимствование кэша может позволить приложениям, работающим с большими объемами данных, использовать кэши из других ячеек.

В известных архитектурах директорная жертва может потребовать инвалидации всех копий блоков данных частных кэшей, поскольку становится трудно отслеживать эти копии блоков данных частных кэшей. Последующие обращения к этим блокам данных могут потребовать обращения к памяти системы. Аморфный кэш может сгладить влияние инвалидации за счет перемещения директорных жертв в домашнюю ячейку, где отслеживание посредством директории не требуется.

На фиг.9 показана логическая схема одного из вариантов способа 700 копирования данных в мультипроцессоре СМР 200 с аморфным кэшем. Первоначальная ячейка 402 мультипроцессора СМР может вытеснить копию IDBC 422 из банка IA$В 410 (Этап 902). Эта первоначальная ячейка 402 мультипроцессора СМР может записать копию IDBC 422 в банк НА$В 418 (Этап 904). Домашняя ячейка 404 мультипроцессора СМР может сместить копию EHDBC 802 для более раннего вытеснения (Этап 906). Когда домашняя ячейка 404 мультипроцессора СМР в итоге вытесняет копию EHDBC 802 (Этап 908), эта домашняя ячейка 404 мультипроцессора СМР может записать копию EHDBC 802 в запоминающее устройство данных (Этап 910).

Банк 204 аморфного кэша и директорий 206 могут быть выполнены отдельно. На фиг.10 показана блок-схема одного из вариантов мультипроцессора СМР 1000 с объединенной структурой банка (А$В) 1002 аморфного кэша и директория (DIR) 1004. Банк А$В 1002 может содержать набор копий (DBC) 1006 блоков данных. Директорий DIR 1004 может ассоциировать регистрацию (HBDBR) 1008 блока данных в домашнем банке с копией DBC 1006. Кроме того, директорий DIR 1004 может ассоциировать одну или несколько регистрации (ABDBR) 1010 блока данных в альтернативных банках с копией DBC 1006, вследствие чего директорий DIR 1004 может иметь больше блоков данных, чем банк А$В 1002.

Хотя этого и не требуется, настоящее изобретение описано по меньшей мере частично, в общем контексте выполняемых компьютером команд, таких как программные модули, исполняемые электронным устройством, таким как компьютер общего назначения. В общем случае программные модули включают обычные программы, объекты, компоненты, структуры данных и т.п. для выполнения конкретных задач или реализации конкретных типов абстрактных данных. Более того, специалисты в рассматриваемой области должны понимать, что и другие варианты настоящего изобретения могут быть практически реализованы в средах вычислительных сетей с разнообразными типами конфигураций компьютерных систем, включая персональные компьютеры, ручные устройства, мультипроцессорные системы, микропроцессорные или программируемые бытовые электронные приборы, сетевые персональные компьютеры, мини-компьютеры, центральные универсальные компьютеры и т.п.

Некоторые варианты могут быть реализованы в распределенной вычислительной среде, где выполнение задач происходит посредством локальных и удаленных устройств, связанных (проводными линиями, беспроводными линиями или с использованием сочетания линий обоих видов) через сеть связи.

Варианты в рамках настоящего изобретения могут также включать машиночитаемые носители записи, передающие или сохраняющие записанные на них исполняемые компьютером команды или структуры данных. В качестве такого машиночитаемого носителя записи можно использовать любой доступный носитель, к которому может обратиться и получить доступ компьютер общего или специального назначения. В качестве примера, но не ограничения, такой машиночитаемый носитель записи может представлять собой запоминающее устройство с произвольной выборкой (ЗУПВ (RAM)), постоянное запоминающее устройство (ПЗУ (ROM)), электрически стираемое программируемое ПЗУ (ЭСППЗУ (EEPROM)), дисковод с компакт-дисками (CD-ROM) или другой оптический дисковод, дисковод с магнитным диском, или другое магнитное запоминающее устройство либо какой-либо иной носитель записи, способный переносить или сохранять нужную программу в виде исполняемых компьютером команд или структур данных. При передаче или предоставлении информации через сеть или другую линию связи (проводную, беспроводную или сочетание проводных и беспроводных линий) компьютеру этот компьютер рассматривает такое соединение в качестве машиночитаемого носителя. Таким образом, любое подобное соединение (линию связи) можно совершенно справедливо называть машиночитаемым носителем. Различные сочетания перечисленных выше типов носителей также следует включить в понятие машиночитаемых носителей записи.

Исполняемые компьютером команды включают, например, команды и данные, в соответствии с которыми компьютер общего назначения, компьютер специального назначения или процессорное устройство специального назначения выполняет определенную функцию или группу функций. Исполняемые компьютером команды включают также программные модули, выполняемые компьютерами автономно или в сетевых средах. В общем случае программные модули включают процедуры, программы, объекты, компоненты и структуры данных и т.п., выполняющие конкретные задачи или реализующие конкретные типы абстрактных данных. Исполняемые компьютером команды, соответствующие структуры данных и программные модули представляют примеры программных кодов для выполнения этапов описываемых здесь способов. Конкретные последовательности таких исполняемых компьютером команд или соответствующие структуры данных представляют примеры соответствующих действий для реализации функций описываемых здесь этапов.

Хотя приведенное выше описание может содержать конкретные подробности, их не следует рассматривать в качестве каких-либо ограничений для формулы изобретения. Другие конфигурации рассмотренных вариантов настоящего изобретения также составляют часть объема этого изобретения. Например, принципы рассматриваемого изобретения могут быть применены к каждому индивидуальному пользователю, если каждый пользователь может индивидуально развернуть такую систему. Это позволяет каждому пользователю использовать преимущества настоящего изобретения, даже если для какого-либо одного из большого числа возможных приложений просто не требуются описываемые здесь функциональные возможности. Другими словами, возможно множество примеров конкретной реализации электронных устройств, каждое из которых обрабатывает контент разнообразными возможными способами. Это совсем не обязательно должна быть одна система, используемая всеми конечными пользователями. Соответственно, единственным описанием настоящего изобретения следует считать прилагаемую формулу изобретения и ее законные эквиваленты, а не какие-либо конкретные примеры, приведенные здесь.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТРУКТУРА СОВМЕСТНО ИСПОЛЬЗУЕМОГО КЭША ДЛЯ ВРЕМЕННЫХ И НЕВРЕМЕННЫХ КОМАНД | 1999 |

|

RU2212704C2 |

| СИСТЕМЫ И СПОСОБЫ ПРЕДОТВРАЩЕНИЯ НЕСАНКЦИОНИРОВАННОГО ПЕРЕМЕЩЕНИЯ СТЕКА | 2014 |

|

RU2629442C2 |

| ОТСРОЧКА ОБНОВЛЕНИЙ СОСТОЯНИЙ КЭША В НЕСПЕКУЛЯТИВНОЙ КЭШ-ПАМЯТИ В ПРОЦЕССОРНОЙ СИСТЕМЕ В ОТВЕТ НА СПЕКУЛЯТИВНЫЙ ЗАПРОС ДАННЫХ ДО ТЕХ ПОР, ПОКА СПЕКУЛЯТИВНЫЙ ЗАПРОС ДАННЫХ НЕ СТАНЕТ НЕСПЕКУЛЯТИВНЫМ | 2020 |

|

RU2817624C1 |

| КОМПЬЮТЕРНАЯ СИСТЕМА И СПОСОБ ПЕРЕДАЧИ ДАННЫХ В КОМПЬЮТЕРНОЙ СИСТЕМЕ | 1999 |

|

RU2220444C2 |

| СПОСОБ ФИЛЬТРАЦИИ МЕЖПРОЦЕССОРНЫХ ЗАПРОСОВ В МНОГОПРОЦЕССОРНЫХ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМАХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2189630C1 |

| СПОСОБ МОДИФИКАЦИИ РАЗРЕШЕНИЙ НА ДОСТУП К ПАМЯТИ В ЗАЩИЩЕННОЙ ПРОЦЕССОРНОЙ СРЕДЕ | 2014 |

|

RU2602793C2 |

| СИСТЕМЫ И СПОСОБЫ ПРОВЕРКИ АДРЕСА ВОЗВРАТА ПРОЦЕДУРЫ | 2014 |

|

RU2628163C2 |

| ЗАЩИТА ДОСТУПА К ПАМЯТИ | 1998 |

|

RU2215321C2 |

| ИНТЕГРАЛЬНАЯ СХЕМА С МНОГОПОРТОВОЙ СУПЕРЯЧЕЙКОЙ ПАМЯТИ И СХЕМОЙ КОММУТАЦИИ МАРШРУТА ПЕРЕДАЧИ ДАННЫХ | 2010 |

|

RU2481652C1 |

| ЗАПИСЬ ТРАССИРОВКИ НА ОСНОВЕ КЭША С ИСПОЛЬЗОВАНИЕМ ДАННЫХ ПРОТОКОЛА КОГЕРЕНТНОСТИ КЭША | 2018 |

|

RU2775818C2 |

Изобретение относится к области кэширования однокристальных мультипроцессоров, а в частности к аморфным кэшам для однокристальных мультипроцессоров. Технический результат изобретения заключается в оптимизации работы мультипроцессорного чипа путем увеличения эффективности использования кэша. Способ распределения блоков данных в однокристальном мультипроцессоре с аморфным кэшем содержит этап вызова блока данных из запоминающего устройства данных посредством первоначального процессорного ядра. Данный способ также содержит этап сохранения первоначальной копии блока данных в банке первоначального аморфного кэша, расположенного рядом с этим первоначальным процессорным ядром. Далее осуществляют регистрацию первоначальной копии блока данных в директории домашнего банка, при этом смещение первоначальной копии блока данных для более раннего вытеснения из банка первоначального аморфного кэша путем размещения первоначальной копии блока данных ближе к по меньшей мере ранее использованному концу первоначального регистра, предназначенного для контроля виктимизации. 3 н. и 16 з.п. ф-лы, 10 ил.

1. Способ распределения блоков данных в однокристальном мультипроцессоре с аморфным кэшем, содержащий:

вызов блока данных из запоминающего устройства данных посредством первоначального процессорного ядра;

сохранение первоначальной копии блока данных в банке первоначального аморфного кэша, расположенного рядом с этим первоначальным процессорным ядром;

регистрацию первоначальной копии блока данных в директории домашнего банка;

смещение первоначальной копии блока данных для более раннего вытеснения из банка первоначального аморфного кэша путем размещения первоначальной копии блока данных ближе к по меньшей мере ранее использованному концу первоначального регистра, предназначенного для контроля виктимизации.

2. Способ по п.1, дополнительно содержащий:

вызов первоначальной копии блока данных из банка первоначального аморфного кэша посредством последующего процессорного ядра;

сохранение последующей копии блока данных в банке последующего аморфного кэша, расположенного рядом с этим последующим процессорным ядром; и

регистрацию последующей копии блока данных в директории домашнего банка.

3. Способ по п.2, дополнительно содержащий

сохранение домашней копии блока данных в банке домашнего аморфного кэша.

4. Способ по п.1, дополнительно содержащий:

вытеснение первоначальной копии блока данных из банка первоначального аморфного кэша и

запись первоначальной копии блока данных в банк домашнего аморфного кэша.

5. Способ по п.4, дополнительно содержащий

смещение первоначальной копии блока данных для более раннего вытеснения из банка домашнего аморфного кэша.

6. Способ по п.1, отличающийся тем, что директорий домашнего банка является частью банка домашнего аморфного кэша и имеет больше блоков, доступных для листинга, чем банк домашнего аморфного кэша содержит блоков данных.

7. Первоначальная ячейка однокристального мультипроцессора, содержащая:

первоначальное процессорное ядро для вызова блока данных из запоминающего устройства данных; и

первоначальный банк аморфного кэша, расположенный рядом с первоначальным процессорным ядром, для сохранения первоначальной копии блока данных, зарегистрированной в директории домашнего банка, при этом первоначальный банк аморфного кэша представляет собой гибридный кэш, имеющий общую область и частную область с динамическим распределением емкости между частной и общей областями, при этом динамическое распределение основано на размещении блоков данных в первоначальном регистре первоначальной ячейки однокристального мультипроцессора, причем первоначальный регистр предназначен для контроля виктимизации.

8. Первоначальная ячейка однокристального мультипроцессора по п.7, отличающаяся тем, что последующее процессорное ядро вызывает первоначальную копию блока данных из банка первоначального аморфного кэша, а банк последующего аморфного кэша, расположенный рядом с последующим процессорным ядром, сохраняет последующую копию блока данных, зарегистрированную в директории домашнего банка.

9. Первоначальная ячейка однокристального мультипроцессора по п.8, отличающаяся тем, что домашний банк аморфного кэша сохраняет домашнюю копию блока данных.

10. Первоначальная ячейка однокристального мультипроцессора по п.7, отличающаяся тем, что первоначальная копия блока данных смещена для более раннего вытеснения из банка первоначального аморфного кэша.

11. Первоначальная ячейка однокристального мультипроцессора по п.7, отличающаяся тем, что первоначальную копию блока данных вытесняют из банка первоначального аморфного кэша и записывают в банке домашнего аморфного кэша.

12. Первоначальная ячейка однокристального мультипроцессора по п.11, отличающаяся тем, что первоначальная копия блока данных смещена для более раннего вытеснения из банка домашнего аморфного кэша.

13. Однокристальный мультипроцессор, содержащий:

первоначальное процессорное ядро для вызова блока данных из запоминающего устройства данных;

первоначальный банк аморфного кэша, расположенный рядом с первоначальным процессорным ядром для сохранения первоначальной копии блока данных, в котором первоначальная копия блока данных вытесняется из первоначального банка аморфного кэша, записывается в домашний банк аморфного кэша как домашняя копия блока данных и смещается для более раннего вытеснения из домашнего банка аморфного кэша путем размещения домашней копии блока данных ближе к по меньшей мере ранее использованному концу домашнего регистра, предназначенного для контроля виктимизации; и

директорию домашнего банка для регистрации первоначальной копии блока данных.

14. Однокристальный мультипроцессор по п.13, дополнительно содержащий:

последующее процессорное ядро для вызова первоначальной копии блока данных из банка первоначального аморфного кэша и

банк последующего аморфного кэша, расположенный рядом с последующим процессорным ядром, для сохранения последующей копии блока данных, зарегистрированной в директории домашнего банка.

15. Однокристальный мультипроцессор по п.14, в котором

домашний банк аморфного кэша предназначен для сохранения домашней копии блока данных.

16. Однокристальный мультипроцессор по п.13, отличающийся тем, что первоначальная копия блока данных смещена для более раннего вытеснения из банка первоначального аморфного кэша.

17. Однокристальный мультипроцессор по п.13, отличающийся тем, что первоначальную копию блока данных вытесняют из банка первоначального аморфного кэша и записывают в банке домашнего аморфного кэша.

18. Однокристальный мультипроцессор по п.17, отличающийся тем, что первоначальная копия блока данных смещена для более раннего вытеснения из банка домашнего аморфного кэша.

19. Однокристальный мультипроцессор по п.13, отличающийся тем, что директорий домашнего банка является частью банка домашнего аморфного кэша и имеет больше блоков, доступных для листинга, чем банк домашнего аморфного кэша содержит блоков данных.

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| БЕСЕДИН Д | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

Авторы

Даты

2013-06-10—Публикация

2009-03-31—Подача