Изобретение относится к вычислительной технике и может использоваться в системах автоматического регулирования, автокомпенсаторах, в которых требуется получить результат накопления с помощью алгебраического сложения большого количества двоичных чисел.

Известно устройство для суммирования двоичных чисел (патент SU 1022153, опубл. 07.06.1983 г.), которое содержит накапливающий сумматор, счетчик, два элемента ЗАПРЕТ, первый и второй элементы И.

Недостатком данного устройства является то, что оно не может работать в дополнительном коде и имеет большой объем оборудования.

Наиболее близким аналогом (прототипом) заявляемого устройства является устройство для суммирования двоичных чисел (патент SU 1103223, опубл. 15.07.1984 г.). Данное устройство для суммирования двоичных чисел содержит не только накапливающий сумматор, счетчик, два элемента ЗАПРЕТ, первый и второй элементы ИЛИ, но и с целью расширения функциональных возможностей за счет обеспечения возможности суммирования двоичных чисел, представленных как дополнительным, так и обратным кодами, содержит первый, второй, третий, четвертый, пятый и шестой элементы И и элементы НЕ, что является особенностью устройства.

Недостатком известного устройства является низкое быстродействие из-за большого объема оборудования.

Задачей, на решение которой направлено заявляемое изобретение, является упрощение устройства, увеличение быстродействия и надежности устройства.

Данная задача решается за счет того, что устройство для суммирования содержит накапливающий сумматор, элемент 2И, а также параллельный регистр, который является оперативной памятью накапливающего сумматора. При этом n первых младших входов накапливающего сумматора соединены с входами устройства, а (m+1) первых старших входов накапливающего сумматора соединены со знаковым входом устройства, входы накапливающего сумматора соединены с входами параллельного регистра, выходы которого соединены со вторыми входами накапливающего сумматора и с выходами устройства, вход синхронизации параллельного регистра соединен с входом синхронизации устройства, выход переноса накапливающего сумматора соединен с первым входом элемента 2И, второй вход которого подключен к входу выбора режима устройства, а выход подключен к входу переноса накапливающего сумматора.

Отличительным признаком от прототипа является то, что в предлагаемом устройстве используется параллельный регистр, который позволяет последовательно суммировать входящие числа с каждым синхросигналом, исключая при этом содержащиеся в вышеуказанном прототипе счетчик, первый и второй элементы ИЛИ, второй, третий, четвертый, пятый и шестой элементы И, элемент НЕ, первый и второй элементы запрета.

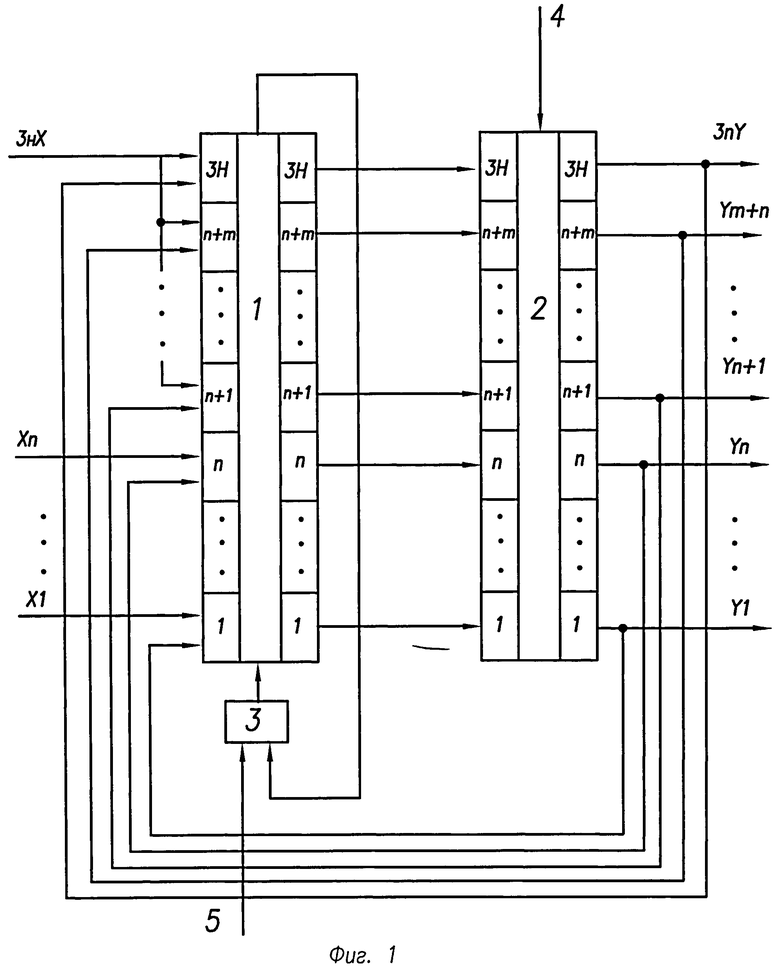

На фиг.1 представлена блок-схема устройства для суммирования.

Устройство для суммирования содержит:

1 - накапливающий сумматор;

2 - параллельный регистр;

3 - элемент 2И;

4 - вход синхронизации;

5 - вход выбора режима.

Сущность работы данного изобретения заключается в том, что на первые информационные входы устройства накапливающего сумматора 1 поступает число х, выраженное обратным или дополнительным кодом, представленное n-информационными и одним знаковым разрядом, причем первый вход знакового разряда соединен с (m+1) старшими первыми входами накапливающего сумматора 1, а полученный результат представлен (n+m)-информационными и одним знаковым разрядами в обратном или дополнительном коде. Полученный результат записывается в параллельный регистр 2 по синхросигналу, поступающему на вход синхронизации 4. С выхода параллельного регистра 2 получаемый результат y поступает на выход устройства и на вторые информационные входы накапливающего сумматора 1.

Устройство позволяет суммировать массивы чисел путем алгебраического сложения очередного (n+1)-разрядного, включая знаковый разряд, (k+1)-го входного числа с результатом сложения предыдущих k чисел, хранящимся в регистре 2 после k-го синхросигнала, поступающего на вход синхронизации 4.

При суммировании чисел, выраженных обратным кодом, подается единичный сигнал на вход выбора режима 5 элемента 2И 3 и замыкается цепь циклического переноса. При этом единичные и нулевые сигналы переноса с выхода переноса накапливающего сумматора 1 поступают через элемент 2И 3 на вход переноса накапливающего сумматора 1.

При суммировании чисел, выраженных дополнительным кодом, подается нулевой сигнал на вход выбора режима 5 элемента 2И 3 и цепь циклического переноса накапливающего сумматора 1 поступает нулевой сигнал с выхода элемента 2И 3.

Устройство, содержащее m+n информационных разрядов, при суммировании чисел одного знака и максимальных по модулю допускает сложение 2m чисел разрядностью (n+1), включая знаковый разряд.

Таким образом, за счет введения параллельного регистра и новых связей положительный эффект предлагаемого устройства заключается в уменьшении объема оборудования и, следовательно, в повышении быстродействия и надежности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования двоичных чисел | 1983 |

|

SU1103223A2 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| Устройство для суммирования двоичных чисел | 1983 |

|

SU1087987A1 |

| Устройство для суммирования чисел | 1984 |

|

SU1183959A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для суммирования п-разрядных двоичных чисел | 1976 |

|

SU634275A1 |

Изобретение относится к вычислительной технике и может использоваться в системах автоматического регулирования, автокомпенсаторах, в которых требуется получить результат накопления с помощью алгебраического сложения большого количества двоичных чисел. Технический результат заключается в увеличении быстродействия и надежности устройства для суммирования. Технический результат достигается за счет устройства для суммирования, которое содержит накапливающий сумматор, элемент 2И, а также параллельный регистр, который является оперативной памятью накапливающего сумматора, n первых младших входов накапливающего сумматора, (m+1) первых старших входов накапливающего сумматора, знаковый вход устройства, вход синхронизации параллельного регистра, выход переноса накапливающего сумматора, первый вход элемента 2И, вход выбора режима устройства. 1 ил.

Устройство для суммирования, содержащее накапливающий сумматор, элемент 2И, а также параллельный регистр, который является оперативной памятью накапливающего сумматора, отличающееся тем, что n первых младших входов накапливающего сумматора соединены с входами устройства, а (m+1) первых старших входов накапливающего сумматора соединены со знаковым входом устройства, выходы накапливающего сумматора соединены с входами параллельного регистра, выходы которого соединены со вторыми входами накапливающего сумматора и с выходами устройства, вход синхронизации параллельного регистра соединен с входом синхронизации устройства, выход переноса накапливающего сумматора соединен с первым входом элемента 2И, второй вход которого подключен к входу выбора режима устройства, а выход подключен к входу переноса накапливающего сумматора.

| Накапливающий сумматор | 1984 |

|

SU1251074A1 |

| Накапливающий сумматор | 1987 |

|

SU1453400A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2381546C2 |

| Устройство для суммирования двоичных чисел | 1983 |

|

SU1103223A2 |

| Накапливающий сумматор | 1989 |

|

SU1640685A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

Авторы

Даты

2015-04-10—Публикация

2013-03-21—Подача