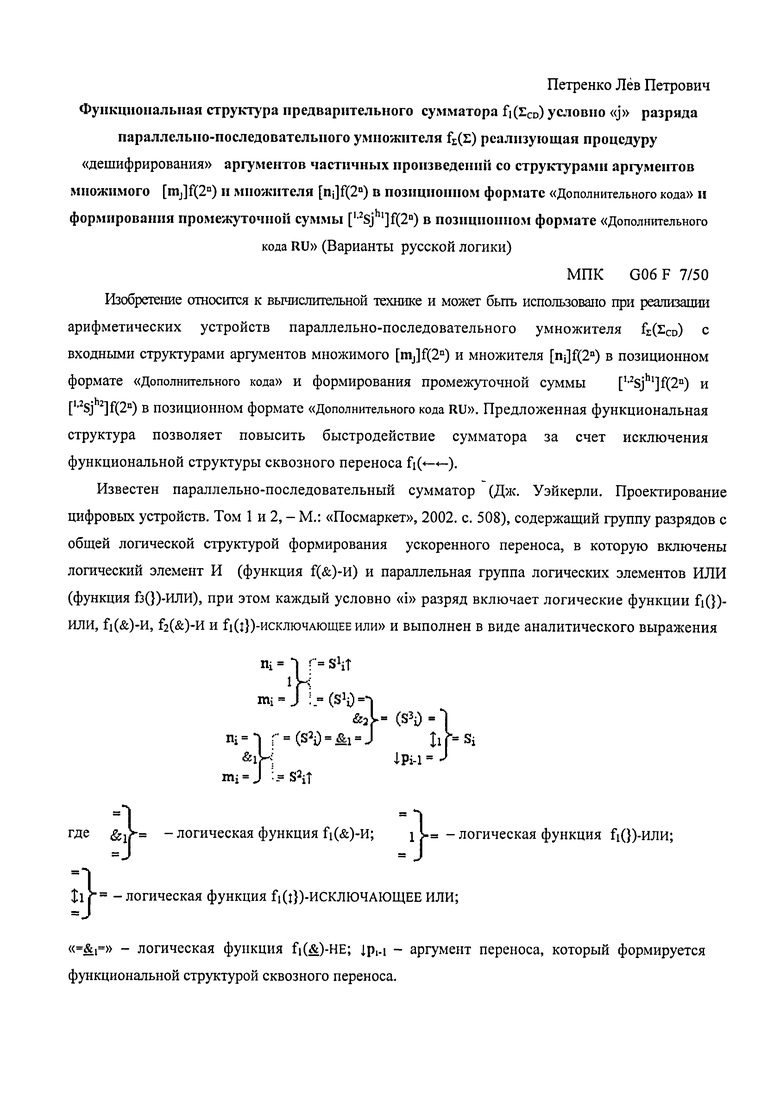

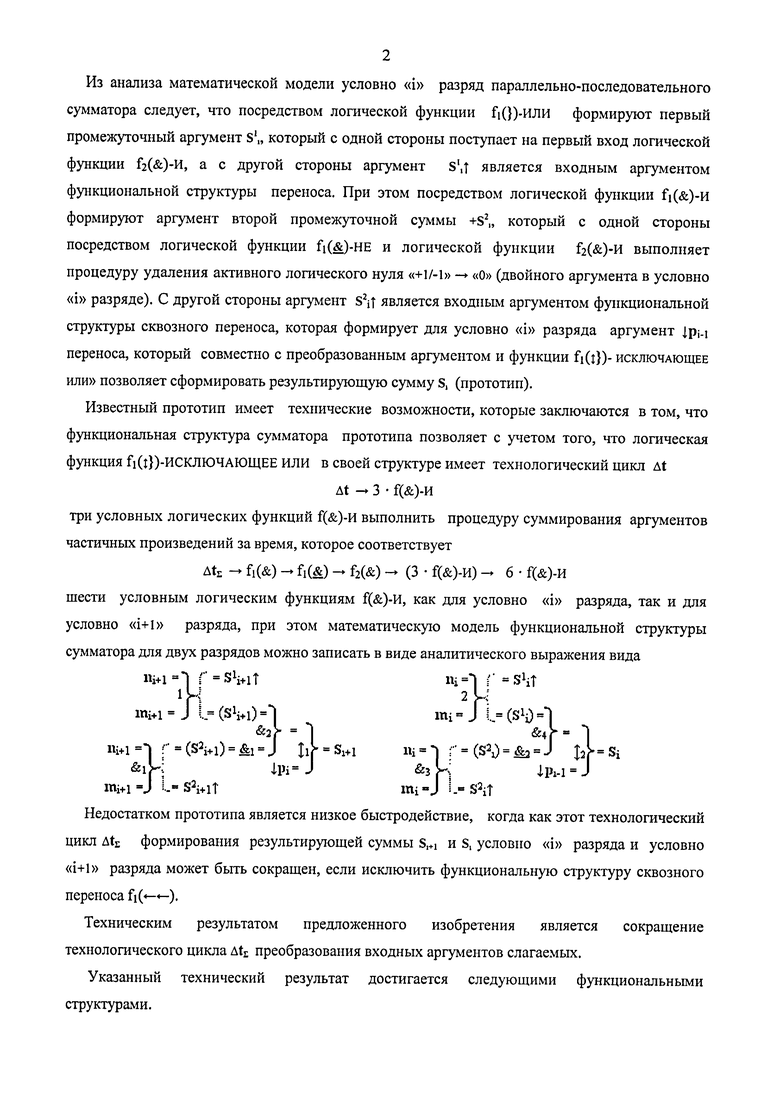

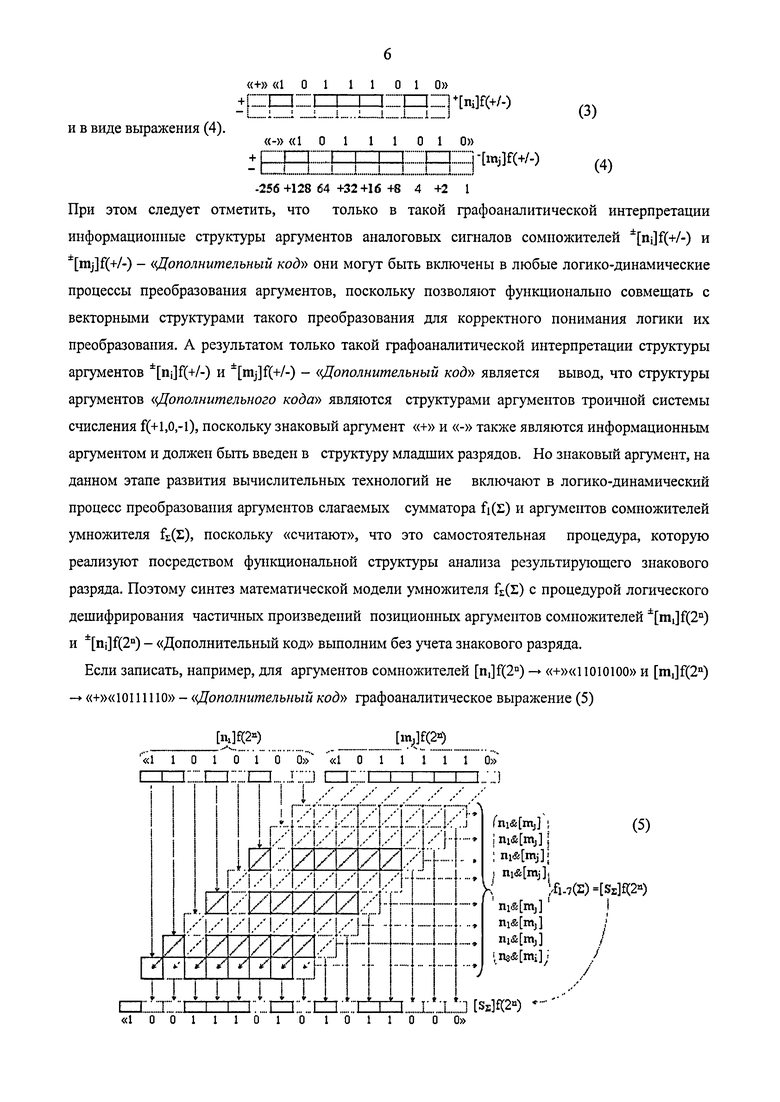

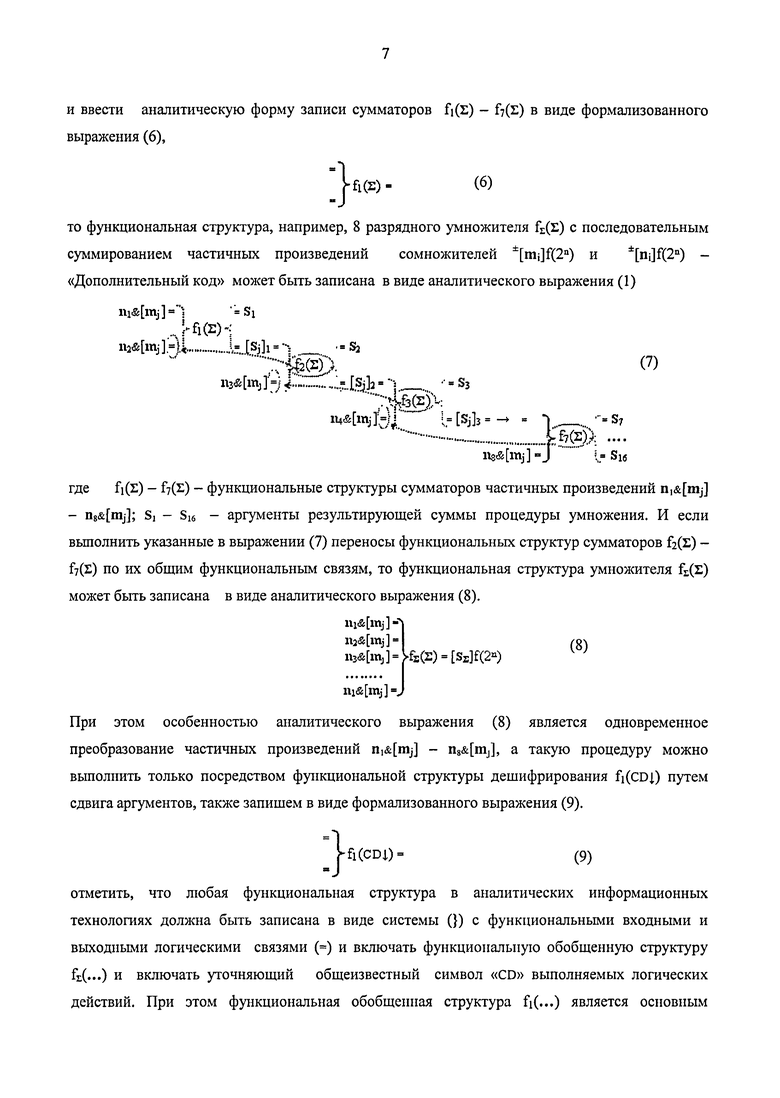

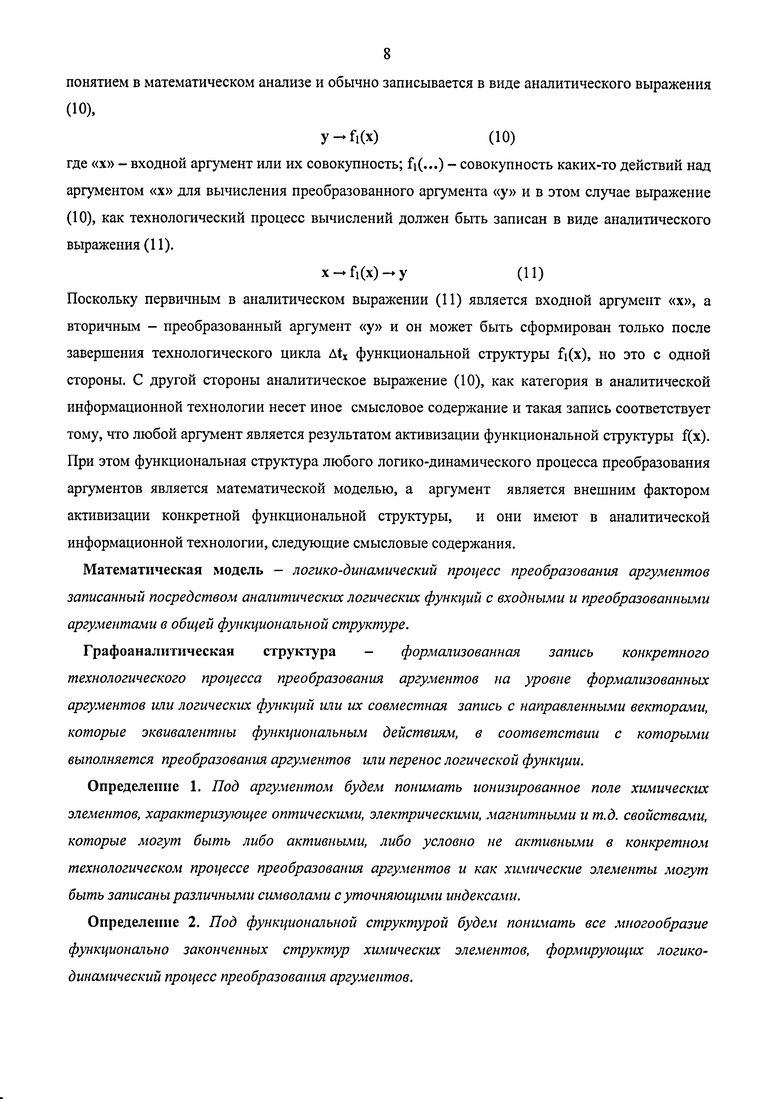

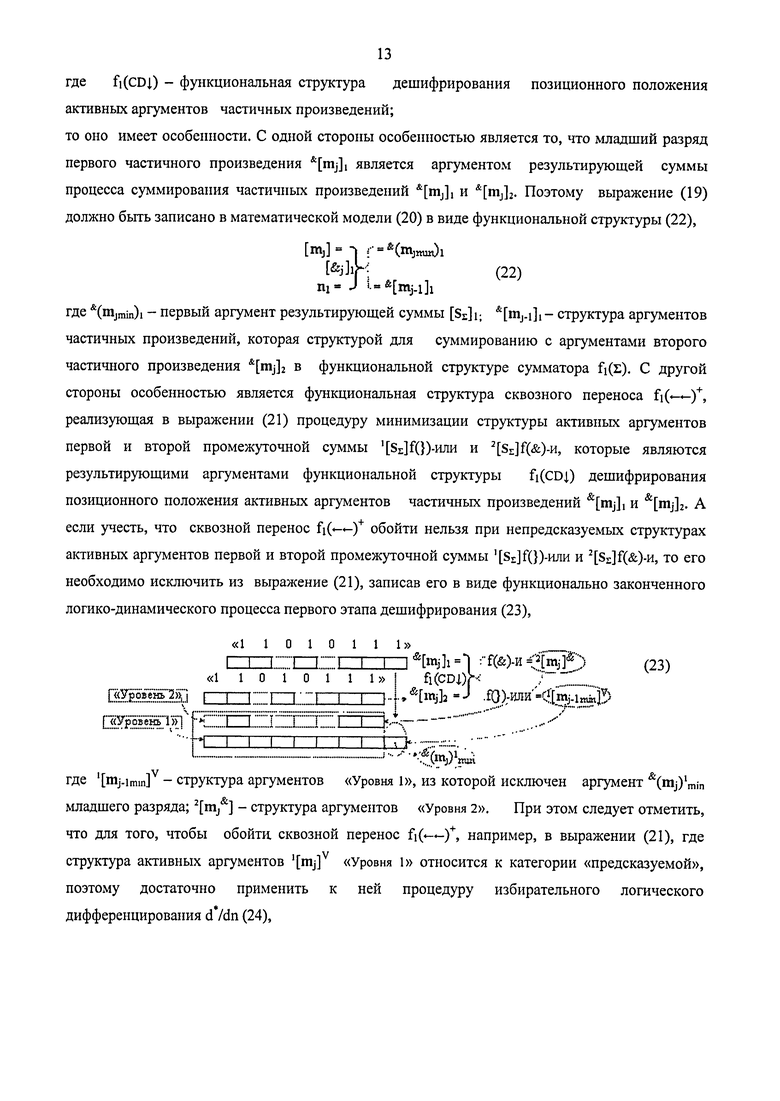

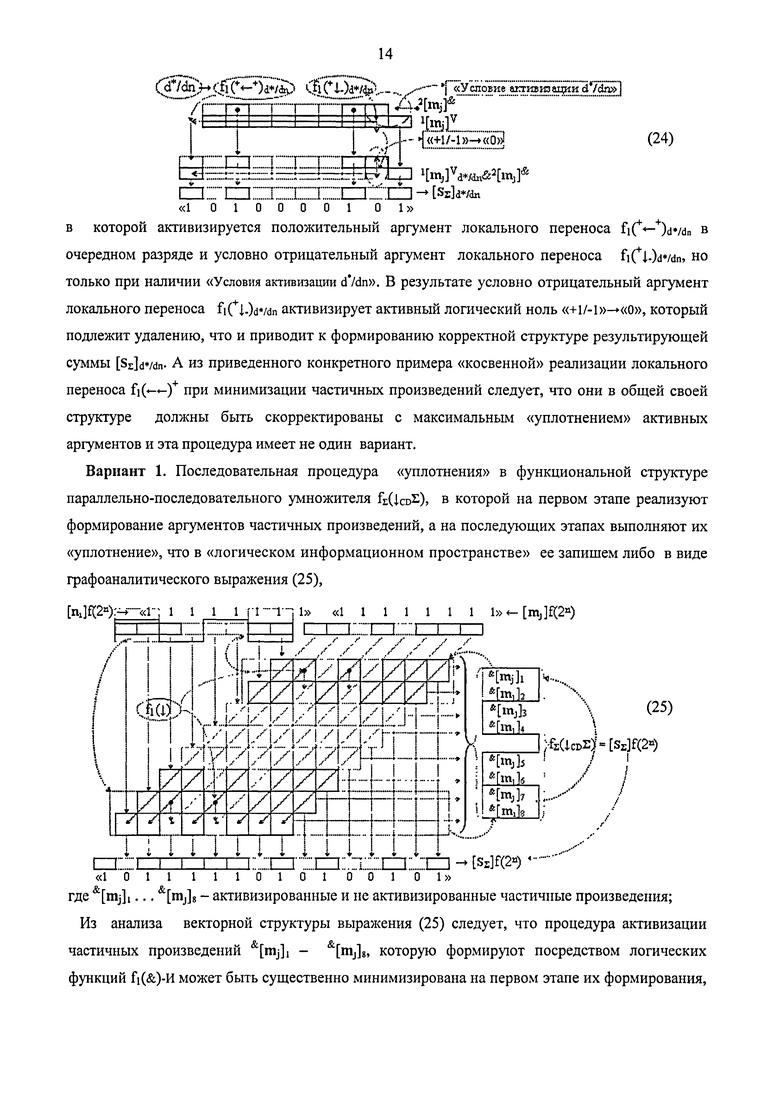

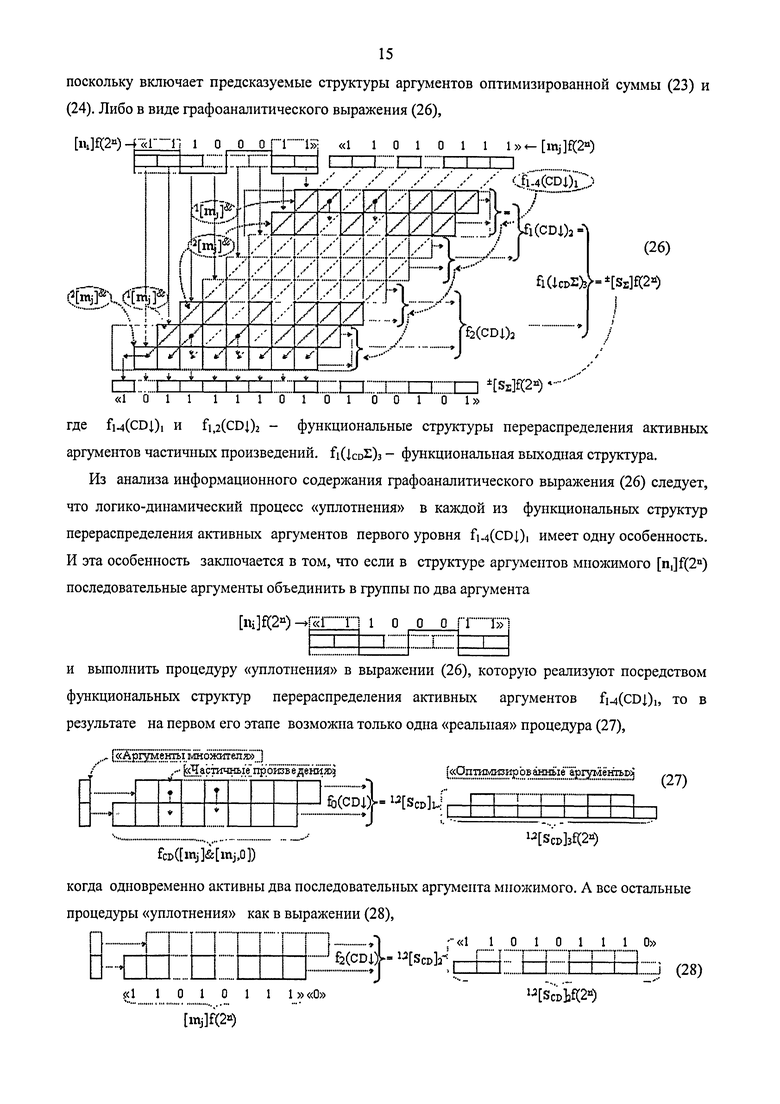

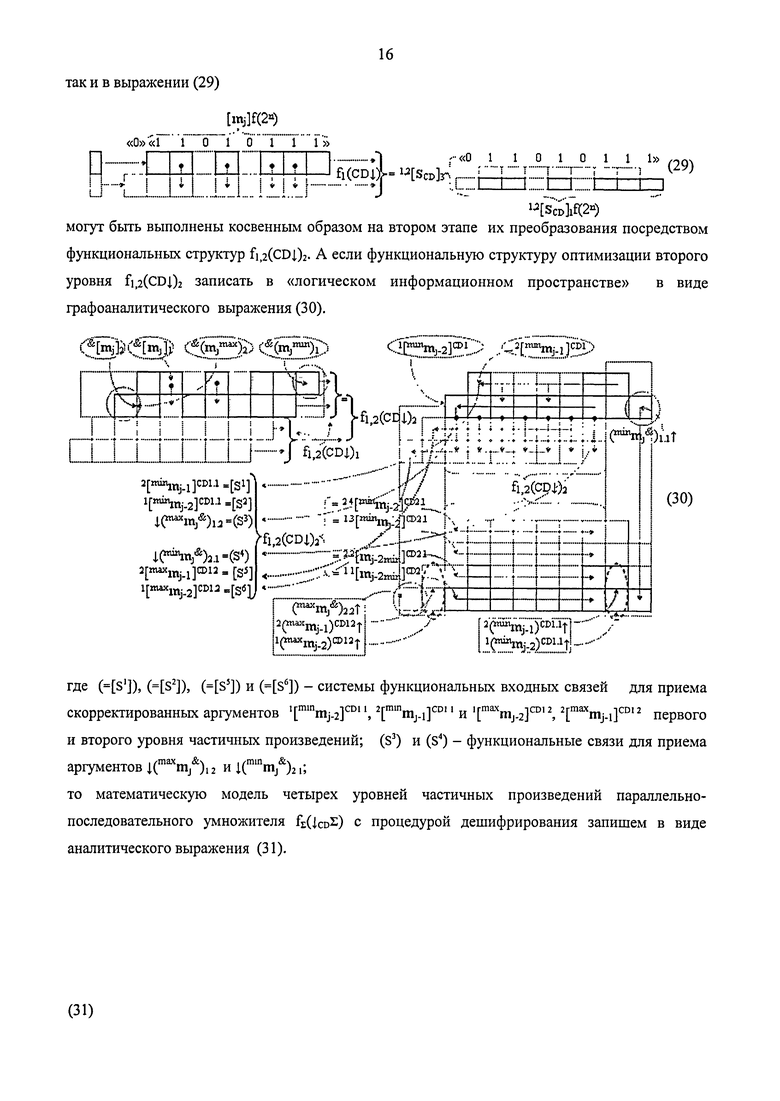

Текст описания приведен в факсимильном виде.

Группа изобретений относится к вычислительной технике и может быть использована при построении параллельно-последовательного умножителя с входными аргументами слагаемых [mj]f(2n) и [ni]f(2n) в формате «дополнительный код». Техническим результатом является повышение быстродействия преобразования входных аргументов. В одном из вариантов структура реализована с использованием логических элементов И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ. 2 н.п. ф-лы.

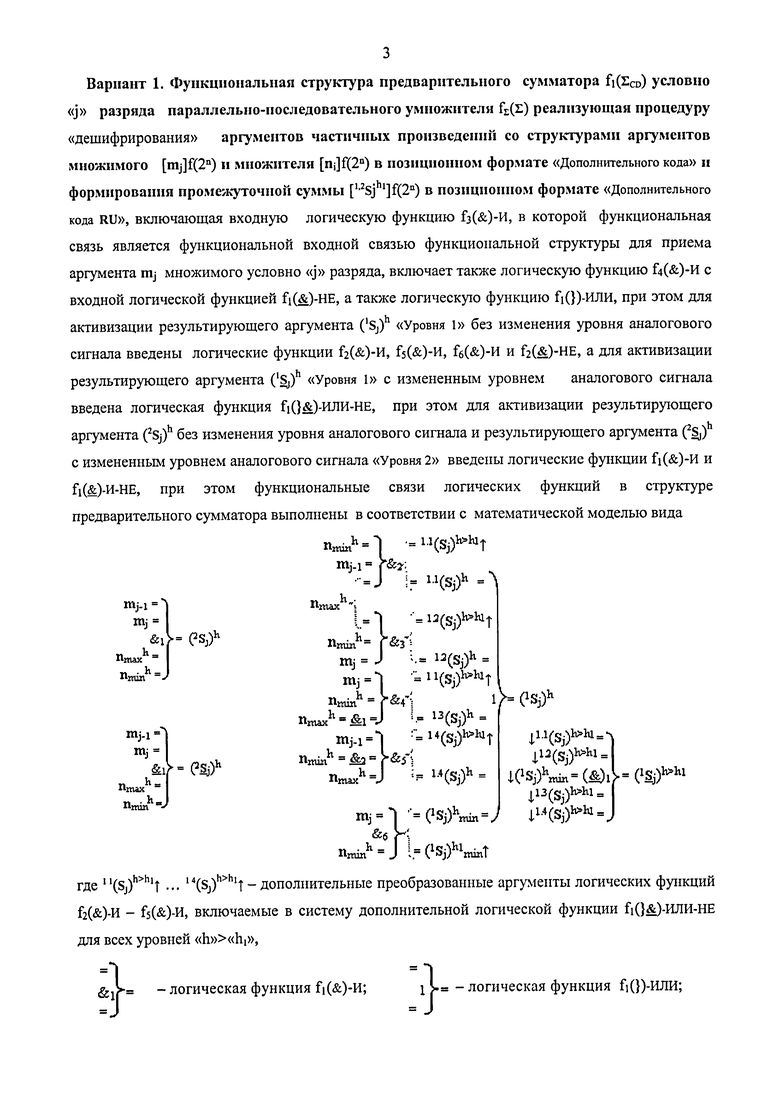

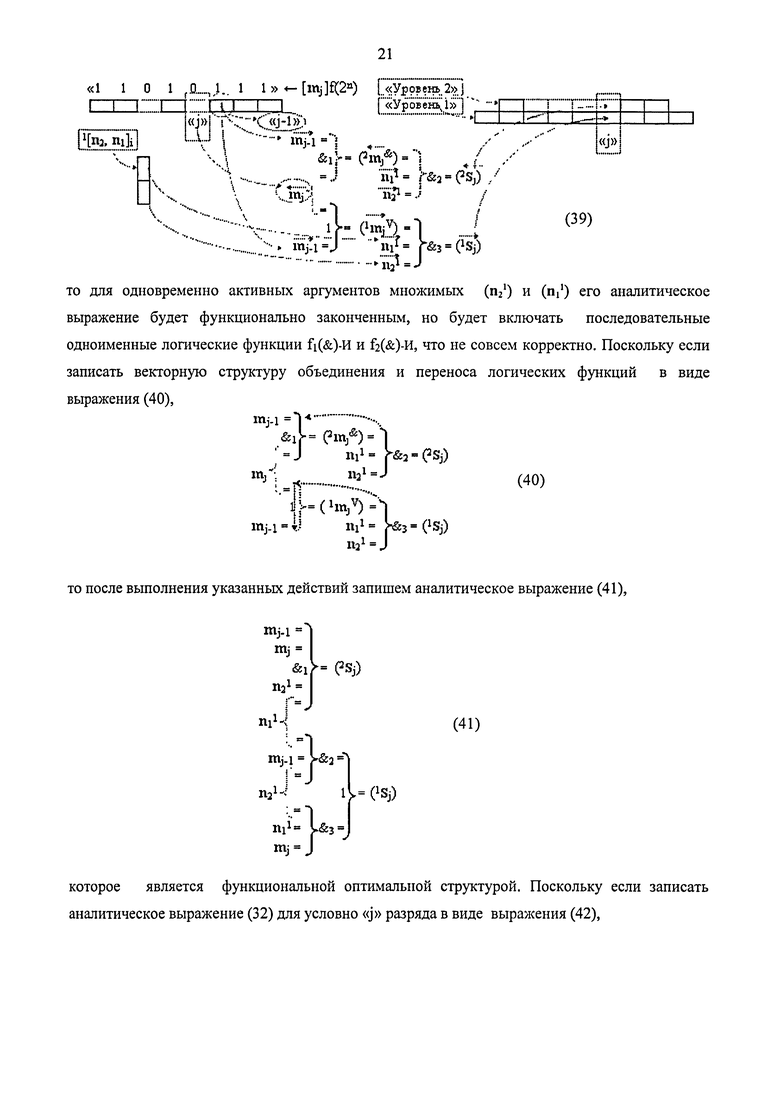

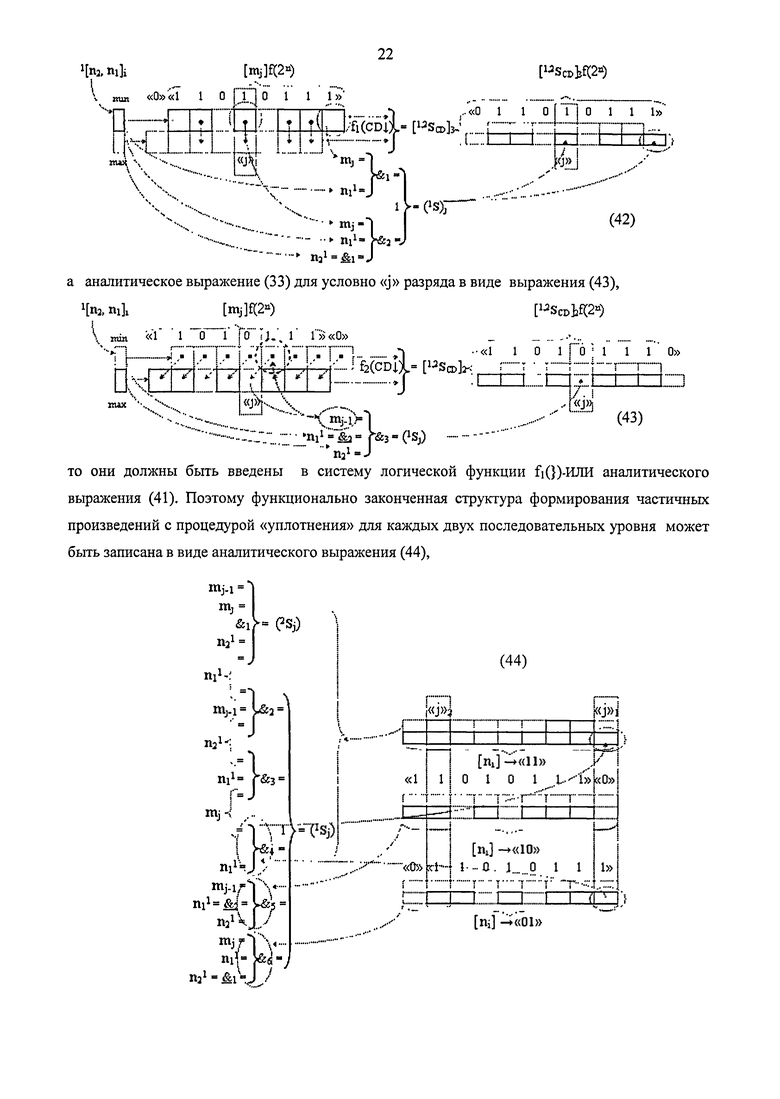

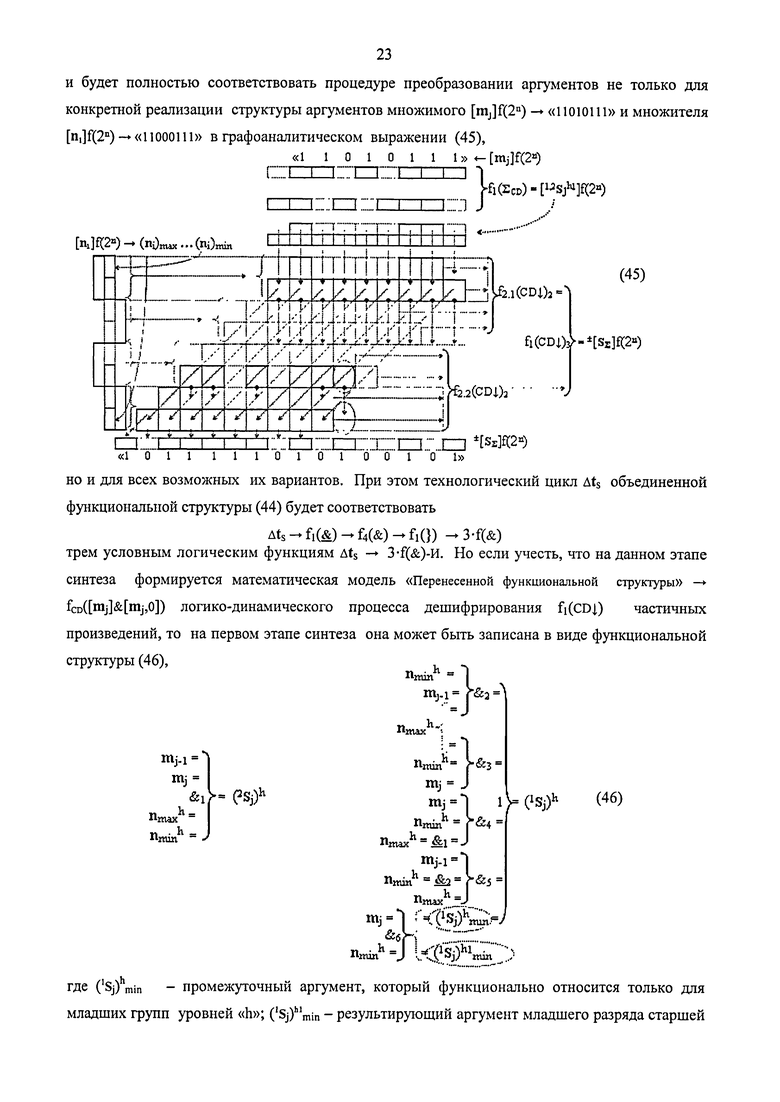

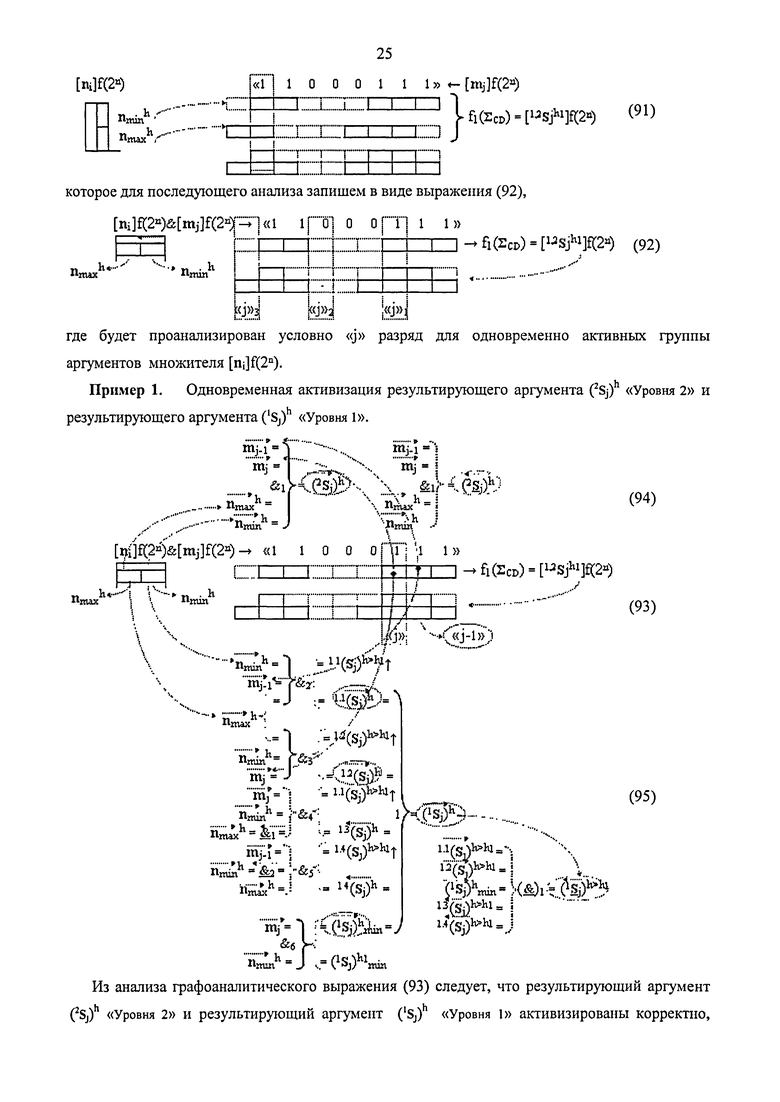

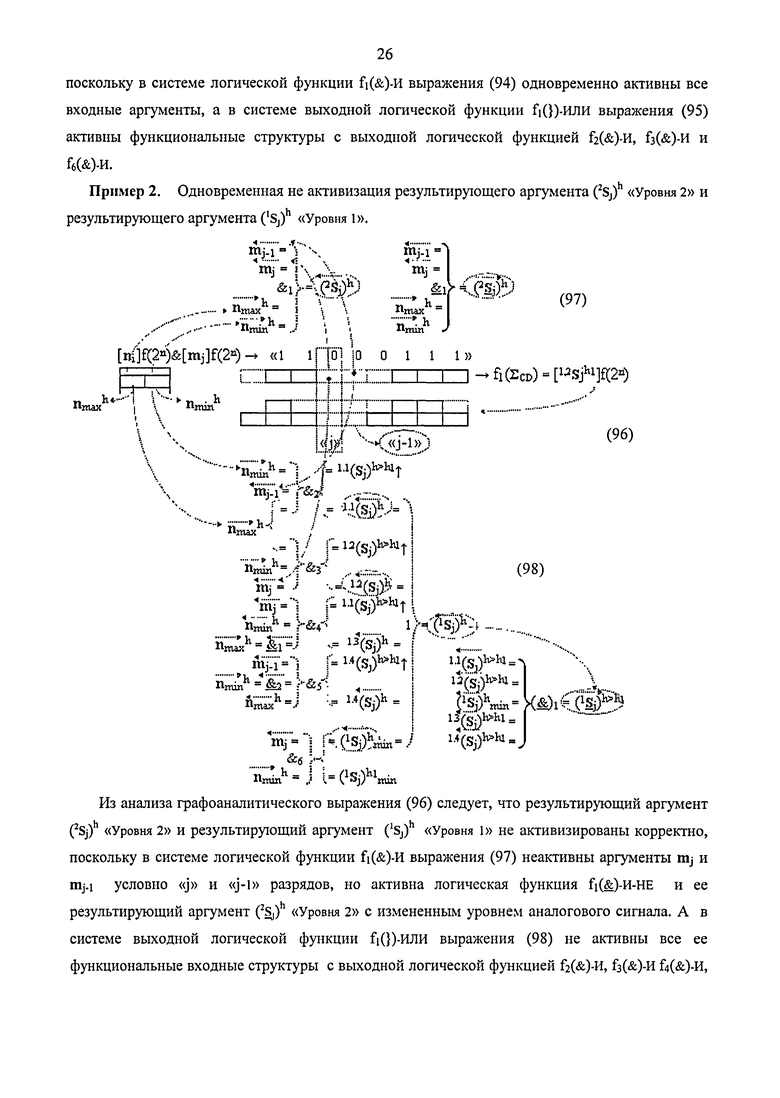

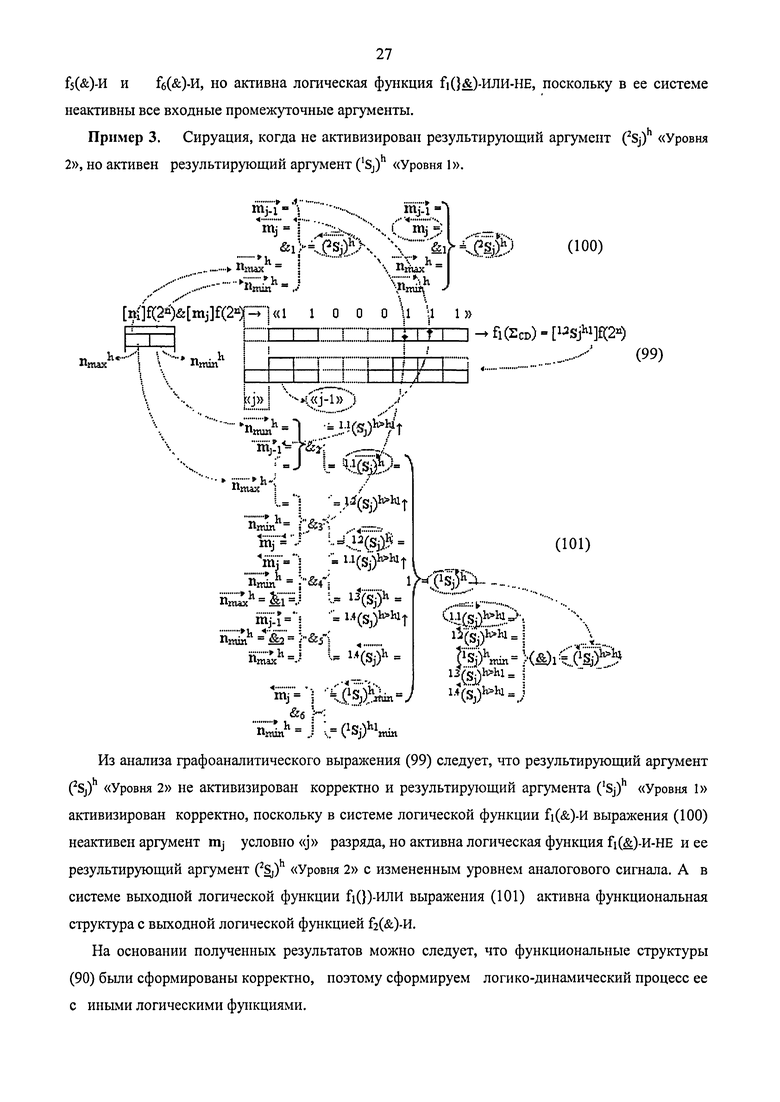

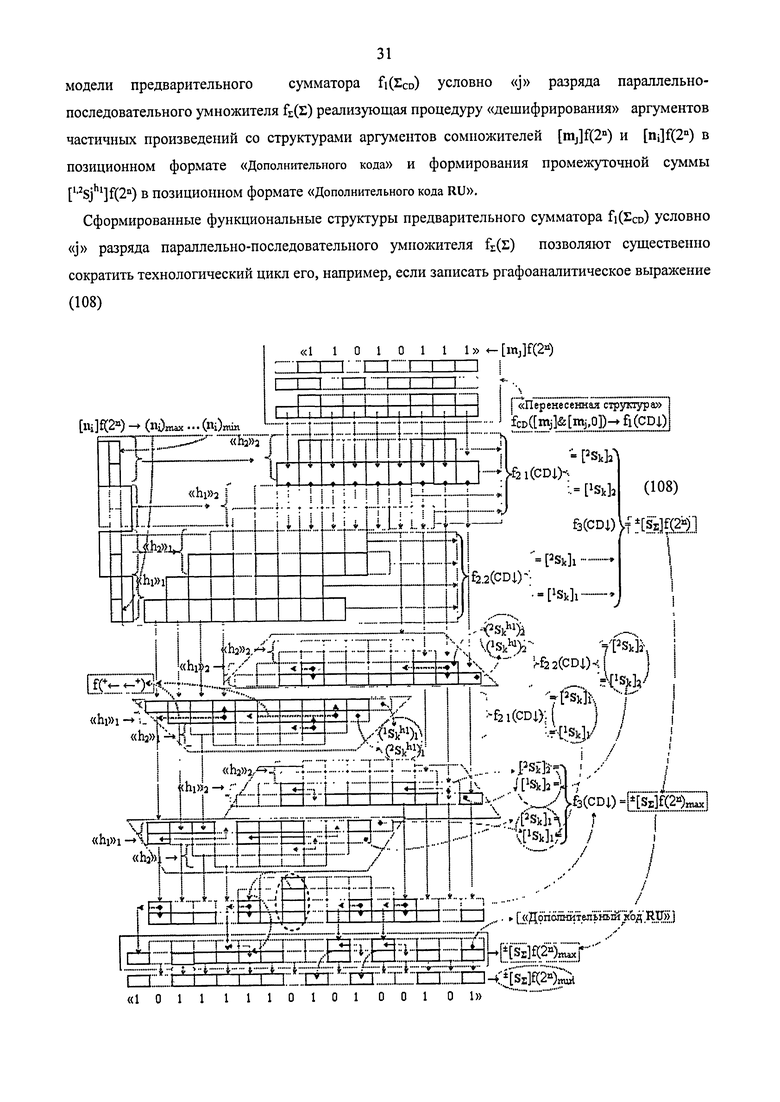

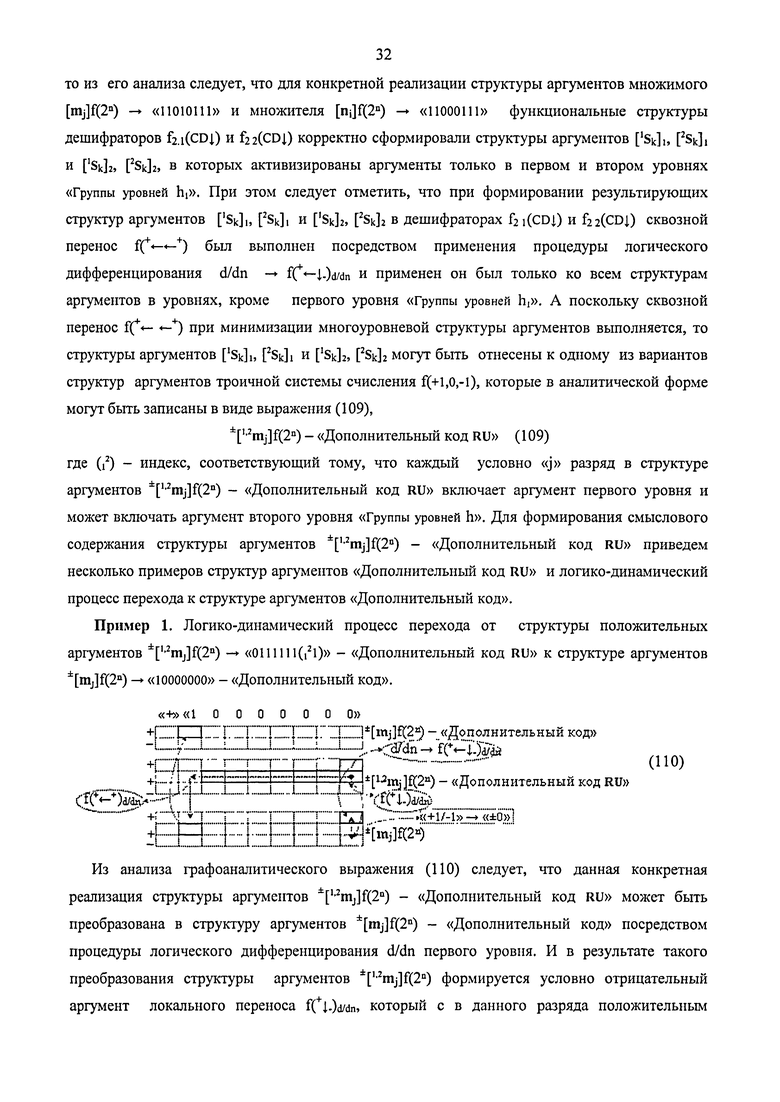

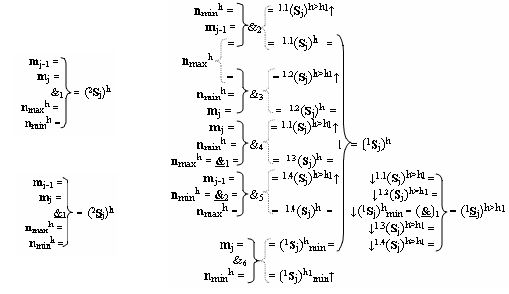

1. Функциональная структура предварительного сумматора f1(ΣCD) условно «j» разряда параллельно-последовательного умножителя fΣ(Σ) реализующая процедуру «дешифрирования» аргументов частичных произведений со структурами аргументов множимого [mj]f(2n) и множителя [ni]f(2n) в позиционном формате «Дополнительного кода» и формирования промежуточной суммы [1,2Sjh1]f(2n) в позиционном формате «Дополнительного кода RU», включающая входную логическую функцию f3(&)-И, в которой функциональная связь является функциональной входной связью функциональной структуры для приема аргумента mj множимого условно «j» разряда, включает также логическую функцию f4(&)-И с входной логической функцией f1(

&

)-НЕ, а также логическую функцию f1(})-ИЛИ, отличающаяся тем, что для активизации результирующего аргумента (1

S

j)h «Уровня 1» без изменения уровня аналогового сигнала введены логические функции f2(&)-И, f5(&)-И, f6(&)-И и f2(

&

)-НЕ, а для активизации результирующего аргумента (1

S

j)h «Уровня 1» с измененным уровнем аналогового сигнала введена логическая функция f1(}&

)-ИЛИ-НЕ, при этом для активизации результирующего аргумента (2

S

j)h без изменения уровня аналогового сигнала и результирующего аргумента (2

S

j)h с измененным уровнем аналогового сигнала «Уровня 2» введены логические функции f1(&)-И и f1(&)-И-НЕ, при этом функциональные связи логических функций в структуре предварительного сумматора выполнены в соответствии с математической моделью вида

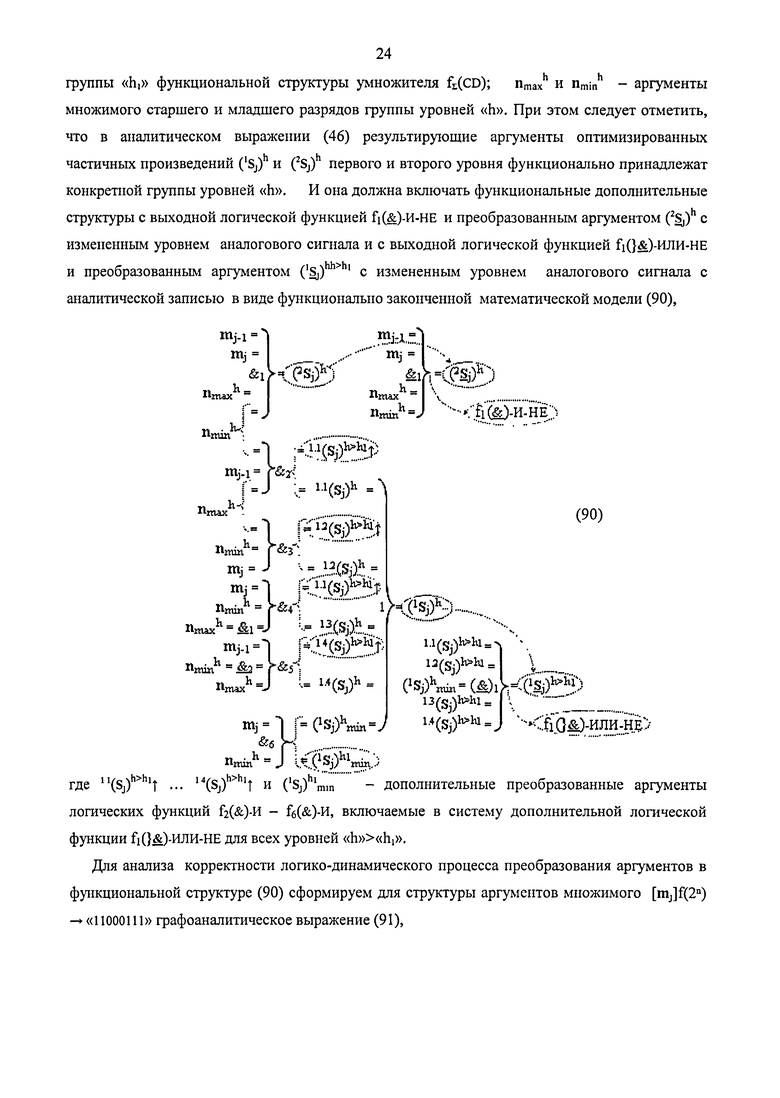

где 1.1(S

j)h>h1↑ … 1.4(S

j)h>h1↑ - дополнительные преобразованные аргументы логических функций f2(&)-И - f5(&)-И, включаемые в систему дополнительной логической функции f1(}&

)-ИЛИ-НЕ для всех уровней «h»>«h1»,

- логическая функция f1(&)-И;

- логическая функция f1(&)-И;

- логическая функция f1(})-ИЛИ;

- логическая функция f1(}&

)-ИЛИ-НЕ;

- логическая функция f1(&)-И-НЕ;

«=

&

1=» - логическая функция f1(

&

)-НЕ изменения активности входных аналоговых сигналов.

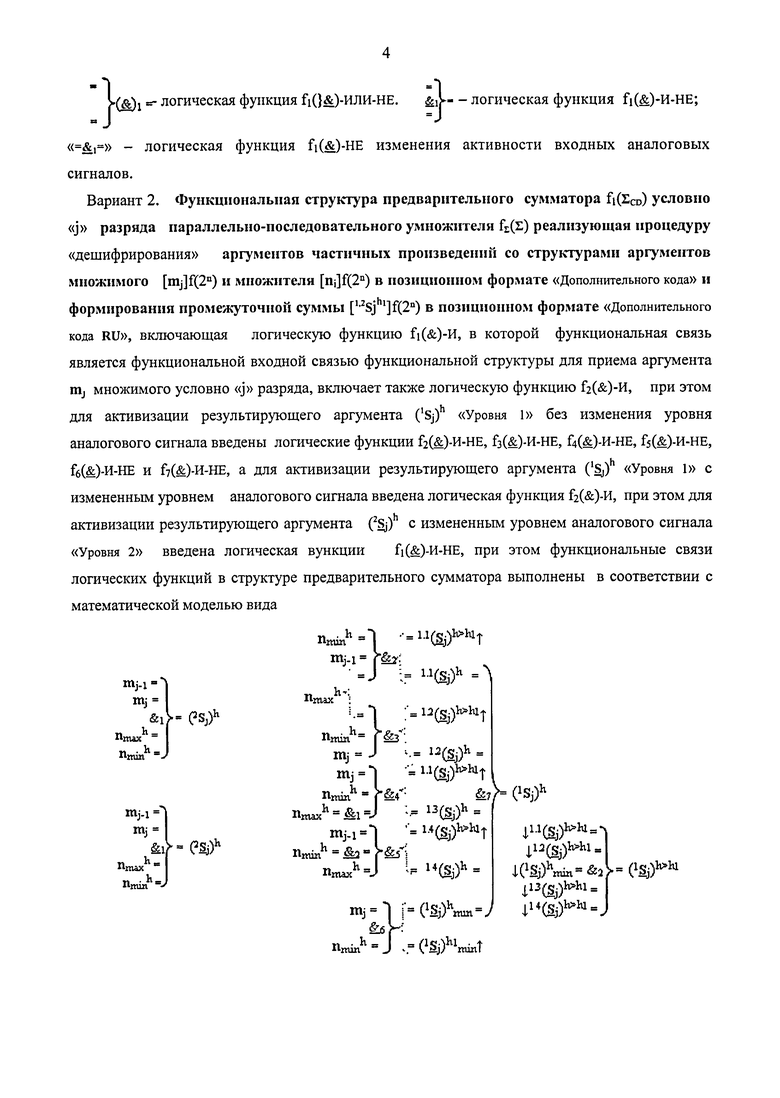

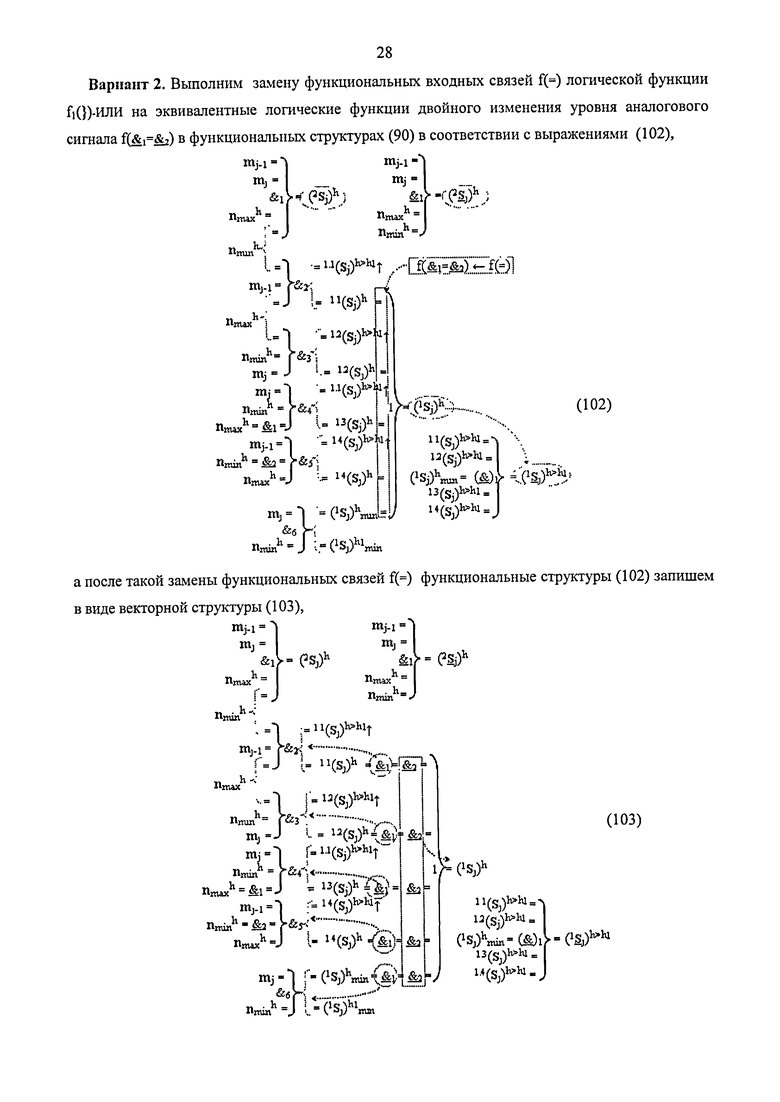

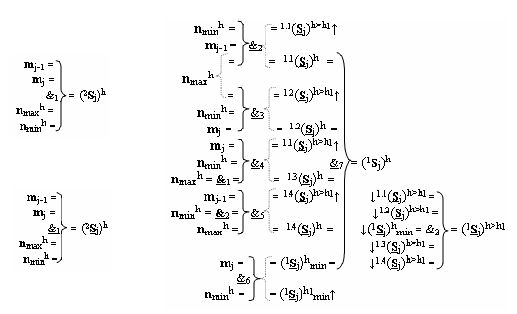

2. Функциональная структура предварительного сумматора f1(ΣCD) условно «j» разряда параллельно-последовательного умножителя fΣ(Σ) реализующая процедуру «дешифрирования» аргументов частичных произведений со структурами аргументов сомножителей [mj]f(2n) и [ni]f(2n) в позиционном формате «Дополнительного кода» и формирования промежуточной суммы [1,2Sjh1]f(2n) и [1,2Sjh2]f(2n) в позиционном формате «Дополнительного кода RU», включающая логическую функцию f1(&)-И, в которой функциональная связь является функциональной входной связью функциональной структуры для приема аргумента mj множимого условно «j» разряда, включает также логическую функцию f2(&)-И, отличающаяся тем, что для активизации результирующего аргумента (1

S

j)h «Уровня 1» без изменения уровня аналогового сигнала введены логические функции f2(&)-И-НЕ, f3(&)-И-НЕ, f4(&)-И-НЕ, f5(&)-И-НЕ, f6(&)-И-НЕ и f7(&)-И-НЕ, а для активизации результирующего аргумента (1

S

j)h «Уровня 1» с измененным уровнем аналогового сигнала введена логическая функция f2(&)-И, при этом для активизации результирующего аргумента (2

S

j)h с измененным уровнем аналогового сигнала «Уровня 2» введена логическая функция f1(&)-И-НЕ, при этом функциональные связи логических функций в структуре предварительного сумматора выполнены в соответствии с математической моделью вида

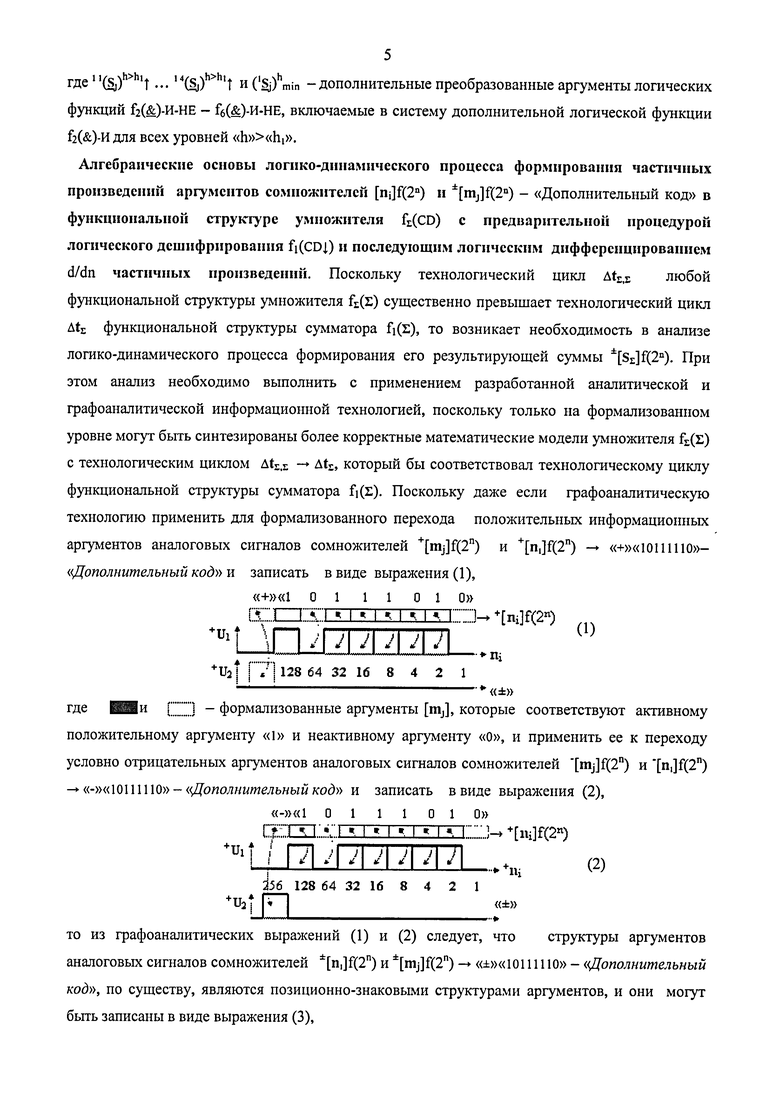

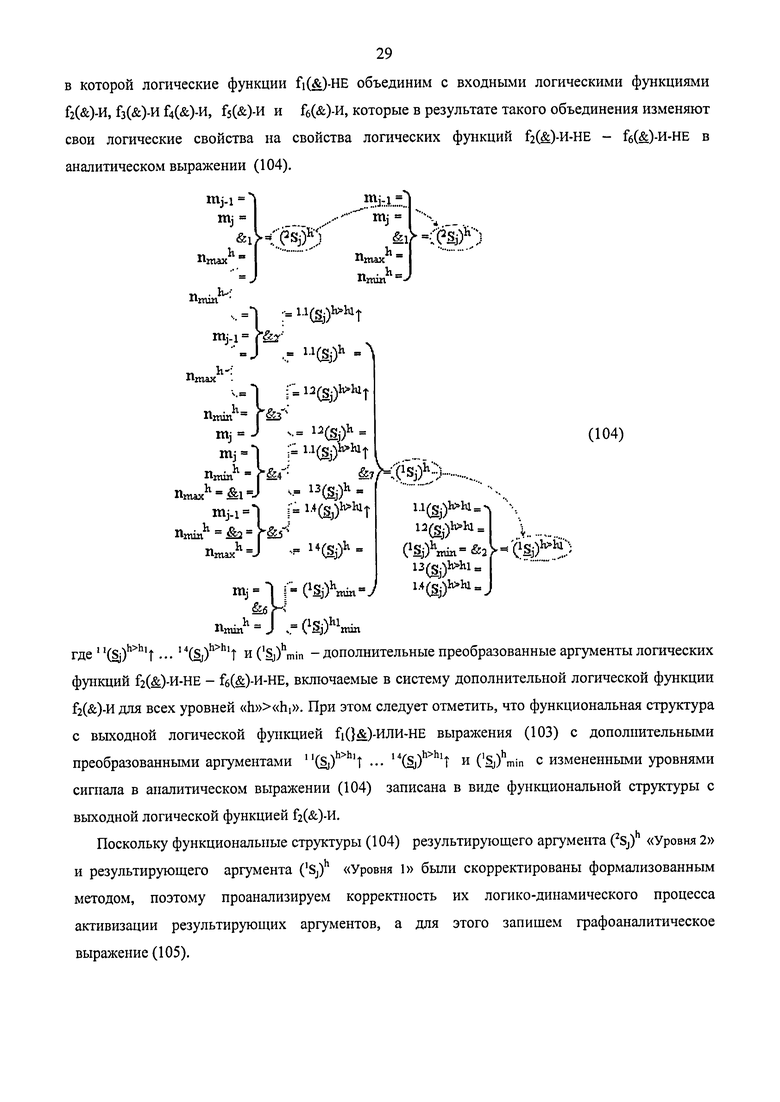

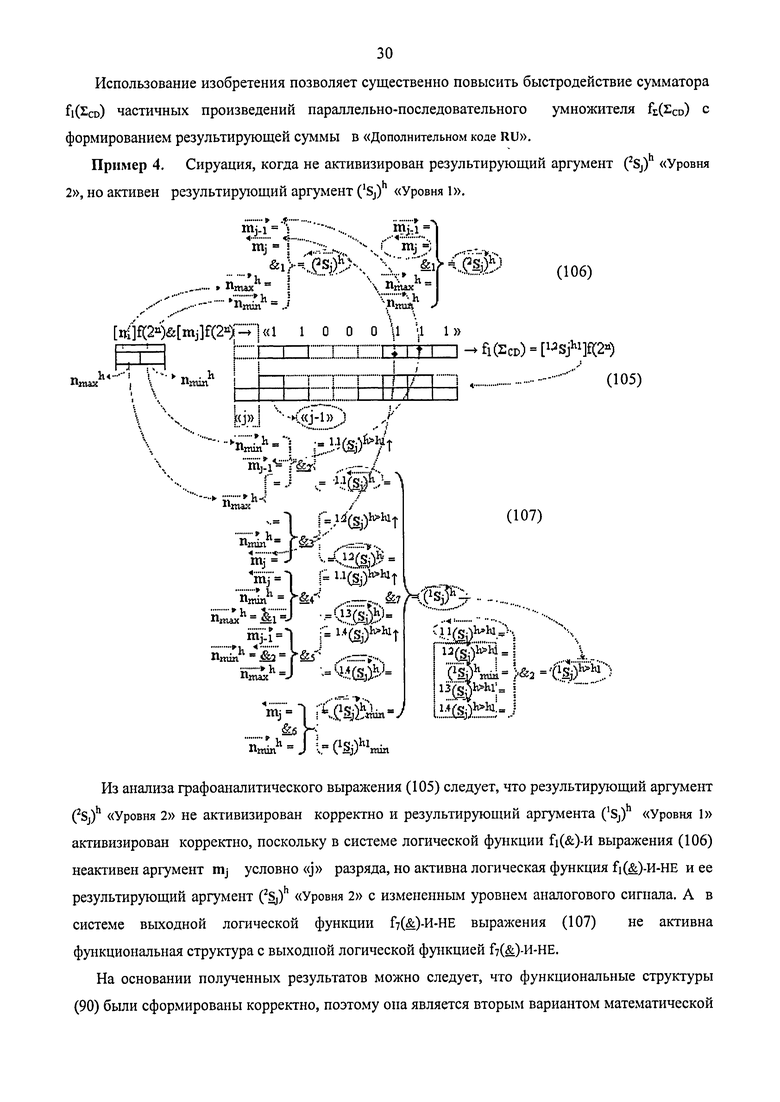

где 1.1(

S

j)h>h1↑ … 1.4(

S

j)h>h1↑ и (1

S

j)h min - дополнительные преобразованные аргументы логических функций f2(&)-И-НЕ - f6(&)-И-НЕ, включаемые в систему дополнительной логической функции f2(&)-И для всех уровней «h»>«h1».

| ДЖ | |||

| УЭЙКЕРЛИ, ПРОЕКТИРОВАНИЕ ЦИФРОВЫХ УСТРОЙСТВ | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ выделения сульфокислот из нефтяных масел | 1913 |

|

SU508A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| ФУНКЦИОНАЛЬНАЯ СТРУКТУРА ПРЕДВАРИТЕЛЬНОГО СУММАТОРА f([m]&[m,0]) ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОГО УМНОЖИТЕЛЯ f(Σ) С ПРОЦЕДУРОЙ ЛОГИЧЕСКОГО ДИФФЕРЕНЦИРОВАНИЯ d/dn ПЕРВОЙ ПРОМЕЖУТОЧНОЙ СУММЫ [S ]f(})-ИЛИ СТРУКТУРЫ АКТИВНЫХ АРГУМЕНТОВ МНОЖИМОГО [0,m]f(2) и [m,0]f(2) (ВАРИАНТЫ) | 2010 |

|

RU2424549C1 |

| ФУНКЦИОНАЛЬНАЯ СТРУКТУРА ПРЕДВАРИТЕЛЬНОГО СУММАТОРА ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОГО УМНОЖИТЕЛЯ f(Σ) С АРГУМЕНТАМИ МНОЖИМОГО [m]f(2) И МНОЖИТЕЛЯ [n]f(2) В ПОЗИЦИОННОМ ФОРМАТЕ (ВАРИАНТЫ) | 2010 |

|

RU2422879C1 |

| US 5426598 A, 20.06.1995 | |||

| JP 63197227 A, 16.08.1988 | |||

| US 2006184605 A1, 17.08.2006. | |||

Авторы

Даты

2016-06-10—Публикация

2011-12-20—Подача